# 8-Channel, 24-Bit ANALOG-TO-DIGITAL CONVERTER

## **FEATURES**

- 24 BITS NO MISSING CODES

- INL: 0.0012% of FSR (max)

- FULL-SCALE INPUT: ±2V<sub>REF</sub>

- PGA FROM 1 TO 128

- 22 BITS EFFECTIVE RESOLUTION (PGA = 1), 19 BITS (PGA = 128)

- SINGLE CYCLE SETTLING MODE

- PROGRAMMABLE DATA OUTPUT RATES UP TO 1kHz

- ON-CHIP 1.25V/2.5V REFERENCE

- ON-CHIP CALIBRATION

- SPI COMPATIBLE

- POWER SUPPLY: 2.7V to 5.25V

- < 1mW POWER CONSUMPTION, V<sub>DD</sub> = 3V

## **APPLICATIONS**

- INDUSTRIAL PROCESS CONTROL

- LIQUID/GAS CHROMATOGRAPHY

- BLOOD ANALYSIS

- SMART TRANSMITTERS

- PORTABLE INSTRUMENTATION

- WEIGH SCALES

- PRESSURE TRANSDUCERS

# DESCRIPTION

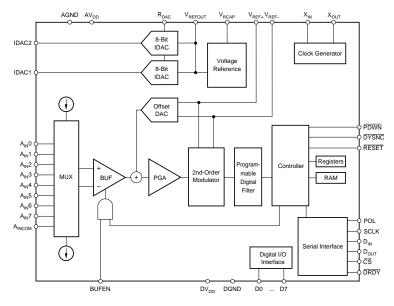

The ADS1217 is a precision, wide dynamic range, deltasigma, Analog-to-Digital (A/D) converter with 24-bit resolution operating from 2.7V to 5.25V supplies. The delta-sigma, A/D converter provides up to 24 bits of no missing code performance and effective resolution of 22 bits.

The eight input channels are multiplexed. Internal buffering can be selected to provide a very high input impedance for direct connection to transducers or low-level voltage signals. Burnout current sources are provided that allow for the detection of an open or shorted sensor. An 8-bit Digital-to-Analog Converter (DAC) provides an offset correction with a range of 50% of the FSR (Full-Scale Range).

The PGA (Programmable Gain Amplifier) provides selectable gains of 1 to 128 with an effective resolution of 19 bits at a gain of 128. The A/D conversion is accomplished with a 2nd-order, delta-sigma modulator and programmable sinc filter. The reference input is differential and can be used for ratiometric measurements. The onboard current DACs operate independently with the maximum current set by an external resistor.

The serial interface is SPI compatible. Eight bits of digital I/O are also provided that can be used for input or output. The ADS1217 is designed for high-resolution measurement applications in smart transmitters, industrial process control, weigh scales, chromatography, and portable instrumentation.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| AV <sub>DD</sub> to AGND             |                                  |

|--------------------------------------|----------------------------------|

| DV <sub>DD</sub> to DGND             |                                  |

| Input Current                        | -                                |

| Input Current                        |                                  |

| A <sub>IN</sub>                      |                                  |

| AV <sub>DD</sub> to DV <sub>DD</sub> |                                  |

| AGND to DGND                         |                                  |

| Digital Input Voltage to GND         | –0.3V to DV <sub>DD</sub> + 0.3V |

| Digital Output Voltage to GND        | 0.3V to DV <sub>DD</sub> + 0.3V  |

| Maximum Junction Temperature         | +150°C                           |

| Operating Temperature Range          | –40°C to +85°C                   |

| Storage Temperature Range            | –60°C to +150°C                  |

| Lead Temperature (soldering, 10s)    | +300°C                           |

NOTE: (1) Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

#### PACKAGE/ORDERING INFORMATION<sup>(1)</sup>

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|---------|--------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

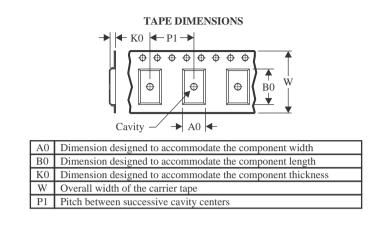

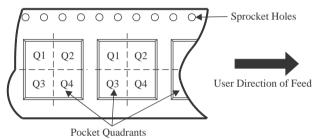

| ADS1217 | TQFP-48      | PFB                   | –40°C to +85°C                    | ADS1217            | ADS1217IPFBT       | Tape and Reel, 250           |

| "       | "            | "                     | "                                 | "                  | ADS1217IPFBR       | Tape and Reel, 2000          |

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet, or see the TI website at www.ti.com.

# ELECTRICAL CHARACTERISTICS: $AV_{DD} = 5V$

All specifications at -40°C to +85°C,  $AV_{DD}$  = +5V,  $DV_{DD}$  = +2.7V to 5.25V,  $f_{MOD}$  = 19.2kHz, PGA = 1, Buffer ON,  $R_{DAC}$  = 150k $\Omega$ ,  $f_{DATA}$  = 10Hz, and  $V_{REF}$  = +2.5V, unless otherwise specified.

| PARAMETER                                                                 | CONDITIONS                                                | MIN         | ТҮР                      | MAX                    | UNITS                   |

|---------------------------------------------------------------------------|-----------------------------------------------------------|-------------|--------------------------|------------------------|-------------------------|

| ANALOG INPUT (A <sub>IN</sub> 0 – A <sub>IN</sub> 7, A <sub>INCOM</sub> ) |                                                           |             |                          |                        |                         |

| Full-Scale Input Voltage                                                  | $(A_{IN+}) - (A_{IN-})$                                   |             | ±2V <sub>REF</sub> /PGA  |                        | V                       |

| Analog Input Voltage                                                      | Buffer OFF                                                | AGND – 0.1  |                          | AV <sub>DD</sub> + 0.1 | V                       |

|                                                                           | Buffer ON                                                 | AGND + 0.05 |                          | AV <sub>DD</sub> – 1.5 | V                       |

| Differential Input Impedance                                              | Buffer OFF                                                |             | 10/PGA                   |                        | MΩ                      |

| Input Current                                                             | Buffer ON                                                 |             | 0.5                      |                        | nA                      |

| Bandwidth                                                                 |                                                           |             |                          |                        |                         |

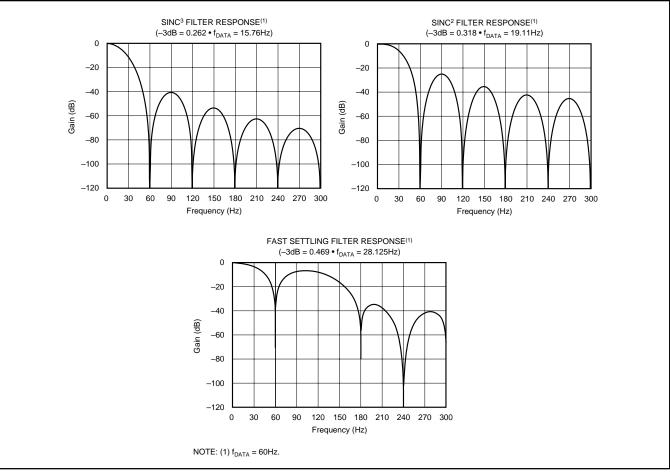

| Fast Settling Filter                                                      | –3dB                                                      |             | 0.469f <sub>DATA</sub>   |                        | Hz                      |

| Sinc <sup>2</sup> Filter                                                  | –3dB                                                      |             | 0.318f <sub>DATA</sub>   |                        | Hz                      |

| Sinc <sup>3</sup> Filter                                                  | –3dB                                                      |             | 0.262f <sub>DATA</sub>   |                        | Hz                      |

| Programmable Gain Amplifier                                               | User Selectable Gain Ranges                               | 1           |                          | 128                    |                         |

| Burnout Current Sources                                                   |                                                           |             | 2                        |                        | μΑ                      |

| OFFSET DAC                                                                |                                                           |             |                          |                        |                         |

| Offset DAC Range                                                          |                                                           |             | ±V <sub>REF</sub> /(PGA) |                        | V                       |

| Offset DAC Monotonicity                                                   |                                                           | 8           |                          |                        | Bits                    |

| Offset DAC Gain Error                                                     |                                                           |             | ±1                       |                        | %                       |

| Offset DAC Gain Error Drift                                               |                                                           |             | 1                        |                        | ppm/°C                  |

| SYSTEM PERFORMANCE                                                        |                                                           |             |                          |                        |                         |

| Resolution                                                                |                                                           | 24          |                          |                        | Bits                    |

| No Missing Codes                                                          | Sinc <sup>3</sup> Filter                                  |             |                          | 24                     | Bits                    |

| Integral Nonlinearity                                                     | End Point Fit, Differential Input,<br>Buffer Off          |             | 0.0003                   | 0.0012                 | % of FSR <sup>(1)</sup> |

| Offset Error                                                              | Before Calibration                                        |             | 7.5                      |                        | ppm of FSR              |

| Offset Drift                                                              |                                                           |             | 0.02                     |                        | ppm of FSR/°C           |

| Gain Error                                                                | After Calibration                                         |             | 0.005                    |                        | %                       |

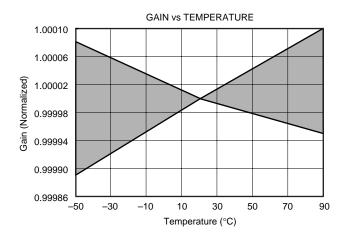

| Gain Error Drift                                                          |                                                           |             | 0.5                      |                        | ppm/°C                  |

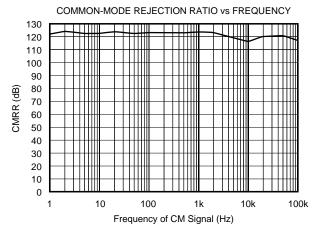

| Common-Mode Rejection                                                     | at DC                                                     | 100         |                          |                        | dB                      |

|                                                                           | $f_{CM} = 60Hz, f_{DATA} = 10Hz$                          |             | 130                      |                        | dB                      |

|                                                                           | $f_{CM} = 50Hz, f_{DATA} = 50Hz$                          |             | 120                      |                        | dB                      |

|                                                                           | $f_{CM} = 60Hz, f_{DATA} = 60Hz$                          |             | 120                      |                        | dB                      |

| Normal-Mode Rejection                                                     | $f_{SIG} = 50Hz, f_{DATA} = 50Hz$                         |             | 100                      |                        | dB                      |

|                                                                           | $f_{SIG} = 60Hz, f_{DATA} = 60Hz$                         |             | 100                      |                        | dB                      |

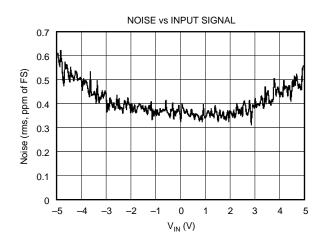

| Output Noise                                                              |                                                           |             | Typical Character        | istics                 |                         |

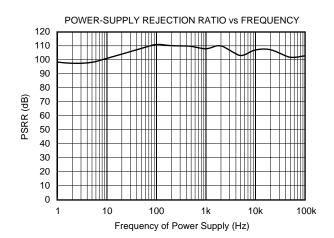

| Power-Supply Rejection                                                    | at DC, dB = $-20\log(\Delta V_{OUT}/\Delta V_{DD})^{(2)}$ | 80          | 95                       |                        | dB                      |

NOTES: (1) FSR is Full-Scale Range. (2)  $\Delta V_{OUT}$  is change in digital result. (3) 12pF switched capacitor at f<sub>SAMP</sub> clock frequency.

2

# ELECTRICAL CHARACTERISTICS: AV<sub>DD</sub> = 5V (Cont.)

All specifications at -40°C to +85°C,  $AV_{DD}$  = +5V,  $DV_{DD}$  = +2.7V to 5.25V,  $f_{MOD}$  = 19.2kHz, PGA = 1, Buffer ON,  $R_{DAC}$  = 150k $\Omega$ ,  $f_{DATA}$  = 10Hz, and  $V_{REF}$  = +2.5V, unless otherwise specified.

| PARAMETER                                                                                                                                                                   | CONDITIONS                                                                                                                                                                | MIN                                             | ТҮР                                                | MAX                                                         | UNITS                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------|-------------------------------------|

| <b>VOLTAGE REFERENCE INPUT</b><br>Reference Input ( $V_{REF}$ )<br>Negative Reference Input ( $V_{REF-}$ )<br>Positive Reference Input ( $V_{REF+}$ )                       | $V_{REF} \equiv (V_{REF*}) - (V_{REF*})$                                                                                                                                  | 0.1<br>AGND – 0.1<br>(V <sub>REF–</sub> ) + 0.1 | 2.5                                                | 2.6<br>(V <sub>REF+</sub> ) - 0.1<br>AV <sub>DD</sub> + 0.1 | V<br>V<br>V                         |

| Common-Mode Rejection<br>Common-Mode Rejection<br>Bias Current <sup>(3)</sup>                                                                                               | at DC<br>$f_{VREFCM} = 60Hz$ , $f_{DATA} = 60Hz$<br>$V_{REF} = 2.5V$ , PGA = 1                                                                                            | (TREF-) - OII                                   | 120<br>120<br>1.3                                  |                                                             | dB<br>dB<br>μA                      |

| ON-CHIP VOLTAGE REFERENCE<br>Output Voltage                                                                                                                                 | REF HI = 1<br>REF HI = 0                                                                                                                                                  | 2.4                                             | 2.5<br>1.25                                        | 2.6                                                         | V<br>V                              |

| Short-Circuit Current Source<br>Short-Circuit Current Sink<br>Drift                                                                                                         |                                                                                                                                                                           |                                                 | 8<br>50<br>15                                      |                                                             | mA<br>μA<br>ppm/°C                  |

| Noise<br>Output Impedance<br>Startup Time                                                                                                                                   | V <sub>RCAP</sub> = 0.1µF, BW = 0.1Hz to 100Hz<br>Sourcing 100µA                                                                                                          |                                                 | 10<br>3<br>5                                       |                                                             | μVrms<br>Ω<br>ms                    |

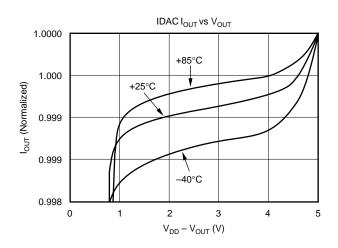

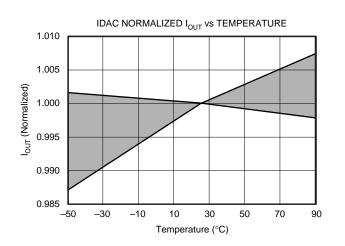

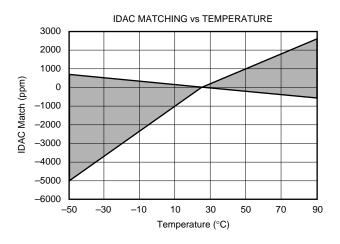

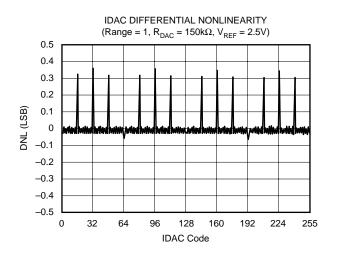

| IDAC<br>Full-Scale Output Current                                                                                                                                           | $R_{DAC}$ = 150kΩ, Range = 1<br>$R_{DAC}$ = 150kΩ, Range = 2<br>$R_{DAC}$ = 150kΩ, Range = 3<br>$R_{DAC}$ = 15kΩ, Range = 3                                               |                                                 | 0.5<br>1<br>2<br>20                                |                                                             | mA<br>mA<br>mA                      |

| Current Setting Resistance (R <sub>DAC</sub> )<br>Monotonicity<br>Compliance Voltage                                                                                        | $R_{DAC} = 150k\Omega$                                                                                                                                                    | 10<br>8<br>0                                    |                                                    | AV <sub>DD</sub> – 1                                        | kΩ<br>Bits<br>V                     |

| Output Impedance<br>PSRR<br>Gain Error<br>Gain Error Drift<br>Gain Error Mismatch<br>Gain Error Mismatch Drift                                                              | V <sub>OUT</sub> = AV <sub>DD</sub> /2, Code > 16<br>Individual IDAC<br>Individual IDAC<br>Between IDACs, Same Range and Code<br>Between IDACs, Same Range and Code       | •                                               | Typical Characteri<br>400<br>5<br>75<br>0.25<br>15 |                                                             | ppm/V<br>%<br>ppm/°C<br>%<br>ppm/°C |

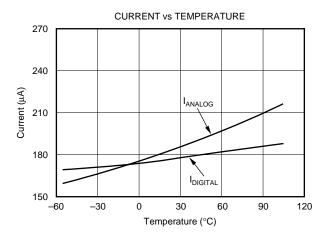

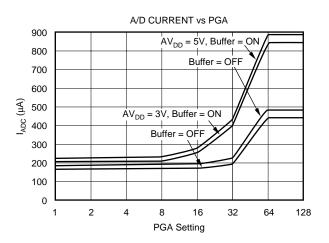

| POWER-SUPPLY REQUIREMENTS<br>Power-Supply Voltage<br>Analog Current (I <sub>ADC</sub> + I <sub>VREF</sub> + I <sub>IDAC)</sub><br>A/D Converter Current (I <sub>ADC</sub> ) | $\begin{array}{l} AV_{DD} \\ \hline PDWN = 0, \text{ or SLEEP} \\ PGA = 1, Buffer OFF \\ PGA = 128, Buffer OFF \\ PGA = 1, Buffer ON \\ PGA = 128, Buffer ON \end{array}$ | 4.75                                            | 1<br>175<br>500<br>250<br>900                      | 5.25<br>275<br>750<br>350<br>1375                           | V<br>nA<br>μA<br>μA<br>μA           |

| V <sub>REF</sub> Current (I <sub>VREF</sub> )<br>I <sub>IDAC</sub> Current (I <sub>IDAC</sub> )                                                                             | Excludes Load Current                                                                                                                                                     |                                                 | 250<br>480                                         | 375<br>675                                                  | μΑ<br>μΑ                            |

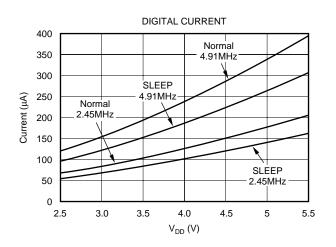

| Digital Current                                                                                                                                                             | Normal Mode, $DV_{DD} = 5V$<br>SLEEP Mode, $DV_{DD} = 5V$<br>Read Data Continuous Mode, $DV_{DD} = 5V$<br>$\overline{PDWN} = 0$                                           |                                                 | 180<br>150<br>230<br>1                             | 275                                                         | μΑ<br>μΑ<br>μΑ<br>nA                |

| Power Dissipation                                                                                                                                                           | PGA = 1, Buffer OFF, REFEN = 0,<br>IDACs OFF, DV <sub>DD</sub> = 5V                                                                                                       |                                                 | 1.8                                                | 2.8                                                         | mW                                  |

NOTES: (1) FSR is Full-Scale Range. (2)  $\Delta V_{OUT}$  is change in digital result. (3) 12pF switched capacitor at f<sub>SAMP</sub> clock frequency.

Downloaded from Arrow.com.

# ELECTRICAL CHARACTERISTICS: $AV_{DD} = 3V$

All specifications at -40°C to +85°C,  $AV_{DD}$  = +3V,  $DV_{DD}$  = +2.7V to 5.25V,  $f_{MOD}$  = 19.2kHz, PGA = 1, Buffer ON,  $R_{DAC}$  = 75k $\Omega$ ,  $f_{DATA}$  = 10Hz, and  $V_{REF}$  = +1.25V, unless otherwise specified.

|                                                                                                                                                                                                                                                  |                                                                                                                                                                     |                                                 | ADS1217                                                                    |                                                             |                                         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------|--|

| PARAMETER                                                                                                                                                                                                                                        | CONDITIONS                                                                                                                                                          | MIN                                             | ТҮР                                                                        | MAX                                                         | UNITS                                   |  |

| ANALOG INPUT (A <sub>IN</sub> 0 – A <sub>IN</sub> 7, A <sub>INCOM</sub> )<br>Full-Scale Input Voltage<br>Analog Input Range                                                                                                                      | (A <sub>IN+</sub> ) − (A <sub>IN−</sub> )<br>Buffer OFF<br>Buffer ON                                                                                                | AGND – 0.1<br>AGND + 0.05                       | ±2V <sub>REF</sub> /PGA                                                    | AV <sub>DD</sub> + 0.1<br>AV <sub>DD</sub> – 1.5            | V<br>V<br>V                             |  |

| Input Impedance<br>Input Current<br>Bandwidth                                                                                                                                                                                                    | Buffer OFF<br>Buffer ON                                                                                                                                             |                                                 | 10/PGA<br>0.5                                                              |                                                             | MΩ<br>nA                                |  |

| Fast Settling Filter<br>Sinc <sup>2</sup> Filter<br>Sinc <sup>3</sup> Filter<br>Programmable Gain Amplifier                                                                                                                                      | -3dB<br>-3dB<br>-3dB<br>User Selectable Gain Ranges                                                                                                                 | 1                                               | 0.469f <sub>DATA</sub><br>0.318f <sub>DATA</sub><br>0.262f <sub>DATA</sub> | 128                                                         | Hz<br>Hz<br>Hz                          |  |

| Burnout Current Sources                                                                                                                                                                                                                          |                                                                                                                                                                     |                                                 | 2                                                                          | 120                                                         | μΑ                                      |  |

| OFFSET DAC<br>Offset DAC Range<br>Offset DAC Monotonicity<br>Offset DAC Gain Error<br>Offset DAC Gain Error Drift                                                                                                                                |                                                                                                                                                                     | 8                                               | ±V <sub>REF</sub> /(PGA)<br>±1<br>2                                        |                                                             | ∨<br>Bits<br>%<br>ppm/°C                |  |

| SYSTEM PERFORMANCE                                                                                                                                                                                                                               |                                                                                                                                                                     |                                                 |                                                                            |                                                             |                                         |  |

| Resolution<br>No Missing Codes<br>Integral Nonlinearity                                                                                                                                                                                          | Sinc <sup>3</sup> Filter<br>End Point Fit, Differential Input,<br>Buffer Off, T = 25°C                                                                              | 24                                              | 0.0003                                                                     | 24<br>0.0012                                                | Bits<br>Bits<br>% of FSR <sup>(1)</sup> |  |

| Offset Error<br>Offset Drift<br>Gain Error                                                                                                                                                                                                       | Before Calibration<br>After Calibration                                                                                                                             |                                                 | 15<br>0.04<br>0.010                                                        |                                                             | ppm of FSR<br>ppm of FSR/°<br>%         |  |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                            |                                                                                                                                                                     | 100                                             | 1.0<br>130<br>120<br>120                                                   |                                                             | ppm/⁰C<br>dB<br>dB<br>dB<br>dB          |  |

| Normal-Mode Rejection<br>Output Noise                                                                                                                                                                                                            | $f_{SIG} = 50Hz$ , $f_{DATA} = 50Hz$<br>$f_{SIG} = 60Hz$ , $f_{DATA} = 60Hz$                                                                                        | See                                             | 100<br>100<br>Typical Characteri                                           | istics                                                      | dB<br>dB                                |  |

| Power-Supply Rejection                                                                                                                                                                                                                           | at DC, dB = -20 log( $\Delta V_{OUT} / \Delta V_{DD}$ ) <sup>(2)</sup>                                                                                              | 75                                              | 90                                                                         |                                                             | dB                                      |  |

| VOLTAGE REFERENCE INPUT<br>Reference Input (V <sub>REF</sub> )<br>Negative Reference Input (V <sub>REF</sub> )<br>Positive Reference Input (V <sub>REF+</sub> )<br>Common-Mode Rejection<br>Common-Mode Rejection<br>Bias Current <sup>(3)</sup> | $V_{REF} \equiv (V_{REF+}) - (V_{REF-})$<br>at DC<br>$f_{VREFCM} = 60Hz, f_{DATA} = 60Hz$<br>$V_{REF} = 1.25V$                                                      | 0.1<br>AGND – 0.1<br>(V <sub>REF-</sub> ) + 0.1 | 1.25<br>120<br>120<br>0.65                                                 | 1.3<br>(V <sub>REF+</sub> ) – 0.1<br>AV <sub>DD</sub> + 0.1 | V<br>V<br>dB<br>dB<br>μA                |  |

| ON-CHIP VOLTAGE REFERENCE<br>Output Voltage<br>Short-Circuit Current Source                                                                                                                                                                      | REF HI = 0                                                                                                                                                          | 1.2                                             | 1.25<br>3                                                                  | 1.3                                                         | V<br>mA                                 |  |

| Short-Circuit Current Sink<br>Drift<br>Noise<br>Output Impedance<br>Startup Time                                                                                                                                                                 | $V_{RCAP} = 0.1\mu$ F, BW = 0.1Hz to 100Hz<br>Sourcing 100 $\mu$ A                                                                                                  |                                                 | 50<br>15<br>10<br>3<br>5                                                   |                                                             | µA<br>ppm/°C<br>µVrms<br>Ω<br>ms        |  |

| IDAC<br>Full-Scale Output Current                                                                                                                                                                                                                | $\begin{array}{l} R_{DAC}=75k\Omega,\ Range=1\\ R_{DAC}=75k\Omega,\ Range=2\\ R_{DAC}=75k\Omega,\ Range=3\\ R_{DAC}=15k\Omega,\ Range=3\\ \end{array}$              |                                                 | 0.5<br>1<br>2<br>20                                                        |                                                             | mA<br>mA<br>mA                          |  |

| Current Setting Resistance (R <sub>DAC</sub> )<br>Monotonicity<br>Compliance Voltage<br>Output Impedance                                                                                                                                         | $R_{DAC} = 75k\Omega$                                                                                                                                               | 10<br>8<br>0<br>See                             | Typical Character                                                          | AV <sub>DD</sub> - 1                                        | kΩ<br>Bits<br>V                         |  |

| PSRR<br>Gain Error<br>Gain Error Drift<br>Gain Error Mismatch<br>Gain Error Mismatch Drift                                                                                                                                                       | V <sub>OUT</sub> = AV <sub>DD</sub> /2, Code > 16<br>Individual IDAC<br>Individual IDAC<br>Between IDACs, Same Range and Code<br>Between IDACs, Same Range and Code |                                                 | 600<br>5<br>75<br>0.25<br>15                                               |                                                             | ppm/V<br>%<br>ppm/°C<br>%<br>ppm/°C     |  |

NOTES: (1) FSR is Full-Scale Range. (2)  $\Delta V_{OUT}$  is change in digital result. (3) 12pF switched capacitor at f<sub>SAMP</sub> clock frequency.

# ELECTRICAL CHARACTERISTICS: AV<sub>DD</sub> = 3V (Cont.)

All specifications at -40°C to +85°C,  $AV_{DD}$  = +3V,  $DV_{DD}$  = +2.7V to 5.25V,  $f_{MOD}$  = 19.2kHz, PGA = 1, Buffer ON,  $R_{DAC}$  = 75k $\Omega$ ,  $f_{DATA}$  = 10Hz, and  $V_{REF}$  = +1.25V, unless otherwise specified.

| PARAMETER                                                                  | CONDITIONS                                                          | MIN | ТҮР | МАХ  | UNITS |

|----------------------------------------------------------------------------|---------------------------------------------------------------------|-----|-----|------|-------|

| POWER-SUPPLY REQUIREMENTS                                                  |                                                                     |     |     |      |       |

| Power-Supply Voltage                                                       | AV <sub>DD</sub>                                                    | 2.7 |     | 3.3  | V     |

| Analog Current (I <sub>ADC</sub> + I <sub>VREF</sub> + I <sub>IDAC</sub> ) | $\overline{\text{PDWN}} = 0$ , or SLEEP                             |     | 1   |      | nA    |

| A/D Converter Current (I <sub>ADC</sub> )                                  | PGA = 1, Buffer OFF                                                 |     | 160 | 250  | μA    |

|                                                                            | PGA = 128, Buffer OFF                                               |     | 450 | 700  | μA    |

|                                                                            | PGA = 1, Buffer ON                                                  |     | 230 | 325  | μA    |

|                                                                            | PGA = 128, Buffer ON                                                |     | 850 | 1325 | μA    |

| V <sub>REF</sub> Current (I <sub>VREF</sub> )                              |                                                                     |     | 250 | 375  | μA    |

| I <sub>IDAC</sub> Current (I <sub>IDAC</sub> )                             | Excludes Load Current                                               |     | 480 | 675  | μΑ    |

| Digital Current                                                            | Normal Mode, DV <sub>DD</sub> = 3V                                  |     | 90  | 200  | μA    |

|                                                                            | SLEEP Mode, DV <sub>DD</sub> = 3V                                   |     | 75  |      | μA    |

|                                                                            | Read Data Continuous Mode, DV <sub>DD</sub> = 3V                    |     | 113 |      | μA    |

|                                                                            | $\overline{PDWN} = 0$                                               |     | 1   |      | nA    |

| Power Dissipation                                                          | PGA = 1, Buffer OFF, REFEN = 0,<br>IDACs OFF, DV <sub>DD</sub> = 3V |     | 0.8 | 1.4  | mW    |

NOTES: (1) FSR is Full-Scale Range. (2)  $\Delta V_{OUT}$  is change in digital result. (3) 12pF switched capacitor at f<sub>SAMP</sub> clock frequency.

# **ELECTRICAL CHARACTERISTICS: Digital**

All specifications at –40°C to +85°C, and  $\text{DV}_{\text{DD}}$  = +2.7V to 5.25V.

| PARAMETER                                         | CONDITIONS            | MIN                    | ТҮР | MAX                  | UNITS |

|---------------------------------------------------|-----------------------|------------------------|-----|----------------------|-------|

| INPUT/OUTPUT                                      |                       |                        |     |                      |       |

| Logic Level                                       |                       |                        |     |                      |       |

| V <sub>IH</sub>                                   |                       | $0.8 	imes DV_{DD}$    |     | DV <sub>DD</sub>     | V     |

| V <sub>IH</sub><br>V <sub>IL</sub> <sup>(1)</sup> |                       | DGND                   |     | $0.2 \times DV_{DD}$ | V     |

| V <sub>OH</sub>                                   | I <sub>OH</sub> = 1mA | DV <sub>DD</sub> - 0.4 |     |                      | V     |

| V <sub>OL</sub>                                   | $I_{OL} = 1mA$        | DGND                   |     | DGND + 0.4           | V     |

| Input Leakage: I <sub>IN</sub>                    | $0 < V_{I} < DV_{DD}$ | -10                    |     | 10                   | μΑ    |

| CLOCK RATES                                       |                       |                        |     |                      |       |

| Master Clock Rate: fosc                           |                       | 1                      |     | 8                    | MHz   |

| Master Clock Period: t <sub>OSC</sub>             | 1/f <sub>OSC</sub>    | 125                    |     | 1000                 | ns    |

NOTE: (1) Maximum  $V_{\rm IL}$  for  $X_{\rm IN}$  is DGND + 0.05V.

Downloaded from Arrow.com.

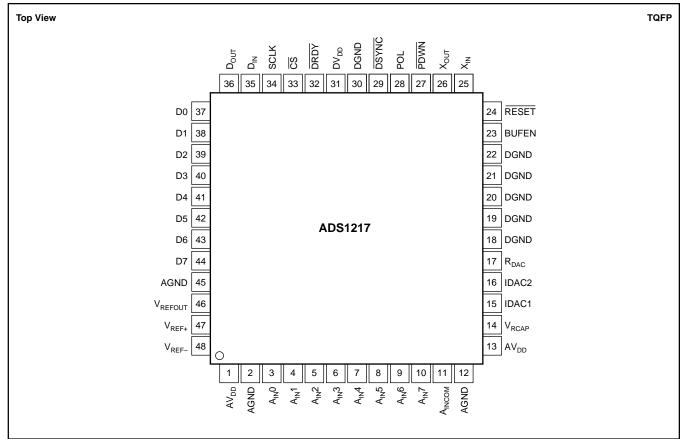

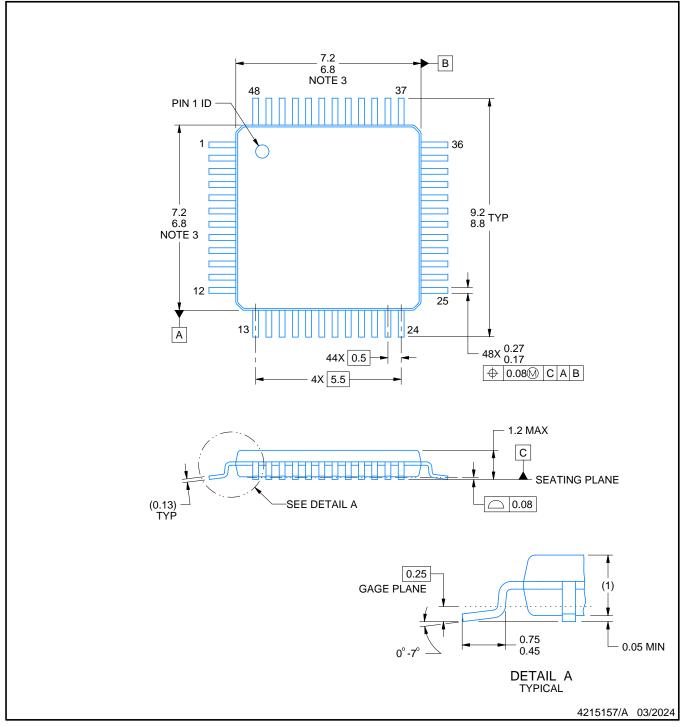

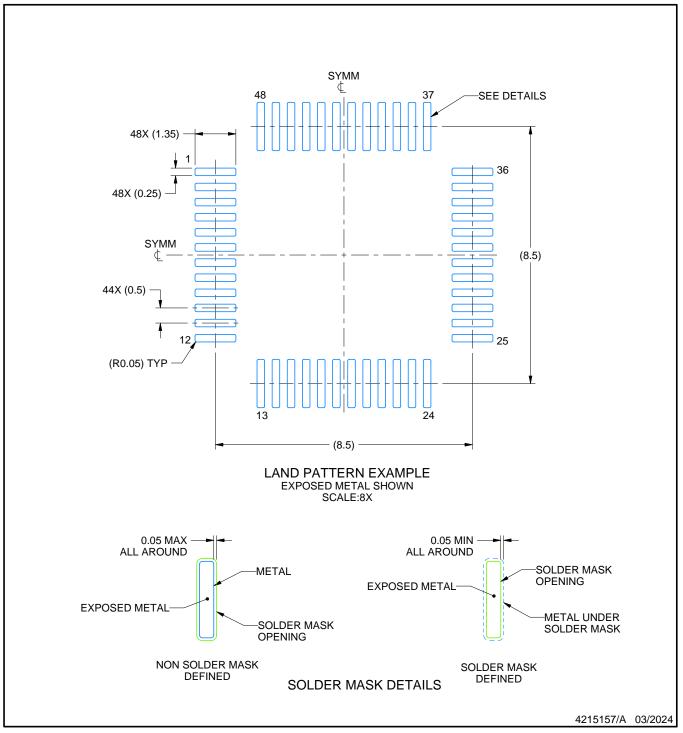

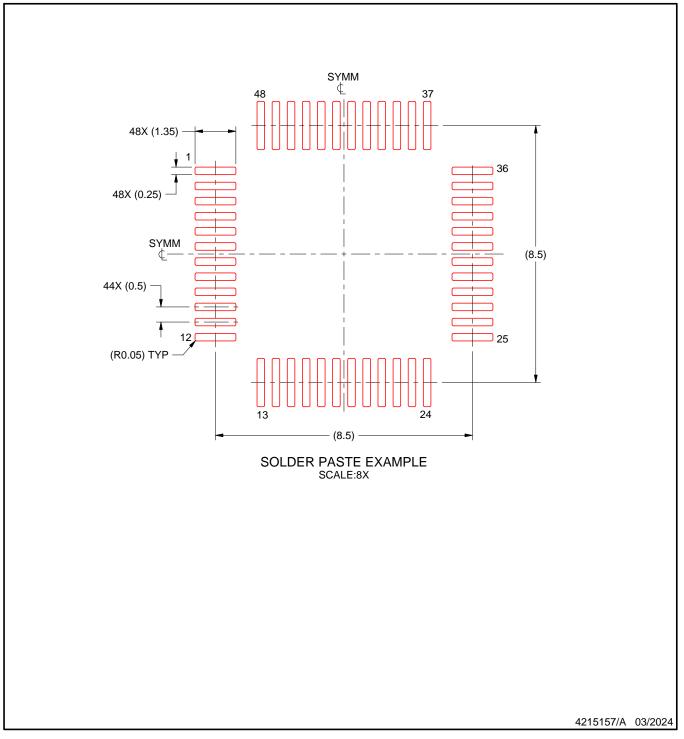

#### **PIN CONFIGURATION**

#### **PIN DESCRIPTIONS**

| PIN<br>NUMBER | NAME               | DESCRIPTION                          | PIN<br>NUMBER | NAME                | DESCRIPTION                                   |

|---------------|--------------------|--------------------------------------|---------------|---------------------|-----------------------------------------------|

| 1             | AV <sub>DD</sub>   | Analog Power Supply                  | 25            | X <sub>IN</sub>     | Clock Input                                   |

| 2             | AGND               | Analog Ground                        | 26            | X <sub>OUT</sub>    | Clock Output, used with crystal or resonator. |

| 3             | A <sub>IN</sub> 0  | Analog Input 0                       | 27            | PDWN                | Active LOW. Power Down. The power-down        |

| 4             | A <sub>IN</sub> 1  | Analog Input 1                       |               |                     | function shuts down the analog and digital    |

| 5             | A <sub>IN</sub> 2  | Analog Input 2                       |               |                     | circuits.                                     |

| 6             | A <sub>IN</sub> 3  | Analog Input 3                       | 28            | POL                 | Serial Clock Polarity Input                   |

| 7             | A <sub>IN</sub> 4  | Analog Input 4                       | 29            | DSYNC               | Active LOW, Synchronization Control Input     |

| 8             | A <sub>IN</sub> 5  | Analog Input 5                       | 30            | DGND                | Digital Ground                                |

| 9             | A <sub>IN</sub> 6  | Analog Input 6                       | 31            | DV <sub>DD</sub>    | Digital Power Supply                          |

| 10            |                    | Analog Input 7                       | 32            | DRDY                | Active LOW, Data Ready Output                 |

| 10            | A <sub>IN</sub> 7  |                                      | 33            | CS                  | Active LOW, Chip Select Input                 |

| 12            | A <sub>INCOM</sub> | Analog Input Common                  | 34            | SCLK                | Serial Clock, Schmitt Trigger                 |

|               | AGND               | Analog Ground                        | 35            | D <sub>IN</sub>     | Serial Data Input, Schmitt Trigger            |

| 13            | AV <sub>DD</sub>   | Analog Power Supply                  | 36            | D <sub>OUT</sub>    | Serial Data Output                            |

| 14            | V <sub>RCAP</sub>  | V <sub>REFOUT</sub> Bypass Capacitor | 37-44         | D0-D7               | Digital I/O 0-7                               |

| 15            | IDAC1              | Current DAC1 Output                  | 45            | AGND                | Analog Ground                                 |

| 16            | IDAC2              | Current DAC2 Output                  | 46            | -                   | Voltage Reference Output                      |

| 17            | R <sub>DAC</sub>   | Current DAC Resistor                 | -             | V <sub>REFOUT</sub> | •                                             |

| 18-22         | DGND               | Digital Ground                       | 47            | V <sub>REF+</sub>   | Positive Differential Reference Input         |

| 23            | BUFEN              | Buffer Enable Input                  | 48            | V <sub>REF-</sub>   | Negative Differential Reference Input         |

| 24            | RESET              | Active LOW, resets the entire chip.  |               |                     |                                               |

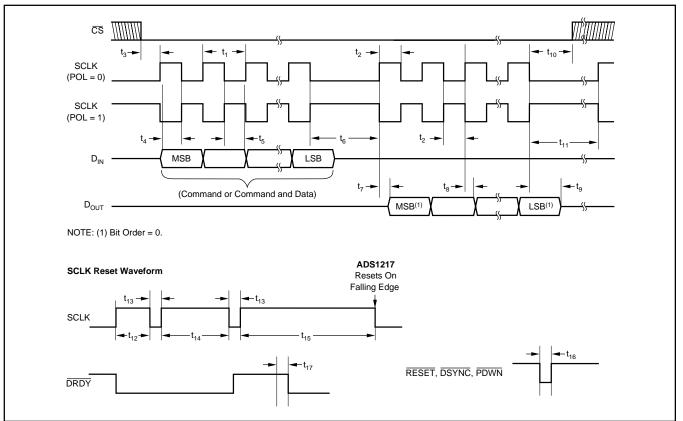

#### **TIMING DIAGRAMS**

#### **TIMING CHARACTERISTICS**

| SPEC               | DESCRIPTION                                                                                                                                                        | MIN      | МАХ  | UNITS                                    |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|------------------------------------------|

| t <sub>1</sub>     | SCLK Period                                                                                                                                                        | 4        | 3    | t <sub>OSC</sub> Periods<br>DRDY Periods |

| t <sub>2</sub>     | SCLK Pulse Width, HIGH and LOW                                                                                                                                     | 200      |      | ns                                       |

| t <sub>3</sub>     | CS LOW to First SCLK Edge; Setup Time <sup>(1)</sup>                                                                                                               | 0        |      | ns                                       |

| t <sub>4</sub>     | D <sub>IN</sub> Valid to SCLK Edge; Setup Time                                                                                                                     | 50       |      | ns                                       |

| t <sub>5</sub>     | Valid D <sub>IN</sub> to SCLK Edge; Hold Time                                                                                                                      | 50       |      | ns                                       |

| t <sub>6</sub>     | Delay Between Last SCLK Edge for $D_{\text{IN}}$ and First SCLK Edge for $D_{\text{OUT}}$ :                                                                        |          |      |                                          |

|                    | RDATA, RDATAC, RREG, WREG, RRAM, WRAM                                                                                                                              | 50       |      | t <sub>OSC</sub> Periods                 |

|                    | CSREG, CSRAMX, CSRAM                                                                                                                                               | 200      |      | t <sub>OSC</sub> Periods                 |

|                    | CSARAM, CSARAMX                                                                                                                                                    | 1100     |      | t <sub>OSC</sub> Periods                 |

| t <sub>7</sub> (2) | SCLK Edge to Valid New D <sub>OUT</sub>                                                                                                                            |          | 50   | ns                                       |

| t <sub>8</sub> (2) | SCLK Edge to D <sub>OUT</sub> , Hold Time                                                                                                                          | 0        |      | ns                                       |

| t <sub>9</sub>     | Last SCLK Edge to $D_{OUT}$ Tri-State<br>NOTE: $D_{OUT}$ goes tri-state immediately when $\overline{CS}$ goes HIGH.                                                | 6        | 10   | t <sub>OSC</sub> Periods                 |

| t <sub>10</sub>    | CS LOW Time After Final SCLK Edge                                                                                                                                  | 0        |      | ns                                       |

| t <sub>11</sub>    | Final SCLK Edge of One Op Code Until First Edge SCLK<br>of Next Command:<br>RREG, WREG, RRAM, WRAM, CSRAMX, CSARAMX,<br>CSRAM, CSARAM, CSREG, DSYNC, SLEEP, RDATA, |          |      | t <sub>OSC</sub> Periods                 |

|                    | RDATAC, STOPC                                                                                                                                                      | 4        |      | t <sub>OSC</sub> Periods                 |

|                    | CREG, CRAM                                                                                                                                                         | 220      |      | t <sub>OSC</sub> Periods                 |

|                    | CREGA                                                                                                                                                              | 1600     |      | t <sub>osc</sub> Periods                 |

|                    | SELFGCAL, SELFOCAL, SYSOCAL, SYSGCAL                                                                                                                               | 7        |      | DRDY Periods                             |

|                    | SELFCAL                                                                                                                                                            | 14<br>16 |      | DRDY Periods                             |

|                    | RESET (Input pin, command, or SCLK pattern)                                                                                                                        |          | 500  | t <sub>OSC</sub> Periods                 |

| t <sub>12</sub>    |                                                                                                                                                                    | 300      | 500  | t <sub>OSC</sub> Periods                 |

| t <sub>13</sub>    |                                                                                                                                                                    | 5        |      | t <sub>OSC</sub> Periods                 |

| t <sub>14</sub>    |                                                                                                                                                                    | 550      | 750  | t <sub>OSC</sub> Periods                 |

| t <sub>15</sub>    |                                                                                                                                                                    | 1050     | 1250 | t <sub>OSC</sub> Periods                 |

| t <sub>16</sub>    | Pulse Width                                                                                                                                                        | 4        |      | t <sub>OSC</sub> Periods                 |

| t <sub>17</sub>    | Data Not Valid                                                                                                                                                     | 4        |      | t <sub>OSC</sub> Periods                 |

NOTES: (1)  $\overline{CS}$  may be tied LOW. (2) Load = 20pF.

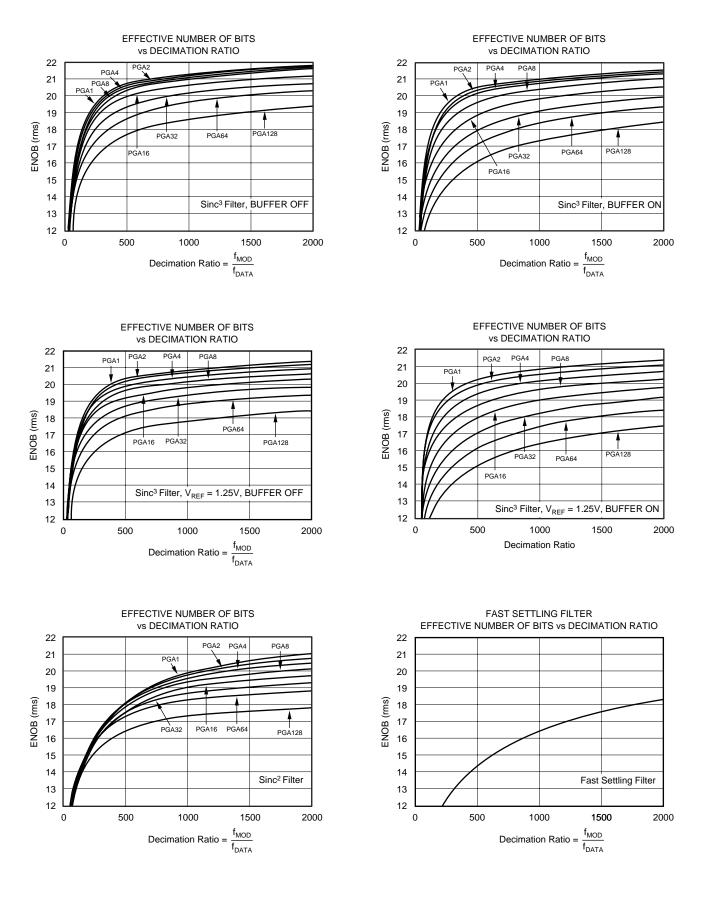

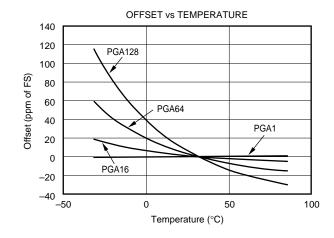

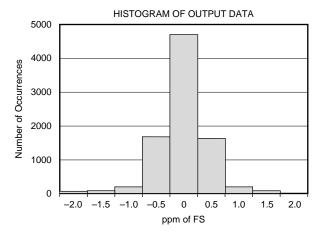

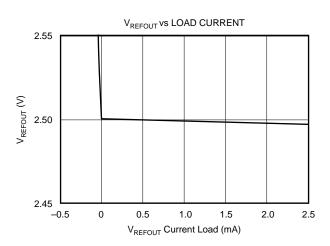

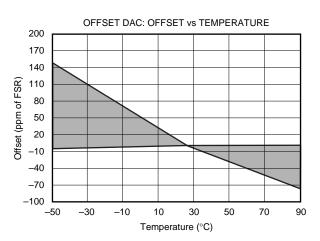

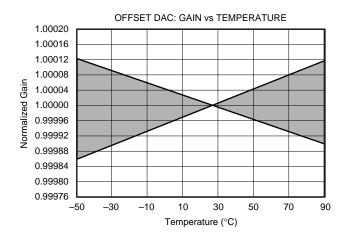

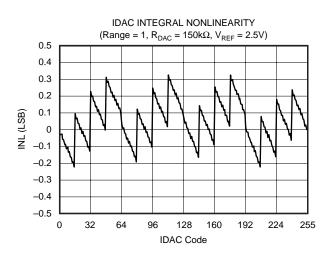

# **TYPICAL CHARACTERISTICS**

$AV_{DD} = +5V, DV_{DD} = +5V, f_{OSC} = 2.4576 MHz, PGA = 1, R_{DAC} = 150 k\Omega, f_{DATA} = 10Hz, and V_{REF} = +2.5V, unless otherwise specified.$

# **TYPICAL CHARACTERISTICS (Cont.)**

$AV_{DD}=+5V,\ DV_{DD}=+5V,\ f_{OSC}=2.4576MHz,\ PGA=1,\ R_{DAC}=150k\Omega,\ f_{DATA}=10Hz,\ and\ V_{REF}=+2.5V,\ unless otherwise specified.$

INTEGRAL NONLINEARITY vs INPUT SIGNAL 6 -40<sup>°</sup>C 4 2 INL (ppm of FS) 0 +25°C -2 -4 +85°Ċ -6 -5 -4 -3 -2 -1 0 2 3 4 5 1  $V_{\rm IN}\left(V\right)$

ADS1217 SBAS260C TEXAS INSTRUMENTS www.ti.com

# **TYPICAL CHARACTERISTICS (Cont.)**

$AV_{DD} = +5V, DV_{DD} = +5V, f_{OSC} = 2.4576 MHz, PGA = 1, R_{DAC} = 150 k\Omega, f_{DATA} = 10 Hz, and V_{REF} = +2.5V, unless otherwise specified.$

# **TYPICAL CHARACTERISTICS (Cont.)**

$AV_{DD} = +5V, DV_{DD} = +5V, f_{OSC} = 2.4576 MHz, PGA = 1, R_{DAC} = 150 k\Omega, f_{DATA} = 10Hz, and V_{REF} = +2.5V, unless otherwise specified.$

ADS1217 SBAS260C TEXAS INSTRUMENTS www.ti.com

# **OVERVIEW**

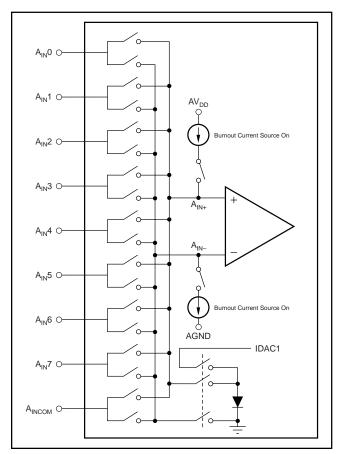

#### INPUT MULTIPLEXER

The input multiplexer (mux) provides for any combination of differential inputs to be selected on any of the input channels, as shown in Figure 1. If channel 1 is selected as the positive differential input channel, any other channel can be selected as the negative differential input channel. With this method, it is possible to have up to eight fully differential input channels.

In addition, current sources are supplied that will source or sink current to detect open or short circuits on the pins.

FIGURE 1. Input Multiplexer Configuration.

#### **TEMPERATURE SENSOR**

An on-chip diode provides temperature sensing capability. When the configuration register for the input MUX is set to all 1s, the diode is connected to the input of the A/D converter. All other channels are open. The anode of the diode is connected to the positive input of the A/D converter, and the cathode of the diode is connected to negative input of the A/D converter. The output of IDAC1 is connected to the anode to bias the diode and the cathode of the diode is also connected to ground to complete the circuit.

In this mode, the output of IDAC1 is also connected to the output pin, so some current may flow into an external load from IDAC1, rather than the diode. See Application Report *Measuring Temperature with the ADS1216, ADS1217, or ADS1218* (SBAA073) for more information.

#### **BURNOUT CURRENT SOURCES**

When the Burnout bit is set in the ACR configuration register, two current sources are enabled. The current source on the positive input channel sources approximately  $2\mu$ A of current. The current source on the negative input channel sinks approximately  $2\mu$ A. This allows for the detection of an open circuit (full-scale reading) or short circuit (0V differential reading) on the selected input differential pair.

#### **INPUT BUFFER**

The input impedance of the ADS1217 without the buffer is  $10M\Omega/PGA$ . With the buffer enabled, the input voltage range is reduced and the analog power-supply current is higher. The buffer is controlled by ANDing the state of the buffer pin with the state of the BUFFER bit in the ACR register. See Application Report *Input Currents for High-Resolution ADCs* (SBAA090) for more information.

#### **IDAC1 AND IDAC2**

The ADS1217 has two 8-bit current output DACs that can be controlled independently. The output current is set with  $R_{DAC}$ , the range select bits in the ACR register, and the 8-bit digital value in the IDAC register. The output current = ( $V_{REF}/8R_{DAC}$ ) ( $2^{RANGE-1}$ ) (DAC CODE). With  $V_{REFOUT}$  = 2.5V and  $R_{DAC}$  = 150k $\Omega$ , the full-scale output can be selected to be 0.5, 1, or 2mA. The compliance voltage range is AGND to within 1V of AV<sub>DD</sub>. When the internal voltage reference of the ADS1217 is used, it is the reference for the IDAC. An external reference may be used for the IDACs by disabling the internal reference and tying the external reference input to the  $V_{REFOUT}$  pin.

#### PGA

The PGA can be set to gains of 1, 2, 4, 8, 16, 32, 64, or 128. Using the PGA can improve the effective resolution of the A/D converter. For instance, with a PGA of 1 on a 10V full-scale range, the A/D converter can resolve to  $2\mu$ V. With a PGA of 128 on a 80mV full-scale range, the A/D converter can resolve to 150nV.

#### PGA OFFSET DAC

The input to the PGA can be shifted by half the full-scale input range of the PGA by using the ODAC register. The ODAC (Offset DAC) register is an 8-bit value; the MSB is the sign and the seven LSBs provide the magnitude of the offset. Using the ODAC does not reduce the performance of the A/D converter. See Application Report *The Offset DAC* (SBAA077) for more information.

#### MODULATOR

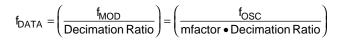

The modulator is a single-loop, 2nd-order system. The modulator runs at a clock speed ( $f_{MOD}$ ) that is derived from the external clock ( $f_{OSC}$ ). The frequency division is determined by the SPEED bit in the setup register.

| SPEED BIT | f <sub>MOD</sub>      |

|-----------|-----------------------|

| 0         | f <sub>OSC</sub> /128 |

| 1         | f <sub>OSC</sub> /256 |

#### **VOLTAGE REFERENCE INPUT**

The ADS1217 uses a differential voltage reference input. The input signal is measured against the differential voltage  $V_{REF} \equiv (V_{REF+}) - (V_{REF-})$ . For  $AV_{DD} = 5V$ ,  $V_{REF}$  is typically 2.5V. For  $AV_{DD} = 3V$ ,  $V_{REF}$  is typically 1.25V. Due to the sampling nature of the modulator, the reference input current increases with higher modulator clock frequency ( $f_{MOD}$ ) and higher PGA settings.

#### **ON-CHIP VOLTAGE REFERENCE**

A selectable voltage reference (1.25V or 2.5V) is available for supplying the voltage reference input. To use, connect V<sub>REF-</sub> to AGND and V<sub>REF+</sub> to V<sub>REFOUT</sub>. The enabling and voltage selection are controlled through bits REF EN and REF HI in the setup register. The 2.5V reference requires AV<sub>DD</sub> = 5V. When using the on-chip voltage reference, the V<sub>REFOUT</sub> pin should be bypassed with a 0.1µF capacitor to AGND.

#### V<sub>RCAP</sub> PIN

This pin provides a bypass cap for noise filtering on internal  $V_{REF}$  circuitry only. As this is a sensitive pin, place the capacitor as close as possible and avoid any resistive loading. The recommended capacitor is a  $0.001\mu$ F ceramic cap. If an external  $V_{REF}$  is used, this pin can be left unconnected.

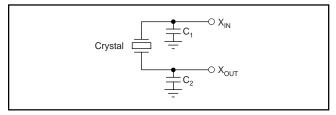

#### **CLOCK GENERATOR**

The clock source for the ADS1217 can be provided from a crystal, oscillator, or external clock. When the clock source is a crystal, external capacitors must be provided to ensure startup and a stable clock frequency; see Figure 2 and Table I.

FIGURE 2. Crystal Connection.

| CLOCK<br>SOURCE | FREQUENCY | C <sub>1</sub> | C <sub>2</sub> | PART<br>NUMBER      |

|-----------------|-----------|----------------|----------------|---------------------|

| Crystal         | 2.4576    | 0-20pF         | 0-20pF         | ECS, ECSD 2.45 - 32 |

| Crystal         | 4.9152    | 0-20pF         | 0-20pF         | ECS, ECSL 4.91      |

| Crystal         | 4.9152    | 0-20pF         | 0-20pF         | ECS, ECSD 4.91      |

| Crystal         | 4.9152    | 0-20pF         | 0-20pF         | CTS, MP 042 4M9182  |

TABLE I. Typical Clock Sources.

#### CALIBRATION

The offset and gain errors in the ADS1217, or the complete system, can be reduced with calibration. Internal calibration of the ADS1217 is called self calibration. This is handled with three commands. One command does both offset and gain calibration. There is also a gain calibration command and an offset calibration command. Each calibration process takes seven  $t_{DATA}$  periods to complete. It takes 14  $t_{DATA}$  periods to

ADS1217 SBAS260C complete both an offset and gain calibration. Self-gain calibration is optimized for PGA gains less than 8. When using higher gains, system gain calibration is recommended.

For system calibration, the appropriate signal must be applied to the inputs. The system offset command requires a "zero" differential input signal. It then computes an offset that will nullify offset in the system. The system gain command requires a positive "full-scale" differential input signal. It then computes a value to nullify gain errors in the system. Each of these calibrations will take seven  $t_{DATA}$  periods to complete.

Calibration must be performed after power on, a change in decimation ratio, or a change of the PGA. For operation with a reference voltage greater than (AV<sub>DD</sub> – 1.5V), the buffer must also be turned off during calibration.

At the completion of calibration, the DRDY signal goes LOW, which indicates the calibration is finished and valid data is available. See Application Report *Calibration Routine and Register Value Generation for the ADS121x Series* (SBAA099) for more information.

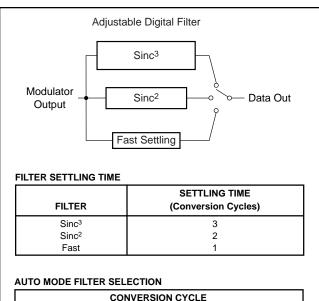

#### DIGITAL FILTER

The Digital Filter can use either the fast settling,  $sinc^2$ , or  $sinc^3$  filter, as shown in Figure 3. In addition, the Auto mode changes the sinc filter after the input channel or PGA is changed. When switching to a new channel, it will use the fast settling filter; It will then use the  $sinc^2$  followed by the  $sinc^3$  filter. This combines the low-noise advantage of the  $sinc^3$  filter with the quick response of the fast settling time filter. See Figure 4 for the frequency response of each filter.

When using the fast setting filter, select a decimation value set by the DEC0 and M/DEC1 registers that is evenly divisible by four for the best gain accuracy. For example, choose 260 rather than 261.

# 1 2 3 4+ Fast Sinc<sup>2</sup> Sinc<sup>3</sup> Sinc<sup>3</sup>

FIGURE 3. Filter Step Responses.

FIGURE 4. Filter Frequency Responses.

#### **DIGITAL I/O INTERFACE**

The ADS1217 has eight pins dedicated for digital I/O. The default power-up condition for the digital I/O pins are as inputs. All of the digital I/O pins are individually configurable as inputs or outputs. They are configured through the DIR control register. The DIR register defines whether the pin is an input or output, and the DIO register defines the state of the digital output. When the digital I/O are configured as inputs, DIO is used to read the state of the pin. If the digital I/O are not used, either 1) configure as outputs; or, 2) leave as inputs and tie to ground, this prevents excess power dissipation.

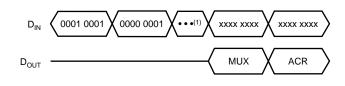

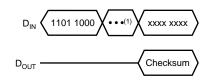

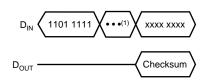

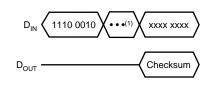

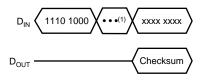

#### SERIAL PERIPHERAL INTERFACE

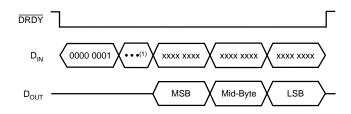

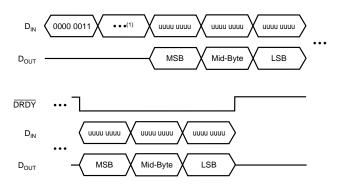

The Serial Peripheral Interface (SPI) allows a controller to communicate synchronously with the ADS1217. The ADS1217 operates in slave only mode.

#### Chip Select (CS)

The chip select  $(\overline{CS})$  input of the ADS1217 must be externally asserted before a master device can exchange data with the ADS1217.  $\overline{CS}$  must be LOW for the duration of the transaction.  $\overline{CS}$  can be tied low.

#### Serial Clock (SCLK)

SCLK, a Schmitt Trigger input, clocks data transfer on the  $D_{IN}$  input and  $D_{OUT}$  output. When transferring data to or from the ADS1217, multiple bits of data may be transferred back-to-

back with no delay in SCLKs or toggling of  $\overline{CS}$ . Make sure to avoid glitches on SCLK as they can cause extra shifting of the data.

#### Polarity (POL)

The serial clock polarity is specified by the POL input. When SCLK is active HIGH, set POL HIGH. When SCLK is active LOW, set POL LOW.

#### DATA READY

The DRDY output is used as a status signal to indicate when data is ready to be read from the ADS1217. DRDY goes LOW when new data is available. It is reset HIGH when a read operation from the data register is complete. It also goes HIGH prior to the updating of the output register to indicate when not to read from the device to ensure that a data read is not attempted while the register is being updated.

#### **DSYNC OPERATION**

DSYNC is used to provide for synchronization of the A/D conversion with an external event. Synchronization can be achieved either through the  $\overline{\text{DSYNC}}$  pin or the DSYNC command. When the  $\overline{\text{DSYNC}}$  pin is used, the filter counter is reset on the falling edge of  $\overline{\text{DSYNC}}$ . The modulator is held in reset until  $\overline{\text{DSYNC}}$  is taken HIGH. Synchronization occurs on the next rising edge of the system clock after  $\overline{\text{DSYNC}}$  is taken HIGH.

14

When the DSYNC command is sent, the filter counter is reset on the edge of the last SCLK on the DSYNC command. The modulator is held in reset until the next edge of SCLK is detected. Synchronization occurs on the next rising edge of the system clock after the first SCLK after the DSYNC command. After a DSYNC operation, DRDY is held HIGH until valid data is ready.

#### RESET

There are three methods to reset the ADS1217: the RESET input, the RESET command, and a special SCLK input pattern. When using the RESET input, take it LOW to force a reset. Make sure to follow the minimum pulse width timing specifications before taking the RESET input back high. Also, avoid glitches on the RESET input as these may cause accidental resets. The RESET command takes effect after all 8 bits have been shifted into DIN. Afterwards, the reset releases automatically. The ADS1217 can also be reset with a special pattern on SCLK, see the Timing Diagram. Reset occurs on the falling edge of the last SCLK edge in the pattern (for POL = 0). Afterwards, the reset releases automatically.

#### POWER-UP—SUPPLY VOLTAGE RAMP RATE

The power-on reset circuitry was designed to accommodate digital supply ramp rates as slow as 1V/10ms. To ensure proper operation, the power supply should ramp monotonically.

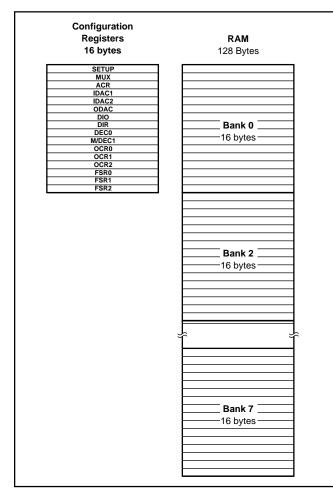

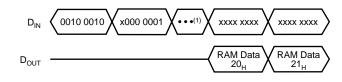

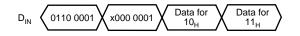

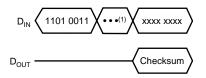

#### MEMORY

Two types of memory are used on the ADS1217: registers and RAM. 16 registers directly control the various functions (PGA, DAC value, Decimation Ratio, etc.) and can be directly read or written. Collectively, the registers contain all the information needed to configure the part, such as data format, mux settings, calibration settings, decimation ratio, etc. Additional registers, such as output data, are accessed through dedicated instructions.

#### **REGISTER BANK TOPOLOGY**

The operation of the device is set up through individual registers. The set of the 16 registers required to configure the device is referred to as a Register Bank, as shown in Figure 5.

Reads and Writes to Registers and RAM occur on a byte basis. However, copies between registers and RAM occurs on a bank basis. The RAM is independent of the Registers; that is, the RAM can be used as general-purpose RAM.

The ADS1217 supports any combination of eight analog inputs. With this flexibility, the device could easily support eight unique configurations—one per input channel. In order to facilitate this type of usage, eight separate register banks are available. Therefore, each configuration could be written once and recalled as needed without having to serially retransmit all the configuration data. Checksum commands are also included, which can be used to verify the integrity of RAM.

FIGURE 5. Memory Organization.

The RAM provides eight "banks", with a bank consisting of 16 bytes. The total size of the RAM is 128 bytes. Copies between the registers and RAM are performed on a bank basis. Also, the RAM can be directly read or written through the serial interface on power-up. The banks allow separate storage of settings for each input.

The RAM address space is linear, therefore accessing RAM is done using an auto-incrementing pointer. Access to RAM in the entire memory map can be done consecutively without having to address each bank individually. For example, if you were currently accessing bank 0 at offset  $0F_H$  (the last location of bank 0), the next access would be bank 1 and offset  $0O_H$ . Any access after bank 7 and offset  $0F_H$  will wrap around to bank 0 and Offset  $0O_H$ .

Although the Register Bank memory is linear, the concept of addressing the device can also be thought of in terms of bank and offset addressing. Looking at linear and bank addressing syntax, we have the following comparison: in the linear memory map, the address  $14_H$  is equivalent to bank 1 and offset  $04_H$ . Simply stated, the most significant four bits represent the bank, and the least significant four bits represent the offset. The offset is equivalent to the register address for that bank of memory.

## **REGISTER MAP**

| ADDRESS         | REGISTER | BIT 7   | BIT 6   | BIT 5   | BIT 4   | BIT 3    | BIT 2   | BIT 1   | BIT 0     |

|-----------------|----------|---------|---------|---------|---------|----------|---------|---------|-----------|

| 00 <sub>H</sub> | SETUP    | ID      | ID      | ID      | SPEED   | REF EN   | REF HI  | BUF EN  | BIT ORDER |

| 01 <sub>H</sub> | MUX      | PSEL3   | PSEL2   | PSEL1   | PSEL0   | NSEL3    | NSEL2   | NSEL1   | NSEL0     |

| 02 <sub>H</sub> | ACR      | BOCS    | IDAC2R1 | IDAC2R0 | IDAC1R1 | IDAC1R0  | PGA2    | PGA1    | PGA0      |

| 03 <sub>H</sub> | IDAC1    | IDAC1_7 | IDAC1_6 | IDAC1_5 | IDAC1_4 | IDAC1_3  | IDAC1_2 | IDAC1_1 | IDAC1_0   |

| 04 <sub>H</sub> | IDAC2    | IDAC2_7 | IDAC2_6 | IDAC2_5 | IDAC2_4 | IDAC2_3  | IDAC2_2 | IDAC2_1 | IDAC2_0   |

| 05 <sub>H</sub> | ODAC     | SIGN    | OSET_6  | OSET_5  | OSET_4  | OSET_3   | OSET_2  | OSET_1  | OSET_0    |

| 06 <sub>H</sub> | DIO      | DIO_7   | DIO_6   | DIO_5   | DIO_4   | DIO_3    | DIO_2   | DIO_1   | DIO_0     |

| 07 <sub>H</sub> | DIR      | DIR_7   | DIR_6   | DIR_5   | DIR_4   | DIR_3    | DIR_2   | DIR_1   | DIR_0     |

| 08 <sub>H</sub> | DEC0     | DEC07   | DEC06   | DEC05   | DEC04   | DEC03    | DEC02   | DEC01   | DEC00     |

| 09 <sub>H</sub> | M/DEC1   | DRDY    | U/B     | SMODE1  | SMODE0  | Reserved | DEC10   | DEC09   | DEC08     |

| 0A <sub>H</sub> | OCR0     | OCR07   | OCR06   | OCR05   | OCR04   | OCR03    | OCR02   | OCR01   | OCR00     |

| 0B <sub>H</sub> | OCR1     | OCR15   | OCR14   | OCR13   | OCR12   | OCR11    | OCR10   | OCR09   | OCR08     |

| 0C <sub>H</sub> | OCR2     | OCR23   | OCR22   | OCR21   | OCR20   | OCR19    | OCR18   | OCR17   | OCR16     |

| 0D <sub>H</sub> | FSR0     | FSR07   | FSR06   | FSR05   | FSR04   | FSR03    | FSR02   | FSR01   | FSR00     |

| 0E <sub>H</sub> | FSR1     | FSR15   | FSR14   | FSR13   | FSR12   | FSR11    | FSR10   | FSR09   | FSR08     |

| 0F <sub>H</sub> | FSR2     | FSR23   | FSR22   | FSR21   | FSR20   | FSR19    | FSR18   | FSR17   | FSR16     |

TABLE II. Registers.

#### **DETAILED REGISTER DEFINITIONS**

**SETUP** (Address 00<sub>H</sub>) Setup Register

Reset Value = iii01110

| _ | bit 7 | bit 6 | bit 5 | bit 4 | bit 3  | bit 2  | bit 1  | bit 0     |

|---|-------|-------|-------|-------|--------|--------|--------|-----------|

|   | ID    | ID    | ID    | SPEED | REF EN | REF HI | BUF EN | BIT ORDER |

- bit 7-5 Factory Programmed Bits

- bit 4 SPEED: Modulator Clock Speed 0 :  $f_{MOD} = f_{OSC}/128$  (default)

- $1 : f_{MOD} = f_{OSC}/256$

- bit 3 REF EN: Internal Voltage Reference Enable 0 = Internal Voltage Reference Disabled 1 = Internal Voltage Reference Enabled (default)

- bit 2 REF HI: Internal Reference Voltage Select 0 = Internal Reference Voltage = 1.25V

- 1 = Internal Reference Voltage = 2.5V (default)

- bit 1 BUF EN: Buffer Enable

- 0 = Buffer Disabled

- 1 = Buffer Enabled (default)

- bit 0 BIT ORDER: Set Order Bits are Transmitted 0 = Most Significant Bit Transmitted First (default) 1 = Least Significant Bit Transmitted First Data is always shifted into the part most significant bit first. Data is always shifted out of the part most significant byte first. This configuration bit only controls the bit order within the byte of data that is shifted out.

#### **MUX** (Address $01_{H}$ ) Multiplexer Control Register Reset Value = $01_{H}$

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PSEL3 | PSEL2 | PSEL1 | PSEL0 | NSEL3 | NSEL2 | NSEL1 | NSEL0 |

bit 7-4 PSEL3: PSEL2: PSEL1: PSEL0: Positive Channel Select

0000 = AIN0 (default)

0001 = AIN1

0010 = AIN2

0011 = AIN3

- 0100 = AIN4

- 0101 = AIN5

- 0101 = AINS0110 = AIN6

- 0110 = AIN00111 = AIN7

- 1xxx = AINCOM (except when all bits are 1s)

- 1111 Temperature Sensor Diada

- 1111 = Temperature Sensor Diode

- bit 3-0 NSEL3: NSEL2: NSEL1: NSEL0: Negative Channel Select

- 0000 = AIN0

- 0001 = AIN1 (default)

- 0010 = AIN2

- 0011 = AIN3

- 0100 = AIN4

- 0101 = AIN5

- 0110 = AIN6

- 0111 = AIN7

- 1xxx = AINCOM (except when all bits are 1s)

- 1111 = Temperature Sensor Diode

**ACR** (Address  $02_{H}$ ) Analog Control Register Reset Value =  $00_{H}$

| leset \ | /alue =                             | 00 <sub>H</sub>                                      |                                     |                |         |          |           |

|---------|-------------------------------------|------------------------------------------------------|-------------------------------------|----------------|---------|----------|-----------|

| bit 7   | bit 6                               | bit 5                                                | bit 4                               | bit 3          | bit 2   | bit 1    | bit 0     |

| BOCS    | IDAC2R1                             | IDAC2R0                                              | IDAC1R1                             | IDAC1R0        | PGA2    | PGA1     | PGA0      |

| oit 7   | 0 = D                               | S: Burno<br>isabled<br>nabled                        |                                     | rent Sou<br>t) | irce    |          |           |

| DAC C   | Current :                           | $=\left(\frac{V_{RE}}{8R_{D}}\right)$                | $\frac{F}{AC} \left( 2^{R} \right)$ | ANGE-1)(       | DAC C   | ode)     |           |

| bit 6-5 | IDAC2<br>00 = 0<br>01 = 1<br>10 = 1 |                                                      | ault)<br>1<br>2                     | : Full-S       | cale Ra | ange Se  | elect for |

| bit 4-3 | IDAC<br>00 = 0<br>01 = 1<br>10 = 1  |                                                      | ault)<br>1<br>2                     | : Full-So      | cale Ra | ange Se  | elect for |

| bit 2-0 | Gain                                | Selectic<br>1 (defa<br>2<br>4<br>8<br>16<br>32<br>64 | n                                   | : Progra       | mmable  | e Gain A | Amplifier |

#### **IDAC1** (Address $03_{H}$ ) Current DAC 1 Reset Value = $00_{H}$

| bit 7   | bit 6   | bit 5   | bit 4   | bit 3   | bit 2   | bit 1   | bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IDAC1_7 | IDAC1_6 | IDAC1_5 | IDAC1_4 | IDAC1_3 | IDAC1_2 | IDAC1_1 | IDAC1_0 |

The DAC code bits set the output of DAC1 from 0 to full-scale. The value of the full-scale current is set by this Byte,  $V_{REF}$ ,  $R_{DAC}$ , and the DAC1 range bits in the ACR register.

#### IDAC2 (Address $04_{\rm H}$ ) Current DAC 2

Reset Value =  $00_{H}$

| bit 7   | bit 6   | bit 5   | bit 4   | bit 3   | bit 2   | bit 1   | bit 0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IDAC2_7 | IDAC2_6 | IDAC2_5 | IDAC2_4 | IDAC1_3 | IDAC1_2 | IDAC1_1 | IDAC1_0 |

The DAC code bits set the output of DAC2 from 0 to full-scale. The value of the full-scale current is set by this Byte,  $V_{REF}$ ,  $R_{DAC}$ , and the DAC2 range bits in the ACR register.

**ODAC** (Address  $05_{H}$ ) Offset DAC Setting Reset Value =  $00_{H}$

| bit 7 | bit 6  | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| SIGN  | OSET6  | OSET5 | OSET4 | OSET3 | OSET2 | OSET1 | OSET0 |

| bit 7 | Offset | Sign  |       |       |       |       |       |

0 = Positive

1 = Negative

bit 6-0 Offset =

$$\frac{V_{REF}}{PGA} \cdot \left(\frac{Code}{127}\right)$$

NOTE: The offset must be used after calibration or the calibration will notify the effects.

| DIO (Ad | ddress  | 06 <sub>H</sub> ) Di | gital I/O |       |       |       |       |  |

|---------|---------|----------------------|-----------|-------|-------|-------|-------|--|

| Reset \ | /alue = | 00 <sub>H</sub>      |           |       |       |       |       |  |

| bit 7   | bit 6   | bit 5                | bit 4     | bit 3 | bit 2 | bit 1 | bit 0 |  |

| DIO7    | DIO6    | DIO5                 | DIO4      | DIO3  | DIO2  | DIO1  | DIO0  |  |

A value written to this register will appear on the digital I/O pins if the pin is configured as an output in the DIR register. Reading this register will return the value of the digital I/O pins.

| ``    | ddress (<br>/alue = | 112   | ection | control f | or digit | al I/O |       |  |

|-------|---------------------|-------|--------|-----------|----------|--------|-------|--|

| bit 7 | bit 6               | bit 5 | bit 4  | bit 3     | bit 2    | bit 1  | bit 0 |  |

| DIR7  | DIR6                | DIR5  | DIR4   | DIR3      | DIR2     | DIR1   | DIR0  |  |

Each bit controls whether the Digital I/O pin is an output (= 0) or input (= 1). The default power-up state is as inputs.

#### DEC0 (Address 08<sub>H</sub>) Decimation Register (Least Significant 8 bits)

#### Reset Value = $80_{H}$

| bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DEC07 | DEC06 | DEC05 | DEC04 | DEC03 | DEC02 | DEC01 | DEC00 |

The decimation value is defined with 11 bits for a range of 20 to 2047. This register is the least significant 8 bits. The 3 most significant bits are contained in the M/DEC1 register. The default data rate is 10Hz with a 2.4576MHz crystal.

**M/DEC1** (Address  $09_{\rm H}$ ) Mode and Decimation Register Reset Value =  $07_{\rm H}$

| bit 7 | bit 6 | bit 5  | bit 4  | bit 3    | bit 2 | bit 1 | bit 0 |

|-------|-------|--------|--------|----------|-------|-------|-------|

| DRDY  | U/B   | SMODE1 | SMODE0 | Reserved | DEC10 | DEC09 | DEC08 |

DRDY: Data Ready (Read Only) This bit duplicates the state of the DRDY pin.

bit 6 U/B: Data Format

bit 7

0 = Bipolar (default)

1 = Unipolar

| U/B | ANALOG INPUT | DIGITAL OUTPUT |

|-----|--------------|----------------|