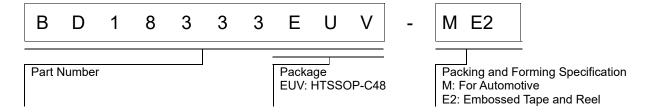

# **Automotive LED Driver Series**

# 24CH Linear LED Driver Embedded Automotive Lamps LED Driver

# **BD18333EUV-M**

# **General Description**

BD18333EUV-M is 24CH constant current driver with 8-bit PWM dimming and 8-bit local DC dimming individual channels. Communication with  $\mu$ -Controller is available via UART.

#### **Features**

- Nano Cap<sup>TM</sup> Integrated

- AEC-Q100 Qualified(Note 1)

- ISO 26262 Process Compliant to Support ASIL-B

- Integrated 24CH LED Constant Current Driver

- UART Interface

- Independent 8-bit PWM Dimming Function

- Independent 8-bit Local DC Dimming Function

- Independent 4-bit Delay Function

- LSI Protection Function (UVLO, TSD)

- LED Abnormality Detection Function (Open/Short)

- LED Cathode Short Detection Function

- Integrated Abnormality Output the FAILB Pin (Note 1) Grade 1

#### **Application**

- Rear Lamps (+ Animation)

- Position/DRL (+ Animation)

- Turn (+ Animation)

# **Key Specification**

■ Operating Input Voltage Range : 4.5 V to 40.0 V ■ LED Pin Maximum Output Current : 125 mA ■ Operating Temperature Range : -40 °C to +125 °C

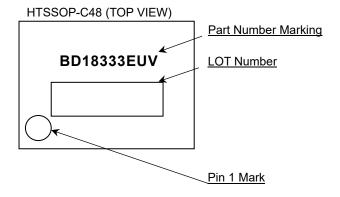

## Package HTSSOP-C48

W (Typ) x D (Typ) x H (Max) 12.5 mm x 8.1 mm x 1.0 mm

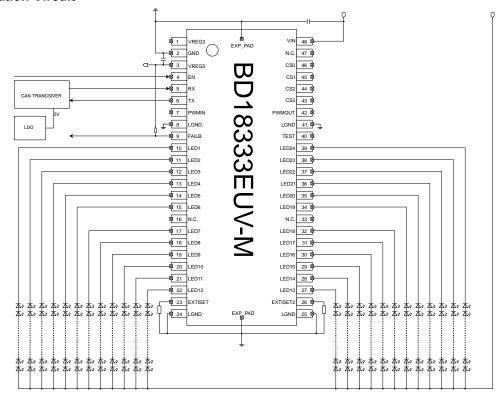

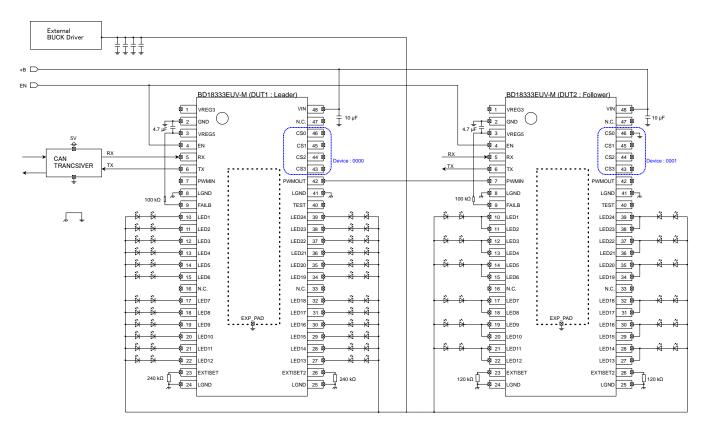

# **Typical Application Circuit**

Figure 1. Application Circuit

Nano Cap™ is a trademark or a registered trademark of ROHM Co., Ltd.

OProduct structure: Silicon integrated circuit OThis product has no designed protection against radioactive rays.

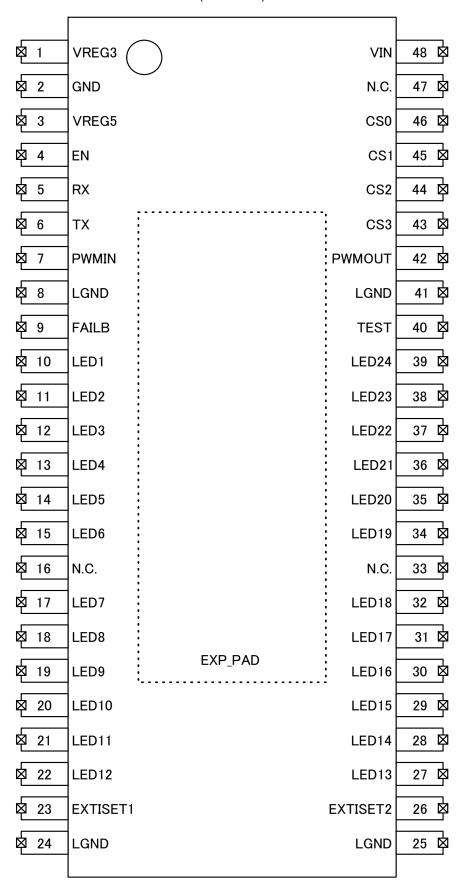

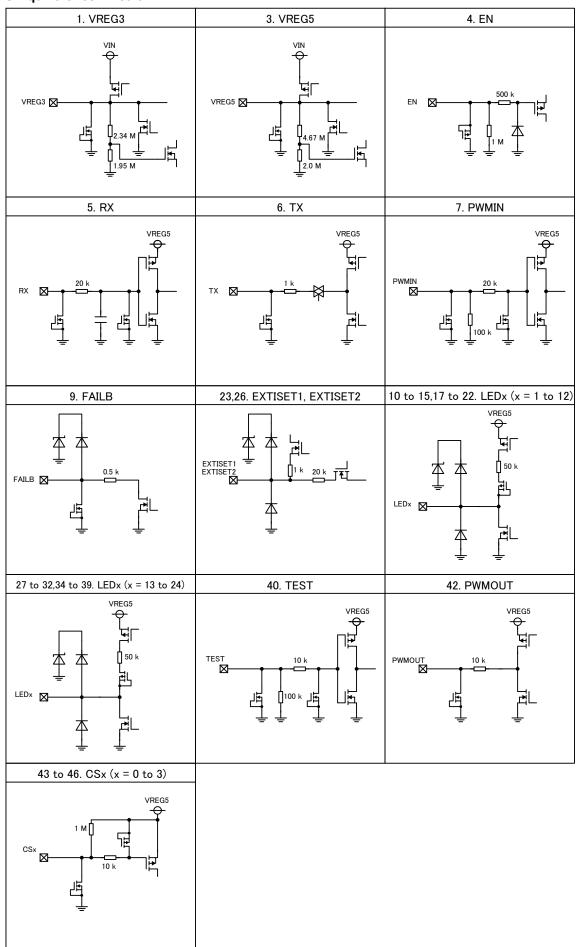

# **Pin Configuration**

# HTSSOP-C48 (TOP VIEW)

Figure 2. Pin Configuration

# **Pin Description**

|            | ription  |                                                       |

|------------|----------|-------------------------------------------------------|

| Pin<br>No. | Pin Name | Function                                              |

| 1          | VREG3    | 3.3 V voltage output                                  |

| 2          | GND      | Ground                                                |

| 3          | VREG5    | 5.0 V voltage output                                  |

| 4          | EN       | Chip enable                                           |

| 5          | RX       | UART signal receiver                                  |

| 6          | TX       | UART signal transmitter                               |

| 7          | PWMIN    | PWM input frequency for PWM frequency synchronization |

| 8          | LGND     | LED driver ground                                     |

| 9          | FAILB    | Error flag                                            |

| 10         | LED1     | LED current output                                    |

| 11         | LED2     | LED current output                                    |

| 12         | LED3     | LED current output                                    |

| 13         | LED4     | LED current output                                    |

| 14         | LED5     | LED current output                                    |

| 15         | LED6     | LED current output                                    |

| 16         | N.C.     | Non wire connection                                   |

| 17         | LED7     | LED current output                                    |

| 18         | LED8     | LED current output                                    |

| 19         | LED9     | LED current output                                    |

| 20         | LED10    | LED current output                                    |

| 21         | LED11    | LED current output                                    |

| 22         | LED12    | LED current output                                    |

| 23         | EXTISET1 | LED current setting Pin                               |

| 24         | LGND     | LED driver ground                                     |

# **Pin Description - continued**

| Pin<br>No. | Pin Name | Function                                                                                                                                      |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 25         | LGND     | LED driver ground                                                                                                                             |

| 26         | EXTISET2 | LED current setting Pin for LIMPHOME mode                                                                                                     |

| 27         | LED13    | LED current output                                                                                                                            |

| 28         | LED14    | LED current output                                                                                                                            |

| 29         | LED15    | LED current output                                                                                                                            |

| 30         | LED16    | LED current output                                                                                                                            |

| 31         | LED17    | LED current output                                                                                                                            |

| 32         | LED18    | LED current output                                                                                                                            |

| 33         | N.C.     | Non wire connection                                                                                                                           |

| 34         | LED19    | LED current output                                                                                                                            |

| 35         | LED20    | LED current output                                                                                                                            |

| 36         | LED21    | LED current output                                                                                                                            |

| 37         | LED22    | LED current output                                                                                                                            |

| 38         | LED23    | LED current output                                                                                                                            |

| 39         | LED24    | LED current output                                                                                                                            |

| 40         | TEST     | TEST mode setting Pin                                                                                                                         |

| 41         | LGND     | LED driver ground                                                                                                                             |

| 42         | PWMOUT   | PWM output signal for PWM frequency synchronization                                                                                           |

| 43         | CS3      | Chip select                                                                                                                                   |

| 44         | CS2      | Chip select                                                                                                                                   |

| 45         | CS1      | Chip select                                                                                                                                   |

| 46         | CS0      | Chip select                                                                                                                                   |

| 47         | N.C.     | Non wire connection                                                                                                                           |

| 48         | VIN      | Power supply input                                                                                                                            |

| -          | EXP-PAD  | Exposed pad. Connect EXP-PAD to the internal PCB ground plane using multiple via, it will provide excellent heat dissipation characteristics. |

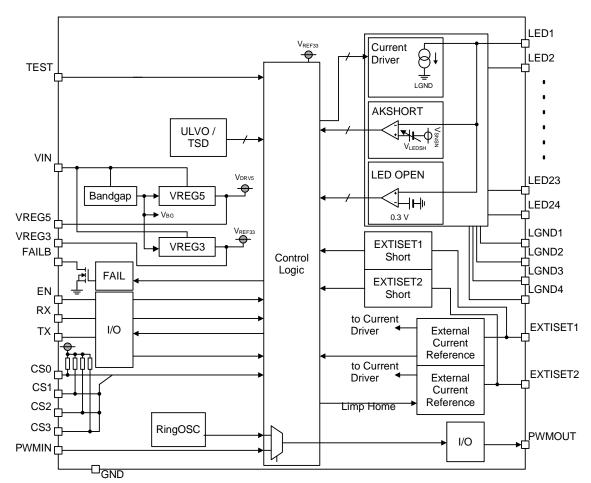

# **Block Diagram**

Figure 3. Block Diagram

# **Description of Block**

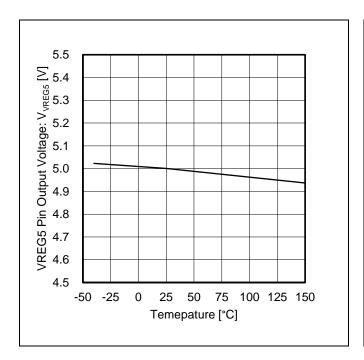

#### 1. Reference Voltage (VREG5, VREG3)

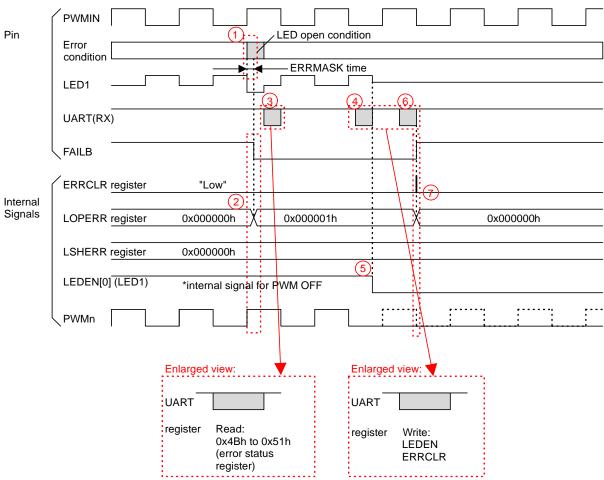

This IC generates 5.0 V (Typ) and 3.3 V (Typ) from the voltage input to VIN. These voltages are output on the VREG5 and the VREG3 pins. The output voltage of the VREG5 pin ( $V_{VREG5}$ ) is used as the power supply for the internal circuit, and the output voltage of the VREG3 pin ( $V_{VREG3}$ ) is used as the power supply for the internal digital circuit. To secure the phase compensation capacitance, it is necessary to connect 1.0  $\mu$ F to 10  $\mu$ F to the VREG5 pin and 0.0  $\mu$ F (the VREG3 pin is able to set for capacitor less application with Nano Cap<sup>TM</sup> technology) to 0.1  $\mu$ F to the VREG3 pin. If a capacitor is not connected to the VREG5 pin, circuit operation such as oscillation of the reference voltage will be very unstable. Do not use these pins voltages as a power source other than this LSI.

UVLO function is built in to the VIN pin, the VREG5 pin and the VREG3 pin. When the conditions of VIN > 4.2 V (Typ), VREG5 > 4.2 V (Typ), VREG3 > 2.8 V (Typ) are satisfied, the IC starts operating. If any condition of VIN < 4.0 V (Typ), VREG5 < 4.0 V (Typ), VREG3 < 2.7 V (Typ) is satisfied, the IC will stop operating.

Nano Cap™ is a combination of technologies which allow stable operation even if output capacitance is connected with the range of nF unit. And, this IC achieve capacitor less technology with the Nano Cap™.

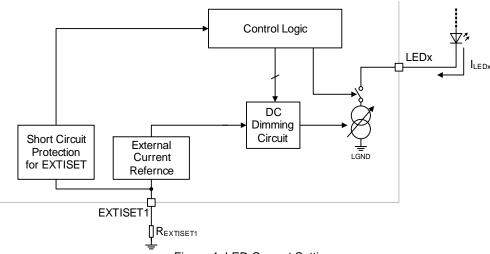

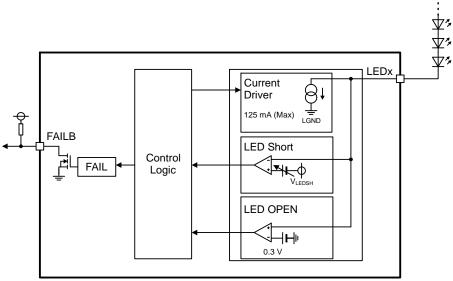

#### 2. Current Driver

This IC has a built-in 24CH constant current driver. The maximum output current of the constant current driver is 125 mA/CH when the EXTISET1 function is used. Built-in PWM dimming and DC dimming function for each CH. The resolution for each dimming mode depends on the register settings. Please refer to the detailed description of Address 0x00h, 0x24h to 0x2Fh, 0x30h to 0x32h, 0x33h to 0x4Ah for the setting of dimming mode and output current.

Figure 4. LED Current Setting

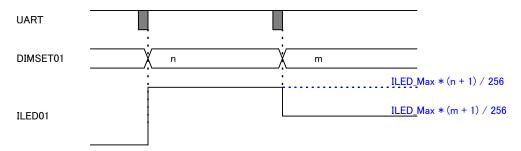

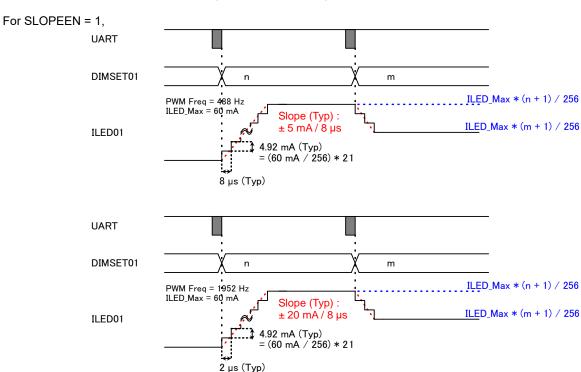

# (1) Local PWM Dimming Control and LED Current Setting

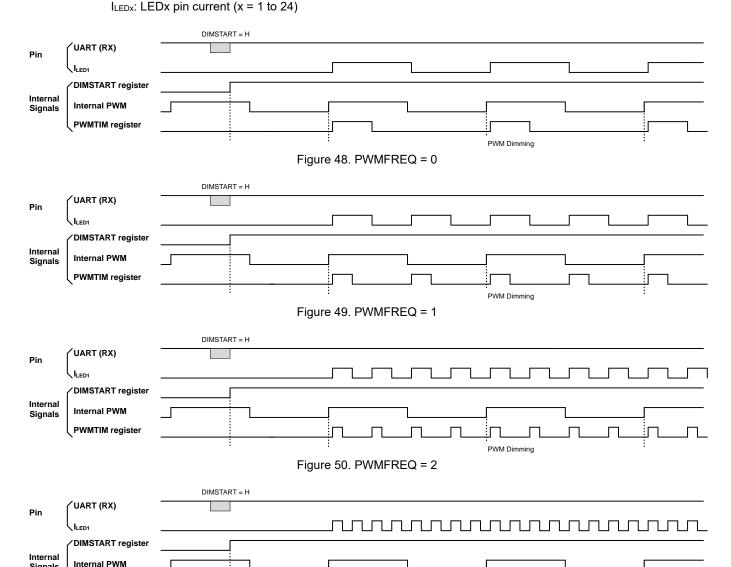

This IC has a built-in 8-bit PWM dimming function. LED current PWM on duty of each channel can be controlled by UART input. To use 8-bit PWM dimming, set the DIMMODE register value to "0". When using PWM dimming, the LED current can be set by the built-in 4-bit DC dimming function.

LED current PWM on duty and LED current I<sub>LEDx</sub> (x = 1 to 24) can be calculated by the following formula.

$$PWM\ ON\ duty = \frac{DIMSETx[7:0]+1}{256} \times 100\ [\%]$$

where

DIMSETx[7:0] is the decimal number of DIMSETx[7:0]. (x = 01 to 24)

In case of using the EXTISET1 pin

$$I_{LEDx} = \frac{(DCDIMx[3:0]+1)}{16} \times \left(\frac{V_{EXTISET1}}{R_{EXTISET1}} \times 12000\right) \text{ [A]}$$

where:

DCDIMx[3:0] is the decimal number of DCDIMx[3:0]. (x = 01 to 24)

$V_{EXTISET1}$  is the EXTISET1 pin voltage, 600 mV (Typ).

$R_{EXTISET1}$  is the Resistor for connecting the EXTISET1 pin.

#### 2. Current Driver -continued

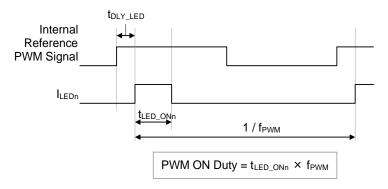

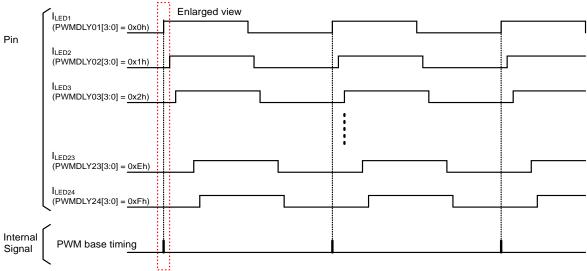

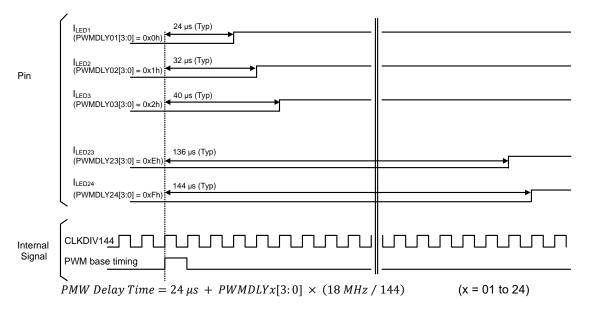

# (2) Local PWM Delay Control

This IC can reduce the load fluctuation by controlling the rising timing of LED current for each CH. This setting is not required when using Local DC dimming described later. Delay width  $(t_{DLY\_LED})$  can be calculated by the following formula.

$$t_{DLY\ LED} = 4bit\_DC\_PWMDLYx[3:0] \times 8 + 24$$

[µs]

where:

$4bit\_DC\_PWMDLYx[3:0]$  is the decimal number of PWMDLYx[3:0]. (x = 01 to 24) t<sub>LED\_ONn</sub> is LED current PWM on time. (n = 1 to 24) f<sub>PWM</sub> is PWM dimming frequency.

Figure 5. Local PWM Delay Control

# (3) Local DC Dimming Control

This IC can switch the 8-bit PWM dimming register for Local DC dimming. To use 8-bit DC dimming, set the DIMMODE register value to "1". When using 8-bit DC dimming, PWM ON Duty is fixed at 100 %. LED current  $I_{LEDn}$  (n = 1 to 24) can be calculated by the following formula.

In case of using the EXTISET1 pin

$$I_{LEDn} = \frac{(DIMSETx[7:0]+1)}{256} \times \left(\frac{V_{EXTISET1}}{R_{EXTISET1}} \times 12000\right) \text{ [A]}$$

where:

DIMSETx[7:0] is the decimal number of DIMSETx[7:0].  $V_{EXTISET1}$  is the EXTISET1 pin voltage, 600 mV (Typ).  $R_{EXTISET1}$  is the Resitor for connecting the EXTISET1 pin.

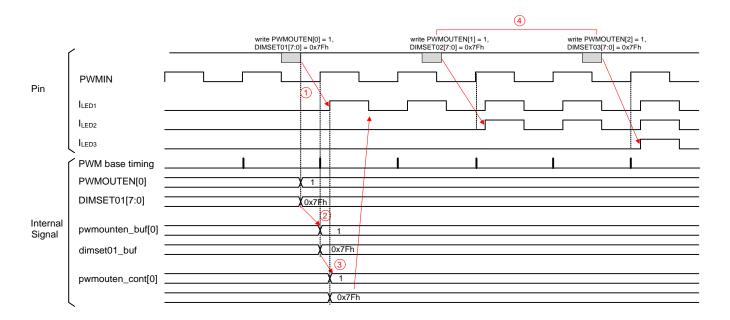

# (4) LED Current Output Enable (PWMOUT, LEDEN)

This IC can individually turn off the CH regardless of the PWM/DC dimming setting. It can be set by updating the register of Address 0x30h (PWMOUTL), 0x31h (PWMOUTM) and 0x32h (PWMOUTH). When this register is set, the output is kept on until the next PWM cycle and the output is turn off at the PWM rising timing. The LED current ON/OFF control can also be controlled using the Address 0x04h (LEDENL), 0x05h (LEDENM) and 0x06h (LEDENH) registers. For these registers, ON/OFF control is reflected immediately when written to the register.

# **Description of Blocks - continued**

#### 3. Diagnosis Enable (DEN)

When  $V_{IN} < V_{IN\_DEN}$ , the IC cannot detect LED Open Detection (LEDOP).  $V_{IN\_DEN}$  can be defined by setting register. (Address 0x17h)

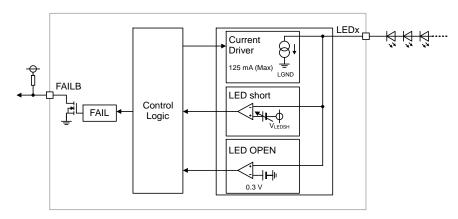

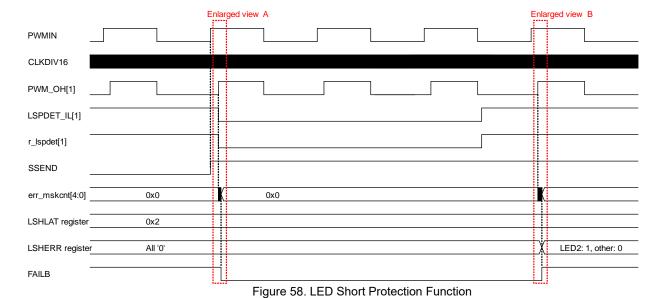

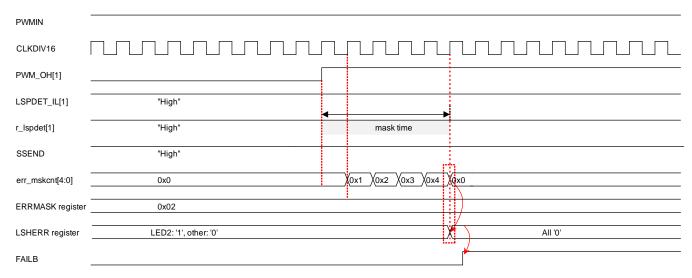

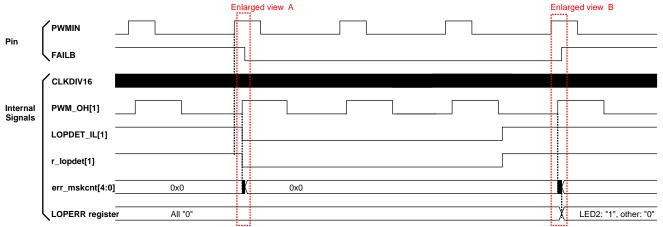

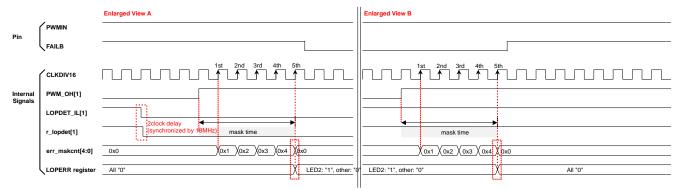

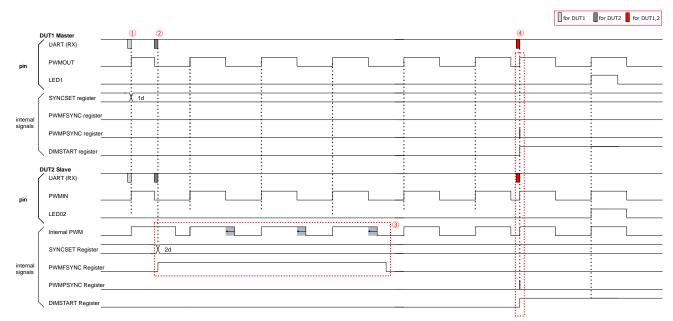

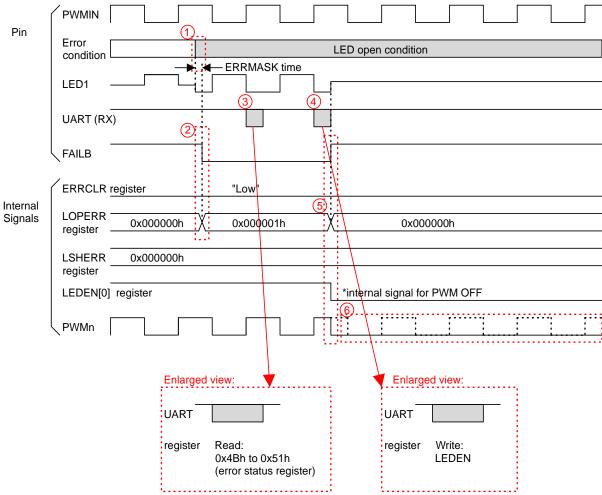

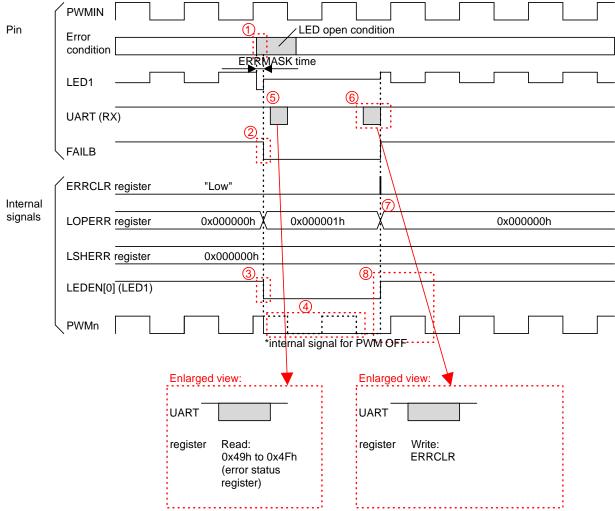

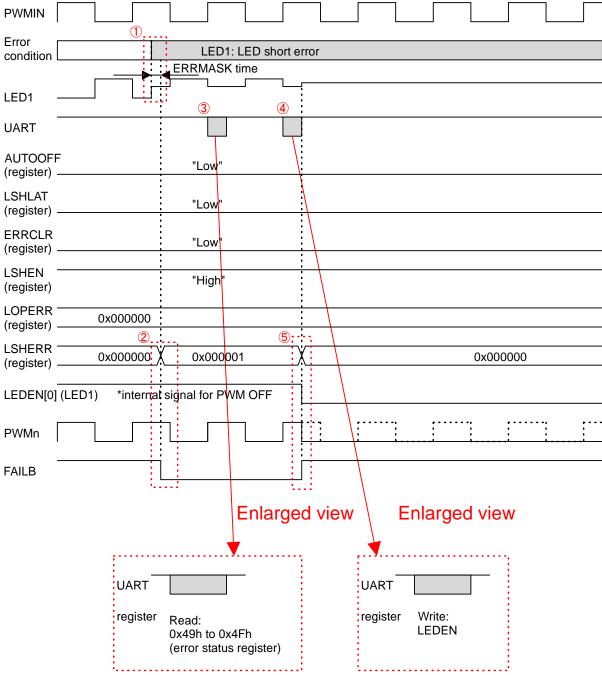

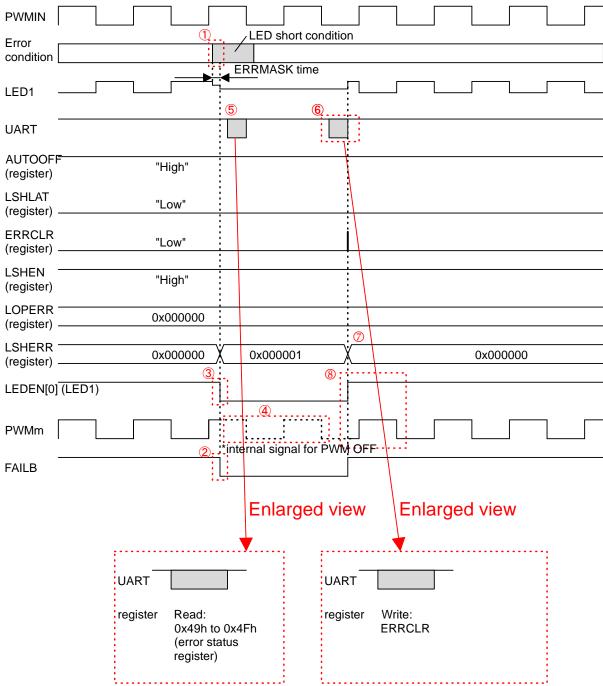

#### 4. LED Short Detection and Open Detection

This IC has LED short detection and open detection. LED short detection can be disabled, and LED short detect voltage can be controlled by UART input. (Disable setting: Address 0x09h, 0x0Ah, LED detect voltage setting: Address 0x0Bh to 0x16h) LED error detection status of each channel can be read by UART input. (LED short: Address 0x4Bh to 0x4Dh, LED open: Address 0x4Dh to 0x50h)

The IC can detect LED short condition when IC meets the following condition:

$$V_{LEDx} > V_{LEDSH}$$

and  $V_{IN} > V_{IN DEN}$

#### Where:

$V_{LEDx}$  is the LEDx pin voltage. (x = 1 to 24)  $V_{LEDSH}$  is the LED short detect voltage  $V_{IN\ DEN}$  is the Diagnosis Enable VIN voltage

The IC can also detect LED open condition when the IC meets the following condition:

$$V_{LEDx} < V_{LEDOP}$$

and  $V_{IN} > V_{IN DEN}$

#### Where:

$V_{LEDx}$  is the LEDx pin voltage. (x = 1 to 24)

$V_{LEDOP}$  is the LED open detecting voltage, 0.3 V (Typ).

$V_{IN\ DEN}$  is the Diagnosis Enable VIN voltage.

If the IC detects LED error (short or open) mode and set AUTOOFF register to "1" (Address 0x07h: SYSSET4), Current Driver of detected CH is turn off and the FAILB pin voltage is switched to "Low". Other current driver CH are continuing to output.

Figure 6. LED Open Detection

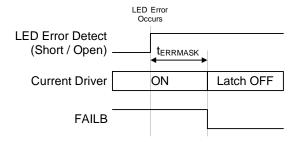

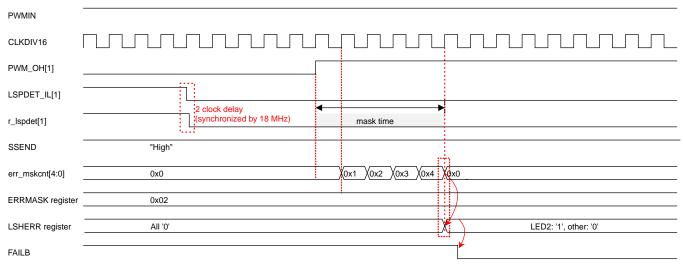

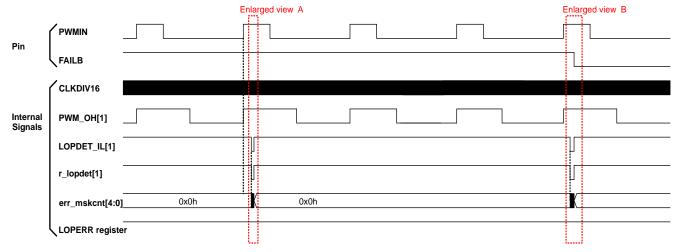

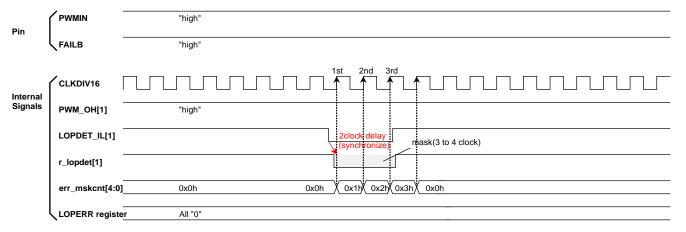

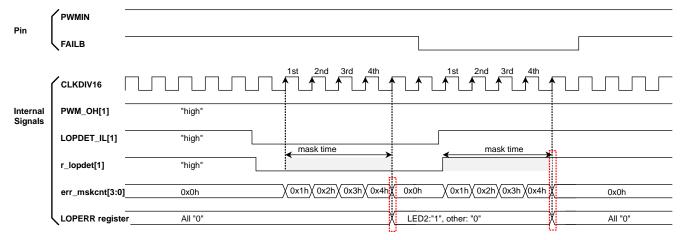

#### **LED Error Output Mask Time Setting**

The mask time for LED error detection can be controlled by UART input. (Address 0x03h: SYSSET3) LED error detection is disabled until the mask time has elapsed.

Figure 7. LED Error Output Mask Time Setting

#### Where:

terrmask is the mask time for LED error detection.

# **Description of Blocks - continued**

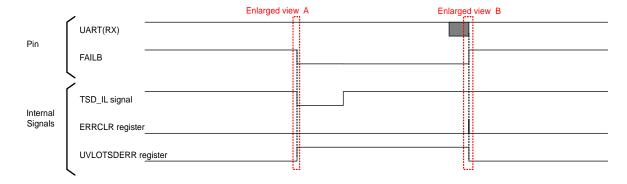

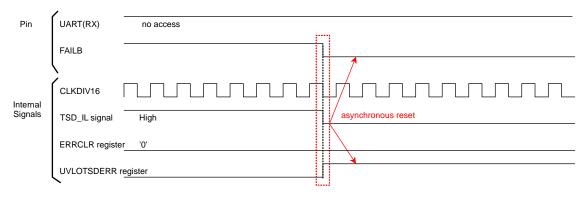

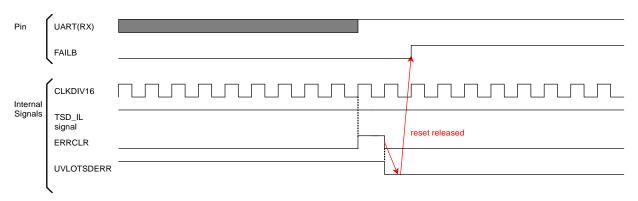

#### **Protection Feature**

Table 1. Protection Table 1

| No. | Protection                            | Detect<br>condition                               | Release<br>condition                                    | Current<br>Driver | FAILB | Status register | LIMPHOME <sup>(Note 2)</sup> |

|-----|---------------------------------------|---------------------------------------------------|---------------------------------------------------------|-------------------|-------|-----------------|------------------------------|

| 1   | VIN<br>UVLO                           | VIN <<br>4.0 V (Typ)                              | VIN ><br>4.2 V (Typ)                                    | OFF               | Low   | UVLOTSDERR      | 0                            |

| 2   | VREG5<br>UVLO                         | VREG5 <<br>4.0 V (Typ)                            | VREG5 ><br>4.2 V (Typ)                                  | OFF               | Low   | UVLOTSDERR      | 0                            |

| 3   | VREG3<br>UVLO                         | VREG3 <<br>2.7 V (Typ)                            | VREG3 ><br>2.8 V (Typ)                                  | OFF               | Low   | UVLOTSDERR      | 0                            |

| 4   | TSD                                   | Ta ><br>175 °C (Typ)                              | Ta <<br>150 °C (Typ)                                    | OFF               | Low   | UVLOTSDERR      | 0                            |

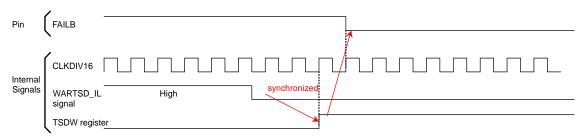

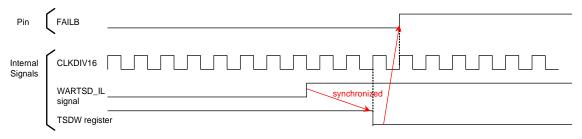

| 5   | TSD<br>warning                        | Ta ><br>125 °C (Typ)                              | Ta <<br>110 °C (Typ)                                    | operating         | Low   | TSDW            | 0                            |

| 6   | LED open                              | V <sub>LEDx</sub> < 0.3 V (Typ)                   | V <sub>LEDx</sub> > 0.4 V (Typ)                         | operating         | Low   | LOPERR          | 0                            |

| 7   | LED Short                             | V <sub>LEDx</sub> > register setting & PWM "High" | V <sub>LEDx</sub> <<br>register setting<br>& PWM "High" | operating         | Low   | LSHERR          | -                            |

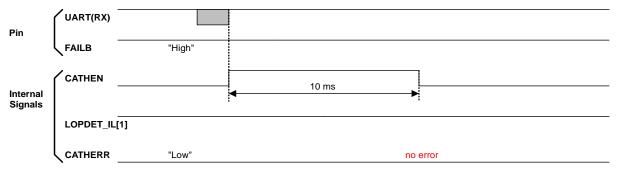

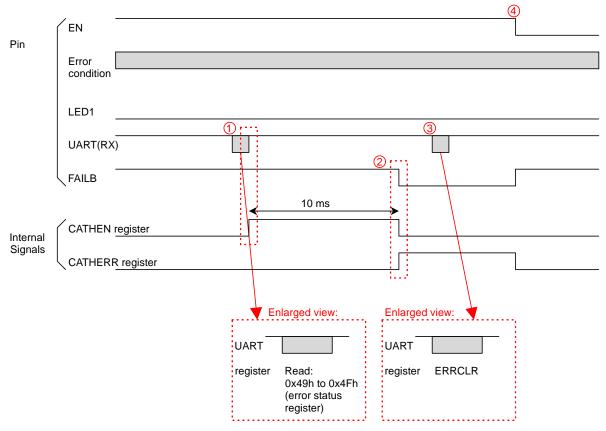

| 8   | LED cathode short <sup>(Note 1)</sup> | V <sub>LEDx</sub> < 0.3 V<br>(Typ)                | -                                                       | operating         | Low   | CATHERR         | -                            |

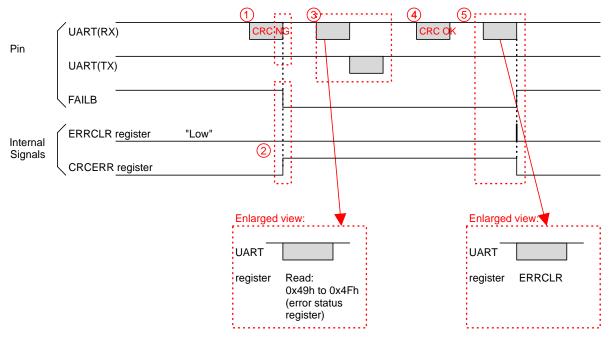

| 9   | CRC error                             | Error in data<br>setent in<br>UART<br>Write/Read  | No error in<br>data sent in<br>UART Write               | operating         | Low   | CRCERR          | 0                            |

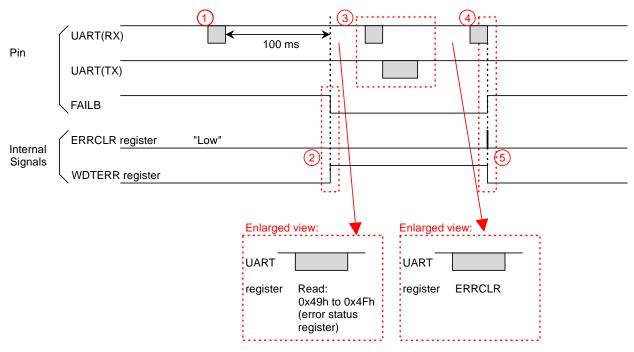

| 10  | UART WDT                              | no access<br>during 100 ms                        | -                                                       | operating         | Low   | WDTERR          | -                            |

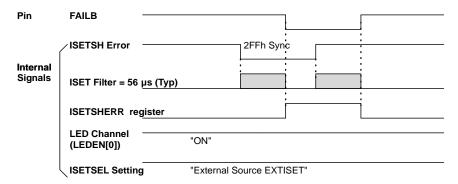

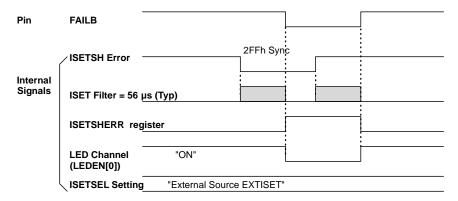

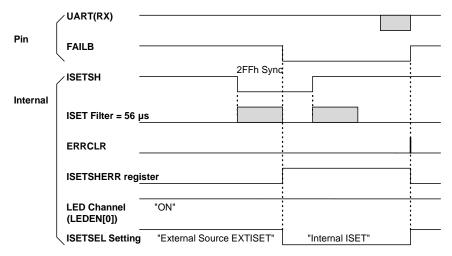

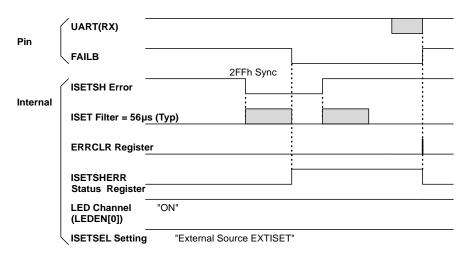

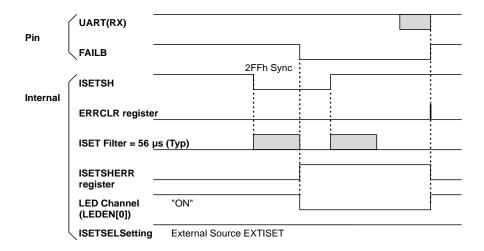

| 11  | ISETSH1                               | R <sub>EXTISET1</sub> < 30 kΩ (Typ)               | R <sub>EXTISET1</sub> > 30 kΩ (Typ)                     | operating         | Low   | ISETSHERR       | 0                            |

| 12  | ISETSH2                               | R <sub>EXTISET2</sub> < 30 kΩ (Typ)               | R <sub>EXTISET2</sub> > 30 kΩ (Typ)                     | operating         | Low   | ISETSHERR       | 0                            |

When it detects "VINUVLO" or "VREG3UVLO" or "VREG5UVLO" or "TSD" or "EN = L", it invokes system reset. it can't detect other protection. (x = 1 to 24)

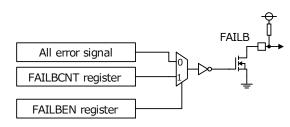

The FAILB pin is recommended to pull up to VREG5. Recommended value for pull up resistance is 20 k $\Omega$  to 100 k $\Omega$ . When above failure is detected, the FAILB pin voltage becomes "Low". If the FAILB pin is not used pin shall be kept open.

<sup>(</sup>Note 1) "LED open protection" is not available when set CATHEN register to "1".

(Note 2) "O" this protection can be detected during LIMPHOME mode. "-" this protection cannot be detected during LIMPHOME mode. If any of "-" protection is detect before entering LIMPHOME mode, keep status register until mode returns to normal.

#### 5. Protection Feature - continued

Table 2. Protection Table 2

| No. | Protection        | SSMASK | ERRMASK | Protection enable | Status and FAILB<br>output latch<br>enable | AUTOOFF |

|-----|-------------------|--------|---------|-------------------|--------------------------------------------|---------|

| 1   | VIN<br>UVLO       | -      | -       | -                 | 0                                          | -       |

| 2   | VREG5<br>UVLO     | -      | -       | -                 | 0                                          | -       |

| 3   | VREG3<br>UVLO     | -      | -       | -                 | 0                                          | -       |

| 4   | TSD               | -      | -       | -                 | 0                                          | -       |

| 5   | TSD<br>warning    | -      | -       | TSDWEN            | -                                          | -       |

| 6   | LED open          | 0      | 0       | LOPEN             | LOPLAT                                     | 0       |

| 7   | LED short         | 0      | 0       | LSHEN             | LSHLAT                                     | 0       |

| 7   | LED cathode short | -      | -       | CATHEN            | 0                                          | -       |

| 8   | CRC error         | -      | -       | -                 | CRCERLAT                                   | -       |

| 9   | UART WDT          | -      | -       | WDTEN             | 0                                          | -       |

| 10  | ISETSH1           | -      | -       | ISETSEL           | ISETLAT                                    | -       |

| 11  | ISETSH2           | -      | -       | ISETSEL           | ISETLAT                                    | -       |

O: It has this function by default.

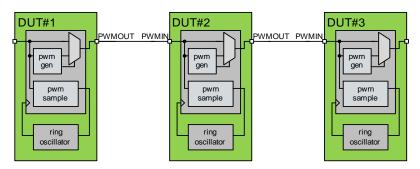

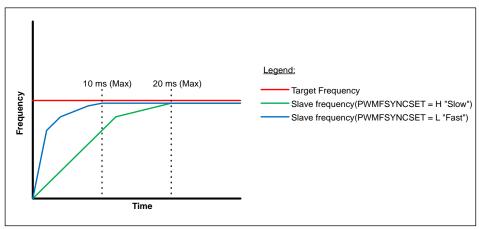

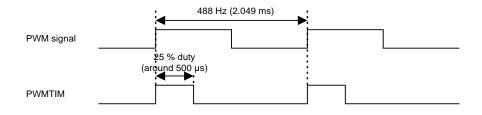

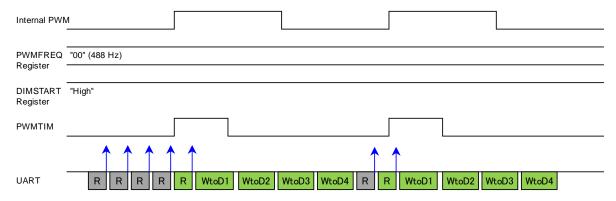

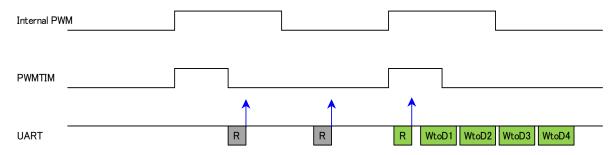

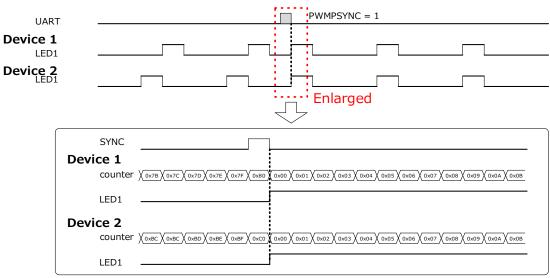

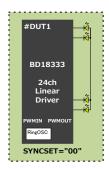

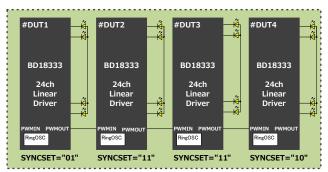

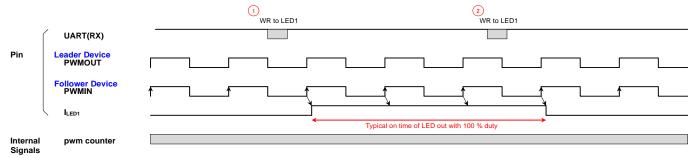

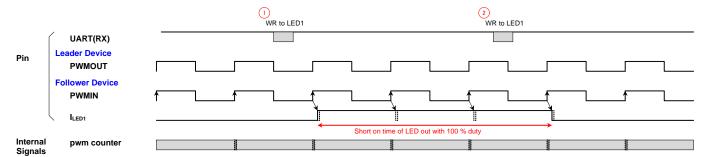

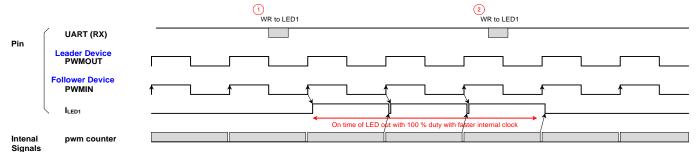

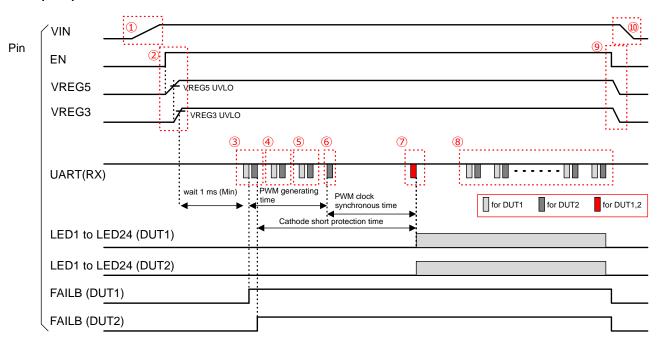

# 6. PWM Synchronization for Each Device

This feature allows BD18333EUV-M to synchronize internal clock with other BD18333EUV-M and vice versa. SYNCSET register can set this IC as Leader or Follower. As Leader Device, it generates 488 Hz (Typ) reference signal (duty = 50 %) in PWMOUT that other Follower devices use to adjust internal clock. As Follower Device, it enables PWMIN input to receive the reference signal to adjust internal clock and LED output timing.

Figure 8. PWM Synchronization Setting

In this figure above, DUT#1 is a Leader device, it generates the reference signal via PWMOUT. On the other hand, DUT#2 receives the reference signal via PWMIN, it processes this signal to adjust the internal ring oscillator. Same process in DUT#2 occur in DUT#3 and so on. There is only a single Leader device.

<sup>-:</sup> It doesn't have this function.

# **Description of Blocks - continued**

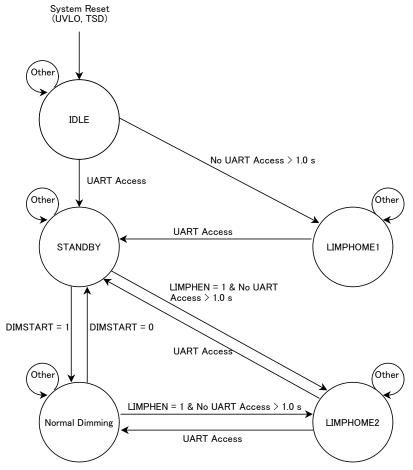

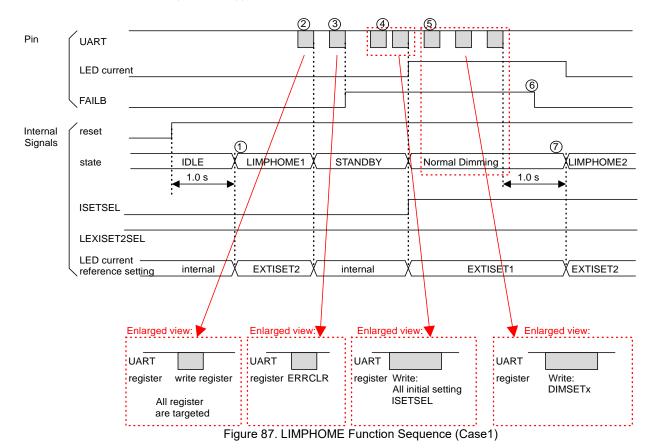

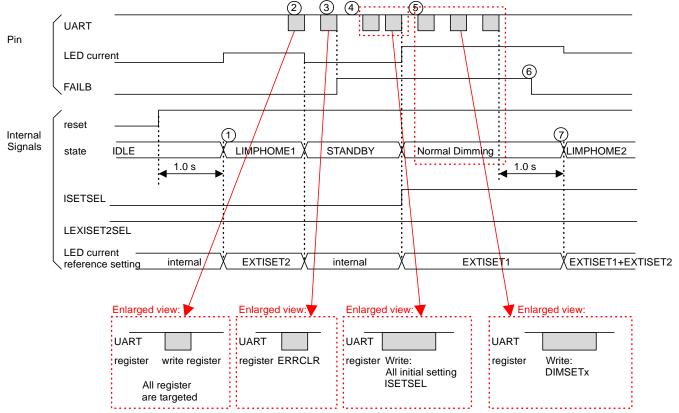

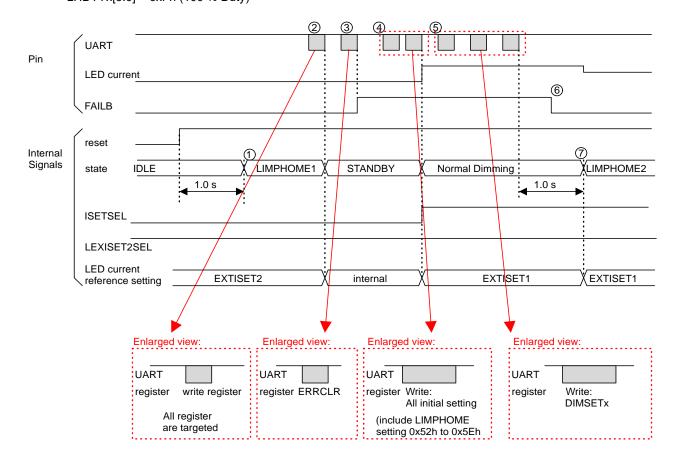

#### 7. LIMPHOME Function

This IC has LIMPHOME function. This function is controlled by LIMPHEN register (Address 0x5Eh, initially enabled). If LIMPHEN is "1" and there is no UART access (no CRC OK) for over 1.0 s (Typ), device detects the error and operates LED dimming. In each state, LED dimming is according to the latest register value (DIMSET, DCDIM and LHDTY). The registers are updated at the timing described in the register description.

Note: Devices can be connected in parallel, refer to UART Protocol for more details. When a device is connected in parallel and is not being accessed while other devices are being accessed, it will not enter LIMPHOME mode.

Figure 9. LIMPHOME Function

Table 3. LIMPHOME Dimming Settings (x = 1 to 24)

| State             | Description                                                    | Dimming setting                                                                                                               |                                                 |                                                |  |  |  |  |

|-------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------|--|--|--|--|

| State             | Description                                                    | Current reference setting                                                                                                     | DC current setting                              | PWM duty setting                               |  |  |  |  |

| IDLE              | Reset condition, No lighting                                   | -                                                                                                                             | -                                               | -                                              |  |  |  |  |

| STANDBY           | During initial setting,<br>No lighting                         | -                                                                                                                             | -                                               | -                                              |  |  |  |  |

| LIMPHOME1         | lighting by EXTISET2 resistor (UART error condition)           | EXTISET2                                                                                                                      | 100 % (DCDIMx)                                  | 100 % (LHDTYx)                                 |  |  |  |  |

| Normal<br>Dimming | Normal dimming condition                                       | ISETSEL = 0 (Internal ISET)<br>ISETSEL = 1 (EXTISET1)                                                                         | DIMMODE = 0<br>DCDIMx<br>DIMMODE = 1<br>DIMSETx | DIMMODE = 0<br>DIMSETx<br>DIMMODE = 1<br>100 % |  |  |  |  |

| LIMPHOME2         | lighting by UART<br>LIMPHOME setting (UART<br>error condition) | LEXTISET2SEL = 1 <sup>(Note 1)</sup> EXTISET1 + EXTISET2  LEXTISET2SEL = 0 ISETSEL = 0 (Internal ISET) ISETSEL = 1 (EXTISET1) | DIMMODE = 0<br>DCDIMX<br>DIMMODE = 1<br>DIMSETX | LHDTYx                                         |  |  |  |  |

(Note 1) Not Recommended Setting

#### 7. LIMPHOME Function - continued

At LIMPHOME1,

In case of the EXTIET2 pin set "OPEN"

$$I_{LEDn} = 0 [A]$$

In case of the EXTISET2 pin set R<sub>EXTISET2</sub>

$$I_{LEDn} = \frac{V_{EXTISET2}}{R_{EXTISET2}} \times 12000$$

[A]

At LIMPHOME2,

$$PWM\ ON\ duty = \frac{LHDTYx[3:0] + 1}{16} \times 100\ [\%]$$

In case of using the EXTISET2 pin and the EXTISET2 pin set "OPEN"

$$I_{LEDn} = 0 [A]$$

In case of using the EXTISET2 pin and DIMMODE = 0

$$I_{LEDn} = \frac{(DCDIMx[3:0]+1)}{16} \times \left(\frac{V_{EXTISET1}}{R_{EXTISET2}} + \frac{V_{EXTISET2}}{R_{EXTISET2}}\right) \times 12000 \text{ [A]}$$

In case of using the EXTISET2 pin and DIMMODE = 1

$$I_{LEDn} = \frac{(DIMSETx[7:0]+1)}{256} \times \left(\frac{V_{EXTISET1}}{R_{EXTISET2}} + \frac{V_{EXTISET2}}{R_{EXTISET2}}\right) \times 12000 \text{ [A]}$$

In case of using the Internal Current Set and DIMMODE = 0

$$I_{LEDn} = \frac{(DCDIMx[3:0] + 1)}{16} \times 0.060$$

[A]

In case of using the Internal Current Set and DIMMODE = 1

$$I_{LEDn} = \frac{(DIMSETx[7:0] + 1)}{256} \times 0.060$$

[A]

In case of using the EXTISET1 pin and DIMMODE = 0

$$I_{LEDn} = \frac{(DCDIMx[3:0]+1)}{16} \times \left(\frac{V_{EXTISET1}}{R_{EXTISET1}} \times 12000\right)$$

[A]

In case of using the EXTISET1 pin and DIMMODE = 1

$$I_{LEDn} = \frac{(DIMSETx[7:0]+1)}{256} \times \left(\frac{V_{EXTISET1}}{R_{EXTISET1}} \times 12000\right) [A]$$

where: (n = 1 to 24, x = 01 to 24)

$I_{LEDn}$  is the each channel current.

$V_{EXTISET2}$  is the EXTISET2 pin voltage. It is 300 mV (Typ).

$R_{EXTISET2}$  is the Resistor for connecting the EXTISET2 pin.

LHDTYx[3:0] is the decimal number of LHDTYx[3:0].

DCDIMx[3:0] is the decimal number of DCDIMx[3:0].

DIMSETx[7:0] is the decimal number of DIMSETx[7:0].

$V_{EXTISET1}$  is the EXTISET1 pin voltage, 600 mV (Typ).

$R_{EXTISET1}$  is the Resistor for connecting the EXTISET1 pin

Absolute Maximum Ratings (Tj = 25 °C)

| Parameter                                                                               | Symbol                                                                                  | Rating                               | Unit |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------|------|

| Power Supply Voltage                                                                    | Vin                                                                                     | -0.2 to +42.0                        | ٧    |

| EN Pin Voltage                                                                          | Ven                                                                                     | -0.2 to VIN                          | ٧    |

| LED1 to LED24 Pin Voltage                                                               | V <sub>LED1</sub> to V <sub>LED24</sub>                                                 | -0.2 to +42.0                        | ٧    |

| VREG3 Pin Voltage                                                                       | Vvreg3                                                                                  | -0.2 to +4.5                         | ٧    |

| VREG5, FAILB, RX, TX, PWMIN, PWMOUT, CS0, CS1, CS2, CS3, EXTISET1, EXTISET2 Pin Voltage | Vvreg5, Vfailb, Vrx, Vtx, Vpwmin, Vpwmout, Vcs0, Vcs1, Vcs2, Vcs3, Vextiset1, Vextiset2 | -0.2 to +7.0<br>< V <sub>VREG5</sub> | V    |

| Storage Temperature Range                                                               | Tstg                                                                                    | -55 to +150                          | °C   |

| Maximum Junction Temperature                                                            | Tjmax                                                                                   | 150                                  | °C   |

Caution 1: Operating the IC over the absolute maximum ratings may damage the IC. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the IC is operated over the absolute maximum ratings.

# Thermal Resistance<sup>(Note 1)</sup>

| Deservator                                                     | Currely of     | Thermal Res            | 1.1                      |      |  |

|----------------------------------------------------------------|----------------|------------------------|--------------------------|------|--|

| Parameter                                                      | Symbol         | 1s <sup>(Note 3)</sup> | 2s2p <sup>(Note 4)</sup> | Unit |  |

| HTSSOP-C48                                                     |                |                        |                          |      |  |

| Junction to Ambient                                            | θја            | 71.20                  | 28.30                    | °C/W |  |

| Junction to Top Characterization Parameter <sup>(Note 2)</sup> | $\Psi_{ m JT}$ | 9.00                   | 7.00                     | °C/W |  |

| Layer Number of Measurement Board | Material  | Board Size                    |

|-----------------------------------|-----------|-------------------------------|

| Single                            | FR-4      | 114.3 mm x 76.2 mm x 1.57 mmt |

| Тор                               |           |                               |

| Copper Pattern                    | Thickness |                               |

| Footprints and Traces             | 70 µm     |                               |

| Layer Number of<br>Measurement Board | Material  | Board Size               | Thermal V<br>Pitch |                   | e 5)<br>Diameter |           |

|--------------------------------------|-----------|--------------------------|--------------------|-------------------|------------------|-----------|

| 4 Layers                             | FR-4      | 114.3 mm x 76.2 mm       | 1.20 mm            | Ф                 | 0.30 mm          |           |

| Тор                                  |           | 2 Internal Laye          | Bottom             |                   |                  |           |

| Copper Pattern                       | Thickness | Copper Pattern Thickness |                    | Copper Pattern    |                  | Thickness |

| Footprints and Traces                | 70 µm     | 74.2 mm x 74.2 mm 35 μm  |                    | 74.2 mm x 74.2 mm |                  | 70 µm     |

(Note 5) This thermal via connect with the copper pattern of layers 1,2, and 4. The placement and dimensions obey a land pattern.

Caution 2: Should by any chance the maximum junction temperature rating be exceeded the rise in temperature of the chip may result in deterioration of the properties of the chip. In case of exceeding this absolute maximum rating, design a PCB with thermal resistance taken into consideration by increasing board size and copper area so as not to exceed the maximum junction temperature rating.

<sup>(</sup>Note 1) Based on JESD51-2A (Still-Air), using a BD18333EUV-M Chip.

(Note 2) The thermal characterization parameter to report the difference between junction temperature and the temperature at the top center of the outside surface of the component package.

(Note 3) Using a PCB board based on JESD51-3.

(Note 4) Using a PCB board based on JESD51-5, 7.

**Recommended Operating Condition**

| Parameter                                                      | Symbol             | Min | Тур  | Max  | Unit | Comment                                           |

|----------------------------------------------------------------|--------------------|-----|------|------|------|---------------------------------------------------|

| Power Supply Voltage <sup>(Note 1)</sup>                       | VIN                | 4.5 | 12.0 | 40.0 | V    |                                                   |

| Operating Temperature                                          | Topr               | -40 | 25   | +125 | °C   |                                                   |

| The Capacitor for Connecting the VREG5 Pin                     | C <sub>VREG5</sub> | 1.0 | 4.7  | 10.0 | μF   |                                                   |

| The Capacitor for Connecting the VREG3 Pin <sup>(Note 2)</sup> | C <sub>VREG3</sub> | 0.0 | -    | 0.1  | μF   |                                                   |

| The Resistor for Connecting the EXTISET1 Pin                   | REXTISET1          | 56  | -    | 1200 | kΩ   |                                                   |

| The Resistor for Connecting the EXTISET2 Pin                   | REXTISET2          | 56  | -    | 720  | kΩ   |                                                   |

| The Resistor for Connecting the FAILB Pin                      | RFAILB             | 56  | 100  | 220  | kΩ   |                                                   |

| PWMIN Frequency                                                | fextclk            | 400 | 488  | 600  | Hz   |                                                   |

| PWMIN Duty                                                     | DEXTCLK            | -   | 50   | -    | %    | Please connect to the PWMOUT pin of Leader device |

Note: Above operation range is referring to IC independently. Thorough verification of the coefficient setting in actual application shall be practiced.

<sup>(</sup>Note 1) When IC is started, the volrage must be UVLO release voltage or more. Therefore, consider the power supply drop caused by the parasitic resistor.

VIN (Min) = 4.5V is the minimum value that can operate the IC independently after started. The minimum value of power supply voltage that can be set depends on the voltage drop due to the parasitic resistor of power line.

<sup>(</sup>Note 2) The VREG3 pin is designed to work with "Capacitor less" application for use Nano Cap™ technology. When adding capacitor, it may affect noise. So please kindly consider noise reduction such as using a 2s2p PCB board and etc.

# **Electrical Characteristic**

(Unless otherwise specified :  $V_{IN}$  = 13 V , Tj= -40 °C to +150 °C)

| miess otherwise specified . VIN - 13 V                                            | , 1j= <del>-4</del> 0 C to + | 150 () |      |      |      |                                                                                                                                      |

|-----------------------------------------------------------------------------------|------------------------------|--------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                                         | Symbol                       | Min    | Тур  | Max  | Unit | Condition                                                                                                                            |

| [Device Overview]                                                                 |                              |        |      |      |      |                                                                                                                                      |

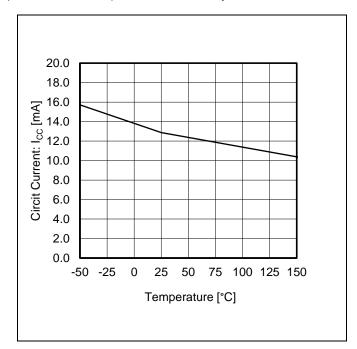

| Circuit Current                                                                   | Icc                          | -      | 12.5 | 20.0 | mA   | V <sub>EN</sub> = High,<br>24CH Current driver OFF                                                                                   |

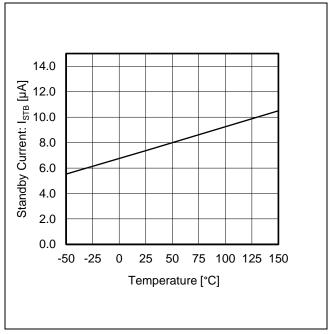

| Standby Current                                                                   | I <sub>STB</sub>             | -      | 7.0  | 15.0 | μA   | V <sub>EN</sub> = Low                                                                                                                |

| [VREG5 Block]                                                                     |                              |        |      |      |      |                                                                                                                                      |

| VREG5 Pin Output Voltage                                                          | Vvreg5                       | 4.5    | 5.0  | 5.5  | V    | I <sub>VREG5</sub> = 0 mA                                                                                                            |

| VREG5 Pin<br>Load Regulation Voltage                                              | $\Delta V_{ m VREG5}$        | -      | -    | 50   | mV   | Ivreg5 = 5 mA                                                                                                                        |

| VREG5 Pin Over Current Protection                                                 | Ivreg50CP                    | 60     | -    | -    | mA   |                                                                                                                                      |

| [VREG3 Block]                                                                     |                              |        |      |      |      |                                                                                                                                      |

| VREG3 Pin Output Voltage                                                          | V <sub>VREG3</sub>           | 3.1    | 3.3  | 3.5  | V    | I <sub>VREG3</sub> = 0 mA                                                                                                            |

| VREG3 Pin<br>Load Regulation Voltage                                              | ΔV <sub>VREG3</sub>          | -      | -    | 30   | mV   | I <sub>VREG3</sub> = 5 mA                                                                                                            |

| VREG3 Pin Over Current Protection                                                 | Ivreg30cp                    | 30     | -    | -    | mA   |                                                                                                                                      |

| [Constant Current Driver Block]                                                   |                              |        |      |      |      |                                                                                                                                      |

| LED Pin ON Resistance                                                             | R <sub>LED1</sub>            | -      | -    | 6.5  | Ω    | Tj = 25 °C,                                                                                                                          |

| LLD I III ON Resistance                                                           | R <sub>LED2</sub>            | -      | -    | 9.5  | Ω    | Tj = -40 °C to +150 °C,                                                                                                              |

| LED Pin Output Current                                                            |                              | -3.5   | -    | +3.5 | %    | Tj = 25 °C,<br>$R_{EXTISET1} = 120$ kΩ,<br>ISETSEL = 1,<br>DCDIMx[3:0] = 0xFh,<br>DIMSETx[7:0] = 0xFFh<br>(x = 01 to 24)             |

| Absolute Error 1 (Iout_ave/Iout_ideal - 1)                                        | $\Delta$ I $_{ m OUTA1}$     | -5.5   | -    | +5.5 | %    | Tj = -40 °C to +150 °C,<br>$R_{EXTISET1}$ = 120 kΩ,<br>ISETSEL = 1,<br>DCDIMx[3:0] = 0xFh,<br>DIMSETx[7:0] = 0xFFh<br>(x = 01 to 24) |

| LED Pin Output Current<br>Relative Error 1<br>(Ioutx/Iout_Ave - 1)                | $\Delta$ loutr1              | -4     | -    | +4   | %    | Tj = 25 °C,<br>$R_{\text{EXTISET1}} = 120 \text{ k}\Omega$ ,<br>ISETSEL = 1,<br>DIMSETx[7:0] = 0xFFh<br>(x = 01  to  24)             |

| LED Pin Output Current                                                            | I <sub>INL</sub>             | -1.5   | -    | +1.5 | LSB  | Tj = 25 °C<br>$R_{EXTISET1}$ = 120 kΩ,<br>ISETSEL = 0,                                                                               |

| DC Dimming Function Differential Nonlinearity <sup>(Note 1)</sup>                 | I <sub>DNL</sub>             | -1.5   | -    | +1.5 | LSB  | DIMMODE = 0,<br>DCDIMx[3:0] = 0x0h to 0xFh<br>DIMSETx[7:0] = 0xFFh,<br>(x = 01 to 24)                                                |

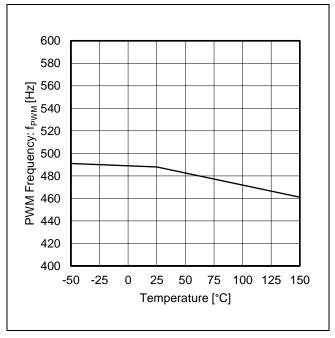

| PWM Frequency                                                                     | f <sub>РWМ</sub>             | 440    | 488  | 535  | Hz   |                                                                                                                                      |

| EXTISET1 Pin<br>Short Circuit Protection Resistor                                 | REXTISET1_SCP                | -      | 30   | 50   | kΩ   |                                                                                                                                      |

| EXTISET2 Pin Short Circuit Protection Resistor (Note 1) Guaranteed by design only | REXTISET2_SCP                | -      | 30   | 50   | kΩ   |                                                                                                                                      |

(Note 1) Guaranteed by design only

Electrical Characteristic - continued (Unless otherwise specified:  $V_{IN}$  = 13 V , Tj= -40 °C to +150 °C)

| Parameter                      | Symbol                  | Min | Тур | Max | Unit | Condition                                                                                    |

|--------------------------------|-------------------------|-----|-----|-----|------|----------------------------------------------------------------------------------------------|

| [PROTECT LOGIC Block]          |                         |     |     |     |      |                                                                                              |

| VREG5UVLO Detection Voltage    | V <sub>VREG5UVLO</sub>  | 3.8 | 4.0 | 4.2 | V    | V <sub>VREG5</sub> falling detect threshold                                                  |

| VREG5UVLO Hysteresis Voltage   | V <sub>VREG5UVHYS</sub> | -   | 200 | -   | mV   |                                                                                              |

| VREG3UVLO Detection Voltage    | Vvreg3uvlo              | 2.5 | 2.7 | 2.9 | V    | V <sub>VREG3</sub> falling detect threshold                                                  |

| VREG3UVLO Hysteresis Voltage   | VVREG3UVHYS             | -   | 100 | -   | mV   |                                                                                              |

| VINUVLO Detection Voltage      | Vvinuvlo                | 3.8 | 4.0 | 4.2 | V    | V <sub>VIN</sub> falling detect threshold                                                    |

| VINUVLO Hysteresis Voltage     | V <sub>VINUVHYS</sub>   | -   | 200 | -   | mV   |                                                                                              |

| [LED Abnormal Detection Block] |                         |     |     |     |      |                                                                                              |

| LEDOPEN Detection Voltage      | VLEDOP                  | 0.2 | 0.3 | 0.4 | V    | V <sub>LEDn</sub> falling detect threshold (n = 1 to 24)                                     |

| SHORT Detection Voltage        | VLEDSH                  | 1.8 | 2.0 | 2.2 | V    | $V_{LEDn}$ rising detect threshold<br>(n = 1 to 24)<br>LEDSHx[7:0] = 0x21h<br>(x = 01 to 24) |

| Diagnosis Enable VIN Voltage   | VIN_DEN                 | 6.3 | 7.0 | 7.7 | V    | DENVOLT[3:0] = 0x7h                                                                          |

Electrical Characteristic - continued (Unless otherwise specified:  $V_{IN}$  = 13 V, Tj = -40 °C to +150 °C)

| Parameter                        | Symbol              | Min                          | Тур  | Max                         | Unit | Condition                                  |

|----------------------------------|---------------------|------------------------------|------|-----------------------------|------|--------------------------------------------|

| [EN Input Pin]                   |                     |                              |      |                             |      |                                            |

| EN Pin Input Current             | I <sub>EN</sub>     | 2.5                          | 5    | 10                          | μA   | V <sub>EN</sub> = 5.0 V                    |

| EN Input Pin High Voltage        | V <sub>ENH</sub>    | 0.75 x<br>V <sub>VREG5</sub> | -    | V <sub>IN</sub>             | V    |                                            |

| EN Input Pin Low Voltage         | V <sub>ENL</sub>    | -0.2                         | -    | 0.2 x<br>V <sub>VREG5</sub> | V    |                                            |

| [LOGIC Input (CS0, CS1, CS2, CS3 | )]                  |                              |      |                             |      |                                            |

| CSx Pin Output Current           | Icsx                | -10                          | -5   | -                           | μA   | (x = 0,1,2,3)<br>$V_{CSx} = 0.0 \text{ V}$ |

| CSx Pin Setting Voltage          | V <sub>CSxSET</sub> | -                            | -    | 2.5                         | V    |                                            |

| [LOGIC Input (PWMIN)]            |                     |                              |      |                             |      |                                            |

| PWMIN Pin Input Current          | I <sub>PWMIN</sub>  | 20                           | 50   | 100                         | μA   | V <sub>PWMIN</sub> = 5.0 V                 |

| PWMIN Input Pin High Voltage     | V <sub>PWMINH</sub> | 0.75 x<br>V <sub>VREG5</sub> | -    | V <sub>VREG5</sub> + 0.2    | V    |                                            |

| PWMIN Input Pin Low Voltage      | VPWMINL             | -0.2                         | -    | 0.2 x<br>V <sub>VREG5</sub> | V    |                                            |

| [LOGIC Input (RX)]               |                     |                              |      |                             |      |                                            |

| RX Input Pin High Voltage        | V <sub>RXH</sub>    | 0.75 x<br>V <sub>VREG5</sub> | -    | V <sub>VREG5</sub> + 0.2    | V    |                                            |

| RX Input Pin Low Voltage         | $V_{RXL}$           | -0.2                         | -    | 0.2 x<br>V <sub>VREG5</sub> | V    |                                            |

| [LOGIC Output Block (PWMOUT)]    |                     |                              |      | _                           |      |                                            |

| Output High Voltage              | Vоитн               | 0.75 x<br>V <sub>VREG5</sub> | -    | V <sub>VREG5</sub><br>+ 0.2 | V    | I <sub>PWMOUT</sub> = -1 mA                |

| Output Low Voltage               | Voutl               | -                            | -    | 0.2                         | V    | I <sub>PWMOUT</sub> = +1 mA                |

| [LOGIC Output Block (TX) Block]  |                     |                              |      |                             |      |                                            |

| Output High Voltage              | V <sub>TXH</sub>    | 0.75 x<br>V <sub>VREG5</sub> | -    | V <sub>VREG5</sub> + 0.2    | V    | I <sub>TX</sub> = -1 mA                    |

| Output Low Voltage               | $V_{TXL}$           | -                            | -    | 0.2 x<br>V <sub>VREG5</sub> | V    | I <sub>TX</sub> = +1 mA                    |

| [FAILB Output Block]             |                     |                              |      |                             |      |                                            |

| FAILB Pin ON Resistance          | RFAILB              | 0.30                         | 0.65 | 1.00                        | kΩ   | I <sub>FAILB</sub> = 1 mA                  |

| FAILB Pin Leak Current           | ILEAKFAILB          | -                            | -    | 10                          | μA   | V <sub>FAILB</sub> = 5.0 V                 |

# **Typical Performance Curve**

(Unless otherwise specified  $V_{IN}$  = 13 V, Tj = -40 °C to +150 °C,  $C_{VREG5}$  = 4.7  $\mu$ F)

Figure 10. Circuit Current vs Temperature

Figure 11. Standby Current vs Temperature

Figure 12. VREG5 Pin Output Voltage vs Temperature

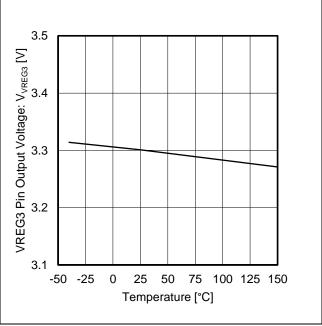

Figure 13. VREG3 Pin Output Voltage vs Temperature

# **Typical Performance Curve - continued**

(Unless otherwise specified  $V_{IN}$  = 13 V, Tj = -40 °C to +150 °C ,  $C_{VREG5}$  = 4.7  $\mu$ F)

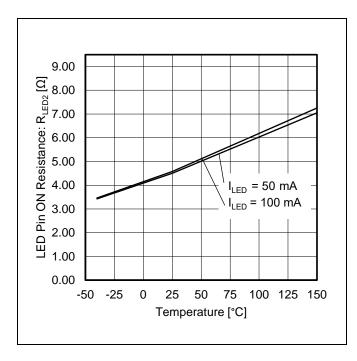

Figure 14. LED Pin Ron vs Temperature

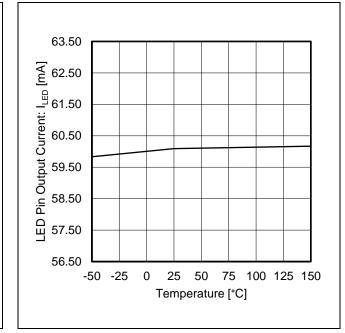

Figure 15. LED Pin Output Current vs Temperature

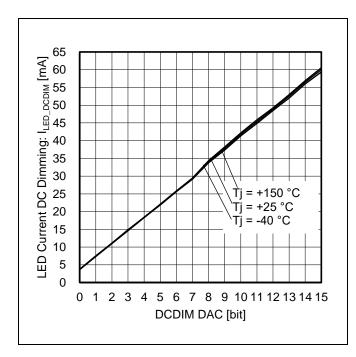

Figure 16. LED Pin Output Current DC Dimming vs DCDIM DAC

Figure 17. PWM Frequency vs Temperature

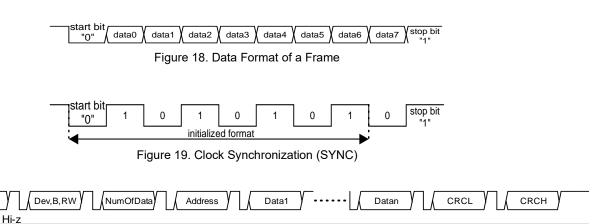

RX

ΤX

SYNC

# **Functions of Logic Block**

#### 1. UART Protocol and AC Electrical Characteristics

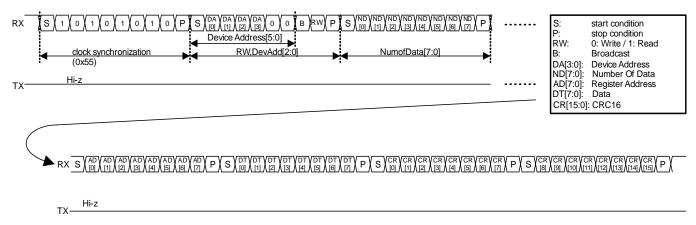

This device has a UART Interface (Universal Asynchronous Receiver-Transmitter). This interface uses the RX (Receiver) and TX (Transmitter) pins for communication. The initial value of UART communication RX and TX is "High". The format of a frame consists of 10-bit: start bit, 8-bit data and stop bit. Data is sent from LSB first to MSB last.

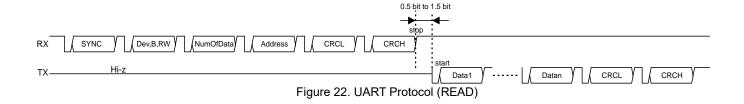

For read command, MCU must synchronize each frame of UART start bit and strobe data at 50 % to provide enough margin to ensure successful communication.

Figure 20. UART Protocol (WRITE)

Figure 21. Detail of UART Protocol (WRITE)

# Functions of Logic Block - continued

# 2. UART AC Timing

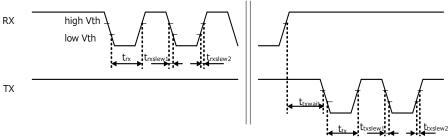

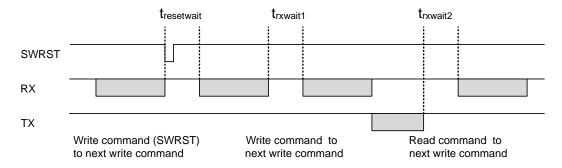

Figure 23. UART AC Timing

Figure 24. UART Inter-command Timing

Table 4. UART AC Characteristics Recommended Operation Condition (Unless otherwise specified,  $V_{IN}$  =13 V ,Tj = -40 °C to +150 °C)

| Parameter                 | Symbol           |     | Rating |                        | Unit  | Comments                                             |

|---------------------------|------------------|-----|--------|------------------------|-------|------------------------------------------------------|

| Farameter                 | Symbol           | Min | Тур    | Max                    | Offic | Comments                                             |

| RX transfer time          | t <sub>rx</sub>  | 1.0 | -      | 10.0                   | μs    |                                                      |

| TX transfer time          | t <sub>tx</sub>  | 1.0 | -      | 10.0                   | μs    |                                                      |

| TX output delay time      | ttxwait          | 0.5 | 1.0    | 1.5                    | bit   |                                                      |

| RX slew rate High to Low  | trxslew1         | -   | -      | t <sub>rx</sub> x 10 % | μs    |                                                      |

| RX slew rate Low to High  | trxslew2         | -   | -      | t <sub>rx</sub> x 10 % | μs    |                                                      |

| TX slew rate High to Low  | ttxslew1         | -   | -      | t <sub>tx</sub> x 10 % | μs    |                                                      |

| TX slew rate Low to High  | ttxslew2         | -   | -      | t <sub>tx</sub> x 10 % | μs    |                                                      |

| RX to RX wait time        | trxwait1         | 2.0 | -      | -                      | μs    | The time interval between continuous write commands. |

| TX to RX wait time        | <b>t</b> rxwait2 | 2.0 | -      | ı                      | μs    | The time interval between read and write commands.   |

| RX to RX wait after SWRST | tresetwait       | 100 | -      | -                      | μs    | The time required after the software reset write.    |

(Output load capacitance : 15 pF)

# Functions of Logic Block - continued

#### 3 **UART Protocol**

#### **Initialize Format**

| bit7 | bit6 | bit5 | bit4 bit3 |   | bit2 | bit1 | bit0 |

|------|------|------|-----------|---|------|------|------|

| 0    | 1    | 0    | 1         | 0 | 1    | 0    | 1    |

This interface receives SYNC frame 0x55h (0b01010101) to calculate the baudrate of the incoming UART command. It generates internal sampling time based on the computed baudrate (1-bit period / 2). After receiving the SYNC frame, this interface expects succeeding frames have the same baudrate as that of the SYNC frame. If incorrect input timing occurred, it may trigger communication error.

#### 3.2 Device Address, Broadcast, Read/Write

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2  | bit1 | bit0 |

|------|------|------|------|------|-------|------|------|

| RW   | В    |      |      | DA   | [5:0] |      |      |

| bit     | Parameter      | Function                                                                                                                                            |

|---------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| DA[5:0] | Device Address | We can set from "0b000000" to "0b001111".  DA[0] = CS0 setting  DA[1] = CS1 setting  DA[2] = CS2 setting  DA[3] = CS3 setting  DA[4] = 0  DA[5] = 0 |

#### Note:

- 1. When the CSx (x = 0 to 3) pin are OPEN, DA[5:0] = 0b0000000.

- When the CSx pin short to GND, DA[n] is "High", inverted operation. (n = 0 to 5) When the CSx pin set to over 4.5 V (Typ), DA[n] is "Low", inverted operation.

| bit | Parameter | Function                                             |

|-----|-----------|------------------------------------------------------|

| D   | Proodoot  | 0: Access the device that matched the device address |

| В   | Broadcast | 1: Access all devices connected to the UART line.    |

# Note:

- Broadcast is not possible for Read access

- 2. If B = 1, device address setting is ignored.

| bit | Parameter  | Function                       |

|-----|------------|--------------------------------|

| RW  | Read/Write | 0: Write access 1: Read access |

# 3 UART Protocol - continued

#### 3.3 Number of Data

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

NumOfData[7:0]

| bit             | Parameter                  | Function                       |  |  |  |  |  |  |

|-----------------|----------------------------|--------------------------------|--|--|--|--|--|--|

| NumOfData [7:0] | Number of Data transferred | Available to use from 1 to 27. |  |  |  |  |  |  |

#### Note:

- 1. Available data buffer for multiple write access is 27 data.

- 2. NumOfData = 0 is not valid.

- 3. NumOfData > 27 is not valid.

# 3.4 Register Address

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

RegAddr [7:0]

| bit           | Parameter        | Function                                       |

|---------------|------------------|------------------------------------------------|

| RegAddr [7:0] | Register Address | It is available to access from 0x00h to 0x5Eh. |

# 3.5 Data

bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0

Data [7:0]

| bit        | Parameter | value           |  |  |  |  |  |  |

|------------|-----------|-----------------|--|--|--|--|--|--|

| Data [7:0] | Data      | 0x00h to 0xFFh. |  |  |  |  |  |  |

#### 3 UART Protocol - continued

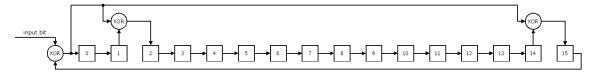

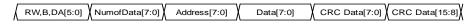

#### 3.6 CRC

16bit LSB First:

Cyclic Redundancy Check (CRC)

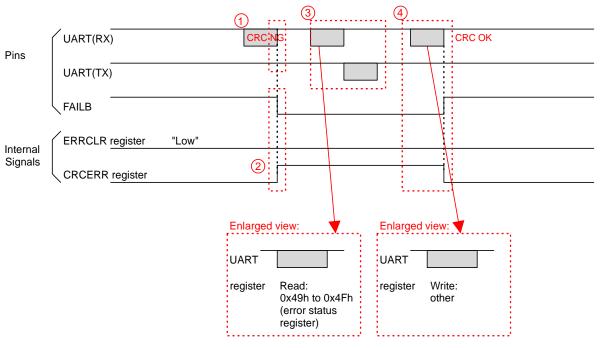

The CRC-16 is used to detect errors in the UART I/F Communication data.

The data included for CRC computation are the following: Device address, Number of Data, Address Data, Write or Read Data.

During write communication (both write and read command has write communication),

The last 2 frames received in a write communication is a 16-bit CRC data that will be compared to the computed CRC. If CRC data is the same with the computed CRC, Register Map will be updated with all the written data.

Else, All written data will be disregarded, CRC Status Register becomes High and FAILB output becomes "Low".

CRC Error is released after sending UART Write command with correct data (Matched CRC Calculation). UART Read command will not release CRC Error.

CRC Polynomial: CRC Polynomial is expressed as CRC16-IBM  $x^{16}+x^{15}+x^2+1$

#### Bit Order LSB First:

The CRC calculation starts with LSB and proceeds from bit[0] to bit[7] of each byte.

Figure 25. CRC Polynomial

## **CRC Initial Setting:**

The initial value is "0x0000h".

The CRC calculate registers are reset to the initial value of "0x0000h" prior to each CRC bytes calculation.

#### Example for

Figure 26. CRC Data Format

| RW,B,DA[5:0]:   | DA[7:0]  | = 0x1Ah | to | DA[0:7]  | = 0x58h |

|-----------------|----------|---------|----|----------|---------|

| NumOfData[7:0]: | ND[7:0]  | = 0x02h | to | ND[0:7]  | = 0x40h |

| Address[7:0]:   | AD[7:0]  | = 0xA5h | to | AD[0:7]  | = 0xA5h |

| Data[7:0]:      | DT[7:0]  | = 0x5Ah | to | DT[0:7]  | = 0x5Ah |

| CRC Data[7:0]:  | CR[7:0]  | = 0xBAh | to | CR[0:7]  | = 0xB3h |

| CRC Data[15:8]: | CR[15:8] | = 0xCDh | to | CR[8:15] | = 0x5Dh |

$X^{16} + X^{15} + X^2 + 1$

# 3.6 CRC - continued

CRC:

BACD

#### 3. UART Protocol - continued

#### 3.7 Example of UART Protocol

Single device, 1 byte Write (Write to Device #1)

(CS3,CS2,CS1,CS0) = "0101"

B = 0: Target Device receives the data

DevAddr[5:0] = 0x05h: Target Device Address NumOfData[7:0] = 1: 1 byte Write mode

RW = 0: Write

RegAddr[7:0] = 0x02h: Address

Data[7:0] = 0xAAh: Data

Figure 27. UART Protocol of the 1 byte Write to Device #1

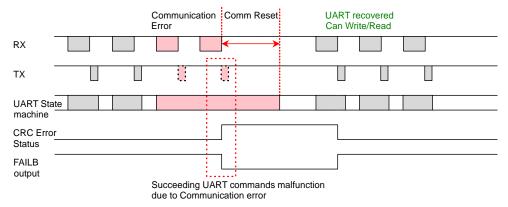

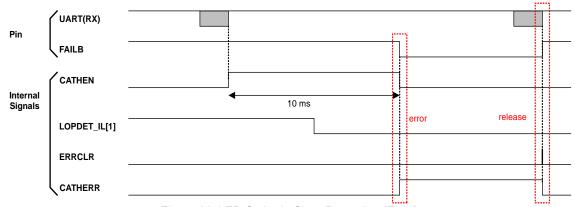

#### 4. Communication Reset

UART IF has a communication reset function. This function can be used to interrupt UART communication and return to idle condition. This function is triggered by setting RX to "High" for atleast 2.75 ms (Typ). This feature can be used to recover from communication. If Communication Reset is executed, it will not affect LED Dimming. When UART is in IDLE condition it does not detect Communication Reset.

Figure 28. Communication Reset

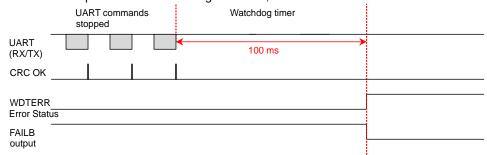

# 5. Watchdog Timer (WDT)

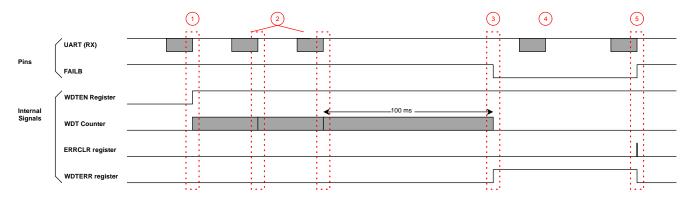

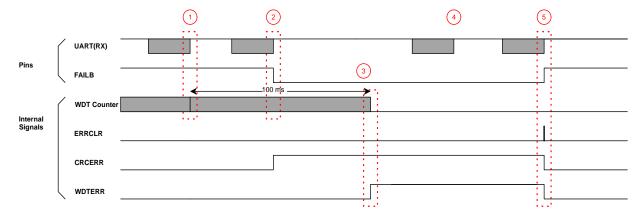

UART IF has a watchdog timer function. This function monitors the RX line for no UART access for 100 ms (Typ) and notifies via status register and FAILB output. This no UART access means no successful UART command (no CRC OK). This function is enabled by WDTEN (initial is "Low") and the status can be checked in WDTERR Status register and can be observed in the FAILB pin output. When detected, it returns the UART state to idle condition and does not affect LED Dimming. Details of the operation is further discussed in Error Control and Error Sequence.

When a device is connected in parallel and is not being accessed, it will not detect WDT

Figure 29. Watchdog Timer

# Functions of Logic Block - continued

# 6. Register Map

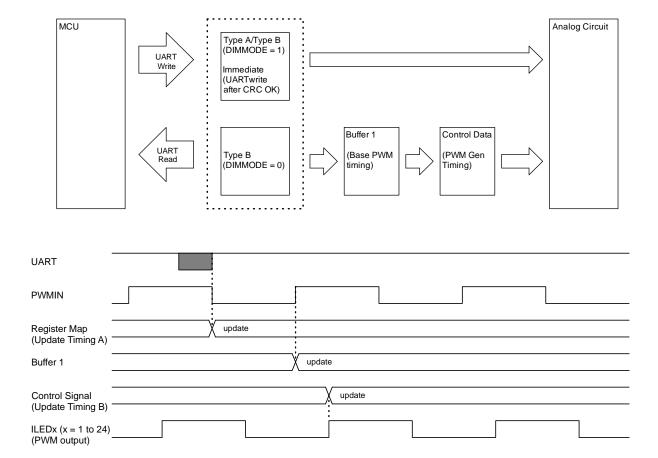

Each registers is updated at the 2 timings.

Reset Condition: "UVLO" condition = VREG3UVLO, VREG5UVLO, VINUVLO, TSD or EN is detected.

Register Update timing for control data:

- A. Updated to the newest data immediately when the data is written.

- B. Updated to the newest data when the next PWM (PWM is internal signal) timing after the data is written.

Figure 30. UART Data Flow

# 6. Register Map - continued

\*Attention:

Please don't access (Write/Read) register except for following registers (0x00h to 0x5Eh) and write "0" in "-". "RESERVED" Registers can be written/read. Do not update.

Address 0x00h to 0x23h (1/3)

| Address       | Address uxuun to ux23n (1/3) |                             |                            |           |                            |                |                              |          |                           |                    |                  |                                       |                                      |                                                                             |

|---------------|------------------------------|-----------------------------|----------------------------|-----------|----------------------------|----------------|------------------------------|----------|---------------------------|--------------------|------------------|---------------------------------------|--------------------------------------|-----------------------------------------------------------------------------|

| Register Name | Address                      | Bit[7]                      | Bit[6]                     | Bit[5]    | Bit[4]                     | Bit[3]         | Bit[2]                       | Bit[1]   | Bit[0]                    | Register<br>Access | initial          | Reset<br>Condition                    | update<br>timing                     | comments                                                                    |

| SYNC          | 0x00                         | PWMFSYNCSET                 | PWMTIM <sup>(Note 2)</sup> | ISETSEL   | SLOPEEN                    | DIMMODE        | PWMPSYNC <sup>(Note 1)</sup> | DIMSTART | SWRST <sup>(Note 1)</sup> | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | PWM phase syncronization and output                                         |

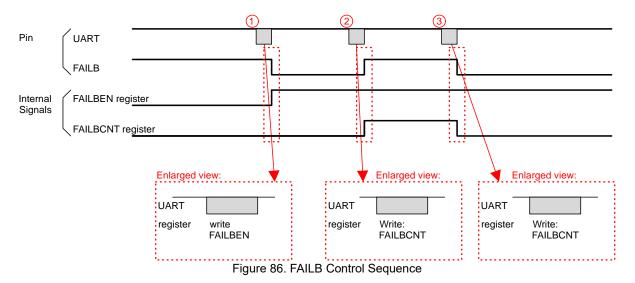

| SYSSET1       | 0x01                         | FAILBCNT                    | FAILBEN                    |           | RESERVED                   |                | PWMFSYNC <sup>(Note 2)</sup> | SYNC     | SET[1:0]                  | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | PWM frequency synchronous setting and SSCG<br>enable, FAILB control setting |

| SYSSET2       | 0x02                         |                             |                            |           | RESI                       | ERVED          |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | Reserved                                                                    |

| SYSSET3       | 0x03                         |                             | ERRMA                      | SK[3:0]   |                            |                | RESE                         | RVED     |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | Error mask for LED open/short, Error mask setting during softstart          |

| LEDENL        | 0x04                         |                             |                            |           | LEDE                       | EN[7:0]        |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | Channel enable for LED1 to LED8                                             |

| LEDENM        | 0x05                         |                             |                            |           | LEDE                       | N[15:8]        |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | Channel enable for LED9 to LED16                                            |

| LEDENH        | 0x06                         |                             |                            |           | LEDEI                      | N[23:16]       |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | Channel enable for LED17 to LED24                                           |

| SYSSET4       | 0x07                         | -                           | ISETLAT                    | AUTOOFF   | ERRCLR <sup>(Note 1)</sup> | RESERVED       | CRCERLAT                     | LSHLAT   | LOPLAT                    | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | Error status and flag latch setting                                         |

| SYSSET5       | 0x08                         | -                           | -                          | RESERVED  | RESERVED                   | CATHEN(Note 1) | TSDWEN                       | WDTEN    | LOPEN                     | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | error enable<br>CATHEN returns '0' automatically                            |

| LEDSHENL      | 0x09                         |                             |                            |           | LSHE                       | N[7:0]         |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | LED short enable                                                            |

| LEDSHENH      | 0x0A                         | -                           | -                          | ISETSH    | ICNT[1:0]                  |                | LSHEN                        | [11:8]   |                           | R/W                | 0x20             | UVLO or<br>SWRST                      | Type A                               | LED short enable, OCP current setting                                       |

| LEDSHTH0102   | 0x0B                         |                             | •                          | •         | LEDSHTH                    | 10102[7:0]     |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | LED short detection voltage for LED1 and LED2                               |

| LEDSHTH0304   | 0x0C                         |                             |                            |           | LEDSHTH                    | 10304[7:0]     |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | LED short detection voltage for LED3 and LED4                               |

| LEDSHTH0506   | 0x0D                         |                             |                            |           | LEDSHTH                    | 10506[7:0]     |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | LED short detection voltage for LED5 and LED6                               |

| LEDSHTH0708   | 0x0E                         |                             |                            |           | LEDSHTH                    | 10708[7:0]     |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | LED short detection voltage for LED7 and LED8                               |

| LEDSHTH0910   | 0x0F                         |                             |                            |           | LEDSHTH                    | 10910[7:0]     |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | LED short detection voltage for LED9 and LED10                              |

| LEDSHTH1112   | 0x10                         |                             |                            |           | LEDSHTH                    | 11112[7:0]     |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | LED short detection voltage for LED11 and LED12                             |

| LEDSHTH1314   | 0x11                         |                             |                            |           | LEDSHTH                    | 11314[7:0]     |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | LED short detection voltage for LED13 and LED14                             |

| LEDSHTH1516   | 0x12                         |                             |                            |           | LEDSHTH                    | 11516[7:0]     |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | LED short detection voltage for LED15 and LED16                             |

| LEDSHTH1718   | 0x13                         |                             |                            |           | LEDSHTH                    | 11718[7:0]     |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | LED short detection voltage for LED17 and LED18                             |

| LEDSHTH1920   | 0x14                         |                             |                            |           | LEDSHTH                    | 11920[7:0]     |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | LED short detection voltage for LED19 and LED20                             |

| LEDSHTH2122   | 0x15                         |                             |                            |           | LEDSHTH                    | 12122[7:0]     |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | LED short detection voltage for LED21 and LED22                             |

| LEDSHTH2324   | 0x16                         |                             |                            |           | LEDSHTH                    | 12324[7:0]     |                              |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | LED short detection voltage for LED23 and LED24                             |

| DENVOLT       | 0x17                         | RESE                        | RVED                       | PWMFF     | REQ[1:0]                   | DENVOLT[3:0]   |                              |          | R/W                       | 0x00               | UVLO or<br>SWRST | Type A                                | DEN threshold voltage                |                                                                             |

| PWMDLY0102    | 0x18                         |                             | PWMDL                      | .Y02[3:0] |                            |                | PWMDLY01[3:0]                |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | PWM delay setting for LED1 and LED2                                         |

| PWMDLY0304    | 0x19                         |                             | PWMDL                      | Y04[3:0]  |                            |                | PWMDLY03[3:0]                |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | PWM delay setting for LED3 and LED4                                         |

| PWMDLY0506    | 0x1A                         |                             | PWMDL                      | Y06[3:0]  |                            |                | PWMDL                        | Y05[3:0] |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | PWM delay setting for LED5 and LED6                                         |

| PWMDLY0708    | 0x1B                         |                             | PWMDL                      | .Y08[3:0] |                            |                | PWMDL                        | Y07[3:0] |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | PWM delay setting for LED7 and LED8                                         |

| PWMDLY0910    | 0x1C                         | PWMDLY10[3:0] PWMDLY09[3:0] |                            |           |                            |                | Y09[3:0]                     |          | R/W                       | 0x00               | UVLO or<br>SWRST | Type A                                | PWM delay setting for LED9 and LED10 |                                                                             |

| PWMDLY1112    | 0x1D                         | PWMDLY12[3:0]               |                            |           |                            |                | PWMDL                        | Y11[3:0] |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | PWM delay setting for LED11 and LED12                                       |

| PWMDLY1314    | 0x1E                         | PWMDLY14[3:0]               |                            |           |                            |                | PWMDLY13[3:0]                |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | PWM delay setting for LED13 and LED14                                       |

| PWMDLY1516    | 0x1F                         | PWMDLY16[3:0]               |                            |           | PWMDLY15[3:0]              |                |                              | R/W      | 0x00                      | UVLO or<br>SWRST   | Type A           | PWM delay setting for LED15 and LED16 |                                      |                                                                             |

| PWMDLY1718    | 0x20                         |                             | PWMDLY18[3:0]              |           |                            |                | PWMDLY17[3:0]                |          |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | PWM delay setting for LED17 and LED18                                       |

| PWMDLY1920    | 0x21                         |                             | PWMDL                      | Y20[3:0]  |                            |                | PWMDL                        | Y19[3:0] |                           | R/W                | 0x00             | UVLO or<br>SWRST                      | Type A                               | PWM delay setting for LED19 and LED20                                       |