# Silicon Carbide (SiC) Module - EliteSiC, 6 mohm, 1200 V, SiC M3 MOSFET, 2-PACK Half Bridge Topology, F2 Package with HPS DBC

# NXH006P120M3F2PTHG

The NXH006P120M3F2PTHG is a power module containing 6 m $\Omega$  / 1200 V SiC MOSFET half-bridge and a thermistor with HPS DBC in an F2 package.

### **Features**

- $6 \text{ m}\Omega$  / 1200 V M3S SiC MOSFET Half-Bridge

- HPS DBC

- Thermistor

- Pre-Applied Thermal Interface Material (TIM)

- Press-Fit Pins

- These Devices are Pb-Free, Halide Free and are RoHS Compliant

## **Typical Applications**

- Solar Inverter

- Uninterruptible Power Supplies

- Electric Vehicle Charging Stations

- Industrial Power

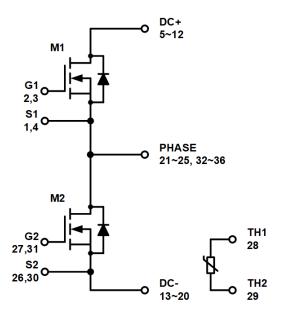

Figure 1. NXH006P120M3F2 Schematic Diagram

### **PACKAGE PICTURE**

PIM36 56.7x42.5 (PRESS FIT) CASE 180BY

### **MARKING DIAGRAM**

NXH006P120M3F2PTHG ATYYWW

$\begin{array}{ll} {\sf NXH006P120M3F2PTHG} = {\sf Specific\ Device\ Code} \\ {\sf AT} &= {\sf Assembly\ \&\ Test\ Site} \\ \end{array}$

YWW = Year and Work Week

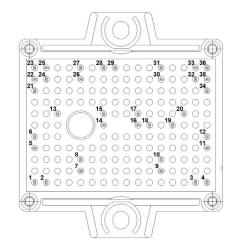

### **PIN CONNECTIONS**

See Pin Function Description for pin names

### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 4 of this data sheet.

# PIN FUNCTION DESCRIPTION

| Pin | Name  | Description                          |

|-----|-------|--------------------------------------|

| 1   | S1    | Q1 Kelvin Emitter (High side switch) |

| 2   | G1    | Q1 Gate (High side switch)           |

| 3   | G1    | Q1 Gate (High side switch)           |

| 4   | S1    | Q1 Kelvin Emitter (High side switch) |

| 5   | DC+   | DC Positive Bus connection           |

| 6   | DC+   | DC Positive Bus connection           |

| 7   | DC+   | DC Positive Bus connection           |

| 8   | DC+   | DC Positive Bus connection           |

| 9   | DC+   | DC Positive Bus connection           |

| 10  | DC+   | DC Positive Bus connection           |

| 11  | DC+   | DC Positive Bus connection           |

| 12  | DC+   | DC Positive Bus connection           |

| 13  | DC-   | DC Negative Bus connection           |

| 14  | DC-   | DC Negative Bus connection           |

| 15  | DC-   | DC Negative Bus connection           |

| 16  | DC-   | DC Negative Bus connection           |

| 17  | DC-   | DC Negative Bus connection           |

| 18  | DC-   | DC Negative Bus connection           |

| 19  | DC-   | DC Negative Bus connection           |

| 20  | DC-   | DC Negative Bus connection           |

| 21  | PHASE | Center point of half bridge          |

| 22  | PHASE | Center point of half bridge          |

| 23  | PHASE | Center point of half bridge          |

| 24  | PHASE | Center point of half bridge          |

| 25  | PHASE | Center point of half bridge          |

| 26  | S2    | Q2 Kelvin Emitter (Low side switch)  |

| 27  | G2    | Q2 Gate (Low side switch)            |

| 28  | TH1   | Thermistor Connection 1              |

| 29  | TH2   | Thermistor Connection 2              |

| 30  | S2    | Q2 Kelvin Emitter (Low side switch)  |

| 31  | G2    | Q2 Gate (Low side switch)            |

| 32  | PHASE | Center point of half bridge          |

| 33  | PHASE | Center point of half bridge          |

| 34  | PHASE | Center point of half bridge          |

| 35  | PHASE | Center point of half bridge          |

| 36  | PHASE | Center point of half bridge          |

### **MAXIMUM RATINGS**

| Rating                                                      | Symbol              | Value      | Unit       |

|-------------------------------------------------------------|---------------------|------------|------------|

| SIC MOSFET                                                  |                     |            | •          |

| Drain-Source Voltage                                        | V <sub>DSS</sub>    | 1200       | V          |

| Gate-Source Voltage                                         | V <sub>GS</sub>     | +22/-10    | V          |

| Continuous Drain Current @ $T_c$ = 80 °C ( $T_J$ = 175 °C)  | I <sub>D</sub>      | 191        | Α          |

| Pulsed Drain Current (T <sub>J</sub> = 175 °C)              | I <sub>Dpulse</sub> | 382        | Α          |

| Maximum Power Dissipation @ $T_c$ = 80 °C ( $T_J$ = 175 °C) | P <sub>tot</sub>    | 556        | W          |

| Minimum Operating Junction Temperature                      | T <sub>JMIN</sub>   | -40        | °C         |

| Maximum Operating Junction Temperature                      | T <sub>JMAX</sub>   | 175        | °C         |

| THERMAL PROPERTIES                                          |                     |            |            |

| Storage Temperature Range                                   | T <sub>stg</sub>    | -40 to 150 | °C         |

| TIM Layer Thickness                                         | T <sub>TIM</sub>    | 160 ±20    | μ <b>m</b> |

| INSULATION PROPERTIES                                       |                     |            |            |

| Isolation Test Voltage, t = 1 s, 60 Hz                      | V <sub>is</sub>     | 4800       | $V_{RMS}$  |

| Creepage Distance                                           |                     | 12.7       | mm         |

| СТІ                                                         |                     | 600        |            |

| Substrate Ceramic Material                                  |                     | HPS        |            |

| Substrate Ceramic Material Thickness                        |                     | 0.38       | mm         |

| Substrate Warpage (Note 2)                                  | W                   | Max 0.18   | mm         |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

## **RECOMMENDED OPERATING RANGES**

| Rating                                | Symbol | Min | Max | Unit |

|---------------------------------------|--------|-----|-----|------|

| Module Operating Junction Temperature | $T_J$  | -40 | 150 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = 25 °C unless otherwise noted)

| Parameter                       | Symbol              | Test Conditions                                                         | Min  | Тур   | Max | Unit |

|---------------------------------|---------------------|-------------------------------------------------------------------------|------|-------|-----|------|

| SIC MOSFET CHARACTERISTICS      |                     |                                                                         |      |       |     |      |

| Zero Gate Voltage Drain Current | I <sub>DSS</sub>    | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 1200 V                         | _    | _     | 300 | μΑ   |

| Drain-Source On Resistance      | R <sub>DS(ON)</sub> | V <sub>GS</sub> = 18 V, I <sub>D</sub> = 100 A, T <sub>J</sub> = 25 °C  | _    | 6.5   | 8   | mΩ   |

|                                 |                     | V <sub>GS</sub> = 18 V, I <sub>D</sub> = 100 A, T <sub>J</sub> = 125 °C | _    | 10.8  | -   |      |

|                                 |                     | V <sub>GS</sub> = 18 V, I <sub>D</sub> = 100 A, T <sub>J</sub> = 150 °C | _    | 12.4  | -   |      |

|                                 |                     | V <sub>GS</sub> = 18 V, I <sub>D</sub> = 100 A, T <sub>J</sub> = 175 °C | _    | 14.6  | -   |      |

| Gate-Source Threshold Voltage   | V <sub>GS(TH)</sub> | $V_{GS} = V_{DS}$ , $I_D = 80 \text{ mA}$                               | 1.8  | 2.8   | 4.4 | V    |

| Gate Leakage Current            | I <sub>GSS</sub>    | $V_{GS} = -10 \text{ V} / 20 \text{ V}, V_{DS} = 0 \text{ V}$           | -400 | _     | 400 | nA   |

| Gate-Resistance                 | $R_{G}$             | f = 1 MHz                                                               | _    | 0.375 | -   | Ω    |

| Input Capacitance               | C <sub>ISS</sub>    | $V_{DS} = 800 \text{ V}, V_{GS} = 0 \text{ V}, f = 100 \text{ kHz}$     | _    | 11914 | -   | pF   |

| Reverse Transfer Capacitance    | C <sub>RSS</sub>    |                                                                         | _    | 48    | -   |      |

| Output Capacitance              | C <sub>OSS</sub>    |                                                                         | _    | 669   | -   |      |

<sup>1.</sup> Refer to ELECTRICAL CHĂRACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

<sup>2.</sup> Height difference between horizontal plane and substrate copper bottom.

# **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = 25 °C unless otherwise noted) (continued)

| Parameter                             | Symbol              | Test Conditions                                                                                             | Min | Тур   | Max | Unit |

|---------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| SIC MOSFET CHARACTERISTICS            | •                   |                                                                                                             |     |       |     | •    |

| Total Gate Charge                     | Q <sub>G(TOTA</sub> | $V_{DS} = 800 \text{ V}, V_{GS} = -5/20 \text{ V}, I_D = 100 \text{ A}$                                     | -   | 622   | -   | nC   |

| Gate-Source Charge                    | $Q_{GS}$            |                                                                                                             | -   | 109   | _   | nC   |

| Gate-Drain Charge                     | $Q_{GD}$            |                                                                                                             | -   | 120   | _   | nC   |

| Turn-on Delay Time                    | t <sub>d(on)</sub>  | T <sub>J</sub> = 25 °C                                                                                      | -   | 40.53 | _   | ns   |

| Rise Time                             | t <sub>r</sub>      | $V_{DS} = 600 \text{ V}, I_D = 100 \text{ A}$<br>$V_{GS} = -5 \text{ V} / 18 \text{ V}, R_G = 1 \Omega$     | -   | 13.61 | _   |      |

| Turn-off Delay Time                   | t <sub>d(off)</sub> |                                                                                                             | -   | 109   | -   | 1    |

| Fall Time                             | t <sub>f</sub>      |                                                                                                             | -   | 8.54  | _   |      |

| Turn-on Switching Loss per Pulse      | E <sub>ON</sub>     |                                                                                                             | -   | 0.89  | _   | mJ   |

| Turn-off Switching Loss per Pulse     | E <sub>OFF</sub>    |                                                                                                             | -   | 0.44  | _   | 1    |

| Turn-on Delay Time                    | t <sub>d(on)</sub>  | T <sub>J</sub> = 150 °C                                                                                     | -   | 38.21 | _   | ns   |

| Rise Time                             | t <sub>r</sub>      | $V_{DS} = 600 \text{ V}, I_{D} = 100 \text{ A}$<br>$V_{GS} = -5 \text{ V} / 18 \text{ V}, R_{G} = 1 \Omega$ | -   | 12.92 | _   | 1    |

| Turn-off Delay Time                   | t <sub>d(off)</sub> | as a garage                                                                                                 | -   | 118   | _   | 1    |

| Fall Time                             | t <sub>f</sub>      |                                                                                                             | -   | 8.73  | _   | 1    |

| Turn-on Switching Loss per Pulse      | E <sub>ON</sub>     |                                                                                                             | -   | 1.12  | _   | mJ   |

| Turn-off Switching Loss per Pulse     | E <sub>OFF</sub>    |                                                                                                             | -   | 0.44  | _   | 1    |

| Diode Forward Voltage                 | $V_{SD}$            | I <sub>D</sub> = 100 A, T <sub>J</sub> = 25 °C                                                              | -   | 5.31  | 7.5 | V    |

|                                       |                     | I <sub>D</sub> = 100 A, T <sub>J</sub> = 125 °C                                                             | -   | 4.91  | _   | 1    |

|                                       |                     | I <sub>D</sub> = 100 A, T <sub>J</sub> = 150 °C                                                             | -   | 4.82  | _   | 1    |

| Thermal Resistance - Chip-to-Case     | R <sub>thJC</sub>   | M1, M2                                                                                                      | -   | 0.171 | _   | °C/W |

| Thermal Resistance – Chip-to-Heatsink | R <sub>thJH</sub>   | Thermal grease, Thickness = 2 Mil +2%, A = 2.8 W/mK                                                         | -   | 0.288 | -   | °C/W |

| THERMISTOR CHARACTERISTICS            | •                   |                                                                                                             |     | •     |     | •    |

| Nominal Resistance                    | R <sub>25</sub>     | T <sub>NTC</sub> = 25 °C                                                                                    | -   | 5     | _   | kΩ   |

| Nominal Resistance                    | R <sub>100</sub>    | T <sub>NTC</sub> = 100 °C                                                                                   | -   | 493   | _   | Ω    |

| Nominal Resistance                    | R <sub>150</sub>    | T <sub>NTC</sub> = 150 °C                                                                                   | -   | 159.5 | _   | Ω    |

| Deviation of R <sub>100</sub>         | ΔR/R                | T <sub>NTC</sub> = 100 °C                                                                                   | -5  | -     | 5   | %    |

| Power Dissipation – Recommended Limit | P <sub>D</sub>      | 0.15 mA, non-self-heating effect                                                                            | -   | 0.1   | -   | mW   |

| Power Dissipation – Absolute Maximum  | P <sub>D</sub>      | 5 mA                                                                                                        | -   | 34.2  | _   | mW   |

| Power Dissipation Constant            |                     |                                                                                                             | -   | 1.4   | _   | mW/K |

| B-value                               | <u> </u>            | B(25/50), tolerance ±2%                                                                                     | -   | 3375  | -   | K    |

| B-value                               | 1                   | B(25/100), tolerance ±2%                                                                                    | -   | 3436  | _   | К    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

# **ORDERING INFORMATION**

| Orderable Part Number | Marking            | Package                                                                                                       | Shipping                |

|-----------------------|--------------------|---------------------------------------------------------------------------------------------------------------|-------------------------|

| NXH006P120M3F2PTHG    | NXH006P120M3F2PTHG | F2HALFBR: Case 180BY Press-fit Pins with pre-applied thermal interface material (TIM) (Pb-Free / Halide Free) | 20 Units / Blister Tray |

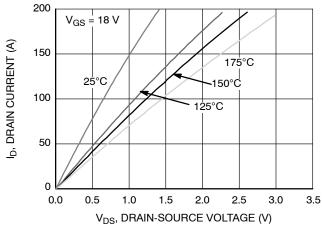

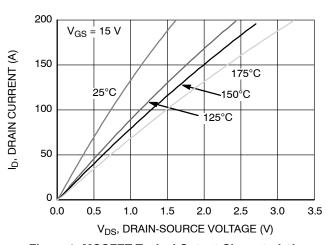

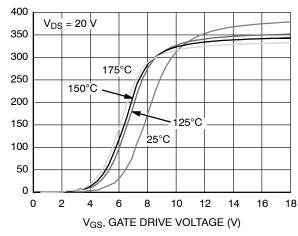

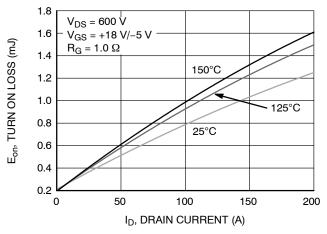

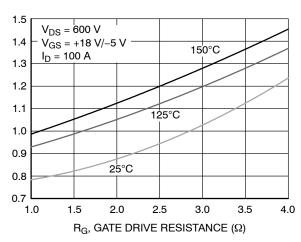

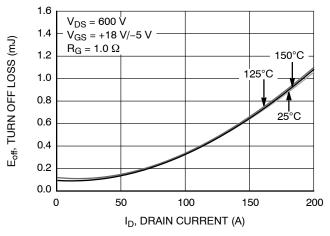

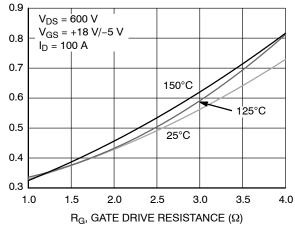

### **TYPICAL CHARACTERISTIC**

(M1/M2 SiC MOSFET CHARACTERISTIC)

ID, DRAIN CURRENT (A)

Figure 2. MOSFET Typical Output Characteristic

Figure 3. MOSFET Typical Output Characteristic

Figure 4. MOSFET Typical Transfer Characteristic

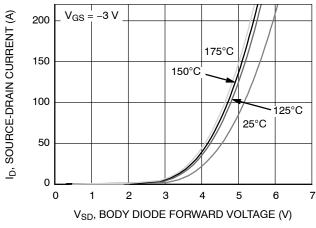

Figure 5. Body Diode Forward Characteristic

Figure 6. MOSFET  $R_{DS(ON)}$  vs.  $I_D$

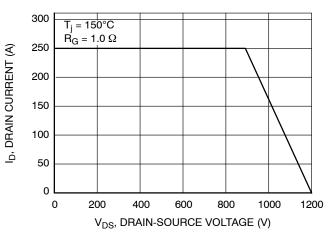

Figure 7. MOSFET RBSOA

### **TYPICAL CHARACTERISTIC**

(M1/M2 SiC MOSFET CHARACTERISTIC)

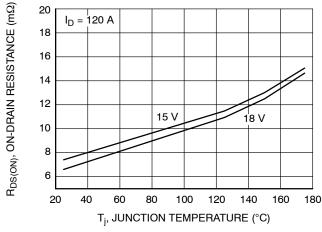

Figure 8. MOSFET  $R_{DS(ON)}$  vs.  $T_j$

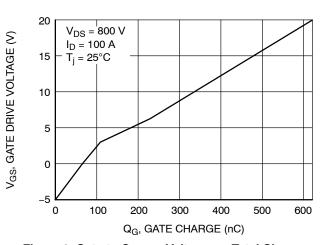

Figure 9. Gate-to-Source Voltage vs. Total Charge

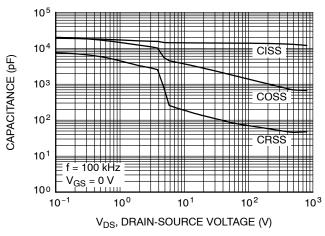

Figure 10. Capacitance vs. Drain-to-Source Voltage

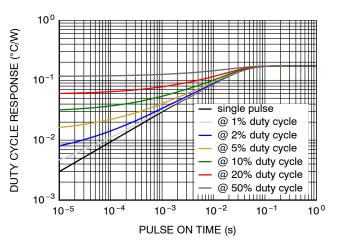

Figure 11. MOSFET Junction-to-Case Transient Thermal Impedance

### **TYPICAL CHARACTERISTIC**

(M1/M1 SiC MOSFET SWITCHING CHARACTERISTIC)

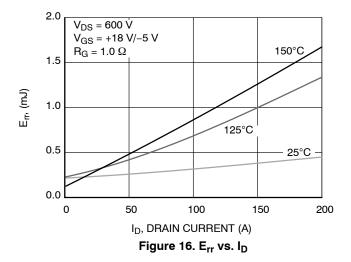

Eon, TURN ON LOSS (mJ)

Eoff, TURN OFF LOSS (mJ)

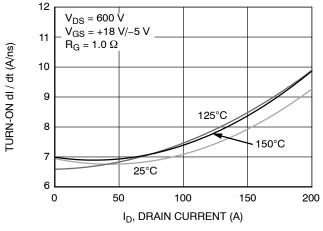

Figure 12. Typical Switching Loss Eon vs. ID

Figure 13. Typical Switching Loss Eon vs. R<sub>G</sub>

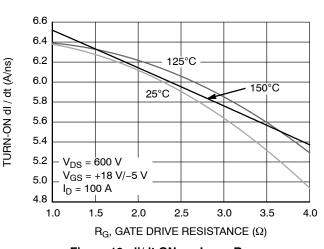

Figure 14. Typical Switching Loss Eoff vs. ID

Figure 15. Typical Switching Loss  $E_{\text{off}}$  vs.  $R_{\text{G}}$

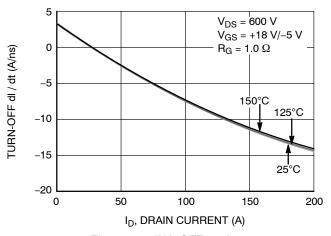

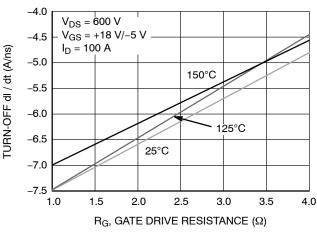

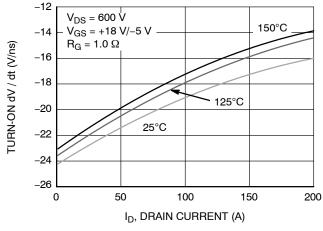

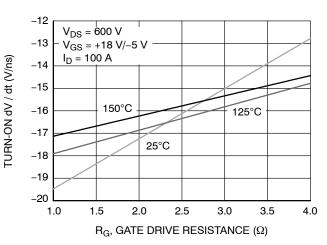

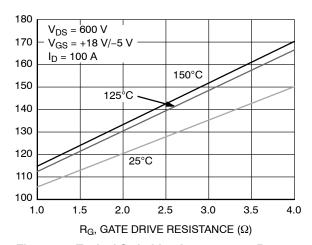

### **TYPICAL CHARACTERISTIC**

(M1/M1 SiC MOSFET SWITCHING CHARACTERISTIC)

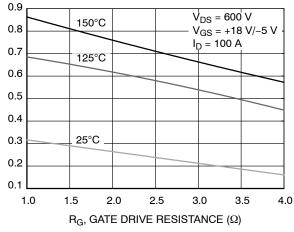

Figure 18. di/dt ON vs.  $I_{D}$

Figure 19. di/dt ON vs.  $I_D$  vs.  $R_G$

Figure 20. di/dt OFF vs. I<sub>D</sub>

Figure 21. di/dt OFF vs. R<sub>G</sub>

Figure 22. dv/dt ON vs. ID

Figure 23. dv/dt ON vs. R<sub>G</sub>

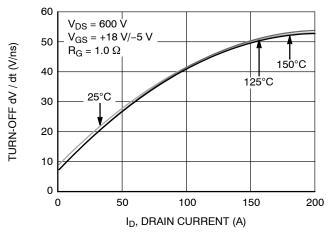

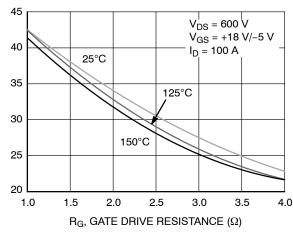

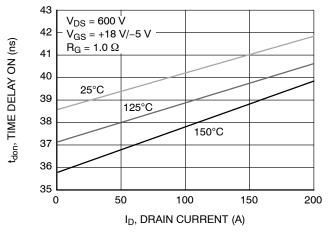

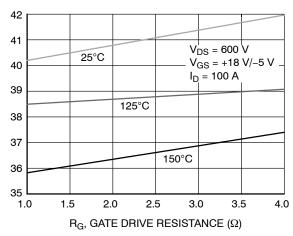

### TYPICAL CHARACTERISTIC

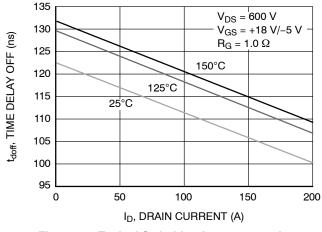

(M1/M1 SiC MOSFET SWITCHING CHARACTERISTIC)

TURN-OFF dV / dt (V/ns)

t<sub>don</sub>, TIME DELAY ON (ns)

Figure 24. dv/dt OFF vs.  $I_D$  vs.  $I_D$

Figure 25. dv/dt OFF vs. I<sub>D</sub> vs. R<sub>G</sub>

Figure 26. Typical Switching Loss  $t_{don}$  vs.  $I_D$

Figure 27. Typical Switching Loss t<sub>don</sub> vs. R<sub>G</sub>

Figure 28. Typical Switching Loss t<sub>doff</sub> vs. I<sub>D</sub>

Figure 29. Typical Switching Loss t<sub>doff</sub> vs. R<sub>G</sub>

doff, TIME DELAY OFF (ns)

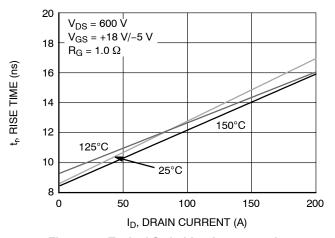

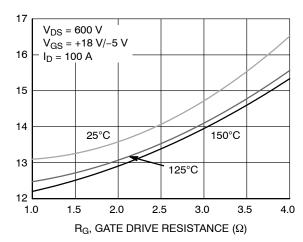

### **TYPICAL CHARACTERISTIC**

(M1/M1 SiC MOSFET SWITCHING CHARACTERISTIC)

t, RISE TIME (ns)

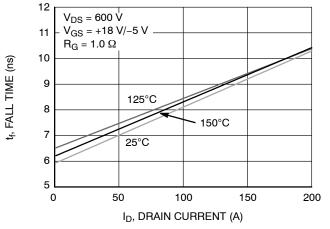

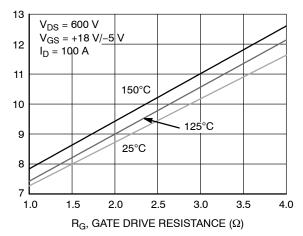

tf, FALL TIME (ns)

Figure 30. Typical Switching Loss  $t_r$  vs.  $I_D$

Figure 31. Typical Switching Loss t<sub>r</sub> vs. R<sub>G</sub>

Figure 32. Typical Switching Loss tf vs. ID

Figure 33. Typical Switching Loss tf vs. RG

Table 1. FOSTER NETWORKS - M1, M2

|                  | M1          |             | M           | 2           |  |

|------------------|-------------|-------------|-------------|-------------|--|

| Foster Element # | Rth (K/W)   | Cth (Ws/K)  | Rth (K/W)   | Cth (Ws/K)  |  |

| 1                | 0.007128913 | 0.014726553 | 0.007362625 | 0.014806718 |  |

| 2                | 0.012161919 | 0.065733420 | 0.012250209 | 0.068123520 |  |

| 3                | 0.007181004 | 0.193791778 | 0.008111627 | 0.172318664 |  |

| 4                | 0.016285510 | 0.295329029 | 0.015759800 | 0.310819905 |  |

| 5                | 0.129692183 | 0.184203426 | 0.130218477 | 0.185033159 |  |

Table 2. CAUER NETWORKS - M1, M2

|                 | M1          |             | N           | 12          |

|-----------------|-------------|-------------|-------------|-------------|

| Cauer Element # | Rth (K/W)   | Cth (Ws/K)  | Rth (K/W)   | Cth (Ws/K)  |

| 1               | 0.014060112 | 0.010299454 | 0.014544451 | 0.010347568 |

| 2               | 0.031541811 | 0.030614887 | 0.032745986 | 0.030654208 |

| 3               | 0.047951752 | 0.086377861 | 0.047636505 | 0.089568373 |

| 4               | 0.041739058 | 0.071218233 | 0.042559339 | 0.069836041 |

| 5               | 0.037156796 | 0.209773695 | 0.036216457 | 0.216319284 |

### PIM36 56.70x42.50x12.00 CASE 180BY ISSUE E **DATE 20 DEC 2023** NOTES: 1. CONTROLLING DIMENSION: MILLIMETERS 2. PIN POSITION TOLERANCE IS ± 0.4mm PACKAGE MARKING LOCATION 3. PRESS FIT PIN MILLIMETERS NOM. MAX. DIM MIN. 11.65 12.35 12.00 Α1 16.10 16.50 16.90 A2 0.00 0.35 0.60 Ė2 А3 13.35 12.95 13.75 1.15 1,20 1.25 b b1 0.59 0.64 0.69 D 56.40 56.70 57.00 D1 4.40 4.50 4.60 D2 50.85 51.00 51.15 47.70 48.00 48.30 42.35 42.50 E1 42.65 ØΡ E2 52.90 53.00 53.10 **E**3 62.30 62.80 63.30 SIDE VIEW TOP VIEW E4 4.90 5.00 5.10 Р 2.20 2.30 2.40 25.5 24.0 24.0 20.8 20.8 11.2 **END VIEW** DBC EXPOSAL **GENERIC MARKING DIAGRAM\* ATYYWW** Ø0.94~1.09 PLATED THRU HOLE FRONTSIDE MARKING Ø9.0 2D RECOMMENDED CODE **MOUNTING PATTERN**

| DESCRIPTION:     | <br>Printed Versions are uncontrolled except when stamped CONTROLLED                                                                                                              | PAGE 1 OF 1 |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DOCUMENT NUMBER: | Electronic versions are uncontrolled except when accessed directly from the Document Repository.  Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

may not follow the Generic Marking.

\*This information is generic. Please refer to device data

sheet for actual part marking. Pb-Free indicator, "G" or

microdot " • ", may or may not be present. Some products

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

BACKSIDE MARKING

YYWW = Year and Work Week Code

= Assembly & Test Site Code

XXXXX = Specific Device Code

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.or

### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales