# MOD6210/MOD6211/MOD6212/MOD6213 Transceiver Module

## **Data Sheet**

SB-DS-02037-A

January 2018

#### **Contents**

| Glossary                                            | 4  |

|-----------------------------------------------------|----|

| 1. General Description                              | 5  |

| 1.1. Key Features                                   |    |

| 2. Product Family                                   | 6  |

| 3. Module Block Diagram and Pinout Descriptions     |    |

| 3.1. Block Diagram                                  |    |

| 3.2. Pinout Descriptions                            | 7  |

| 4. Transceiver Module Dimensions                    | 9  |

| 5. Transceiver Module Connector                     | 11 |

| 6. Transceiver Module System Application            | 13 |

| 7. Transceiver Module Functional Description        |    |

| 7.1. USB 3.0 Interface                              |    |

| 7.2. I <sup>2</sup> C Tunneling                     | 14 |

| 7.3. Debug Port                                     | 15 |

| 7.4. GPI, GPO, and LEDO                             |    |

| 7.5. Reset                                          |    |

| 7.6. Power States                                   |    |

| 7.7. SNAP VBUS_SENSE and VBUS_EN Function           |    |

| 8. Mechanical Placement                             |    |

| 8.1. General Consideration                          |    |

| 8.2. Antenna Configuration                          |    |

| 8.3. Module Integration and Enclosure Design Guides |    |

| 8.3.2. Enclosure                                    |    |

| 8.4. 60 GHz RF Absorber                             |    |

| 8.5. PORON <sup>©</sup> Gasket                      |    |

| 9. Module Placement and Enclosure Design            |    |

| 9.1. MOD6212 to MOD6213 Transceiver Module          |    |

| 9.2. MOD6210 to MOD6211 Transceiver Module          | 23 |

| 9.2.1. Recommendations for Enclosure Design         | 24 |

| 10. RF Link Margin Measurement                      | 25 |

| 11. 60 GHz Regulatory Certification                 | 29 |

| 12. Transceiver Module Specification                | 30 |

| Ordering Information                                |    |

| Production Part Numbers                             |    |

| References                                          |    |

| Standards Documents                                 |    |

| Revision History                                    | 33 |

## **Figures**

| Figure 1.1. Wireless Connector System Diagram                                    | 5  |

|----------------------------------------------------------------------------------|----|

| Figure 3.1. Transceiver Module Block Diagram                                     | 7  |

| Figure 4.1. Transceiver Module Dimensions (in mm)                                | 9  |

| Figure 4.2. MOD6213 Transceiver Module Layout Floorplan                          | 9  |

| Figure 4.3. MOD6212 Transceiver Module Layout Floorplan                          | 10 |

| Figure 4.4. MOD6211 Transceiver Module Layout Floorplan                          | 10 |

| Figure 4.5. MOD6210 Transceiver Module Layout Floorplan                          | 10 |

| Figure 5.1. Module Side Connector                                                | 11 |

| Figure 5.2. System Side Connector                                                |    |

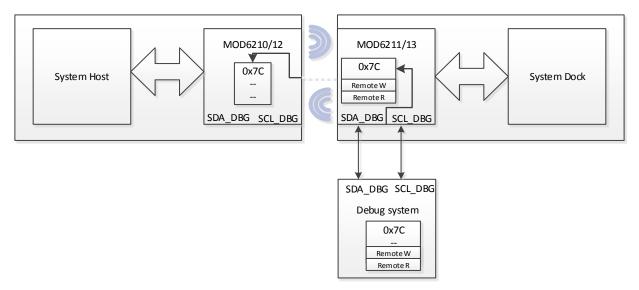

| Figure 6.1. System Level Integration and Test                                    | 13 |

| Figure 7.1. Transceiver Module I <sup>2</sup> C System Diagram                   |    |

| Figure 7.2. Transceiver Module I <sup>2</sup> C Debug Interface                  | 15 |

| Figure 7.3. Transceiver Module Remote I <sup>2</sup> C Debug Principle           | 16 |

| Figure 7.4. Transceiver Module Interrupt Based I <sup>2</sup> C Tunnel           |    |

| Figure 7.5. Module Power States                                                  |    |

| Figure 7.6. VBUSE_SENSE Circuit Example                                          |    |

| Figure 7.7. Use VBUS_EN Signal to Control the Power On/Off for Downstream Device | 19 |

| Figure 8.1. Edge Fire Antenna Configuration                                      | 20 |

| Figure 8.2. Broad Side Antenna Configuration                                     | 20 |

| Figure 8.3. MOD6210/MOD6211 Keep-Out Perimeter                                   |    |

| Figure 8.4. MOD6212/MOD6213 Keep-Out Perimeter                                   |    |

| Figure 8.5. RF Absorber Placement                                                |    |

| Figure 9.1. Broad Fire (MOD6212/MOD6213) Enclosure Design                        | 23 |

| Figure 9.2. Edge Fire (MOD6210/MOD6211) Enclosure Design                         |    |

| Figure 10.1. Snap_tool Debug Console Window (Main Window)                        |    |

| Figure 10.2. Snap_tool RF Throughput Test Page                                   | 26 |

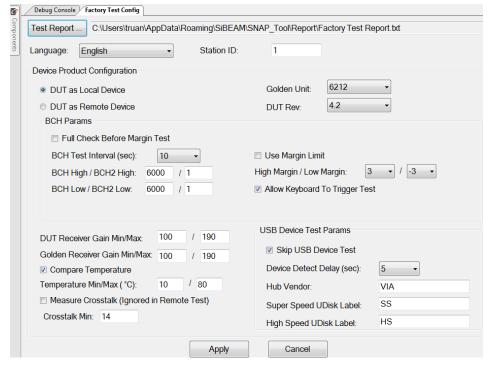

| Figure 10.3. Snap_tool Factory Test Config Page                                  | 26 |

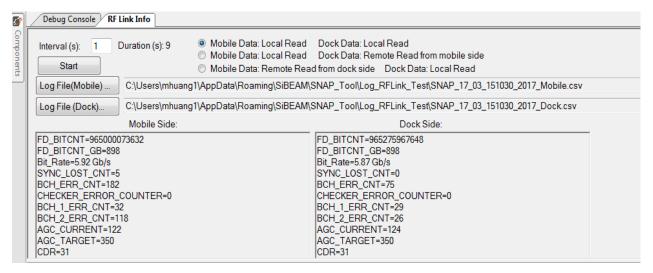

| Figure 10.4. Snap_tool RF Link Info Page Current RF Status                       | 27 |

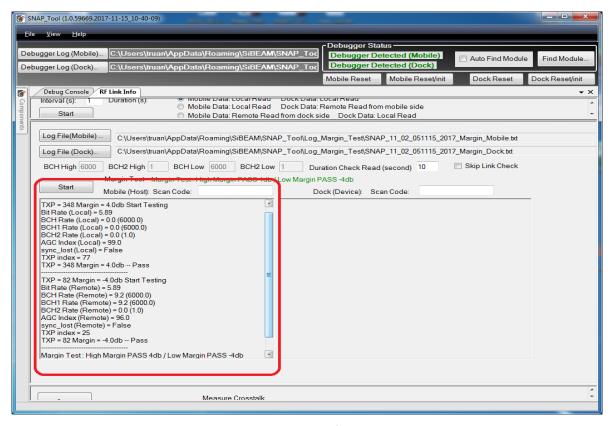

| Figure 10.5. Snap_tool RF Link Info Page RF Link Margin                          | 28 |

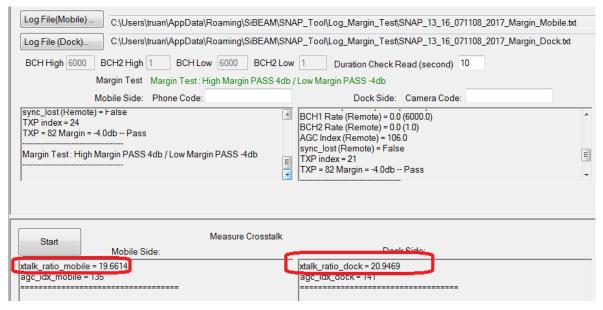

| Figure 10.6. Snap_tool RF Link Info Page Crosstalk Result                        | 28 |

|                                                                                  |    |

| Tables                                                                           |    |

| Tables                                                                           |    |

| Table 3.1. Signal Pinout                                                         |    |

| Table 7.1. Transceiver Personality Based on Pair Configuration                   |    |

| Table 7.2. Remote Debug Registers Description                                    |    |

| Table 9.1. Recommendations for Enclosure Design                                  |    |

| Table 12.1. Module Specification                                                 | 30 |

## **Glossary**

A glossary of terms used in this document.

| Acronym          | Definition                                    |

|------------------|-----------------------------------------------|

| AC               | Alternating Current                           |

| DS               | Downstream facing USB port                    |

| EMI              | Electromagnetic Interference                  |

| EU               | The European Union                            |

| FCC              | Federal Communications Commission             |

| FS               | USB2 Full Speed                               |

| HS               | USB2 High Speed                               |

| IC               | Integrated Circuit                            |

| I <sup>2</sup> C | Inter-Integrated Circuit                      |

| LED              | Light Emitting Diode                          |

| LS               | Low Speed                                     |

| ООК              | On/Off Key Modulation                         |

| RF               | Radio Frequency                               |

| SS               | Super Speed                                   |

| TELEC            | Telecommunication                             |

| US               | Upstream facing USB port                      |

| U0/W0            | Snap active wireless link data transfer state |

| U2               | USB 3.0 link idle, slow exit                  |

| U3               | USB 3.0 suspend mode                          |

## 1. General Description

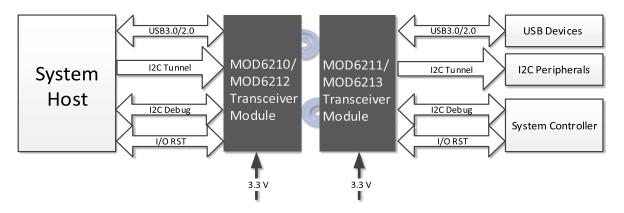

The MOD6210/MOD6211/MOD6212/MOD6213 transceiver modules use SiBEAM Snap<sup>™</sup> technology to make an ultra-short-range, close alignment, high speed, full duplex wireless link operating in the 60 GHz band. The transceiver modules support USB 2.0/USB 3.0 compatible data and  $I^2$ C-compatible control and status information transfers.

Intelligent power management reduces the transceiver power consumption according the wireless and USB link state.

The transceiver modules ease integration into a variety of products by simplifying the design. The transceiver modules have received modular certification, which reduces the burden of regulatory approval for the product.

#### 1.1. Key Features

Simultaneous USB 3.0 and USB 2.0 connections through USB hub (SS, HS, FS, LS supported)

- Up to 6 Gbps full duplex

- Short range wireless link

- No host driver required

- Intelligent power management automatically drops power based on USB link power state (U0 through U3)

- Low power consumption during scan mode when the transceivers are not in range

- I<sup>2</sup>C tunneling over wireless link

- Built-in antenna

- Small form factor 10 mm × 26 mm × 3 mm

- Full regulatory certified modules (TELEC, EU, FCC, and IC)

- Single 3.3 V power rail

- Debug and remote debug function tool suite

- RF performance measurement tool suite

Figure 1.1. Wireless Connector System Diagram

SB-DS-02037-A

## 2. Product Family

| Transceiver Module | Link Side                         | Link Orientation                       |

|--------------------|-----------------------------------|----------------------------------------|

| MOD6210            | Host                              | Edge (parallel to package plane)       |

| MOD6211            | Device                            | Edge (parallel to package plane)       |

| MOD6212            | Host Broad (perpendicular to pack |                                        |

| MOD6213            | Device                            | Broad (perpendicular to package plane) |

| SK621011           | _                                 | Edge (parallel to package plane)       |

| SK621213           | _                                 | Broad (perpendicular to package plane) |

## 3. Module Block Diagram and Pinout Descriptions

This section describes the module block diagram and the detail pinout.

#### 3.1. Block Diagram

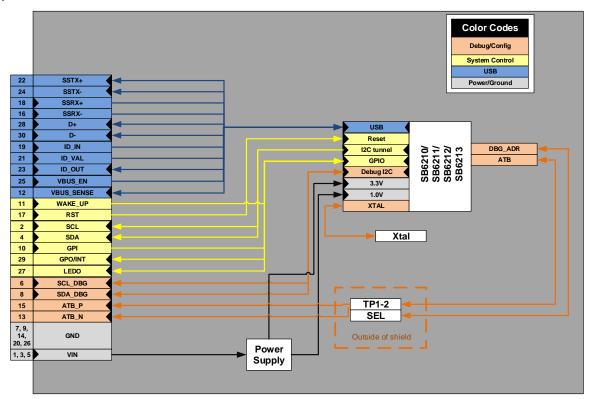

Figure 3.1 is the block diagram of the Transceiver Module. The Pinout Descriptions section describes the functions of each pin.

Figure 3.1. Transceiver Module Block Diagram

## 3.2. Pinout Descriptions

**Table 3.1. Signal Pinout**

| Pin | Name    | Туре             | Dir            | Group                                                                                                    | up Description                                                                                                                                                 |  |

|-----|---------|------------------|----------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | 3V3     | Power            | Input          | Power                                                                                                    | 3.3 V ±5% power supply                                                                                                                                         |  |

| 2   | SCL     | Digital          | In/Out<br>O.D. | I <sup>2</sup> C                                                                                         | I <sup>2</sup> C clock, tunneling port. MOD6210/MOD6212 transceiver module connects to Host board; MOD6211/MOD6213 transceiver module connects to Device board |  |

| 3   | 3V3     | Power            | Input          | Power                                                                                                    | 3.3 V ±5% power supply                                                                                                                                         |  |

| 4   | SDA     | Digital          | In/Out<br>O.D. | I <sup>2</sup> C                                                                                         | I <sup>2</sup> C data, tunneling port. MOD6210/MOD6212 transceiver module connects to Host board; SB6211/SB6213 transceiver module connects to Device board    |  |

| 5   | 3V3     | Power            | Input          | Power 3.3 V ±5% power supply                                                                             |                                                                                                                                                                |  |

| 6   | SCL-DBG | Analog           | Bi-Dir         | USB I <sup>2</sup> C clock, debug port. Connection to debug controller. N required for normal operation. |                                                                                                                                                                |  |

| 7   | GND     | Power            | Input          | Power Ground                                                                                             |                                                                                                                                                                |  |

| 8   | SDA-DBG | I <sup>2</sup> C | In/Out<br>O.D. | Debug                                                                                                    | I <sup>2</sup> C data, debug port. Connection to debug controller. Not required for normal operation.                                                          |  |

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Pin | Name       | Туре    | Dir    | Group           | Description                                                                                                                                                                                       |  |

|-----|------------|---------|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9   | GND        | Power   | Input  | Power           | Ground                                                                                                                                                                                            |  |

| 10  | GPI        | Digital | Input  | GPIO            | General purpose input. Status of this input is reflected on the GPO pin on the opposite side of an active wireless link.                                                                          |  |

| 11  | WAKE_UP    | Digital | Input  | Control         | Force the link to W0 state. This is useful to bypass USB states, when I <sup>2</sup> C tunnel or GPI signal needs to be used, while the link is in low power states. Active High. Optional.       |  |

| 12  | VBUS_SENSE | Digital | Input  | USB             | USB VBUS status input , 3V3                                                                                                                                                                       |  |

| 13  | ATB_N      | Analog  | Output | Debug           | Differential analog test bus – negative terminal                                                                                                                                                  |  |

| 14  | GND        | Power   |        | Power           | Ground                                                                                                                                                                                            |  |

| 15  | ATB-P      | Analog  | Output | Debug           | Differential analog test bus – positive terminal                                                                                                                                                  |  |

| 16  | SSRX-      | Analog  | Input  | USB             | USB super speed receiver differential pair negative input                                                                                                                                         |  |

| 17  | RST        | Digital | Input  | Config          | Reset Input, active HIGH                                                                                                                                                                          |  |

| 18  | SSRX+      | Analog  | Input  | USB             | USB super speed receiver differential pair positive input                                                                                                                                         |  |

| 19  | ID_IN      | Digital | Input  | USB             | USB ID input                                                                                                                                                                                      |  |

| 20  | GND        | Ground  | Input  | SS<br>isolation | Ground                                                                                                                                                                                            |  |

| 21  | ID-VAL     | Digital | Input  | USB             | USB ID valid input                                                                                                                                                                                |  |

| 22  | SSTX+      | Analog  | Output | USB             | USB super speed transmitter differential pair positive output                                                                                                                                     |  |

| 23  | ID_OUT     | Digital | Output | USB             | USB ID output                                                                                                                                                                                     |  |

| 24  | SSTX-      | Analog  | Output | USB             | USB super speed transmitter differential pair negative output                                                                                                                                     |  |

| 25  | VBUS_EN    | Digital | Output | USB             | USB VBUS status output, 3V3                                                                                                                                                                       |  |

| 26  | GND        | Ground  | Input  | SS<br>isolation | Ground                                                                                                                                                                                            |  |

| 27  | LEDO       | Digital | Output | Config          | LED output                                                                                                                                                                                        |  |

| 28  | D+         | Analog  | Bi-Dir | USB             | USB high speed/full speed/low speed positive I/O                                                                                                                                                  |  |

| 29  | GPO/INT    | Digital | Output | GPIO            | General purpose output. When a wireless link is active, the status of this output reflects the GPI pin on the opposite side of the wireless link. Also used as I <sup>2</sup> C tunnel interrupt. |  |

| 30  | D-         | Analog  | Bi-Dir | USB             | USB high speed/full speed/low speed negative I/O                                                                                                                                                  |  |

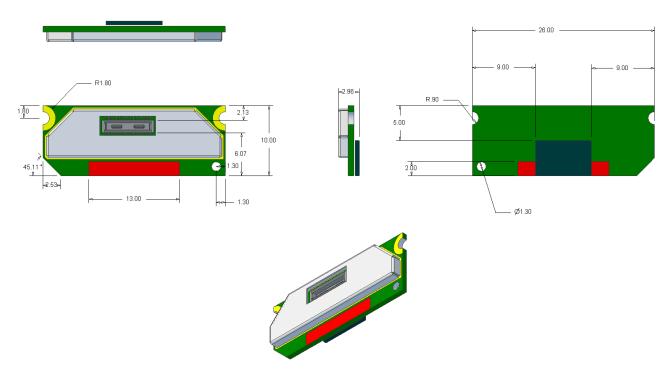

#### 4. Transceiver Module Dimensions

This section describes the dimensions of the module and the PCB layout floor plan.

System integrators can use the module dimensions to start the board layout and enclosure design. Each module PCB silkscreen includes FCC/IC regulatory ID, module name and other PCB related information.

Figure 4.1. Transceiver Module Dimensions (in mm)

Figure 4.2. MOD6213 Transceiver Module Layout Floorplan

Figure 4.3. MOD6212 Transceiver Module Layout Floorplan

Figure 4.4. MOD6211 Transceiver Module Layout Floorplan

Figure 4.5. MOD6210 Transceiver Module Layout Floorplan

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

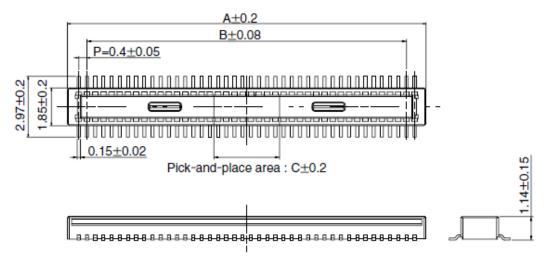

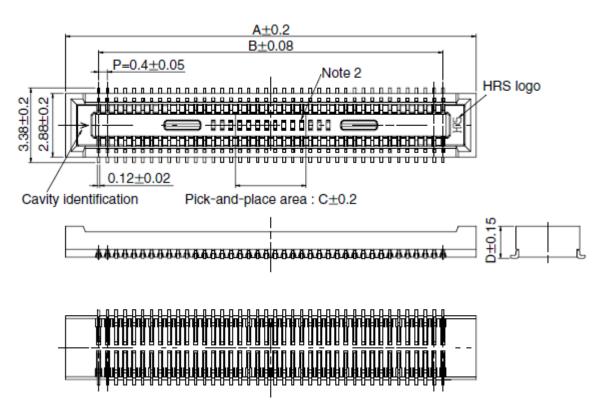

#### 5. Transceiver Module Connector

This module is designed to be connected to the system board through a single board-to-board connector. This module uses the following connector (Figure 5.1) to mate with the connector on the system side:

- Connector type : DF40 from Hirose

- Part number: DF40C-30DP-0.4V (51)

- Description: Dual Row Board to Board Receptacle (Plug), 0.4 pitch, 30 pins

- A=7.52 mm, B=5.6 mm, C =1.5 mm

Figure 5.1. Module Side Connector

On the system side, the following connector (Figure 5.2) should be used to mate with the module:

- Connector type is: DF40 from Hirose

- Part number: DF40C-30DS-0.4V (51)

- Description: Dual row Board-to-Board Socket, 0.4 pitch, 30 pins

- A=8.6 mm, B=5.6 mm, C=1.5 mm

11

Figure 5.2. System Side Connector

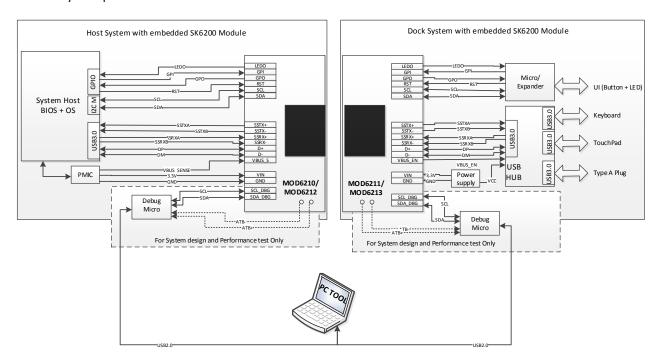

## 6. Transceiver Module System Application

The following diagram shows the module connected to the host or device. In addition, it shows how to connect a debug micro for system performance measurements.

Figure 6.1. System Level Integration and Test

## 7. Transceiver Module Functional Description

#### 7.1. USB 3.0 Interface

The transceiver module interfaces directly with a USB 3.0 port without requiring any additional control or interface logic. ID\_IN and ID\_VAL strapping pins on the MOD621x transceiver module are used along with wireless communication to establish the USB port personality as either upstream facing or downstream facing. The ID\_OUT signal from each transceiver to the attached USB port indicates the upstream or downstream facing transceiver operation.

Table 7.1. Transceiver Personality Based on Pair Configuration

| Pin Conf | iguration |         |        | Transceiver Personality |                   |                   |                   |                   |                   |                             |

|----------|-----------|---------|--------|-------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------|

| SB6210/  | SB6212    | SB6211/ | SB6213 | SB6210<br>/SB6212       | SB6211<br>/SB6213 | SB6210<br>/SB6212 | SB6211<br>/SB6213 | SB6210<br>/SB6212 | SB6211<br>/SB6213 | Application<br>Example      |

| ID_IN    | ID_VAL    | ID_IN   | ID_VAL | ID_OUT                  | ID_OUT            | Facing            | Facing            | VBUS_En           | VBUS_En           |                             |

| 1        | 1         | 0       | 1      | 0                       | Z                 | US                | DS                | 0                 | 1                 | 2 in 1 Laptop               |

| 0        | 1         | 1       | 1      | Z                       | 0                 | DS                | US                | 1                 | 0                 | Sport Camera/<br>Storage    |

| Х        | 0         | 1       | 1      | Z                       | 0                 | DS                | US                | 1                 | 0                 | Mobile Phone (as<br>Device) |

| Х        | 0         | 0       | 1      | 0                       | Z                 | US                | DS                | 0                 | 1                 | Mobile Phone (as<br>Host)   |

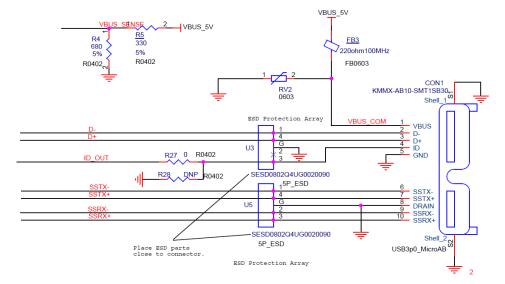

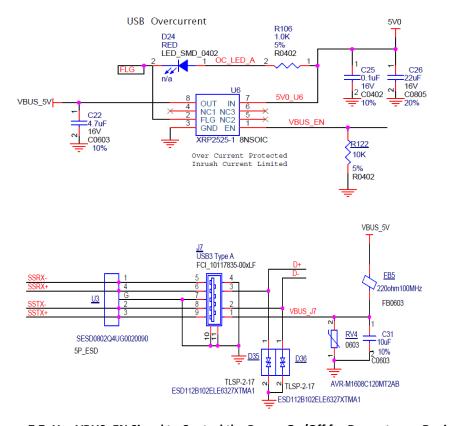

The VBUS supply from the upstream USB port is used as a VBUS\_SENSE input to the transceiver. Note that a resistor divider or equivalent circuit should be used to reduce the +5 V VBUS voltage level to a +3.3 V voltage level that is compatible with the VBUS\_SENSE input. The VBUS status is sent to the downstream facing transceiver, where the VBUS\_EN signal is used to control the local VBUS status at the downstream USB connection.

When an SB6210/SB6212-based module transceiver is located in close proximity to a SB6211/SB6213-based module transceiver, the two transceivers automatically establish a wireless connection, enabling high bandwidth communication with the devices on the other side of the link. Establishing a wireless link is analogous to plugging in a USB cable. Once connected, the link behaves the same as a wired USB 3.0 interface. The ID\_OUT signal emulates the proper grounding of the ID pin that would be seen when attaching a USB cable between devices. The VBUS\_EN signal can be used to drive a VBUS logic input to actually switch the VBUS power to the downstream facing USB interface.

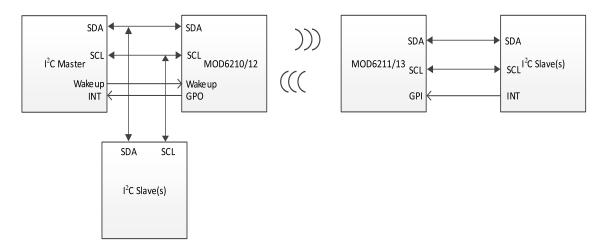

### 7.2. I<sup>2</sup>C Tunneling

I<sup>2</sup>C tunneling is a key feature of the transceiver module. It allows an I<sup>2</sup>C master on the MOD6210/MOD6212 transceiver module (Figure 7.1) to communicate with I<sup>2</sup>C devices connected to the MOD6211/MOD6213 transceiver module. The key elements of this feature are highlighted below:

- 400 kHz interface. Sub-SCL latency, ~100 ns

- Applications can include I/O expander, EPROM, low-speed peripherals, and others.

The transceiver module has an internal power management state machine that follows USB-defined states. It is possible that the first I<sup>2</sup>C transaction happens when the wireless link is turned OFF (for power saving while USB is inactive). This transaction wakes up the wireless link, but it is also possible for this first transaction to fail while the wireless link is being restored. For this reason, designers should make sure that they have a retry mechanism with an appropriate timeout period.

There is also an auto timeout after which, if there is no transaction on USB, WAKE\_UP pin or I<sup>2</sup>C tunnel, the system returns to power saving state and the link is shut off again.

Figure 7.1. Transceiver Module I<sup>2</sup>C System Diagram

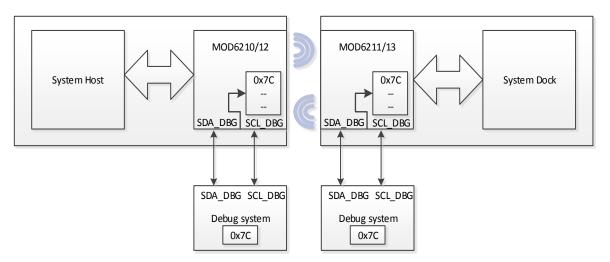

#### 7.3. Debug Port

An optional I<sup>2</sup>C debug port may be used to access the internal I<sup>2</sup>C debug registers of the transceiver module. The debug interface uses slave address 0x7C (Figure 7.2).

Figure 7.2. Transceiver Module I<sup>2</sup>C Debug Interface

SB-DS-02037-A

Figure 7.3. Transceiver Module Remote I<sup>2</sup>C Debug Principle

A unique feature of the transceiver module is the ability to perform remote debug. The bottom four registers of each register bank are used to allow remote I<sup>2</sup>C read and write. These remote debug operations are executed in the local I<sup>2</sup>C register bank by proxy (Figure 7.3).

A remote I<sup>2</sup>C debug command is executed by writing a command in register 0x7FC, followed by writing the remote register address in register 0x7FD. Data from remote I<sup>2</sup>C read operation is read back from register 0x7FF, whereas data for remote I2C write operation is written in register 0x7FE.

Table 7.2. Remote Debug Registers Description

| Reg | Name           | 7    | 6    | 5    | 4     | 3    | 2    | 1    | 0    |

|-----|----------------|------|------|------|-------|------|------|------|------|

| 7FC | Remote command | _    | _    | _    | t.out | err  | busy | rd   | wr   |

| 7FD | Remote address | A[7] | A[6] | A[5] | A[4]  | A[3] | A[2] | A[1] | A[0] |

| 7FE | Remote WR      | D[7] | D[6] | D[5] | D[4]  | D[3] | D[2] | D[1] | D[0] |

| 7FF | Remote RD      | D[7] | D[6] | D[5] | D[4]  | D[3] | A[2] | D[1] | D[0] |

#### 7.4. GPI, GPO, and LEDO

The transceiver module contains a general purpose input (GPI), a general purpose output (GPO), as well as a dedicated LED output (LEDO) pin.

The LEDO indicates the state of the wireless link. A persistent low (OFF state) indicates that the SK621x transceiver module is powered down or being held in reset. A periodic high (blinking) indicates that the device is scanning for a connection. An active high (ON state) indicates that a link is established.

Without a link present, GPO stays low (OFF state). When a link is established and the transfer is in full speed mode (WO state), the GPO reflects the state of the GPI pin on the opposite side of the link. If the GPI pin on the opposite side of the link is left high, the GPO output can be used to indicate that wireless RF link is established. If the device goes into a "Detached State"—link is established but no data is being transferred—the GPO signal periodically goes high (blinking).

Each GPI pin can be used to control the state of the GPO pin on the opposite side of the link, but only when the link is in a Full Speed mode (WO state).

GPI on SK6211/13-MOD to GPO on SK6210/12-MOD can also be used as interrupt function along with the WAKE\_UP pin to wake up the wireless link and I<sup>2</sup>C host for service (as shown in Figure 7.4). Asserting WAKE\_UP forces the wireless link to W0 state or stops the link from entering low power modes (W2, W3, IDLE). This combination of WAKE\_UP pin and GPO/INT works together with the I<sup>2</sup>C tunnel function to prevent the need for polling on the I<sup>2</sup>C tunnel from the master side.

Figure 7.4. Transceiver Module Interrupt Based I<sup>2</sup>C Tunnel

#### 7.5. Reset

The transceiver module has an RST input pin that keeps the device in standby. The module includes a power-on-reset circuit in case an RST signal is not available. If the RST signal is not connected, this pin should be tied to GND to avoid spurious resets during normal operation.

#### 7.6. **Power States**

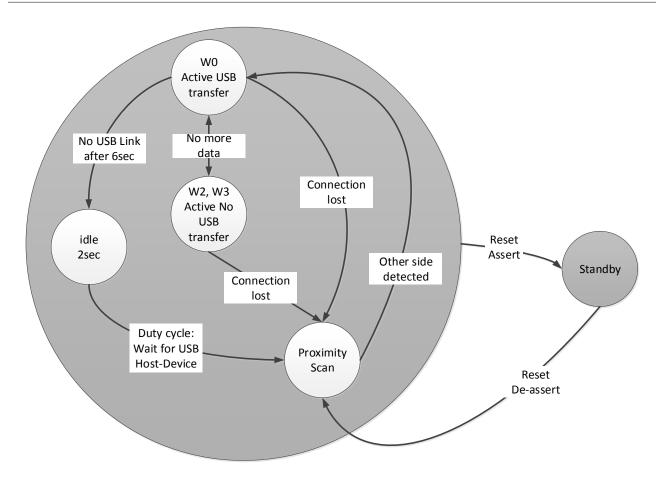

The transceiver module has automatic power state management that does not require external host supervision or control, as shown in Figure 7.5.

A simple dock detection mechanism can trigger transceiver module standby mode and reach a power consumption level in the mobile device of about 10  $\mu$ W.

It is assumed, in most typical use cases, that the W0 state is only reached when the mobile device is docked to an AC powered accessory.

To comply with some regulations, "Flight mode", all radio OFF, is supported in hardware reset state.

The transceiver module takes full advantage of advanced power profiles defined by USB specifications such as Super Speed U2/U3 and USB2.0 SUSPEND/LPM.

Downloaded from Arrow.com.

Figure 7.5. Module Power States

#### 7.7. SNAP VBUS\_SENSE and VBUS\_EN Function

The VBUS supply from the upstream USB port is used as a VBUS\_SENSE input to the transceiver. Note that a resistor divider or equivalent circuit should be used to reduce the +5 V VBUS voltage level to a +3.3 V voltage level that is compatible with the VBUS\_SENSE input as shown in Figure 7.6. The VBUS status is sent to the downstream facing transceiver, where the VBUS\_EN signal is used to control the local VBUS status at the downstream USB connection. The system designer should use the VBUS\_EN signal to control the 5 V power to the downstream device, as shown in Figure 7.7. This ensures that USB enumeration starts after the wireless link is established and hence avoids device enumeration retries.

Figure 7.6. VBUSE\_SENSE Circuit Example

Figure 7.7. Use VBUS\_EN Signal to Control the Power On/Off for Downstream Device

SB-DS-02037-A

19

#### 8. Mechanical Placement

#### 8.1. General Consideration

- The transceiver module operates between 59 GHz and 65 GHz.

- Modulation scheme is OOK which provides 2 isolated wireless links of 6 Gbps maximum bitrate.

- Package size is 10 mm × 26 mm × 3 mm.

- Operating on the model of Plug/Receptacle of physical connectors, an odd part can only be connected to an even part. For example, MOD6210 device automatically connects to MOD6211 device but does not connect to MOD6212 device.

#### 8.2. Antenna Configuration

There are two antenna configurations:

- MOD6210 and MOD6211 contain edge fire antenna, as shown in Figure 8.1.

- MOD6212 and MOD6213 contain broad side antenna, as shown in Figure 8.2.

Edge fire antenna radiates with the main lobe parallel to the chip package surface pointing out of the long edge of the package.

Figure 8.1. Edge Fire Antenna Configuration

Broad side antenna radiates with the main lobe perpendicular to the chip package surface pointing out from the mounting PCB.

Figure 8.2. Broad Side Antenna Configuration

#### 8.3. Module Integration and Enclosure Design Guides

Integration of the wireless transceiver requires careful design of the system PCB and enclosure to maximize RF performance. The following sections provide design guidelines for system integrators. Failure to follow these guidelines may result in a system with degraded RF performance.

#### 8.3.1. Keep-out Area

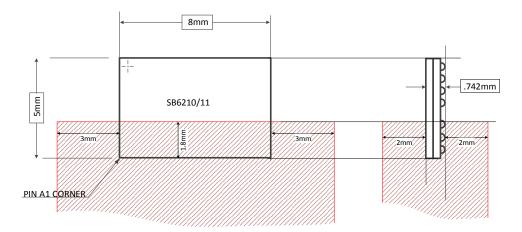

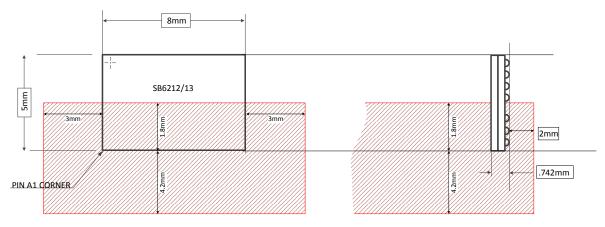

To minimize RF interference, a keep-out volume is recommended around the transceiver module. The Keep-out definition for the MOD6210/MOD6211 transceiver module is shown in Figure 8.3 and the keep-out volume for MOD6212/MOD6213 transceiver module is shown in Figure 8.4.

Figure 8.3. MOD6210/MOD6211 Keep-Out Perimeter

Figure 8.4. MOD6212/MOD6213 Keep-Out Perimeter

Within the Keep-out area, the guidelines below should be followed:

- Keep ground plane under the transceiver module.

- No electronic should be placed under the transceiver module.

- No metal parts, metal paints, fasteners nor screws should be placed under the transceiver module.

- Place 60 GHz RF absorber under the transceiver module to decrease RF interference.

#### 8.3.2. Enclosure

The system enclosure design can increase RF interference as well as increase signal path loss. The guidelines below should be followed when designing the system enclosure:

- Avoid using an enclosure material with a dielectric constant greater than 10 at 60 GHz. ABS, PE, PC, which are generally low loss at materials at 60 GHz are good choices.

- A flat surface perpendicular to the main lobe is preferred. Avoid ribbing, multi-layering or creating complex assemblies containing several compounds.

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

21

- Avoid high incidence angle at the material surface.

- An enclosure thickness of 2 mm or less is preferred.

- Chip-to-chip separation should be less than 5 mm.

- A PORON gasket placed between the transceiver module and the enclosure can be used to minimize link degradation.

#### 8.4. 60 GHz RF Absorber

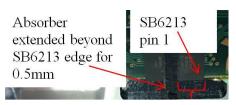

Judicious use of a 60 GHz RF absorber is an effective method of reducing unwanted signal in design. The following recommendations need apply:

- Reduce crosstalk by adding a strip of RF absorber offset towards the RX antenna on the integrated circuit of the MOD6211/MOD6213 transceiver module (Figure 8.5).

- Reduce unwanted reflections by adding RF absorber on any large metallic structures, such as EMI shields, that are

placed in proximity to the integrated circuit.

Absorber is 1.5→2.0mm by 6.0mm. Edge of absorber is 4.0mm from Edge of SB6213 where pin 1 is.

Figure 8.5. RF Absorber Placement

We recommend using the following RF absorber:

- 60 GHz 0.25mm thick RF absorber:

- JCS-9/SS6M .010\*12\*12

- ECCOSORB

- P/N 85000164

#### 8.5. PORON<sup>©</sup> Gasket

If the air gap between the integrated circuit on the wireless transceiver and the enclosure is larger than 0.5 mm, add the PORON above the SB621x chip to eliminate the air gap and improve the link performance.

Example PORON part number:

Rogers Corporation PORON

P/N = 4701-60-25031-04

Thickness = 0.79 mm, density = 400

## 9. Module Placement and Enclosure Design

#### 9.1. MOD6212 to MOD6213 Transceiver Module

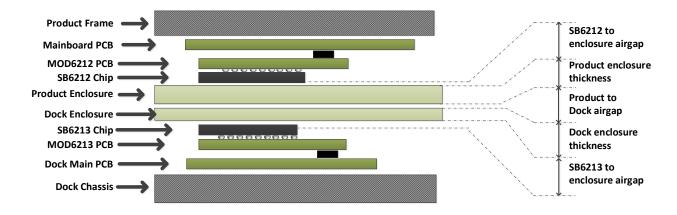

For a MOD6212 to MOD6213 connection, a simplified system integration material stack should look like the figure below (Figure 9.1). Some of the dimension are fixed by design, for instance chip thickness and board to board connector height. Some other dimensions are decided at system level and have impact on the RF link quality, for example, the air gaps and the enclosure thickness. Other dimension are system driven but do not seem to affect the RF link condition, such as the frame or chassis design when it is below the main PCB.

Figure 9.1. Broad Fire (MOD6212/MOD6213) Enclosure Design

#### 9.2. MOD6210 to MOD6211 Transceiver Module

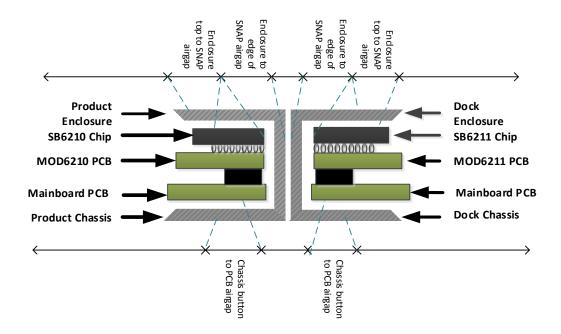

For a MOD6210 to MOD6211 configuration, a simplified system integration material stack should look like the figure below (Figure 9.2).

Figure 9.2. Edge Fire (MOD6210/MOD6211) Enclosure Design

© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

SB-DS-02037-A 23

#### 9.2.1. Recommendations for Enclosure Design

The table below lists the recommendations for the enclosure design.

#### **Table 9.1. Recommendations for Enclosure Design**

| Enclosure Design Requirement                                                                                        | MOD6212 + MOD6213<br>Enclosure Design | MOD6210 + MOD6211<br>Enclosure Design |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|

| Product enclosure + dock enclosure total thickness                                                                  | < 3.5 mm                              | < 3.5 mm                              |

| Air gap between product enclosure and dock enclosure                                                                | < 0.1 mm                              | < 0.1 mm                              |

| Distance from the top of the SB6212/13 chip surface to enclosure                                                    | < 0.5 mm                              | _                                     |

| Total distance between the top surface of SB6212 chip to top surface of SB6213 chip                                 | < 5 mm                                | _                                     |

| Total distance between the edge of SB6210 chip to edge of SB6211 chip                                               | _                                     | < 5 mm                                |

| If possible, add 60 GHz absorber between Main PCB and MOD621x device to reduce the crosstalk.                       | Yes                                   | Yes                                   |

| If there is an air gap larger than 0.5 mm between enclosure and Snap, add PORON to improve the RF link performance. | Yes                                   | _                                     |

| Follow the keep out area rules defined in the Keep-out Area section.                                                | Yes                                   | Yes                                   |

## 10. RF Link Margin Measurement

After integrating transceiver module into a system, it is important to verify that the RF link is performing adequately. A PC-based tool is provided to report critical RF performance parameters when host PC is connected to the transceiver module debug port. This tool is typically used under the following circumstances:

- 1. Initial design bring-up and performance tuning.

- 2. Validation of manufacturing design across system manufacturing tolerances.

- Production test.

Refer to the Snap™ Development Kit User Guide (SB-UG-02006) included in the reference kit package for the installation instructions. After the snap\_tool software is installed, the user guide can also be downloaded from the Help pull-down menu.

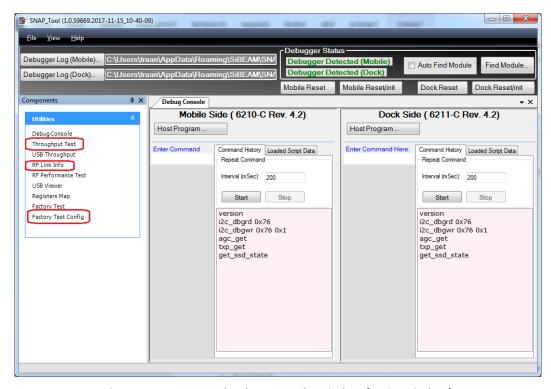

The Throughput Test and RF Link Info functions can be used to verify the RF performance (Figure 10.1).

Figure 10.1. Snap\_tool Debug Console Window (Main Window)

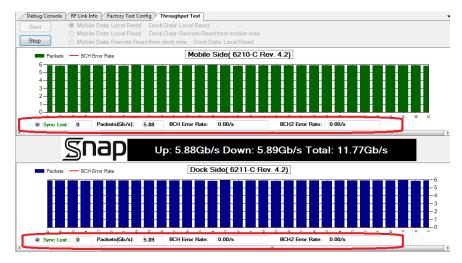

Check RF throughput through Snap\_tool Throughput Test function to make sure the RF link is at the stable stage (Figure 10.2):

- Sync Lost = 0

- Package throughput = ~5.5Gb/s

- BCH Error Rate <= 6 /sec</li>

- BCH2 Error rate = 0

25

Figure 10.2. Snap\_tool RF Throughput Test Page

Use the Snap\_tool RF Link Info page (Figure 10.4) to get more details on the RF link status:

- 1. Before running any test cases from the RF\_Link\_Info page, the Factory Test Config page (Figure 10.3) should be used to configure RF link testing options.

- a. Select **Allow Keyboard To Trigger Test** to start RF Margin testing without entering the device bar code. Press **Enter** on each bar code input box to start the testing.

- b. Un-check **Use Margin Limit** to allow the application to perform complete RF margin checking during the initial stage design phase. After verifying that a large pool of systems has the same RF link status, select this feature to perform sanity check with the defined high/low margin.

- c. Keep the **BCH Test Interval** as it is. Snap\_tool collects RF data based on the interval defined here to analyze the BCH results for RF link status.

- d. Keep the BCH High/BCH Low value set to the restricted limit for the initial testing.

Figure 10.3. Snap\_tool Factory Test Config Page

- 2. Use the RF link status function to check RF link status in real time (Figure 10.4):

- a. Bit Rate should be greater 5.5 Gb/s.

- b. Sync\_Lost, BCH\_ERR\_CNT, BCH\_1\_ERR\_CNT and BCH\_2\_ERR\_CNT should stay constant meaning that the RF link is in a healthy state.

- c. **AGC\_Current** should be greater than 110 for both sides of the link.

- d. Select device as local or remote to start the testing. If you define a device as remote, the snap tool queries the remote SNAP device registers through the SNAP remote debug registers.

Figure 10.4. Snap\_tool RF Link Info Page Current RF Status

- 3. Use RF Link Margin function (Figure 10.5) to check the RF link margin.

- a. Margin is reported in this format: 4db/-4db 4db is the maximum margin for the local side.

- -4db is the maximum margin for the remote side.

- b. The minimum targeted margin for a design should be 2db/-1db. Measured margins lower than this threshold require design changes. Ideally you should target a margin of 4db/-4db.

- c. Test condition is defined from the Factory Test Config page.

27 Downloaded from **Arrow.com**.

Figure 10.5. Snap\_tool RF Link Info Page RF Link Margin

- Crosstalk ratio from the RF Link Info page (Figure 10.6) is used to check the unwanted signal level.

- With a good design, the crosstalk ratio should be greater than 15 db on both sides of the link. The higher the crosstalk value, the lower the unwanted signal.

- b. To run this test, the Snap\_tool must detect both sides as a local device which means both devices are connected to the test PC USB2 port.

Figure 10.6. Snap\_tool RF Link Info Page Crosstalk Result

## 11. 60 GHz Regulatory Certification

The transceiver modules have received a 60 GHz regulatory grant for FCC/IC/CE/EU/AU/NE. System integrators do not need to repeat 60 GHz regulatory certification, but will need to perform system level EMI testing. If the system is sold into the US market, Lattice Semiconductor will need to collect the system test results in accordance with the FCC limited modular grant requirement.

New Chinese government regulations waive the requirement for 60 GHz certification testing since the module runs on low power short-distance radio transmission.

If the region is not included on the above mentioned regions, the system integrator can use the FCC ID as a reference to apply for the particular regional certification.

SB-DS-02037-A 29

## 12. Transceiver Module Specification

#### **Table 12.1. Module Specification**

| Parameter                       | Value                                                       |  |  |  |  |  |

|---------------------------------|-------------------------------------------------------------|--|--|--|--|--|

| Mechanical                      |                                                             |  |  |  |  |  |

| Dimensions (mm)                 | X = 10, Y= 26, Z = 3                                        |  |  |  |  |  |

| Mounting Screw half hole(x 2)   | M1.6: ISO 7045:1994 – Pan head screws with type H or type Z |  |  |  |  |  |

| Mounting post diameter (mm)     | 1                                                           |  |  |  |  |  |

| Max Module Case Temperature     | 90 °C at 60 °C ambient                                      |  |  |  |  |  |

| System Connector                | B2B, 0.4 mm pitch, 30 pin                                   |  |  |  |  |  |

|                                 | Electrical                                                  |  |  |  |  |  |

| Power Input VIN                 | 3.3 V ±5% DC, 200 mA                                        |  |  |  |  |  |

| Max Input Voltage Ripple        | <10% of VIN peak to peak                                    |  |  |  |  |  |

| Control Serial Port             | I <sup>2</sup> C 400 kHz, 3.3 V                             |  |  |  |  |  |

| Max Power                       | 500 mW (max)                                                |  |  |  |  |  |

| Connected Power                 | 350 mW (typical)                                            |  |  |  |  |  |

| Disconnected Power              | 5 mW                                                        |  |  |  |  |  |

| OFF, Disable Power <10 mA (max) |                                                             |  |  |  |  |  |

|                                 | Radio Frequencies                                           |  |  |  |  |  |

| Operating Frequency             | 59–65 GHz                                                   |  |  |  |  |  |

| Channel Bandwidth               | 6 GHz                                                       |  |  |  |  |  |

| Radiated Power (EIRP)           | 3 dBm (average)                                             |  |  |  |  |  |

| Transmit Antenna Gain           | 0 dBi                                                       |  |  |  |  |  |

| Compl                           | iance and Regulation (not submitted FCC/IC)                 |  |  |  |  |  |

| FCC                             | Part 15 subpart C                                           |  |  |  |  |  |

| IC                              | Part 15 subpart C                                           |  |  |  |  |  |

|                                 | Host independent approval (modular):                        |  |  |  |  |  |

|                                 | • EN305550                                                  |  |  |  |  |  |

| EU                              | • EN301489-28                                               |  |  |  |  |  |

|                                 | • EN62311                                                   |  |  |  |  |  |

|                                 | • EN55022                                                   |  |  |  |  |  |

# **Ordering Information**

#### **Production Part Numbers**

| Module                                                       | Part Number |

|--------------------------------------------------------------|-------------|

| MOD6210 Transceiver Module mobile side edge                  | MOD6210     |

| MOD6211 Transceiver Module dock side edge                    | MOD6211     |

| MOD6212 Transceiver Module mobile side broad                 | MOD6212     |

| MOD6213 Transceiver Module dock side broad                   | MOD6213     |

| SK621011 Module development kit edge to edge configuration   | SK621011    |

| SK621213 Module development kit broad to board configuration | SK621213    |

## References

#### **Standards Documents**

This is a list of the abbreviations used in this document. Contact the responsible standards groups for more information on these specifications.

| Abbreviation | Standards Publication, Organization, and Date                                                                                                                                                        |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB 3.0      | Universal Serial Bus Specification Version 3.0 Revision 1, Copyright © 2011, Texas Instruments, Hewlett-Packard Company, Intel Corporation, Microsoft Corporation, Renesas Corporation, ST-Ericsson. |

| USB 2.0      | Universal Serial Bus Specification Version 2.0 Revision 2, Copyright © 2000, Compaq, Hewlett-Packard Company, Intel Corporation, Lucent, Microsoft Corporation, NEC, Phillips.                       |

| I2C          | I <sup>2</sup> C Bus Specification, Revision 5, 9 Oct 2012, Copyright NXP Semiconductors                                                                                                             |

## **Revision History**

Revision A, January 2018

First production release.

SB-DS-02037-A 33

7<sup>th</sup> Floor, 111 SW 5<sup>th</sup> Avenue Portland, OR 97204, USA T 503.268.8000

www.latticesemi.com

Downloaded from Arrow.com.