Order

Now

TLC6C5716-Q1

SLVSEB5A-JULY 2018-REVISED AUGUST 2018

# TLC6C5716-Q1 Automotive 16-Channel, Full Diagnostics, Constant-Current LED Driver

#### 1 Features

Texas

INSTRUMENTS

- AEC-Q100 Qualified for Automotive Applications Device Temperature Grade 1: –40°C to 125°C. TA

- 16 Constant-Current-Sink Output Channels

- 50-mA Maximum Output Current

- 8-V Maximum Output Voltage

- Two Output Groups: OUTRn, OUTBn

- **Output Current Adjustment**

- 7-Bit Dot Correction (DC) for Each Channel

- 8-Bit Brightness Control (BC) for Each Group

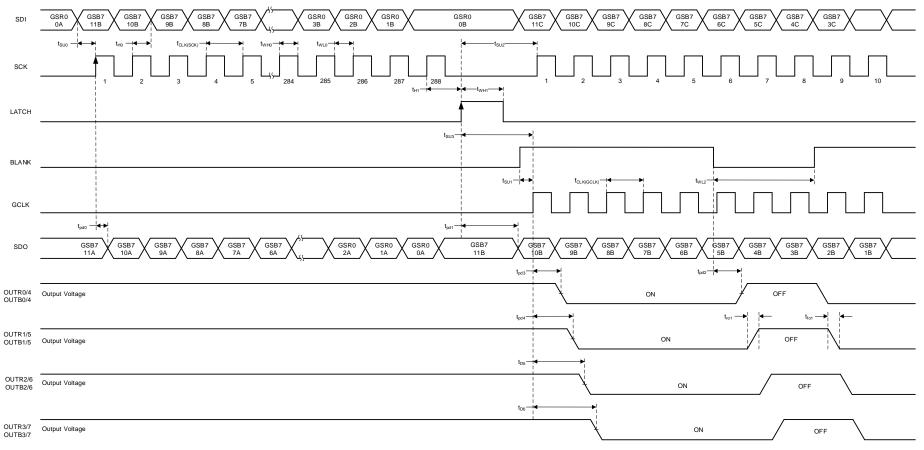

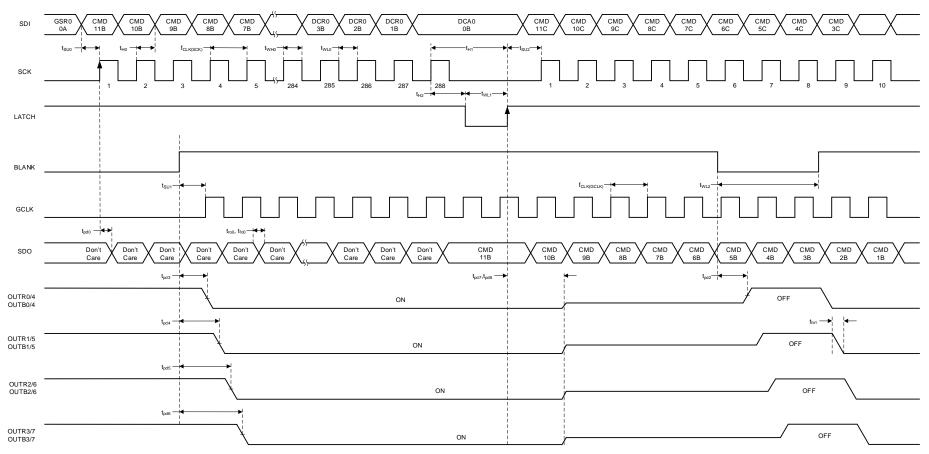

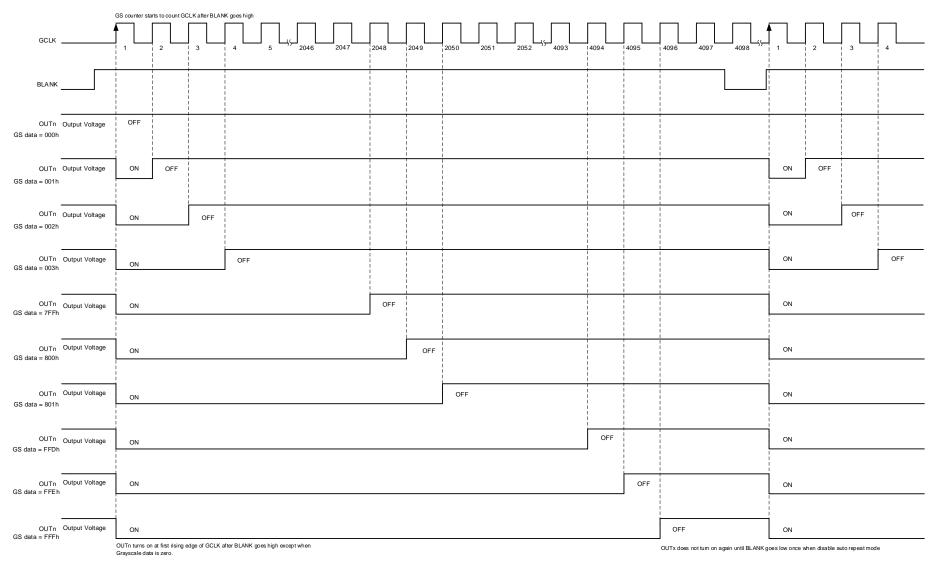

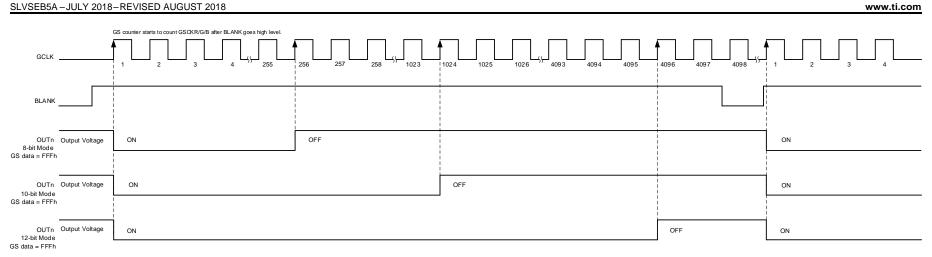

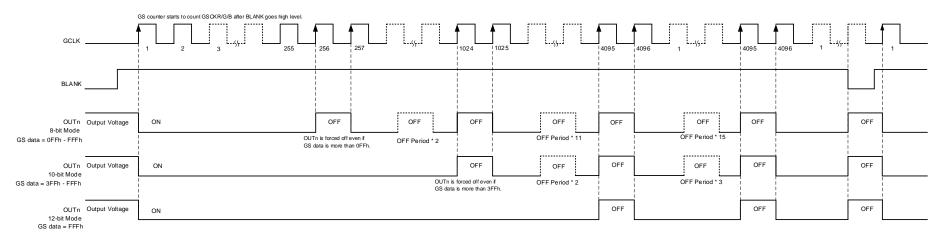

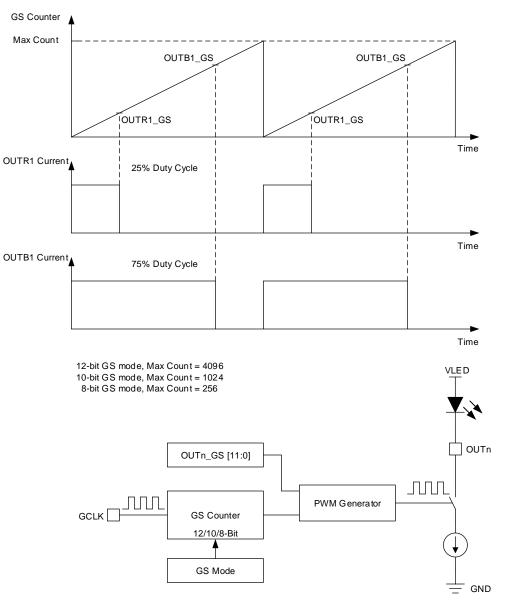

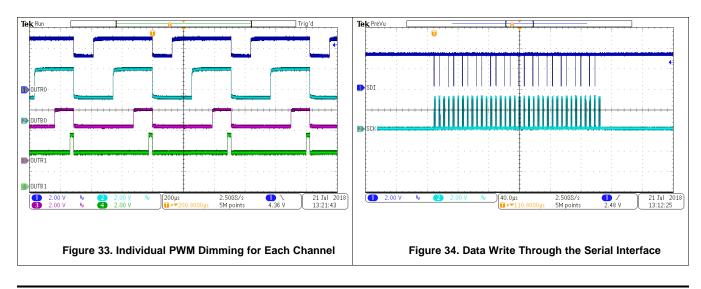

- Integrated PWM Grayscale Generator

- PWM Dimming for Each Individual Channel

- Adjustable Global Grayscale Mode: 12-Bit, 10-Bit, 8-Bit

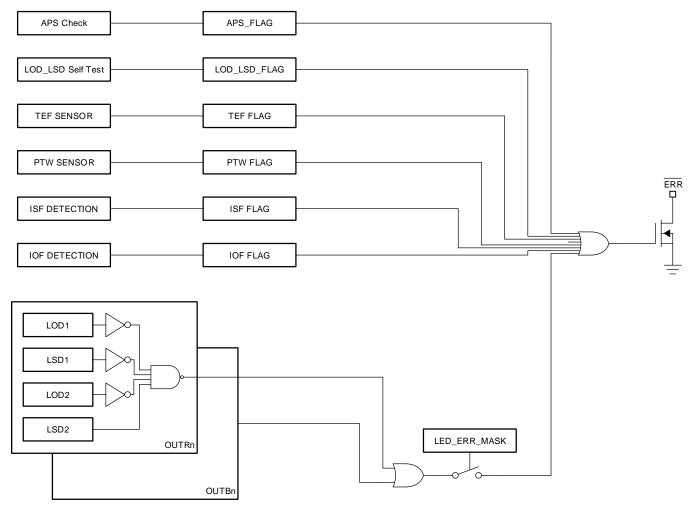

- Protection and Diagnostics

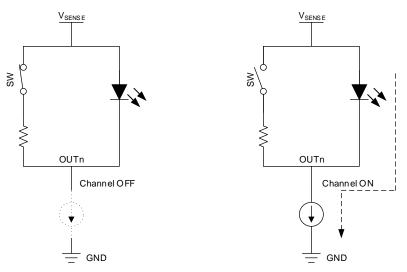

- LED-Open Detection (LOD), LED-Short Detection (LSD), Output Short-to-GND Detection (OSD)

- Adjacent-Pin Short (APS) Detection

- Pre-Thermal Warning (PTW), Thermal Shutdown (TSD)

- IREF Resistor Open- (IOF) and Short-Detection (ISF) and -Protection

- Negate Bit Toggle for GCLK Error Detect and LOD\_LSD Register Error Check

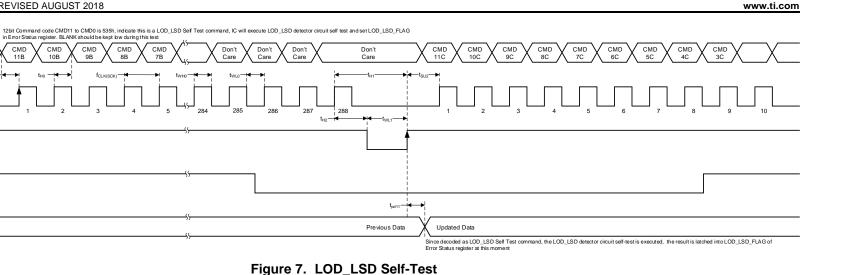

- LOD LSD Circuit Self-Test

- Programmable Output Slew Rate

- **Output Channel Group Delay**

- Serial Data Interface

#### Applications 2

- Automotive Cluster

- Automotive Local Dimming Display

- Automotive Faceplate

- Automotive HVAC Control Panel

- Automotive Center Stack Display

- Automotive Interior and RGB Ambient Lighting

- Automotive Shift-by-Wire and Gear Shifter

## 3 Description

There are automotive applications for indicators and for LCD local-dimming backlighting. For these applications, more persons think multi-channel constant-current LED drivers are necessary. The requirement is to get the same intensity and color temperature of LEDs. For system-level safety, it is necessary that the LED drivers can sense faults.

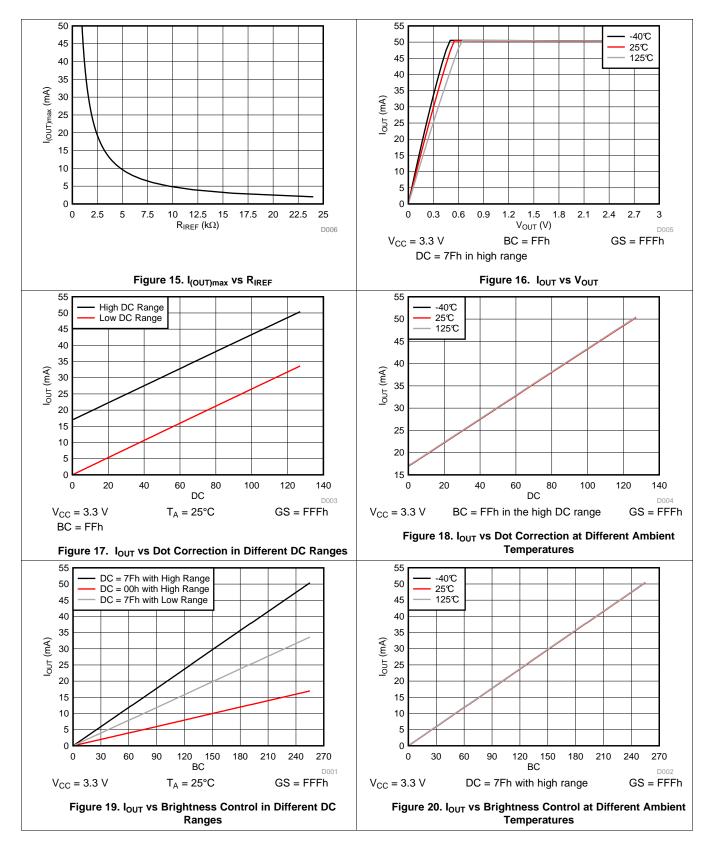

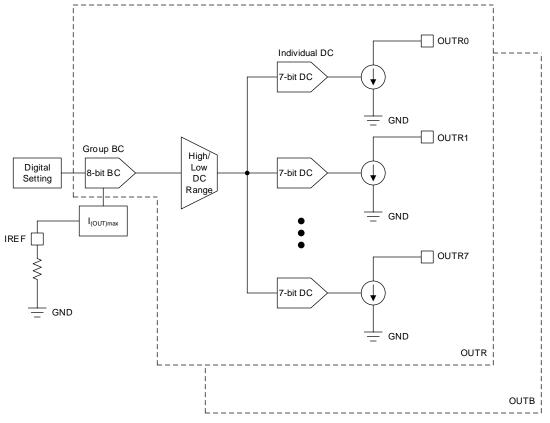

The TLC6C5716-Q1 device is an automotive 16channel constant-current RGB LED driver that can do tests on the LEDs. The TLC6C5716-Q1 device supplies a maximum of 50-mA output current set by an external resistor. The device has a 7-bit dot correction with two ranges for each output. The device also has an 8-bit intensity control for the outputs of each color group.

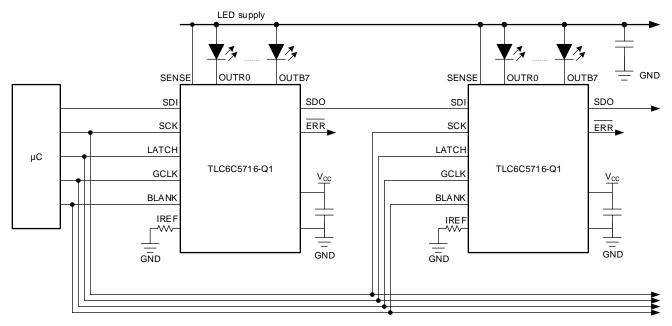

A 12-,10-, or 8-bit grayscale control adjusts the intensity of each output. The device has circuits that sense faults in the system, including LED faults, adjacent-pin short faults, reference-resistor faults, and more. A slew rate control has 2 positions for adjustment to get the largest decrease in system noise. There is an interval between the changes of output level from one LED group to a different one. This interval helps to decrease the starting electrical current. The SDI and SDO pins let more than one device be connected in series for control through 1 serial interface.

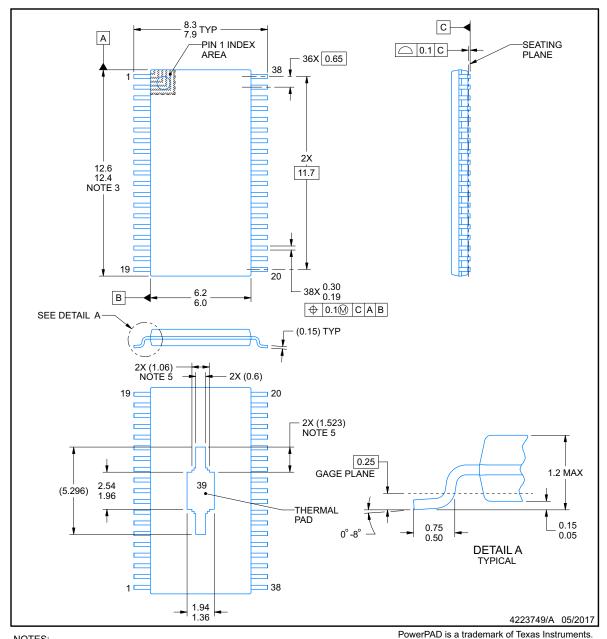

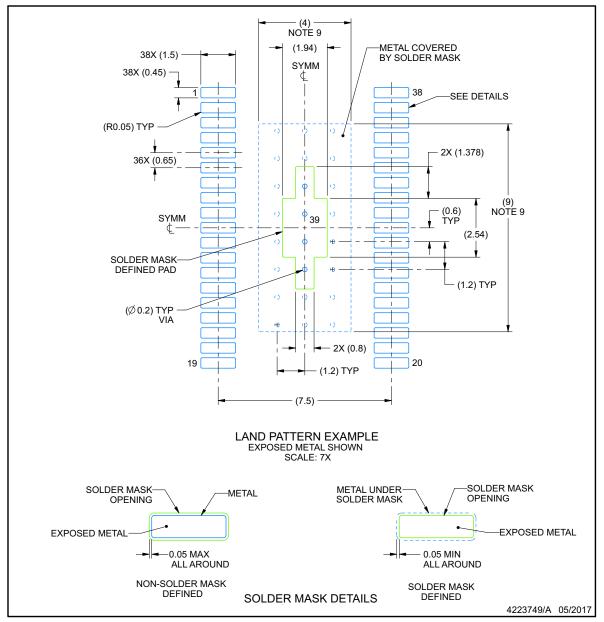

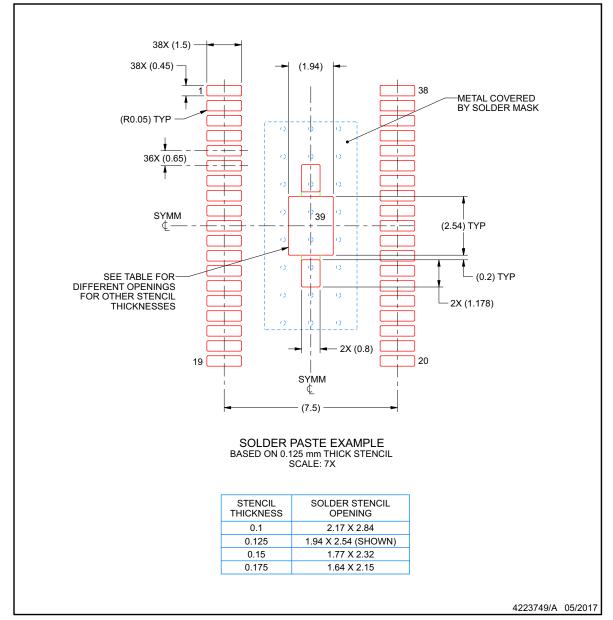

### Device Information<sup>(1)</sup>

| PART NUMBER  | PACKAGE     | BODY SIZE (NOM)    |

|--------------|-------------|--------------------|

| TLC6C5716-Q1 | HTSSOP (38) | 6.20 mm × 12.50 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

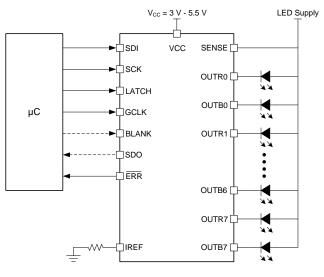

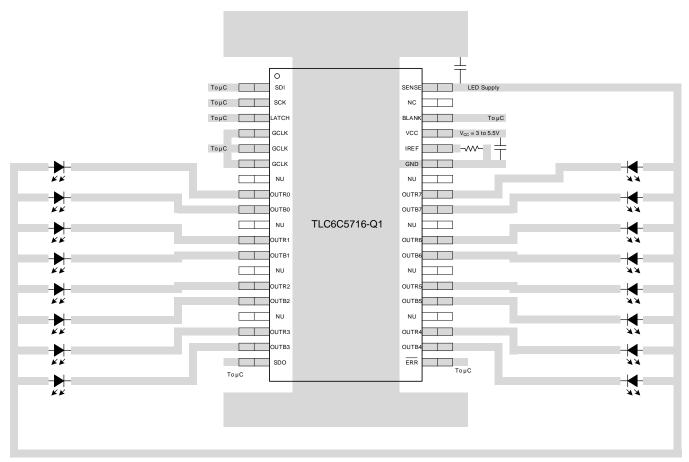

## Typical Application Schematic

## **Table of Contents**

| 1 | Feat        | tures 1                           |  |  |  |  |  |

|---|-------------|-----------------------------------|--|--|--|--|--|

| 2 | Арр         | lications1                        |  |  |  |  |  |

| 3 | Description |                                   |  |  |  |  |  |

| 4 | Rev         | ision History 2                   |  |  |  |  |  |

| 5 | Pin         | Configuration and Functions 3     |  |  |  |  |  |

| 6 | Spe         | cifications 4                     |  |  |  |  |  |

|   | 6.1         | Absolute Maximum Ratings 4        |  |  |  |  |  |

|   | 6.2         | ESD Ratings 4                     |  |  |  |  |  |

|   | 6.3         | Recommended Operating Conditions5 |  |  |  |  |  |

|   | 6.4         | Thermal Information 6             |  |  |  |  |  |

|   | 6.5         | Electrical Characteristics 6      |  |  |  |  |  |

|   | 6.6         | Timing Requirements 8             |  |  |  |  |  |

|   | 6.7         | Switching Characteristics 9       |  |  |  |  |  |

|   | 6.8         | Typical Characteristics 20        |  |  |  |  |  |

| 7 | Deta        | ailed Description 21              |  |  |  |  |  |

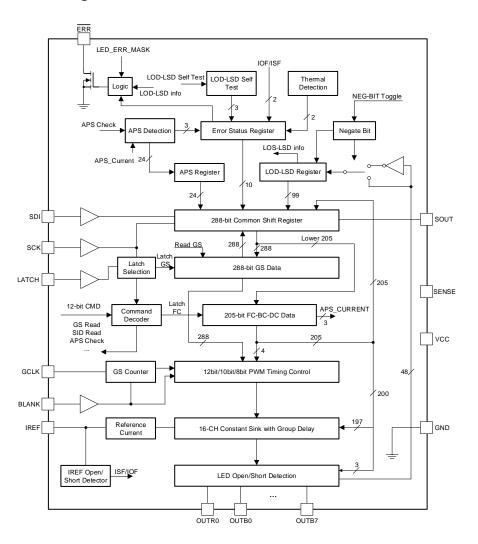

|   | 7.1         | Overview 21                       |  |  |  |  |  |

|   | 7.2         | Functional Block Diagram 21       |  |  |  |  |  |

|   | 7.3         | Feature Description 22            |  |  |  |  |  |

|   |             |                                   |  |  |  |  |  |

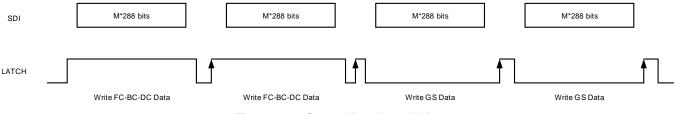

|    | 7.5  | Programming 31                                     |

|----|------|----------------------------------------------------|

|    | 7.6  | Register Maps                                      |

| 8  | Арр  | lication and Implementation 48                     |

|    | 8.1  | Application Information 48                         |

|    | 8.2  | Typical Application 48                             |

| 9  | Pow  | er Supply Recommendations 50                       |

| 10 | Lay  | out 50                                             |

|    | 10.1 | Layout Guidelines 50                               |

|    | 10.2 | Layout Example 50                                  |

| 11 | Dev  | ice and Documentation Support 51                   |

|    | 11.1 | Receiving Notification of Documentation Updates 51 |

|    | 11.2 | Community Resources 51                             |

|    | 11.3 | Trademarks 51                                      |

|    | 11.4 | Electrostatic Discharge Caution 51                 |

|    | 11.5 | Glossary51                                         |

| 12 | Mec  | hanical, Packaging, and Orderable                  |

|    | Info | rmation 51                                         |

|    | 12.1 | Package Option Addendum 52                         |

|    |      |                                                    |

7.4 Device Functional Modes...... 31

# 4 Revision History

| CI | hanges from Original (July 2018) to Revision A                                                                                              | Page |

|----|---------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Changed the description for GCLK in                                                                                                         | 4    |

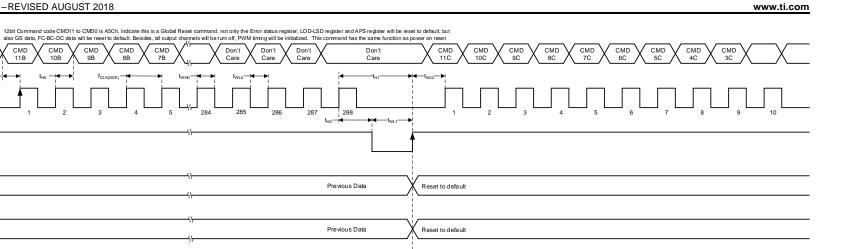

| •  | Changed "indicates" to "initiates" in the Global Reset section                                                                              | 30   |

| •  | Added "the SID" to the Fault Mode section to identify the register where the overtemperature fault is latched                               | 31   |

| •  | Changed "APS time" to "APS detection time" for bit 199 in Table 12                                                                          | 32   |

| •  | Changed "24 zones" to "16 zones" and "six TLC6C5716-Q1 units" to "eight TLC6C5716-Q1 units" in the <i>Detailed Design Procedure</i> section | 49   |

| •  | Added a new sentence preceding Figure 32                                                                                                    | 49   |

| •  | Added the Application Curves section                                                                                                        | 49   |

| •  | Added two sentences to the Power Supply Recommendations section                                                                             | 50   |

Product Folder Links: TLC6C5716-Q1

2

Downloaded from Arrow.com.

www.ti.com

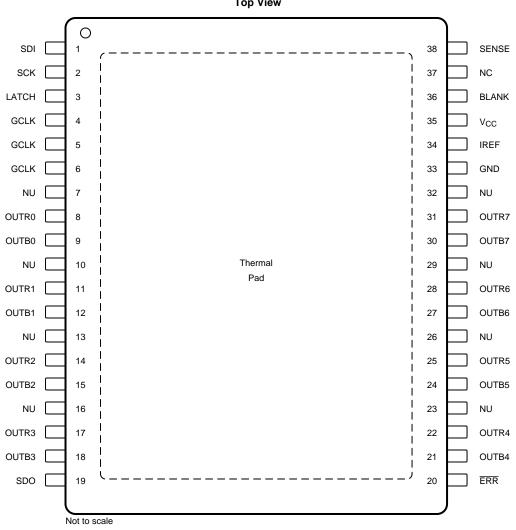

## 5 Pin Configuration and Functions

DAP PowerPAD™ Package 38-Pin HTSSOP With Exposed Thermal Pad Top View

NC - No internal connection

NU - Make no external connection

TLC6C5716-Q1 SLVSEB5A – JULY 2018 – REVISED AUGUST 2018

www.ti.com

**ISTRUMENTS**

ÈXAS

| Pin Functions   |                                  |     |                                                                                                                                                                                                                                                                  |  |  |  |

|-----------------|----------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PII             | N                                | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                      |  |  |  |

| NAME            | NO.                              | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                      |  |  |  |

| BLANK           | 36                               | I   | Blank all outputs. BLANK low forces all channels off. The grayscale counter resets<br>and the grayscale PWM timing controller is initialized. BLANK high starts the<br>grayscale PWM timing controller. Channels are controlled by the PWM timing<br>controller. |  |  |  |

| ERR             | 20                               | 0   | Open-drain error feedback                                                                                                                                                                                                                                        |  |  |  |

| GCLK            | 4, 5, 6                          | I   | Clock input for the grayscale PWM counter, three pins are internally connected together                                                                                                                                                                          |  |  |  |

| GND             | 33                               | _   | Power ground                                                                                                                                                                                                                                                     |  |  |  |

| IREF            | 34                               | I   | Reference-current pin for setting the full-scale output current                                                                                                                                                                                                  |  |  |  |

| LATCH           | 3                                | I   | Latch-enable input pin                                                                                                                                                                                                                                           |  |  |  |

| NC              | 37                               | _   | No internal connection                                                                                                                                                                                                                                           |  |  |  |

| NU              | 7, 10, 13,16,<br>23, 26, 29, 32  | _   | Not used, keep floating                                                                                                                                                                                                                                          |  |  |  |

| OUTB0-OUTB7     | 9, 12, 15, 18,<br>21, 24, 27, 30 | 0   | Constant-current outputs for group B                                                                                                                                                                                                                             |  |  |  |

| OUTR0-OUTR7     | 8, 11, 14,17,<br>22, 25, 28, 31  | 0   | Constant-current outputs for group R                                                                                                                                                                                                                             |  |  |  |

| SCK             | 2                                | I   | Input pin for the data-shift clock                                                                                                                                                                                                                               |  |  |  |

| SDI             | 1                                | I   | Serial data-in pin                                                                                                                                                                                                                                               |  |  |  |

| SDO             | 19                               | 0   | Serial data-out pin                                                                                                                                                                                                                                              |  |  |  |

| SENSE           | 38                               | I   | LED supply sensing pin                                                                                                                                                                                                                                           |  |  |  |

| V <sub>CC</sub> | 35                               | I   | Power supply pin                                                                                                                                                                                                                                                 |  |  |  |

| Thermal pad     | —                                |     | Connect to ground to improve thermal performance                                                                                                                                                                                                                 |  |  |  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating junction temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                |                              | MIN  | MAX                   | UNIT |

|------------------------------------------------|------------------------------|------|-----------------------|------|

|                                                | V <sub>CC</sub>              | -0.3 | 6                     |      |

| Input voltage                                  | SENSE                        | -0.3 | 8                     | V    |

|                                                | BLANK, GCLK, LATCH, SCK, SDI | -0.3 | V <sub>CC</sub> + 0.3 |      |

| Output voltage                                 | ERR, IREF, SDO               | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| Output voltage                                 | OUTR0-OUTR7, OUTB0-OUTB7     | -0.3 | 8                     | v    |

| Output current                                 | OUTR0-OUTR7, OUTB0-OUTB7     | 0    | 50                    | mA   |

| Operating junction temperature, T <sub>J</sub> |                              | -40  | 150                   | °C   |

| Storage temperature, T <sub>stg</sub>          |                              | -55  | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Theseare stress ratings only, which do not imply functional operation of the device at these or anyother conditions beyond those indicated under Recommended OperatingConditions. Exposure to absolute-maximum-rated conditions for extended periods mayaffect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                                             |                      | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------------------|----------------------|-------|------|

|                    |                         | Human-body model (HBM), per AEC Q100-002, <sup>(1)</sup><br>HBM ESD classification level H2 | -002, <sup>(1)</sup> | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), AEC Q100                                                        | All pins             | ±500  | V    |

|                    |                         | classification C4B, per ÀEC Q100-011                                                        | Corner pins          | ±750  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordancewith the ANSI/ESDA/JEDEC JS-001 specification.

# 6.3 Recommended Operating Conditions

over operating junction temperature range (unless otherwise noted)

|                    |                                |                              | MIN                 | NOM MAX             | UNIT |

|--------------------|--------------------------------|------------------------------|---------------------|---------------------|------|

| V <sub>CC</sub>    | Device supply voltage          |                              | 3                   | 5.5                 | V    |

| V <sub>SENSE</sub> | LED supply voltage             |                              |                     | 8                   | V    |

| Vo                 | Output voltage                 |                              |                     | 8                   | V    |

| VIL                | Input logic-low voltage        | BLANK, GCLK, LATCH, SCK, SDI | 0                   | 0.3 V <sub>CC</sub> | V    |

| $V_{IH}$           | Input logic-high voltage       | BLANK, GCLK, LATCH, SCK, SDI | 0.7 V <sub>CC</sub> | V <sub>CC</sub>     | V    |

| I <sub>OH</sub>    | High-level output current      | SDO                          |                     | 1                   | mA   |

|                    | Low lovel input ourrept        | SDO                          |                     | 1                   | mA   |

| IOL                | Low-level input current        | ERR                          |                     | 5                   | mA   |

| I <sub>O</sub>     | Constant output sink current   | OUTR0-OUTR7, OUTB0-OUTB7     | 2                   | 50                  | mA   |

| T <sub>A</sub>     | Operating ambient temperature  |                              | -40                 | 125                 | °C   |

| TJ                 | Operating junction temperature |                              | -40                 | 150                 | °C   |

#### TLC6C5716-Q1

SLVSEB5A – JULY 2018 – REVISED AUGUST 2018

www.ti.com

STRUMENTS

ÈXAS

### 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | TLC6C5716-Q1<br>DAP (HTSSOP)<br>38 PINS | UNIT |

|-----------------------|----------------------------------------------|-----------------------------------------|------|

| D                     | Junction-to-ambient thermal resistance       | 39.6                                    | °C/W |

| $R_{	hetaJA}$         |                                              | 39.0                                    | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 31.2                                    | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 18.0                                    | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.8                                     | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 18.1                                    | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.0                                     | °C/W |

(1) For more information about traditional and newthermalmetrics, see SemiconductorandlCPackageThermal Metrics.

## 6.5 Electrical Characteristics

$V_{CC} = 3 \text{ V}$  to 5.5 V,  $T_J = -40^{\circ}$ Cto150°C,  $V_{SENSE} = 5 \text{ V}$ , GS = FFFh, BC = FFh, DC = 7Fh with upper dotcorrection(DC)range (unless otherwise noted)

|                        | PARAMETER                                                                                    | TEST CONDITIONS                                                                                                | MIN            | TYP  | MAX                 | UNIT  |

|------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------|------|---------------------|-------|

| POWER SUP              | PPLIES (V <sub>CC</sub> , GND)                                                               |                                                                                                                |                |      |                     |       |

|                        |                                                                                              | SDI, SCK, LATCH = L, BLANK = L, GCLK<br>= L, $V_{OUT}$ = 1 V, $I_{OUT}$ = 2 mA                                 |                | 4.2  | 5.5                 |       |

|                        |                                                                                              | SDI, SCK, LATCH = L, BLANK = L, GCLK<br>= L, $V_{OUT}$ = 1 V, $I_{OUT}$ = 20 mA                                |                | 7.7  | 9                   |       |

| I <sub>CC</sub>        | Supply current                                                                               | SDI, SCK, LATCH = L, BLANK = H, GCLK = 8 MHz, $V_{OUT}$ = 1 V, $I_{OUT}$ = 20 mA , autorepeat on               |                | 8.3  | 10                  | mA    |

|                        |                                                                                              | SDI, SCK, LATCH = L, BLANK = H, GCLK = 8 MHz, $V_{OUT}$ = 1 V, $I_{OUT}$ = 50 mA , autorepeat on               |                | 13.5 | 16                  |       |

| LOGIC INPU             | TS (SDI, SCK, LATCH, GCLK, B                                                                 | LANK)                                                                                                          |                |      |                     |       |

| I <sub>lkg</sub>       | Input leakage current                                                                        | V <sub>I</sub> at SCK, LATCH, GCLK = V <sub>CC</sub> ; V <sub>I</sub> at<br>SDI, SCK, LATCH, BLANK, GCLK = GND | -1             |      | 1                   | μA    |

| R <sub>pd</sub>        | Pulldown resistance at<br>BLANK, GCLK                                                        |                                                                                                                | 250            | 500  | 750                 | kΩ    |

| CONTROL O              | UTPUTS (IREF, ERR, SDO)                                                                      |                                                                                                                |                |      |                     |       |

| V <sub>IREF</sub>      | IREF voltage                                                                                 | $R_{IREF} = 0.96 \text{ k}\Omega$                                                                              | 1.17           | 1.2  | 1.23                | V     |

| V <sub>OH</sub>        | High-level output voltage                                                                    | At SDO, $I_{OH} = -1 \text{ mA}$                                                                               | $V_{CC} - 0.4$ |      | V <sub>CC</sub>     | V     |

| V <sub>OL</sub>        | Low-level output voltage                                                                     | At SDO, I <sub>OL</sub> = 1 mA                                                                                 |                |      | 0.4                 | V     |

| V <sub>ERR</sub>       | ERR pin open-drain voltage drop                                                              | I <sub>ERR</sub> = 4 mA                                                                                        |                |      | 0.1 V <sub>CC</sub> | V     |

| I <sub>lkg(ERR)</sub>  | ERR pin leakage current                                                                      | $V_{ERR} = 5 V$                                                                                                |                |      | 1                   | μA    |

| OUTPUT ST              | AGE                                                                                          |                                                                                                                |                |      |                     |       |

| V                      |                                                                                              | $V_{CC} = 3.6 \text{ V}, I_{OUT} = 50 \text{ mA}$                                                              |                |      | 0.67                | V     |

| V <sub>(OUT,min)</sub> | Minimum output voltage                                                                       | V <sub>CC</sub> = 3 V, I <sub>OUT</sub> = 50 mA                                                                |                |      | 0.7                 | V     |

| K <sub>(OUT)</sub>     | Ratio of output current to<br>IREF current, K = I <sub>(OUTx)</sub> /<br>I <sub>(IREF)</sub> |                                                                                                                |                | 40   |                     | mA/mA |

| I <sub>lkg(OUT)</sub>  | Output leakage current                                                                       | $      BLANK = L, V_{OUT} = 7 V, V_{SENSE} = 7 V, \\       I_{OUT} = 50 mA                                  $  |                |      | 0.1                 | μA    |

#### **Electrical Characteristics (continued)**

$V_{CC}$  = 3 V to 5.5 V,  $T_{J}$ =-40°Cto150°C,  $V_{SENSE}$  = 5 V, GS = FFFh, BC = FFh, DC = 7Fh with upper dotcorrection(DC)range (unless otherwise noted)

| PARAMETER                          | TEST CONDITIONS                                                                                                                                                                                                                               | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TYP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| URACY                              |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                    | $V_{OUT}$ = 1 V, $R_{IREF}$ = 24 k $\Omega$                                                                                                                                                                                                   | 1.86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Constant output current            | $V_{OUT}$ = 1 V, $R_{IREF}$ = 0.96 k $\Omega$                                                                                                                                                                                                 | 46.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 53.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                    | V <sub>OUT</sub> = 1V, R <sub>IREF</sub> open or short                                                                                                                                                                                        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Current accuracy (channel-         | $V_{OUT} = 1 \text{ V}, I_{OUT} = 50 \text{ mA}$                                                                                                                                                                                              | -4%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| to-channel in same color<br>group) | $V_{OUT} = 1 \text{ V}, I_{OUT} = 2 \text{ mA}$                                                                                                                                                                                               | -4%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |