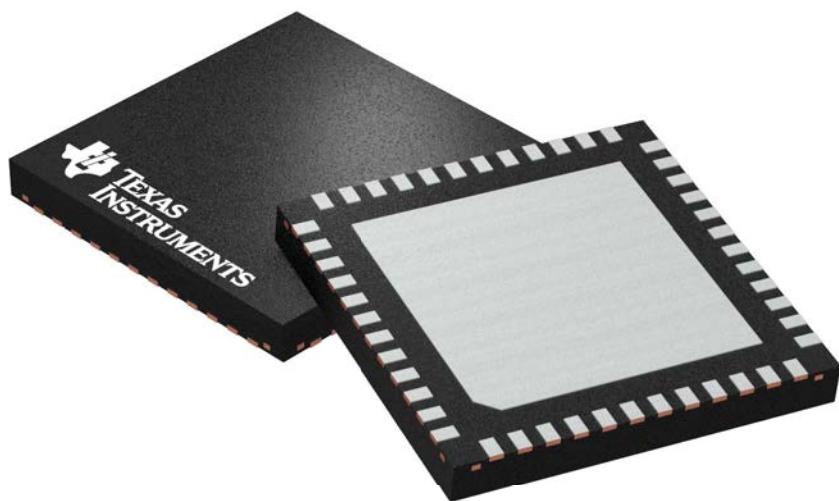

# LMK03318 Ultra-Low-Noise Jitter Clock Generator Family With One PLL, Eight Outputs, Integrated EEPROM

## 1 Features

- Ultra-Low Noise, High Performance

- Jitter: 100-fs RMS Typical,  $F_{OUT} > 100$  MHz

- PSNR: –80 dBc, Robust Supply Noise Immunity

- Flexible Device Options

- Up to 8 AC-LVPECL, AC-LVDS, AC-CML, HCSL or LVCMOS Outputs, or Any Combination

- Pin Mode, I<sup>2</sup>C Mode, EEPROM Mode

- 71-Pin Selectable Pre-programmed Default Start-Up Options

- Dual Inputs With Automatic or Manual Selection

- Crystal Input: 10 to 52 MHz

- External Input: 1 to 300 MHz

- Frequency Margining Options

- Fine Frequency Margining Using Low-Cost Pullable Crystal Reference

- Glitchless Coarse Frequency Margining (%) Using Output Dividers

- Other Features

- Supply: 3.3-V Core, 1.8-V, 2.5-V, or 3.3-V Output Supply

- Industrial Temperature Range (–40°C to 85°C)

## 2 Applications

- Switches and Routers

- Network and Telecom Line Cards

- Servers and Storage Systems

- Wireless Base Station

- PCIe Gen1, Gen2, Gen3, Gen4

- Test and Measurement

- Broadcast Infrastructure

## 3 Description

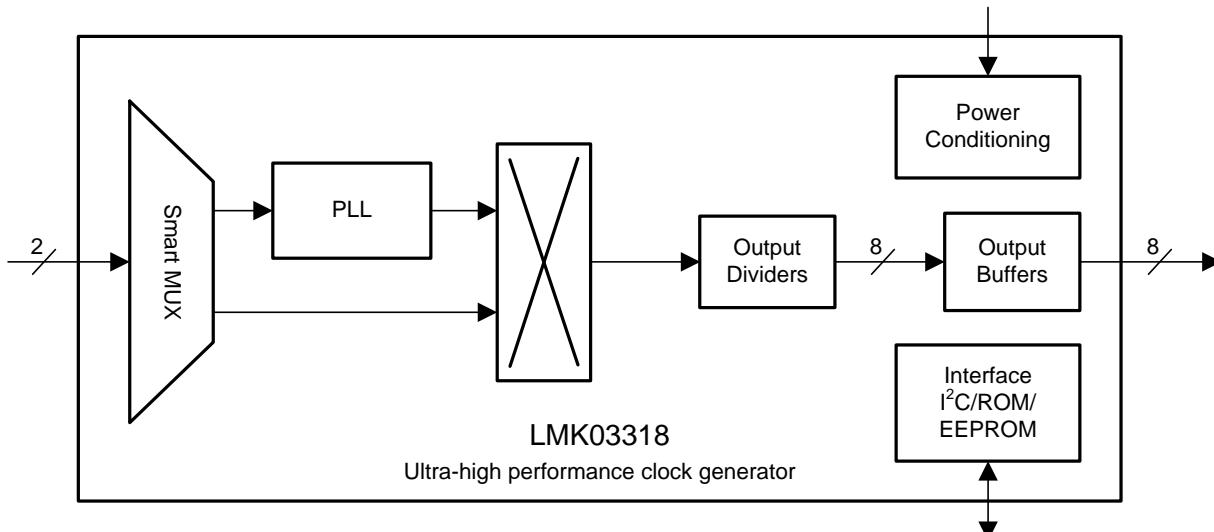

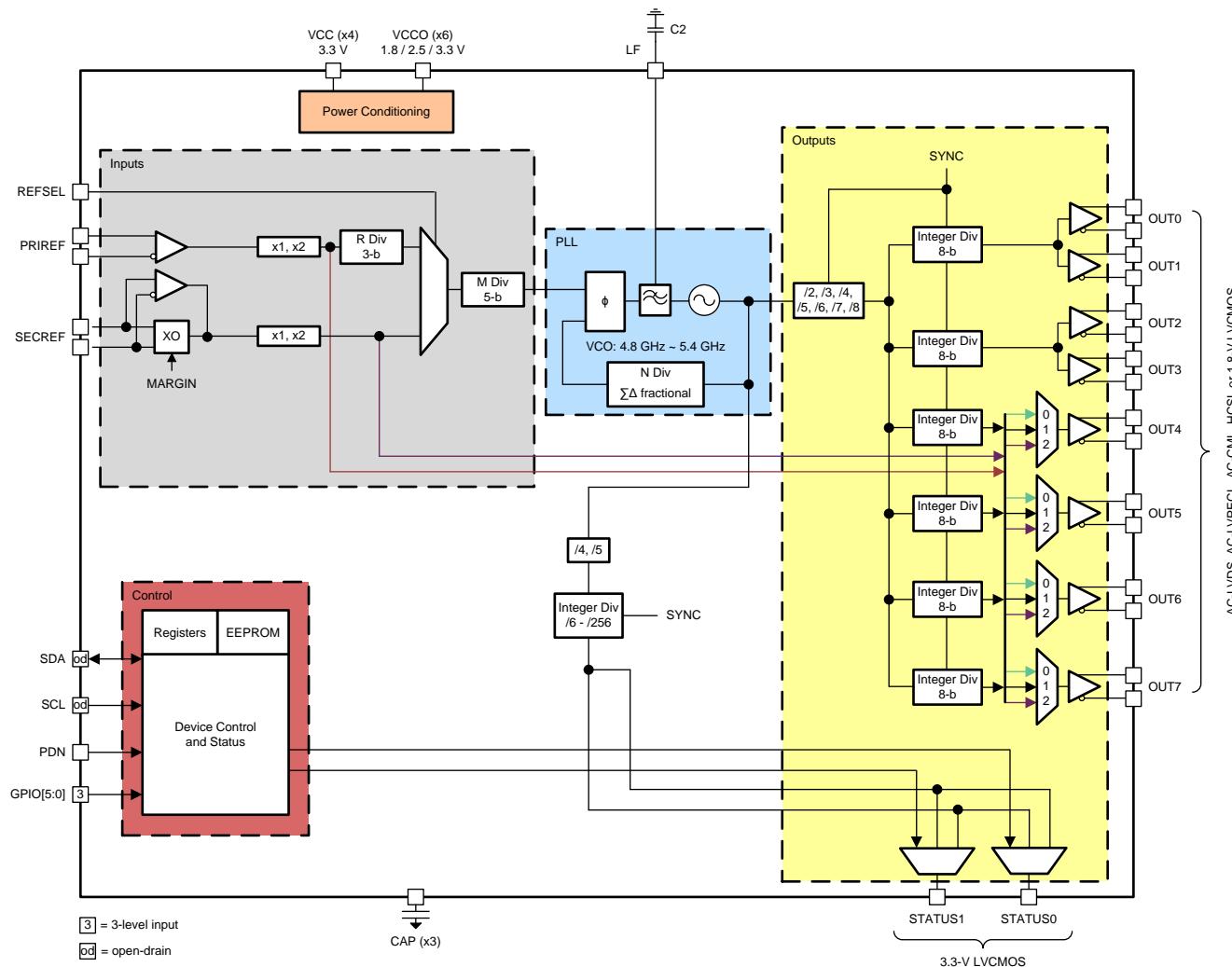

The LMK03318 device is an ultra-low-noise PLLATINUM™ clock generator with one fractional-N frequency synthesizer with integrated VCO, flexible clock distribution and fanout, and pin-selectable configuration states stored in on-chip EEPROM. The device can generate multiple clocks for various multi-gigabit serial interfaces and digital devices, thus reducing BOM cost and board area and improving reliability by replacing multiple oscillators and clock distribution devices. The ultra-low jitter reduces bit-error rate (BER) in high-speed serial links.

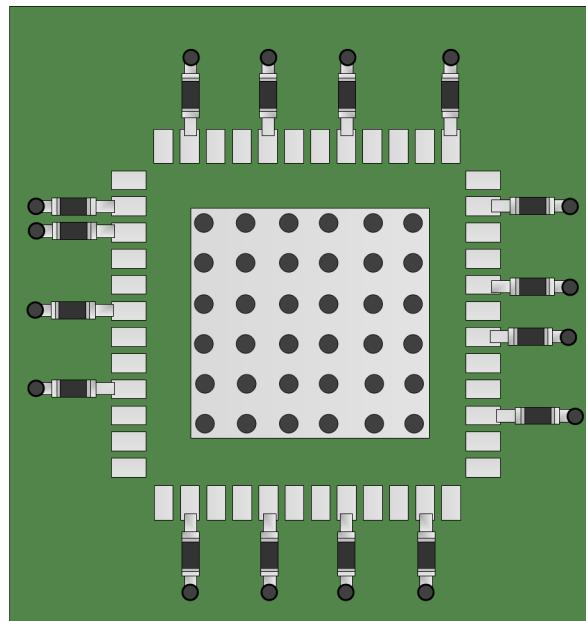

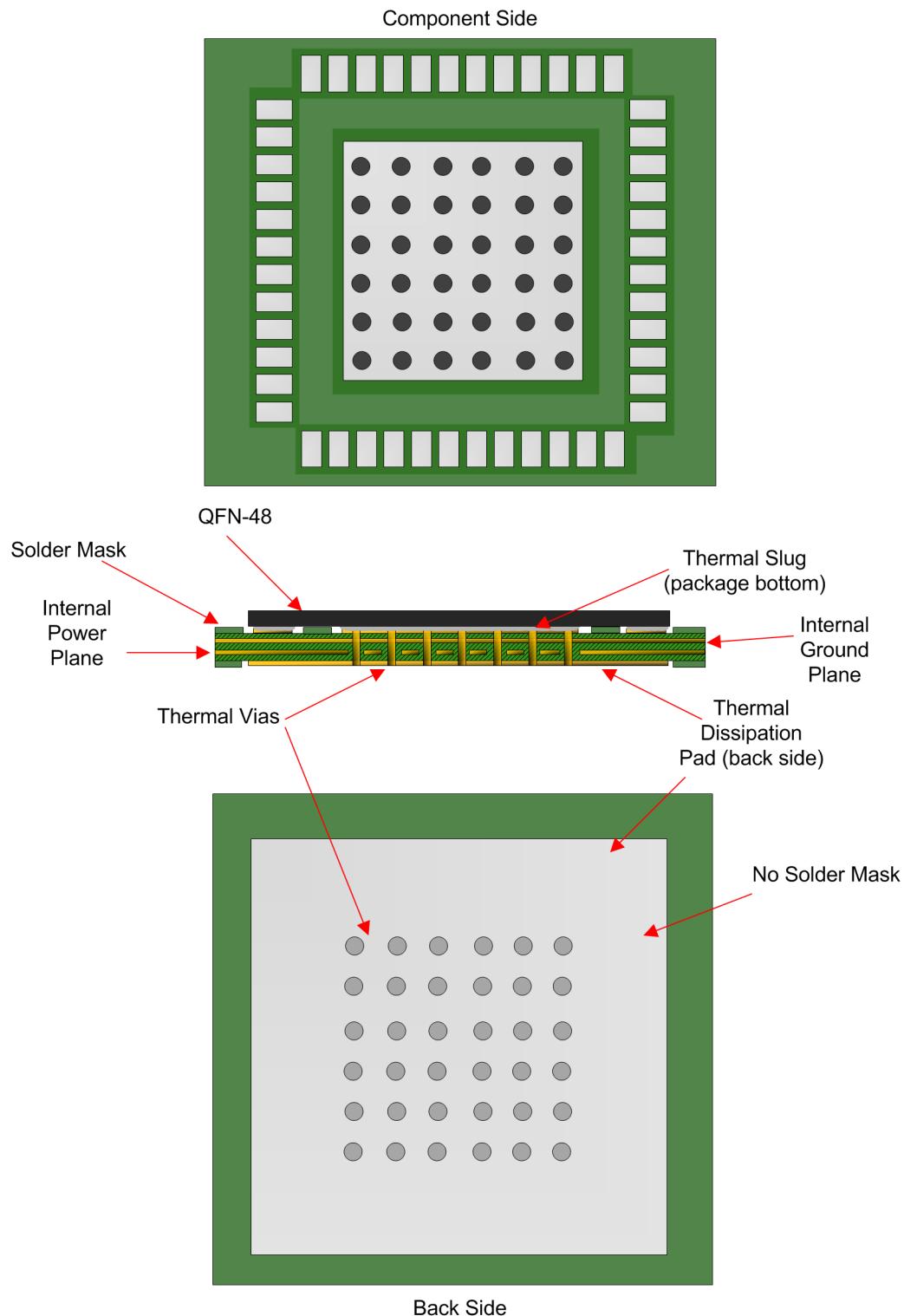

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| LMK03318    | WQFN (48) | 7.00 mm × 7.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

### LMK03318 Simplified Block Diagram

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## Table of Contents

|                                                                              |    |                                                                                     |     |

|------------------------------------------------------------------------------|----|-------------------------------------------------------------------------------------|-----|

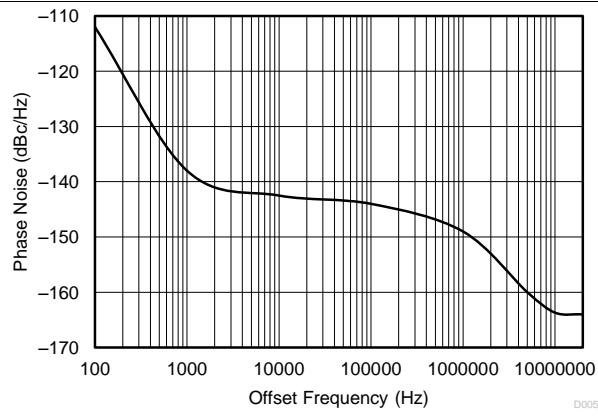

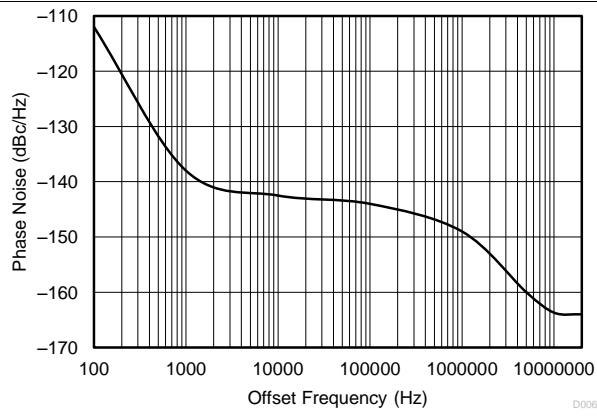

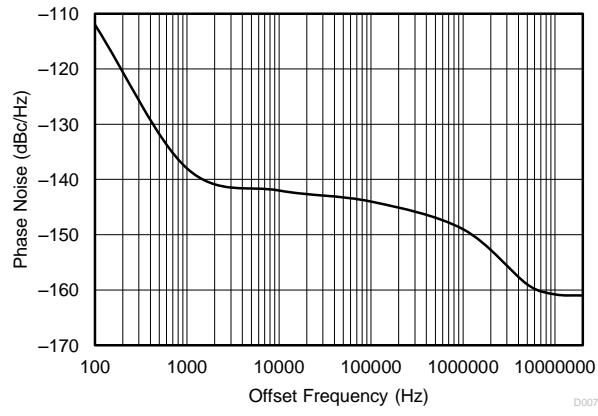

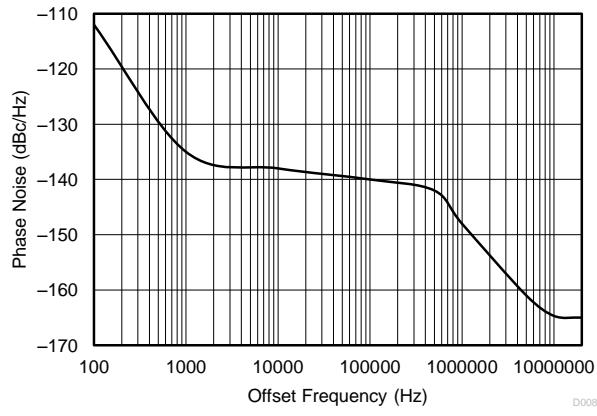

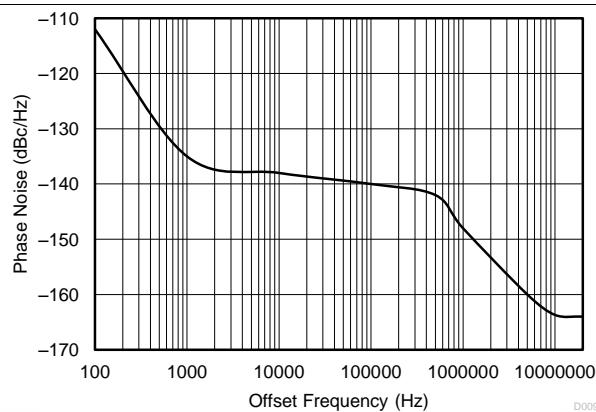

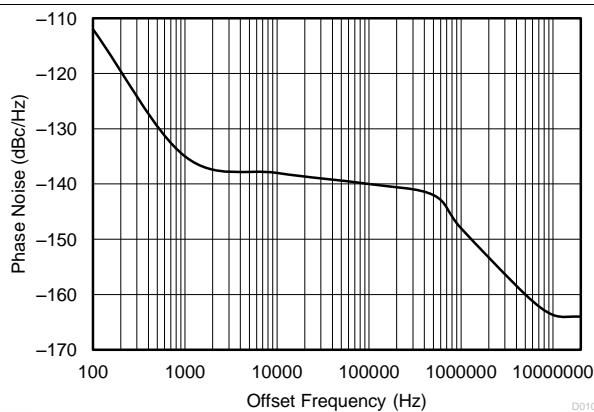

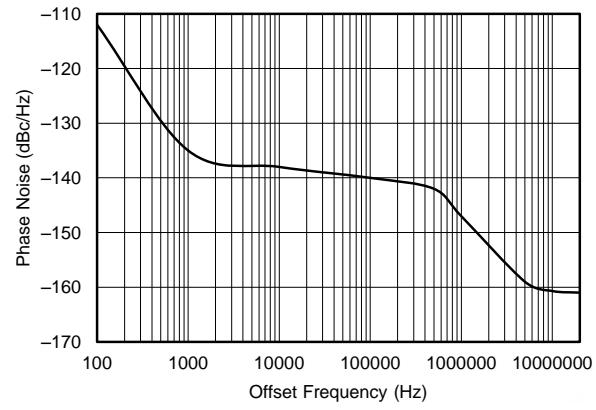

| <b>1 Features</b> .....                                                      | 1  | Phase Noise Characteristics .....                                                   | 17  |

| <b>2 Applications</b> .....                                                  | 1  | 8.26 Closed-Loop Output Jitter Characteristics .....                                | 17  |

| <b>3 Description</b> .....                                                   | 1  | 8.27 PCIe Clock Output Jitter .....                                                 | 17  |

| <b>4 Revision History</b> .....                                              | 3  | 8.28 Typical Power Supply Noise Rejection Characteristics .....                     | 18  |

| <b>5 Description (continued)</b> .....                                       | 4  | 8.29 Typical Power-Supply Noise Rejection Characteristics .....                     | 18  |

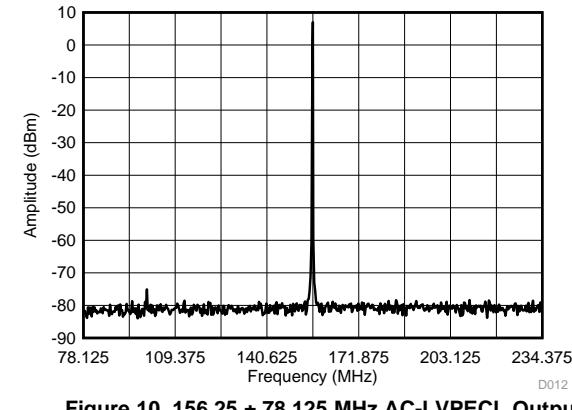

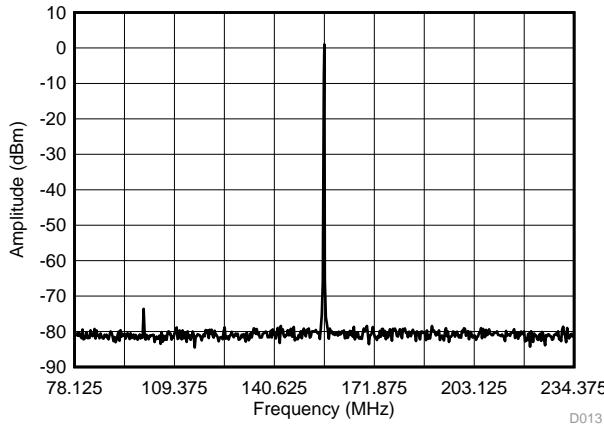

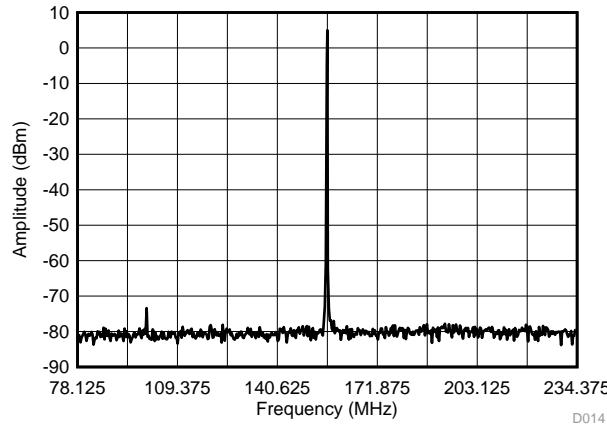

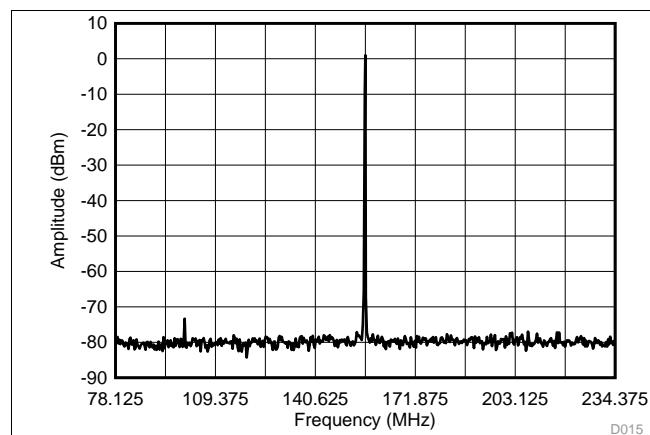

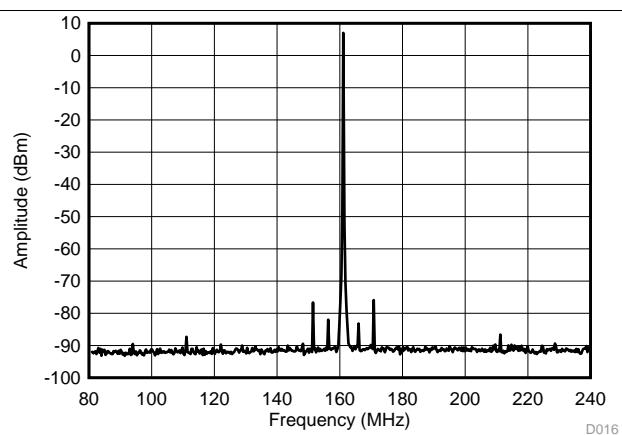

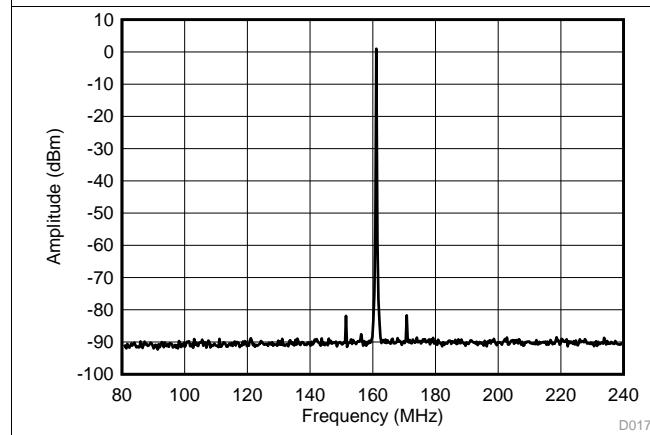

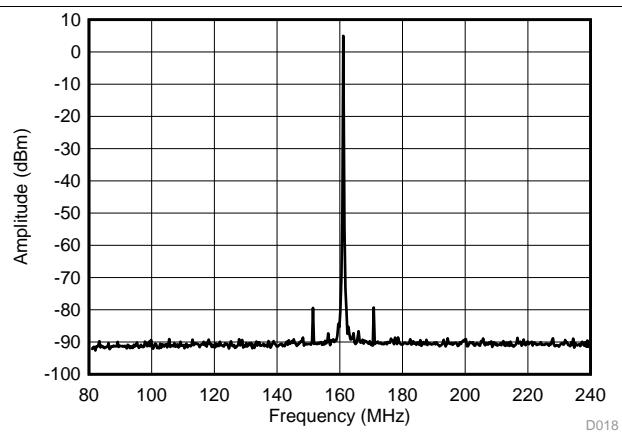

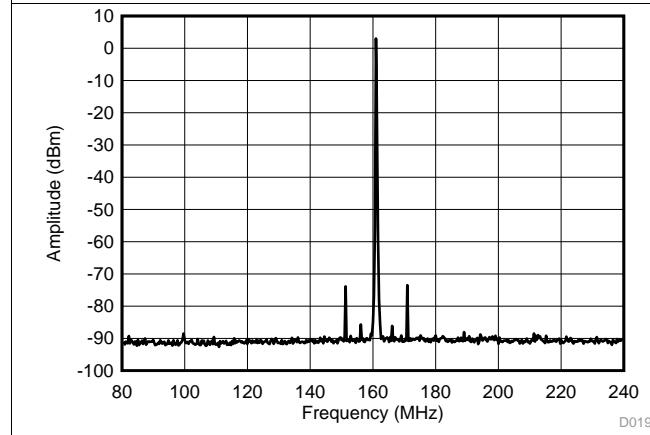

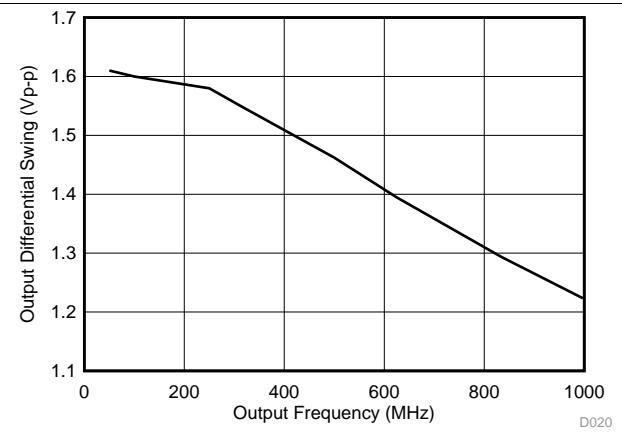

| <b>6 Device Comparison Table</b> .....                                       | 4  | 8.30 Typical Closed-Loop Output Spur Characteristics                                | 18  |

| <b>7 Pin Configuration and Functions</b> .....                               | 5  | 8.31 Typical Characteristics .....                                                  | 19  |

| <b>8 Specifications</b> .....                                                | 7  | <b>9 Parameter Measurement Information</b> .....                                    | 23  |

| 8.1 Absolute Maximum Ratings .....                                           | 7  | 9.1 Test Configurations .....                                                       | 23  |

| 8.2 ESD Ratings .....                                                        | 7  | <b>10 Detailed Description</b> .....                                                | 27  |

| 8.3 Recommended Operating Conditions .....                                   | 8  | 10.1 Overview .....                                                                 | 27  |

| 8.4 Thermal Information .....                                                | 8  | 10.2 Functional Block Diagram .....                                                 | 27  |

| 8.5 Thermal Information .....                                                | 8  | 10.3 Feature Description .....                                                      | 28  |

| 8.6 Electrical Characteristics - Power Supply .....                          | 9  | 10.4 Device Functional Modes .....                                                  | 32  |

| 8.7 Pullable Crystal Characteristics (SECREF_P, SECREF_N) .....              | 10 | 10.5 Programming .....                                                              | 50  |

| 8.8 Non-Pullable Crystal Characteristics (SECREF_P, SECREF_N) .....          | 11 | 10.6 Register Maps .....                                                            | 71  |

| 8.9 Clock Input Characteristics (PRIREF_P/PRIREF_N, SECREF_P/SECREF_N) ..... | 11 | <b>11 Application and Implementation</b> .....                                      | 117 |

| 8.10 VCO Characteristics .....                                               | 11 | 11.1 Application Information .....                                                  | 117 |

| 8.11 PLL Characteristics .....                                               | 12 | 11.2 Typical Applications .....                                                     | 117 |

| 8.12 1.8-V LVCMOS Output Characteristics (OUT[7:0]) .....                    | 12 | <b>12 Power Supply Recommendations</b> .....                                        | 127 |

| 8.13 LVCMOS Output Characteristics (STATUS[1:0]) ..                          | 12 | 12.1 Device Power Up Sequence .....                                                 | 127 |

| 8.14 Open-Drain Output Characteristics (STATUS[1:0]) .....                   | 13 | 12.2 Device Power Up Timing .....                                                   | 128 |

| 8.15 AC-LVPECL Output Characteristics .....                                  | 13 | 12.3 Power Down .....                                                               | 129 |

| 8.16 AC-LVDS Output Characteristics .....                                    | 13 | 12.4 Power Rail Sequencing, Power Supply Ramp Rate, and Mixing Supply Domains ..... | 129 |

| 8.17 AC-CML Output Characteristics .....                                     | 14 | 12.5 Power Supply Bypassing .....                                                   | 131 |

| 8.18 HCSL Output Characteristics .....                                       | 14 | <b>13 Layout</b> .....                                                              | 133 |

| 8.19 Power-On Reset Characteristics .....                                    | 14 | 13.1 Layout Guidelines .....                                                        | 133 |

| 8.20 2-Level Logic Input Characteristics (HW_SW_CTRL, PDN, GPIO[5:0]) .....  | 15 | 13.2 Layout Example .....                                                           | 133 |

| 8.21 3-Level Logic Input Characteristics (REFSEL, GPIO[3:1]) .....           | 15 | <b>14 Device and Documentation Support</b> .....                                    | 135 |

| 8.22 Analog Input Characteristics (GPIO[5]) .....                            | 15 | 14.1 Device Support .....                                                           | 135 |

| 8.23 I <sup>2</sup> C-Compatible Interface Characteristics (SDA, SCL) .....  | 16 | 14.2 Receiving Notification of Documentation Updates .....                          | 135 |

| 8.24 Typical 156.25-MHz Closed-Loop Output Phase Noise Characteristics ..... | 16 | 14.3 Community Resources .....                                                      | 135 |

| 8.25 Typical 161.1328125-MHz Closed-Loop Output                              |    | 14.4 Trademarks .....                                                               | 135 |

## 4 Revision History

| <b>Changes from Revision D (December 2017) to Revision E</b>                                                 | <b>Page</b> |

|--------------------------------------------------------------------------------------------------------------|-------------|

| • Clarified note about $V_{OH}$ (rail-to-rail swing only with $VDDO = 1.8\text{ V} \pm 5\%$ ).....           | 12          |

| • Changed Slew Rate minimum and maximum from: 2.25 V/ns and 5 V/ns to: 1 V/ns and 4 V/ns, respectively ..... | 14          |

| • Updated PROID reset value to be 0x33 (was 0x31).....                                                       | 71          |

| • Updated REVID reset value to be 0x02 (was 0x01) .....                                                      | 71          |

| • Added the <i>Support for PCB Temperature up to 105°C</i> subsection.....                                   | 133         |

| <b>Changes from Revision C (August 2017) to Revision D</b>                                                                  | <b>Page</b> |

|-----------------------------------------------------------------------------------------------------------------------------|-------------|

| • Added bullets to the <i>Applications</i> section .....                                                                    | 1           |

| • Added <i>PCIe Clock Output Jitter</i> table.....                                                                          | 17          |

| • Added tablenotes to <a href="#">Table 10</a> .....                                                                        | 57          |

| • Changed the first paragraph of the <i>Powering Up From Single-Supply Rail</i> section .....                               | 129         |

| • Changed the first paragraph of the <i>Powering Up From Split-Supply Rails</i> section and <a href="#">Figure 84</a> ..... | 130         |

| • Changed the first paragraph and added new content to the <i>Slow Power-Up Supply Ramp</i> section .....                   | 130         |

| • Changed the first paragraph of the <i>Non-Monotonic Power-Up Supply Ramp</i> section .....                                | 131         |

| <b>Changes from Revision B (August 2016) to Revision C</b>                                      | <b>Page</b> |

|-------------------------------------------------------------------------------------------------|-------------|

| • Added a table note to <i>Recommended Operating Conditions</i> explaining the NOM values ..... | 8           |

| • Changed $V_{bb} = 1.3\text{ V}$ to 1.8 in <a href="#">Figure 45</a> .....                     | 35          |

| <b>Changes from Revision A (December 2015) to Revision B</b>             | <b>Page</b> |

|--------------------------------------------------------------------------|-------------|

| • Changed title from Configuring the PLL to Device Functional Modes..... | 32          |

| • Changed title from Interface and Control to Programming .....          | 50          |

| • Added new sections to Power Supply Recommendations .....               | 129         |

## 5 Description (continued)

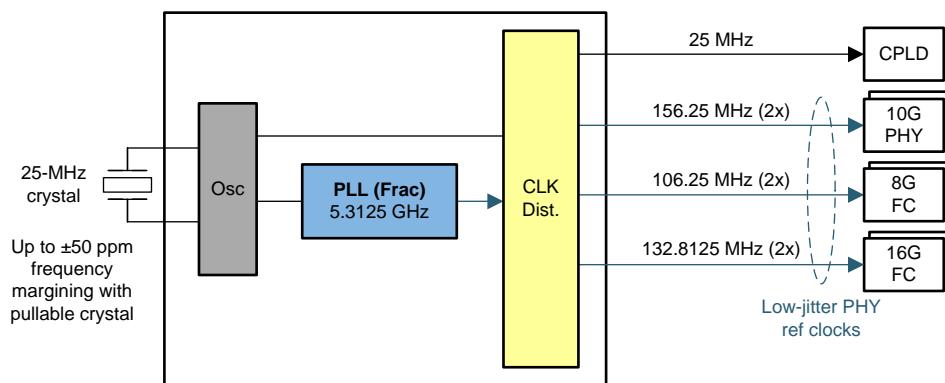

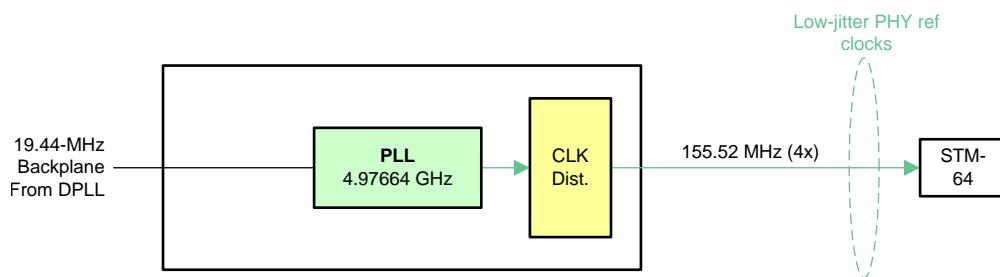

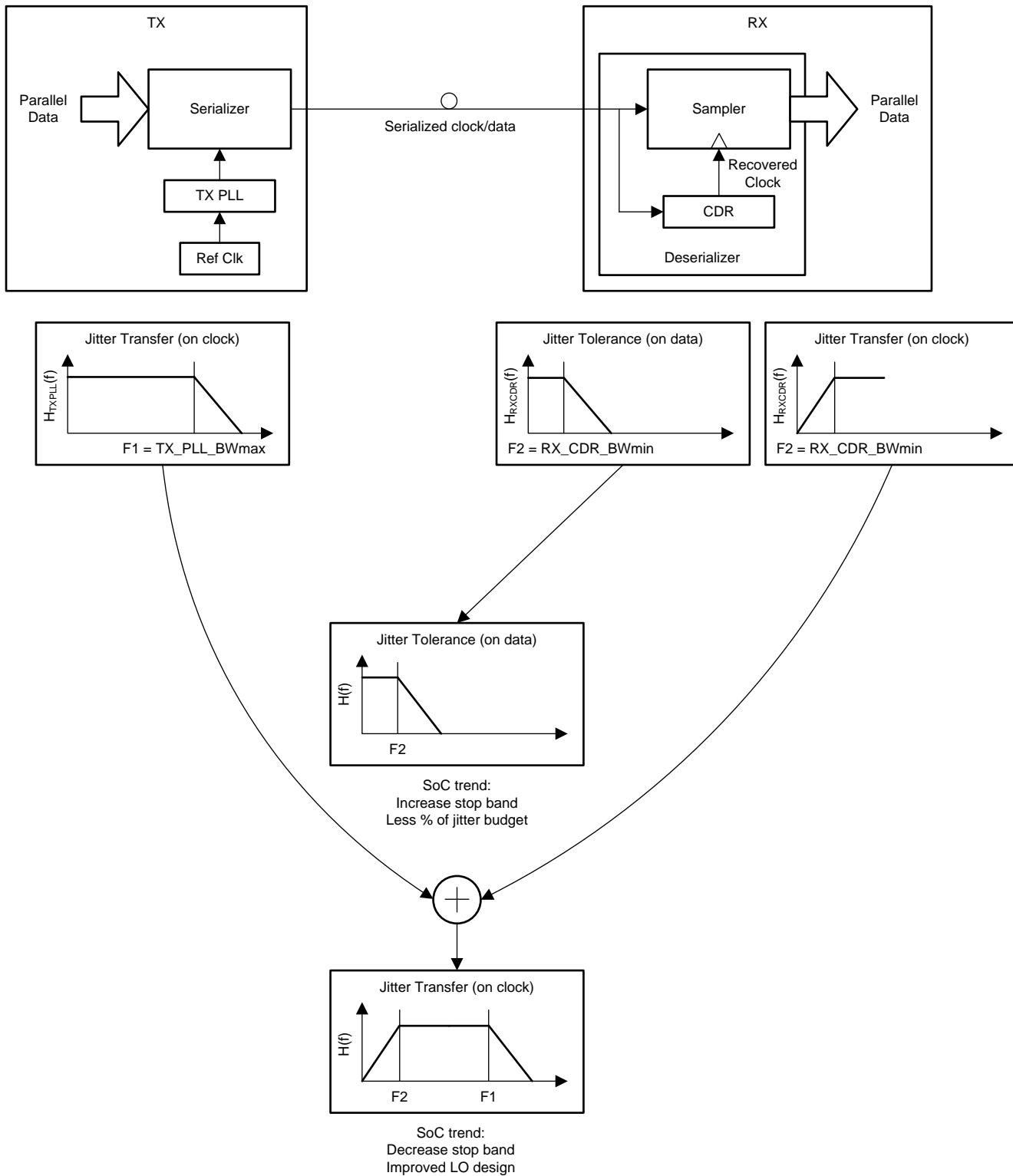

For the PLL, a differential clock, a single-ended clock, or a crystal input can be selected as the reference clock. The selected reference input can be used to lock the VCO frequency at an integer or fractional multiple of the reference input frequency. The VCO frequency can be tuned between 4.8 GHz and 5.4 GHz. The PLL offers the flexibility to select a predefined or user-defined loop bandwidth, depending on the needs of the application. The PLL has a post-divider that can be selected between divide-by 2, 3, 4, 5, 6, 7, or 8.

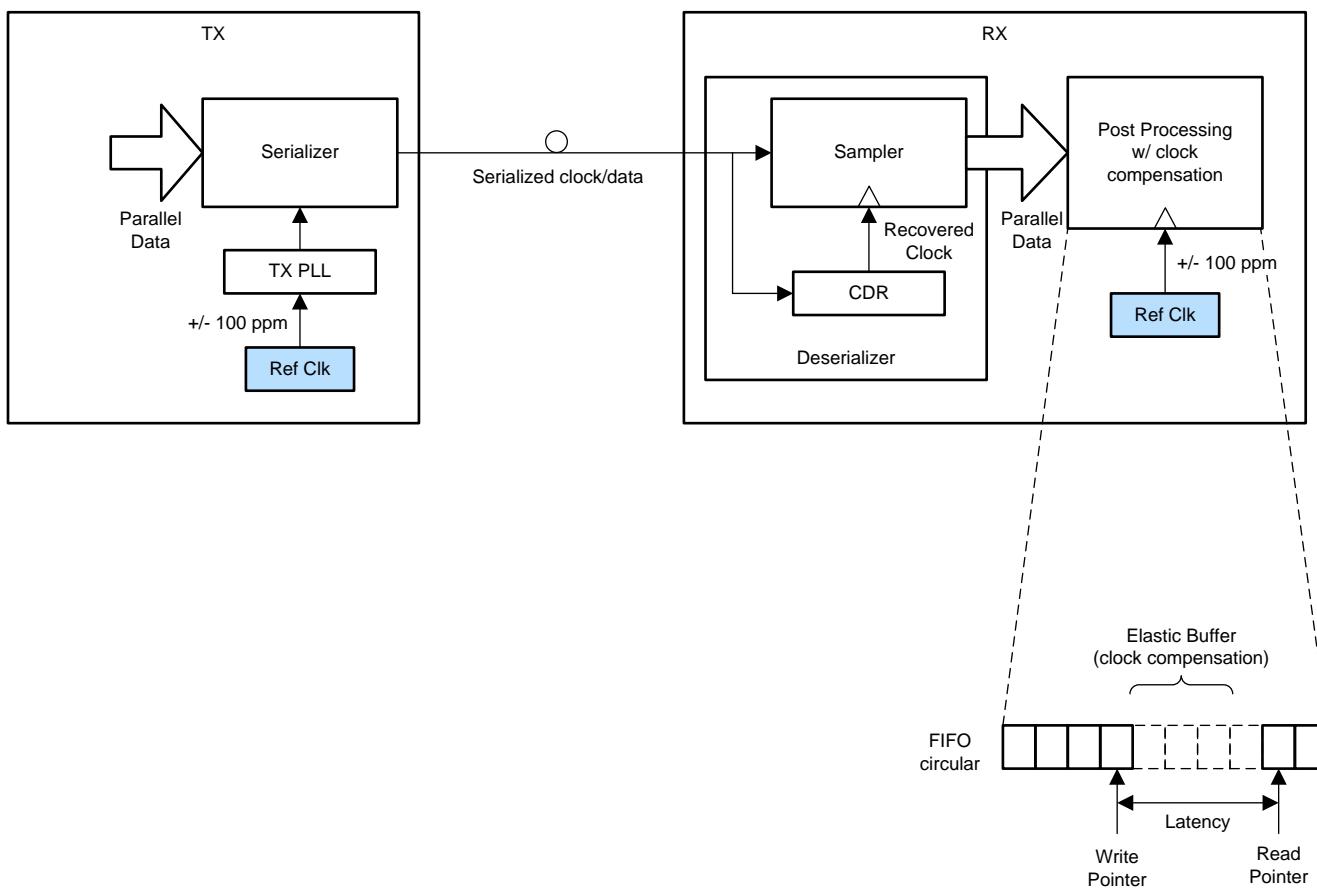

All the output channels can select the divided-down VCO clock from the PLL as the source for the output divider to set the final output frequency. Some output channels can also independently select the reference input for the PLL as an alternative source to be bypassed to the corresponding output buffers. The 8-bit output dividers support a divide range of 1 to 256 (even or odd), output frequencies up to 1 GHz, and output phase synchronization capability.

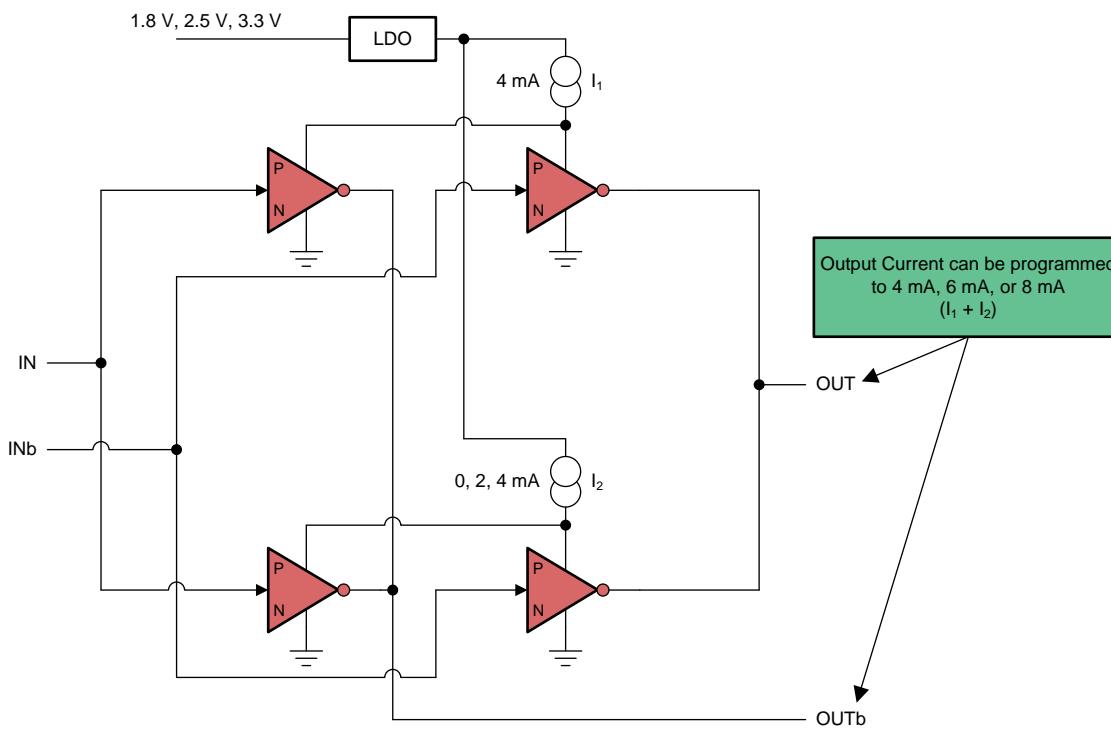

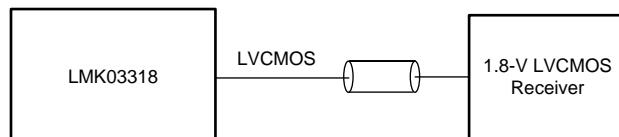

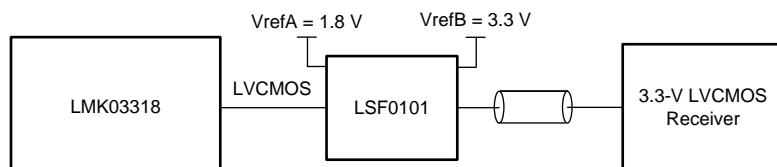

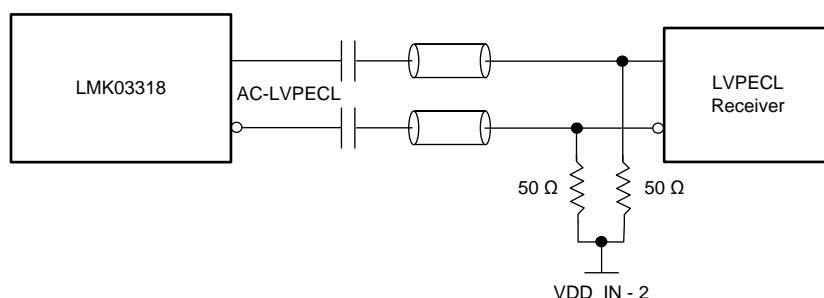

All output pairs are ground-referenced CML drivers with programmable swing that can be interfaced to LVDS, LVPECL, or CML receivers with AC coupling. All output pairs can also be independently configured as HCSL outputs or  $2 \times 1.8\text{-V}$  LVCMOS outputs. The outputs offer lower power at 1.8 V, higher performance and power supply noise immunity, and lower EMI compared to voltage-referenced driver designs (such as traditional LVDS and LVPECL drivers). Two additional 3.3-V LVCMOS outputs can be obtained via the STATUS pins. This is an optional feature in case of a need for 3.3-V LVCMOS outputs and device status signals are not needed.

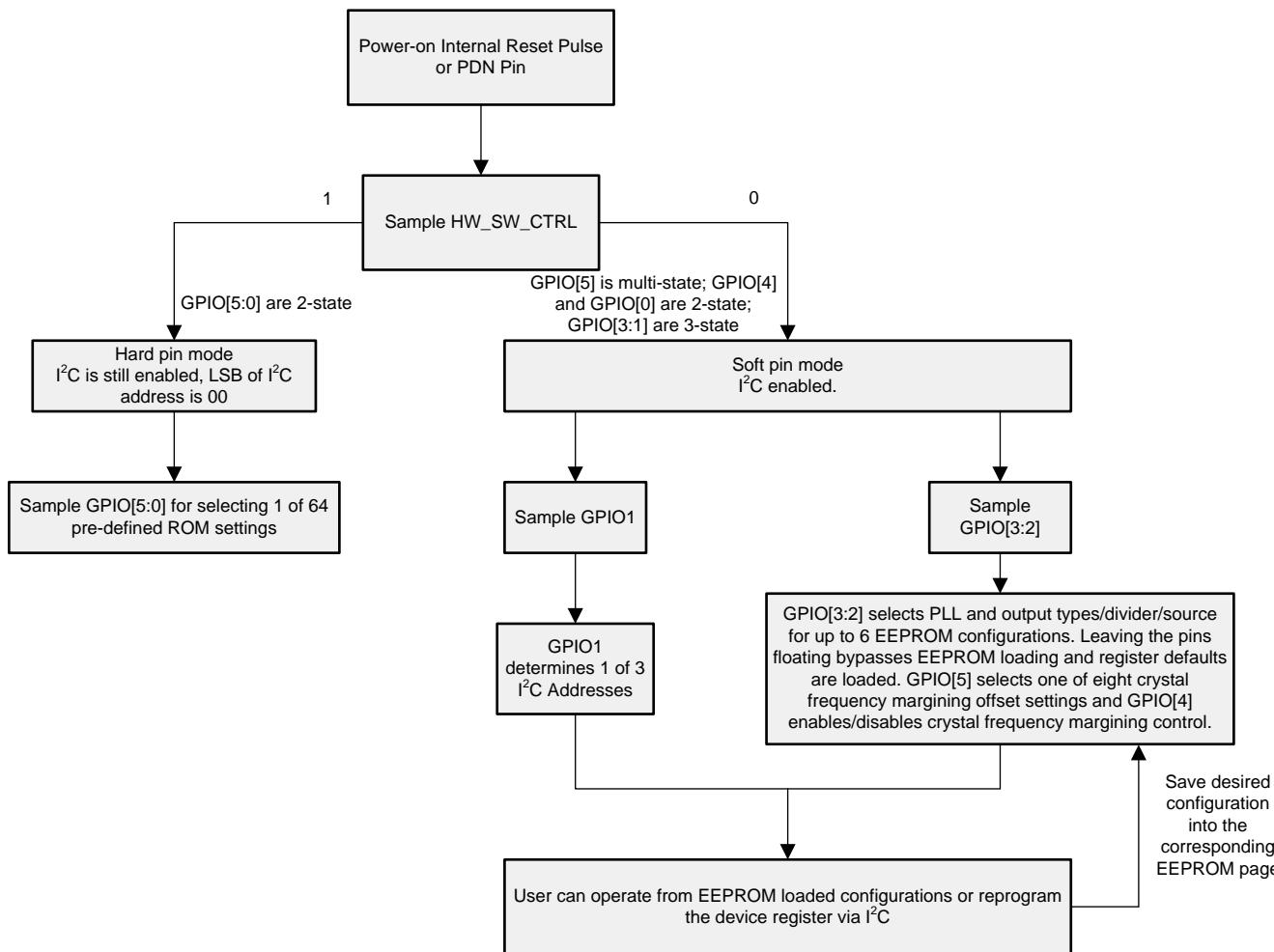

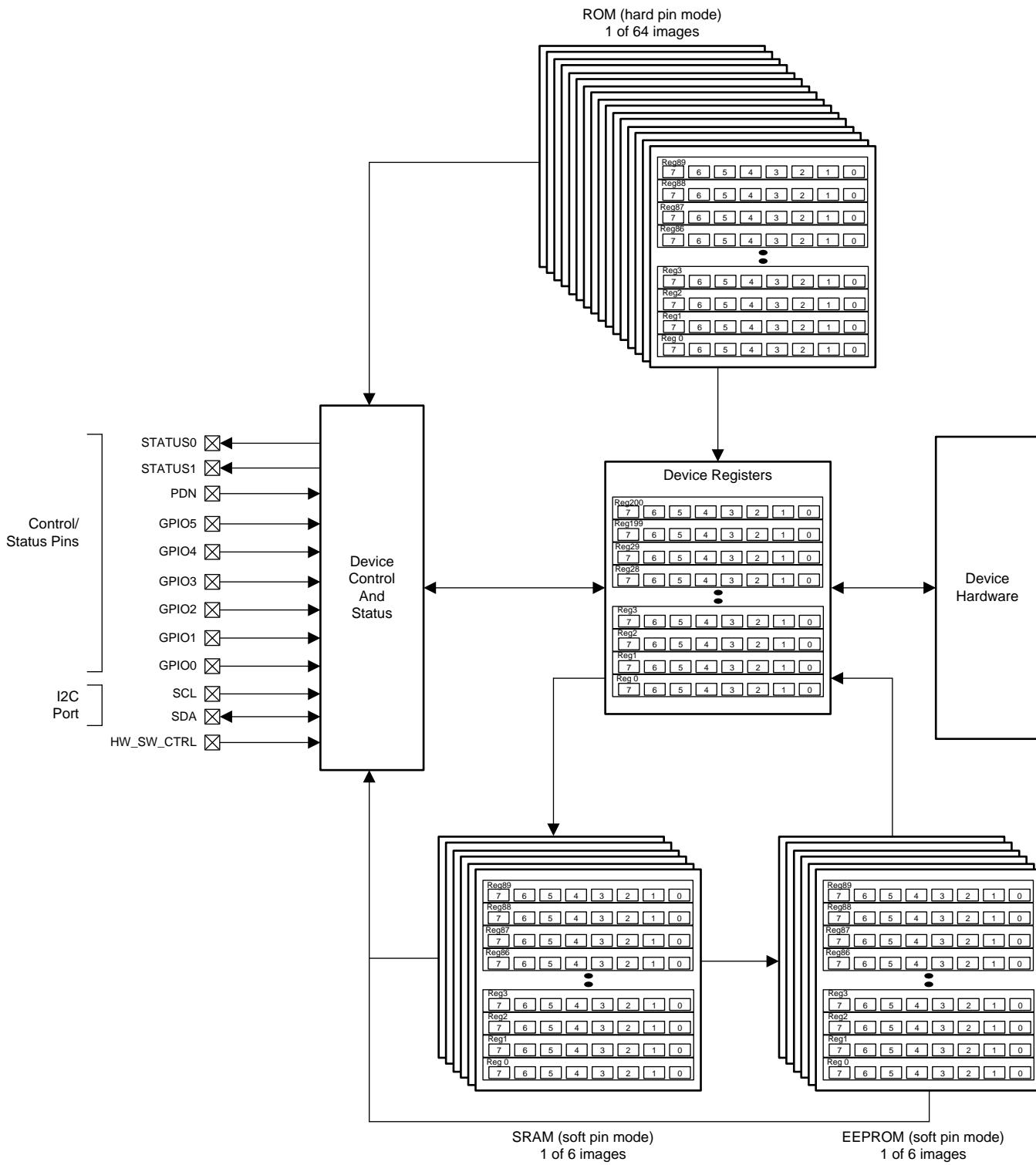

The device features self start-up from on-chip programmable EEPROM or pre-defined ROM memory, which offers multiple custom device modes selectable via pin control eliminating the need for serial programming. The device registers and on-chip EEPROM settings are fully programmable through the I<sup>2</sup>C-compatible serial interface. The device slave address is programmable in EEPROM and LSBs can be set with a 3-state pin.

The device provides two frequency margining options with glitch-free operation to support system design verification tests (DVT), such as standard compliance and system timing margin testing. Fine frequency margining (in ppm) can be supported by using a low-cost pullable crystal on the internal crystal oscillator (XO), and selecting this input as the reference to the PLL synthesizer. The frequency margining range is determined by the trim sensitivity of the crystal and the on-chip varactor range. XO frequency margining can be controlled through pin or I<sup>2</sup>C control for ease-of use and high flexibility. Coarse frequency margining (in %) is available on any output channel by changing the output divide value via I<sup>2</sup>C interface, which synchronously stops and restarts the output clock to prevent a glitch or runt pulse when the divider is changed.

Internal power conditioning provide excellent power supply noise rejection (PSNR), reducing the cost and complexity of the power delivery network. The analog and digital core blocks operate from  $3.3\text{-V} \pm 5\%$  supply and output blocks operate from  $1.8\text{-V}$ ,  $2.5\text{-V}$ , or  $3.3\text{-V} \pm 5\%$  supply.

## 6 Device Comparison Table

Table 1. LVPECL Output Jitter Over Different Integration Bandwidths

| OUTPUT FREQUENCY (MHz) | INTEGRATION BANDWIDTH            | TYPICAL JITTER (ps, rms) |

|------------------------|----------------------------------|--------------------------|

| < 100                  | 12 kHz - 5 MHz                   | 0.15                     |

| > 100                  | 1 kHz - 5 MHz<br>12 kHz - 20 MHz | 0.1                      |

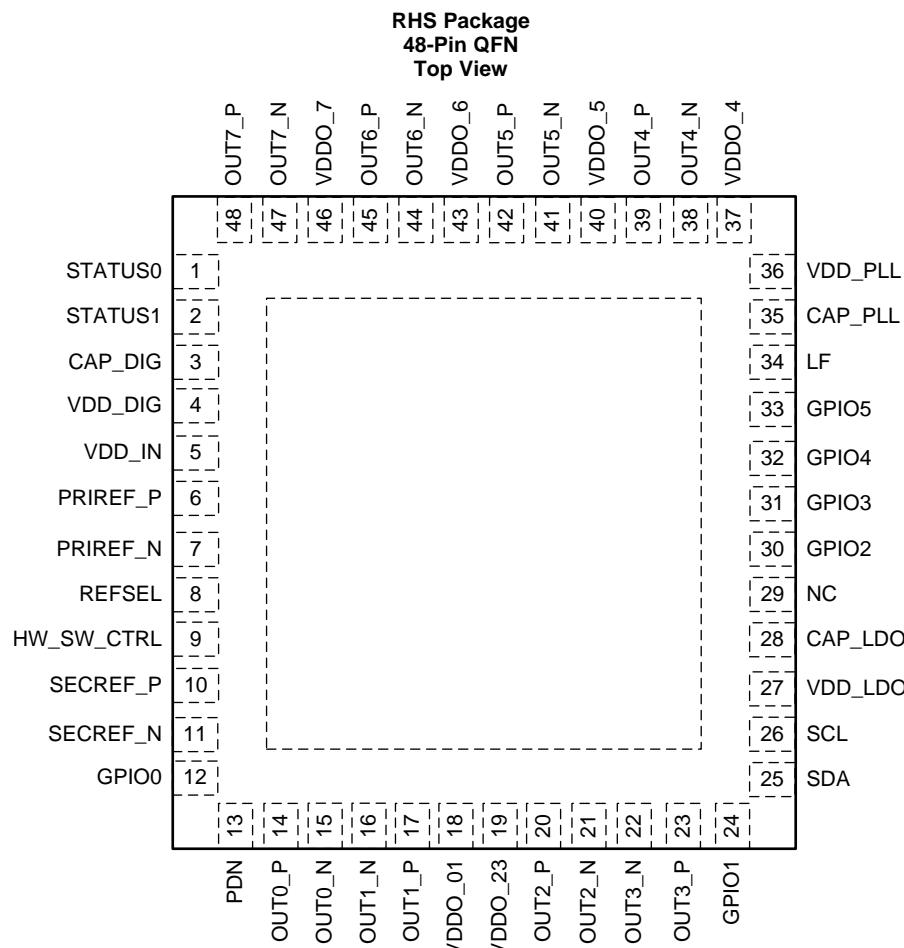

## 7 Pin Configuration and Functions

### Pin Functions

| NO.          | NAME    | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                          |

|--------------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>POWER</b> |         |        |                                                                                                                                                                                                                                                                                                                      |

| n/a          | DAP     | Ground | Die Attach Pad.<br>The DAP is an electrical connection and provides a thermal dissipation path. For proper electrical and thermal performance of the device, a 6 x 6 via pattern (0.3 mm holes) is recommended to connect the DAP to multiple ground layers of the PCB. Refer to <a href="#">Layout Guidelines</a> . |

| 4            | VDD_DIG | Analog | 3.3 V power supply for digital control and STATUS outputs.                                                                                                                                                                                                                                                           |

| 5            | VDD_IN  | Analog | 3.3 V power supply for input block.                                                                                                                                                                                                                                                                                  |

| 18           | VDDO_01 | Analog | 1.8 V, 2.5 V, or 3.3 V power supply for OUT0/OUT1 channel.                                                                                                                                                                                                                                                           |

| 19           | VDDO_23 | Analog | 1.8 V, 2.5 V, or 3.3 V power supply for OUT2/OUT3 channel.                                                                                                                                                                                                                                                           |

| 27           | VDD_LDO | Analog | 3.3 V power supply for PLL LDO.                                                                                                                                                                                                                                                                                      |

| 36           | VDD_PLL | Analog | 3.3 V power supply for PLL/VCO.                                                                                                                                                                                                                                                                                      |

| 37           | VDDO_4  | Analog | 1.8 V, 2.5 V, or 3.3 V power supply for OUT4 channel.                                                                                                                                                                                                                                                                |

| 40           | VDDO_5  | Analog | 1.8 V, 2.5 V, or 3.3 V power supply for OUT5 channel.                                                                                                                                                                                                                                                                |

| 43           | VDDO_6  | Analog | 1.8 V, 2.5 V, or 3.3 V power supply for OUT6 channel.                                                                                                                                                                                                                                                                |

| 46           | VDDO_7  | Analog | 1.8 V, 2.5 V, or 3.3 V power supply for OUT7 channel.                                                                                                                                                                                                                                                                |

**Pin Functions (continued)**

| NO.                      | NAME                  | TYPE      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|-----------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>INPUT BLOCK</b>       |                       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

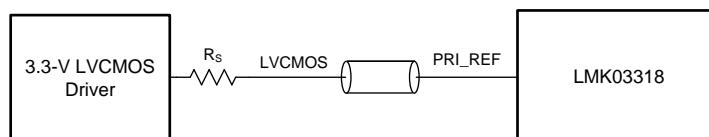

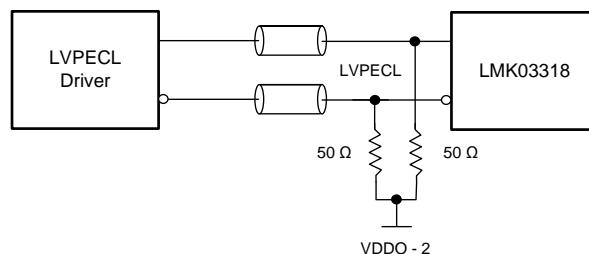

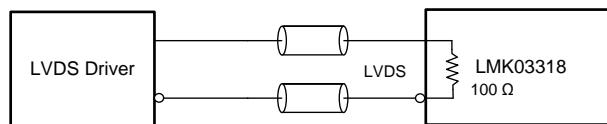

| 6, 7                     | PRIREF_P,<br>PRIREF_N | Universal | Primary reference clock.<br>Accepts a differential or single-ended input. Input pins have AC-coupling capacitors and biasing internally. For LVC MOS input, the non-driven input pin must be pulled down to ground.                                                                                                                                                                                                                                                            |

| 8                        | REFSEL                | LVC MOS   | Manual reference input selection for PLL (3-state).<br>Weak pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9                        | HW_SW_CTRL            | LVC MOS   | Selection for Hard Pin Mode (ROM), Soft Pin Mode (EEPROM), or Register Default Mode.<br>Weak pullup resistor.                                                                                                                                                                                                                                                                                                                                                                  |

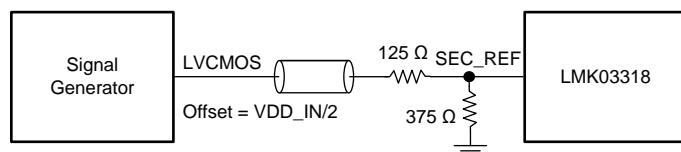

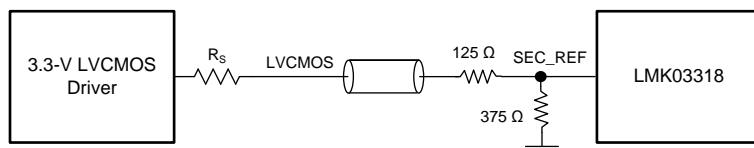

| 10, 11                   | SECREF_P,<br>SECREF_N | Universal | Secondary reference clock.<br>Accepts a differential or single-ended input or crystal input. Input pins have AC-coupling capacitors and biasing internally. For LVC MOS input, external input termination is needed to attenuate the swing to less than 2.6 V, and the non-driven input pin must be pulled down to ground.<br>For crystal input, AT-cut fundamental crystal must be used as per defined specification, and pullable crystal should be used for fine margining. |

| <b>SYNTHESIZER BLOCK</b> |                       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3                        | CAP_DIG               | Analog    | External bypass capacitor for digital blocks. Attach a 10 $\mu$ F to GND.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 28                       | CAP_LDO               | Analog    | External bypass capacitor for PLL LDO. Attach a 10 $\mu$ F to GND.                                                                                                                                                                                                                                                                                                                                                                                                             |

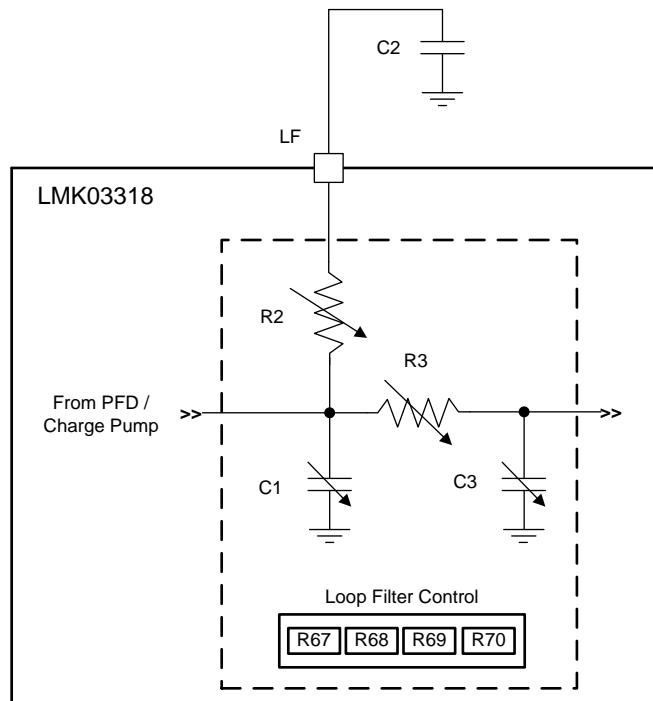

| 34                       | LF                    | Analog    | External loop filter for PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 35                       | CAP_PLL               | Analog    | External bypass capacitor for PLL. Attach a 10 $\mu$ F to GND.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>OUTPUT BLOCK</b>      |                       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14, 15                   | OUT0_P, OUT0_N        | Universal | Differential/LVC MOS output pair 0. Programmable driver with differential or 2 $\times$ 1.8-V LVC MOS outputs.                                                                                                                                                                                                                                                                                                                                                                 |

| 17, 16                   | OUT1_P, OUT1_N        | Universal | Differential/LVC MOS output pair 1. Programmable driver with differential or 2 $\times$ 1.8-V LVC MOS outputs.                                                                                                                                                                                                                                                                                                                                                                 |

| 20, 21                   | OUT2_P, OUT2_N        | Universal | Differential/LVC MOS output pair 2. Programmable driver with differential or 2 $\times$ 1.8-V LVC MOS outputs.                                                                                                                                                                                                                                                                                                                                                                 |

| 23, 22                   | OUT3_P, OUT3_N        | Universal | Differential/LVC MOS output pair 3. Programmable driver with differential or 2 $\times$ 1.8-V LVC MOS outputs.                                                                                                                                                                                                                                                                                                                                                                 |

| 39, 38                   | OUT4_P, OUT4_N        | Universal | Differential/LVC MOS output pair 4. Programmable driver with differential or 2 $\times$ 1.8-V LVC MOS outputs.                                                                                                                                                                                                                                                                                                                                                                 |

| 42, 41                   | OUT5_P, OUT5_N        | Universal | Differential/LVC MOS output pair 5. Programmable driver with differential or 2 $\times$ 1.8-V LVC MOS outputs.                                                                                                                                                                                                                                                                                                                                                                 |

| 45, 44                   | OUT6_P, OUT6_N        | Universal | Differential/LVC MOS output pair 6. Programmable driver with differential or 2 $\times$ 1.8-V LVC MOS outputs.                                                                                                                                                                                                                                                                                                                                                                 |

| 48, 47                   | OUT7_P, OUT7_N        | Universal | Differential/LVC MOS output pair 7. Programmable driver with differential or 2 $\times$ 1.8-V LVC MOS outputs.                                                                                                                                                                                                                                                                                                                                                                 |

### Pin Functions (continued)

| NO.                                               | NAME    | TYPE      | DESCRIPTION                                                                                                                                                                                |

|---------------------------------------------------|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>DIGITAL CONTROL / INTERFACES<sup>(1)</sup></b> |         |           |                                                                                                                                                                                            |

| 1                                                 | STATUS0 | Universal | Status output 0 (open drain, requires external pullup) or 3.3-V LVC MOS output from synth (push-pull). Status signal selection and output polarity are programmable.                       |

| 2                                                 | STATUS1 | Universal | Status output 1 (open drain, requires external pullup) or 3.3-V LVC MOS output from synth (push-pull). Status signal selection and output polarity are programmable.                       |

| 12                                                | GPIO0   | LVC MOS   | Multifunction inputs (2-state).                                                                                                                                                            |

| 13                                                | PDN     | LVC MOS   | Device power-down (active low). Weak pullup resistor.                                                                                                                                      |

| 24                                                | GPIO1   | LVC MOS   | Multifunction input (3-state or 2-state).                                                                                                                                                  |

| 25                                                | SDA     | LVC MOS   | I <sup>2</sup> C serial data (bidirectional, open drain). Requires an external pullup resistor to V <sub>DD</sub> _DIG. I <sup>2</sup> C slave address is initialized from on-chip EEPROM. |

| 26                                                | SCL     | LVC MOS   | I <sup>2</sup> C serial clock (bidirectional, open drain). Requires an external pullup resistor to V <sub>DD</sub> _DIG.                                                                   |

| 29                                                | NC      | N/A       | No connect.                                                                                                                                                                                |

| 30                                                | GPIO2   | LVC MOS   | Multifunction input (3-state or 2-state).                                                                                                                                                  |

| 31                                                | GPIO3   | LVC MOS   | Multifunction input (3-state or 2-state).                                                                                                                                                  |

| 32                                                | GPIO4   | LVC MOS   | Multifunction input (2-state).                                                                                                                                                             |

| 33                                                | GPIO5   | Universal | Multifunction input (2-state) or analog input for frequency margin.                                                                                                                        |

(1) Refer to [Device Configuration Control](#) for details on the digital control/interfaces.

## 8 Specifications

### 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                                                                                                                               | MIN  | MAX                   | UNIT |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|------|

| Supply voltage for input, synthesizer, control, and output blocks, V <sub>DD</sub> _IN, V <sub>DD</sub> _PLL, V <sub>DD</sub> _LDO, V <sub>DD</sub> _DIG, V <sub>DDO</sub> _x | -0.3 | 3.6                   | V    |

| Input voltage, clock and logic inputs, V <sub>IN</sub>                                                                                                                        | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| Output voltage for clock and logic outputs, V <sub>OUT</sub>                                                                                                                  | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| Junction temperature, T <sub>J</sub>                                                                                                                                          |      | 150                   | °C   |

| Storage temperature, T <sub>stg</sub>                                                                                                                                         | -65  | 150                   | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

### 8.2 ESD Ratings

|                    |                         | VALUE                                                                          | UNIT  |   |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|---|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V |

|                    |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> |       |   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2000 V may actually have higher performance.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±500 V may actually have higher performance.

## 8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                                                     | MIN   | NOM | MAX   | UNIT |

|-------------------------------------------------------------------------------------|-------|-----|-------|------|

| Supply voltage for input, analog, control blocks, VDD_IN, VDD_PLL, VDD_LDO, VDD_DIG | 3.135 | 3.3 | 3.465 | V    |

| Supply voltage for output drivers (Differential, LVCMOS), VDDO_x <sup>(1)</sup>     | 1.7   | 1.8 | 3.465 | V    |

|                                                                                     | 1.7   | 2.5 | 3.465 |      |

|                                                                                     | 1.7   | 3.3 | 3.465 |      |

| Ambient temperature, T <sub>A</sub>                                                 | -40   | 25  | 85    | °C   |

| Junction temperature, T <sub>J</sub>                                                |       |     | 125   | °C   |

| Maximum VDD power-up ramp, dVDD/dt                                                  | 0.1   |     | 100   | ms   |

| EEPROM number of writes, WR                                                         |       |     | 100   |      |

(1) The 3 different NOM values are the 3 typical test voltages throughout the data sheet.

## 8.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> | LMK03318 <sup>(2) (3) (4)</sup>              |                   |                   | UNIT  |      |

|-------------------------------|----------------------------------------------|-------------------|-------------------|-------|------|

|                               | RHA (WQFN)                                   |                   |                   |       |      |

|                               | 48 PINS                                      |                   |                   |       |      |

|                               | Airflow (LFM) 0                              | Airflow (LFM) 200 | Airflow (LFM) 400 |       |      |

| R <sub>θJA</sub>              | Junction-to-ambient thermal resistance       | 26.47             | 16.4              | 14.62 | °C/W |

| R <sub>θJC(top)</sub>         | Junction-to-case (top) thermal resistance    | 16.57             | n/a               | n/a   | °C/W |

| R <sub>θJB</sub>              | Junction-to-board thermal resistance         | 6.84              | n/a               | n/a   | °C/W |

| Ψ <sub>JT</sub>               | Junction-to-top characterization parameter   | 0.23              | 0.31              | 0.47  | °C/W |

| Ψ <sub>JB</sub>               | Junction-to-board characterization parameter | 4.02              | 3.86              | 3.84  | °C/W |

| R <sub>θJC(bot)</sub>         | Junction-to-case (bottom) thermal resistance | 1.06              | n/a               | n/a   | °C/W |

- (1) For more information about traditional and new thermal metrics, see [Semiconductor and IC Package Thermal Metrics](#).

- (2) The package thermal resistance is calculated on a 4-layer JEDEC board.

- (3) Package DAP connected to PCB GND plane with 16 thermal vias (0.3 mm diameter).

- (4) Ψ<sub>JB</sub> (junction to board) is used when the main heat flow is from the junction to the GND pad. Refer to the [Layout](#) section for more information on ensuring good system reliability and quality.

## 8.5 Thermal Information

| THERMAL METRIC <sup>(1)</sup> | CONDITION                                    | LMK03318                                                         | UNIT |      |

|-------------------------------|----------------------------------------------|------------------------------------------------------------------|------|------|

|                               |                                              | RHA (WQFN)                                                       |      |      |

|                               |                                              | 48 PINS                                                          |      |      |

| R <sub>θJA</sub>              | Junction-to-ambient thermal resistance       | 10-layer 200 mm × 250 mm board, 36 thermal vias, Airflow = 0 LFM | 10   | °C/W |

| Ψ <sub>JB</sub>               | Junction-to-board characterization parameter | 10-layer 200 mm × 250 mm board, 36 thermal vias, Airflow = 0 LFM | 2.8  | °C/W |

- (1) For more information about traditional and new thermal metrics, see [Semiconductor and IC Package Thermal Metrics](#) application report.

## 8.6 Electrical Characteristics - Power Supply

VDD\_IN, VDD\_PLL, VDD\_LDO, VDD\_DIG = 3.3 V  $\pm$  5%, VDDO\_xx = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5%, T<sub>A</sub> = -40°C to +85°C<sup>(1)(2)</sup>

| PARAMETER       | TEST CONDITIONS                                                            | MIN                                         | TYP | MAX | UNIT |

|-----------------|----------------------------------------------------------------------------|---------------------------------------------|-----|-----|------|

| IDD             | Primary input (differential or single-ended) - active                      |                                             | 10  |     | mA   |

|                 | Secondary input (differential or single-ended) - active                    |                                             | 10  |     |      |

|                 | Secondary input (XO) - active                                              |                                             | 11  |     |      |

|                 | PLL doubler - active                                                       |                                             | 4   |     |      |

|                 | PLL block – active                                                         |                                             | 110 |     |      |

|                 | Control block                                                              |                                             | 53  |     |      |

| IDDO            | Output channel (MUX and Divider only) – active                             |                                             | 46  |     | mA   |

|                 | AC-LVDS driver (one pair)<br>AC-coupled to 100 $\Omega$ differential       |                                             | 10  |     |      |

|                 | AC-LVPECL driver (one pair), AC-coupled to 100 $\Omega$ differential       |                                             | 18  |     |      |

|                 | AC-CML driver (one pair), AC-coupled to 100 $\Omega$ differential          |                                             | 16  |     |      |

|                 | HCSL driver (one pair)<br>50 $\Omega$ to GND                               |                                             | 25  |     |      |

|                 | 1.8-V LVCMOS driver (two outputs), 100 MHz, 5 pF load <sup>(2)</sup>       |                                             | 10  |     |      |

|                 | 3.3-V LVCMOS driver on STATUS0, STATUS1, 100 MHz, 5 pF load <sup>(2)</sup> |                                             | 21  |     |      |

| IDD_IN          | Current consumption, per supply pin                                        | Inputs:                                     | 48  | 65  | mA   |

| IDD_PLL         |                                                                            | - PRI input enabled, set to LVDS mode       | 128 | 158 | mA   |

| IDD_LDO         |                                                                            | - SEC input enabled, set to crystal mode    | 15  | 30  | mA   |

| IDD_DIG         |                                                                            | - Input MUX set to auto select              | 19  | 38  | mA   |

| IDDO_01         |                                                                            | - Reference clock is 25 MHz                 | 85  | 105 | mA   |

| IDDO_23         |                                                                            | - R dividers set to 1                       | 85  | 105 | mA   |

| IDDO_4          |                                                                            | PLL:                                        | 58  | 75  | mA   |

| IDDO_5          |                                                                            | - M divider = 1                             | 58  | 75  | mA   |

| IDDO_6          |                                                                            | - Doubler enabled                           | 58  | 75  | mA   |

| IDDO_7          |                                                                            | - I <sub>CP</sub> = 6.4 mA                  | 58  | 75  | mA   |

| Power Supplies: |                                                                            | - Loop bandwidth = 400 kHz                  |     |     |      |

|                 |                                                                            | - VCO Frequency = 5 GHz                     |     |     |      |

|                 |                                                                            | - Feedback divider = 100                    |     |     |      |

|                 |                                                                            | - Post divider = 8                          |     |     |      |

|                 |                                                                            | Outputs:                                    |     |     |      |

|                 |                                                                            | - OUT[0-7] = 156.25 MHz LVPECL              |     |     |      |

|                 |                                                                            | - STATUS1: Loss of lock PLL                 |     |     |      |

|                 |                                                                            | - STATUS0: Loss of secondary reference      |     |     |      |

|                 |                                                                            | Power Supplies:                             |     |     |      |

|                 |                                                                            | - VDD_IN, VDD_PLL, VDD_LDO, VDD_DIG = 3.3 V |     |     |      |

|                 |                                                                            | - VDDO_xx = 3.3 V                           |     |     |      |

| IDD-PD          | Total device, LMK03318                                                     | Power down (PDN = 0)                        | 30  | 50  | mA   |

(1) Refer to [Parameter Measurement Information](#) for relevant test conditions.

(2) P<sub>TOTAL</sub> = P<sub>DC</sub> + P<sub>AC</sub>, where: P<sub>DC</sub> = 3.4 mA typical. P<sub>AC</sub> = C  $\times$  V<sup>2</sup>  $\times$  f<sub>OUT</sub>.

## 8.7 Pullable Crystal Characteristics (SECREF\_P, SECREF\_N)

VDD\_IN, VDD\_PLL, VDD\_LDO, VDD\_DIG = 3.3 V  $\pm$  5%, VDDO\_x = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5%, T<sub>A</sub> = -40°C to +85°C <sup>(1)(2)(3)(4)</sup>

| PARAMETER                     | TEST CONDITIONS                                                          | MIN                                                                                        | TYP      | MAX | UNIT     |

|-------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------|-----|----------|

| f <sub>XTAL</sub>             | Crystal frequency                                                        | Fundamental Mode                                                                           | 10       | 52  | MHz      |

| ESR                           | Equivalent series resistance                                             | f <sub>XTAL</sub> = 10 MHz to 16 MHz                                                       |          | 60  | $\Omega$ |

|                               |                                                                          | f <sub>XTAL</sub> = 16 MHz to 30 MHz                                                       |          | 50  |          |

|                               |                                                                          | f <sub>XTAL</sub> = 30 MHz to 52 MHz                                                       |          | 30  |          |

| C <sub>L</sub>                | Load capacitance                                                         | Recommended crystal specifications                                                         | 9        |     | pF       |

| C <sub>0</sub>                | Shunt capacitance                                                        |                                                                                            | 2.1      |     | pF       |

| C <sub>0/C<sub>1</sub></sub>  | Shunt capacitance to motional capacitance ratio                          |                                                                                            | 220      | 250 |          |

| P <sub>XTAL</sub>             | Crystal maximum drive level                                              |                                                                                            | 300      |     | $\mu$ W  |

| C <sub>XO</sub>               | On-Chip XO input capacitance at SECREF_P and SECREF_N                    | Single-ended, each pin referenced to GND                                                   | 14       | 24  | pF       |

| Trim                          | Trim sensitivity                                                         | C <sub>L</sub> = 9 pF, f <sub>XTAL</sub> = 50 MHz                                          | 25       |     | ppm/pF   |

|                               |                                                                          | C <sub>L</sub> = 9 pF, f <sub>XTAL</sub> = 25 MHz                                          | 35       |     |          |

| C <sub>on-chip-5p-load</sub>  | On-chip tunable capacitor variation over VT across crystal load of 5 pF  | Frequency accuracy of crystal over temperature, aging and initial accuracy < $\pm$ 25 ppm. |          | 450 | fF       |

| C <sub>on-chip-12p-load</sub> | On-chip tunable capacitor variation over VT across crystal load of 12 pF | Frequency accuracy of crystal over temperature, aging and initial accuracy < $\pm$ 25 ppm. |          | 1.5 | pF       |

| f <sub>PR</sub>               | Pulling range                                                            | Crystal C <sub>0/C<sub>1</sub></sub> < 250                                                 | $\pm$ 50 |     | ppm      |

- (1) Parameter is specified by characterization and is not tested in production.

- (2) The crystal pullability ratio is considered in the case where the XO frequency margining option is enabled. The actual pull range depends on the crystal pullability, as well as on-chip capacitance (C<sub>on-chip</sub>), device crystal oscillator input capacitance (C<sub>XO</sub>), PCB stray capacitance (C<sub>PCB</sub>), and any installed on-board tuning capacitance (C<sub>TUNE</sub>). Trim sensitivity or pullability (ppm/pF), TS = C<sub>1</sub>  $\times$  1e6 / [2  $\times$  (C<sub>0</sub> + C<sub>L</sub>)<sup>2</sup>]. If the total external capacitance is less than the crystal C<sub>L</sub>, the crystal oscillates at a higher frequency than the nominal crystal frequency. If the total external capacitance is higher than C<sub>L</sub>, the crystal oscillates at a lower frequency than nominal.

- (3) Using a crystal with higher ESR can degrade output phase noise and may impact crystal start-up.

- (4) Verified with crystals specified for a load capacitance of C<sub>L</sub> = 9 pF. PCB stray capacitance was measured to be 1 pF. Crystals tested: 19.2-MHz TXC (Part Number: 7M19272001), 19.44 MHz TXC (Part Number: 7M19472001), 25 MHz TXC (Part Number: 7M25072001), 38.88-MHz TXC (Part Number: 7M38872001), 49.152-MHz TXC (Part Number: 7M49172001), 50-MHz TXC (Part Number: 7M50072001).

## 8.8 Non-Pullable Crystal Characteristics (SECREF\_P, SECREF\_N)

VDD\_IN, VDD\_PLL, VDD\_LDO, VDD\_DIG = 3.3 V  $\pm$  5%, VDDO\_x = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5%, T<sub>A</sub> = -40°C to +85°C <sup>(1)(2)(3)</sup>

| PARAMETER                     | TEST CONDITIONS                                                          | MIN                                                                                        | TYP | MAX | UNIT     |

|-------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----|-----|----------|

| f <sub>XTAL</sub>             | Crystal frequency                                                        | Fundamental mode                                                                           | 10  | 52  | MHz      |

| ESR                           | Equivalent series resistance                                             | f <sub>XTAL</sub> = 10 MHz to 16 MHz                                                       | 60  |     |          |

|                               |                                                                          | f <sub>XTAL</sub> = 16 MHz to 30 MHz                                                       | 50  |     | $\Omega$ |

|                               |                                                                          | f <sub>XTAL</sub> = 30 MHz to 52 MHz                                                       | 30  |     |          |

| P <sub>XTAL</sub>             | Crystal maximum drive level                                              |                                                                                            |     | 300 | $\mu$ W  |

| C <sub>XO</sub>               | On-Chip XO input capacitance at X <sub>i</sub> and X <sub>o</sub>        | Single-ended, each pin referenced to GND                                                   | 14  | 24  | pF       |

| C <sub>on-chip-5p-load</sub>  | On-chip tunable capacitor variation over VT across crystal load of 5 pF  | Frequency accuracy of crystal over temperature, aging and initial accuracy < $\pm$ 25 ppm. |     | 450 | fF       |

| C <sub>on-chip-12p-load</sub> | On-chip tunable capacitor variation over VT across crystal load of 12 pF | Frequency accuracy of crystal over temperature, aging and initial accuracy < $\pm$ 25 ppm. |     | 1.5 | pF       |

(1) Parameter is specified by characterization and is not tested in production.

(2) Using a crystal with higher ESR can degrade XO phase noise and may impact crystal start-up.

(3) Verified with crystals specified for a load capacitance of C<sub>L</sub> = 9 pF. PCB stray capacitance was measured to be 1 pF. Crystal tested: 25-MHz TXC (part number: 7M25072001).

## 8.9 Clock Input Characteristics (PRIREF\_P/PRIREF\_N, SECREF\_P/SECREF\_N)

VDD\_IN, VDD\_PLL, VDD\_LDO, VDD\_DIG = 3.3 V  $\pm$  5%, VDDO\_x = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5%, T<sub>A</sub> = -40°C to 85°C <sup>(1)</sup>

| PARAMETER                      | TEST CONDITIONS                             | MIN                                                                                             | TYP  | MAX    | UNIT    |

|--------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------|------|--------|---------|

| f <sub>CLK</sub>               | Input frequency range                       |                                                                                                 | 1    | 300    | MHz     |

| V <sub>IH</sub> <sup>(2)</sup> | LVCMOS input high voltage                   | PRI_REF                                                                                         | 1.4  | VDD_IN | V       |

| V <sub>IH</sub> <sup>(2)</sup> | LVCMOS input high voltage                   | SEC_REF                                                                                         | 1.4  | 2.6    | V       |

| V <sub>IL</sub> <sup>(2)</sup> | LVCMOS input low voltage                    |                                                                                                 | 0    | 0.5    | V       |

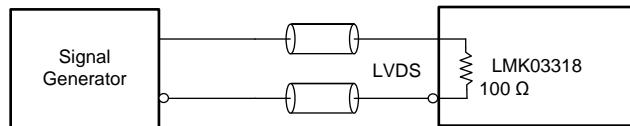

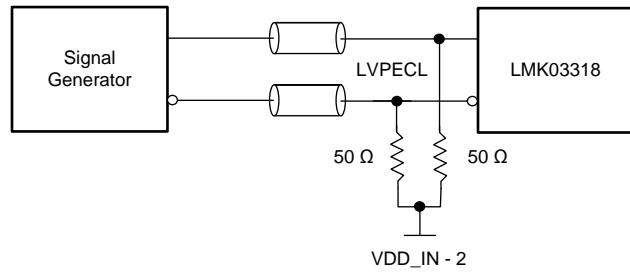

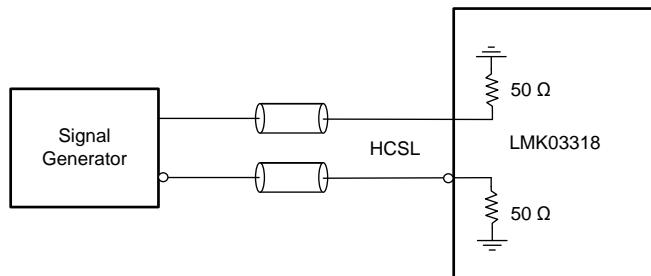

| V <sub>ID,DIFF,PP</sub>        | Input voltage swing, differential peak-peak | Differential input (where V <sub>CLK</sub> – V <sub>nCLK</sub> =  V <sub>ID</sub>   $\times$ 2) | 0.2  | 2      | V       |

| V <sub>ICM</sub>               | Input common-mode voltage                   | Differential input                                                                              | 0.1  | 2      | V       |

| dV/dt <sup>(3)</sup>           | Input edge slew rate (20% to 80%)           | Differential input, peak-peak                                                                   | 0.5  |        | V/ns    |

|                                |                                             | Single-ended input, non-driven input tied to GND                                                | 0.5  |        | V/ns    |

| IDC <sup>(3)</sup>             | Input clock duty cycle                      |                                                                                                 | 40%  | 60%    |         |

| I <sub>IN</sub>                | Input leakage current                       |                                                                                                 | -100 | 100    | $\mu$ A |

| C <sub>IN</sub>                | Input capacitance                           | Single-ended, each pin                                                                          |      | 2      | pF      |

(1) Refer to [Parameter Measurement Information](#) for relevant test conditions.

(2) Slew-rate-detect circuitry must be used when V<sub>IH</sub> < 1.7 V and V<sub>IL</sub> > 0.2 V. V<sub>IH</sub>/V<sub>IL</sub> detect circuitry must be used when V<sub>IH</sub> < 1.5 V and V<sub>IL</sub> > 0.4 V. Refer to [REFDETCTL Register; R25](#) for relevant register information.

(3) Ensured by characterization.

## 8.10 VCO Characteristics

VDD\_IN, VDD\_PLL, VDD\_LDO, VDD\_DIG = 3.3 V  $\pm$  5%, VDDO\_x = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5%, T<sub>A</sub> = -40°C to +85°C

| PARAMETER        | TEST CONDITIONS | MIN | TYP | MAX | UNIT  |

|------------------|-----------------|-----|-----|-----|-------|

| f <sub>VCO</sub> | Frequency range |     | 4.8 | 5.4 | GHz   |

| K <sub>VCO</sub> | VCO Gain        |     |     | 55  | MHz/V |

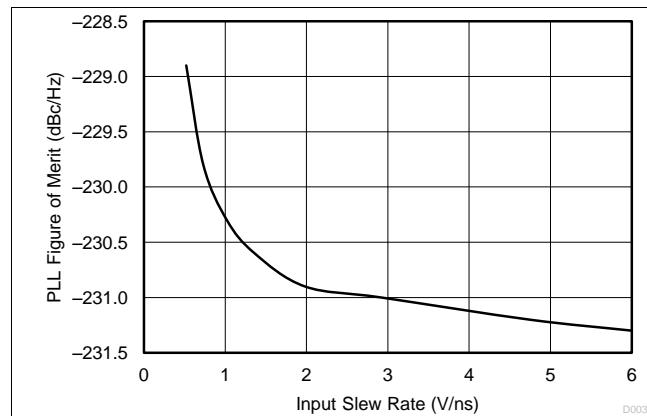

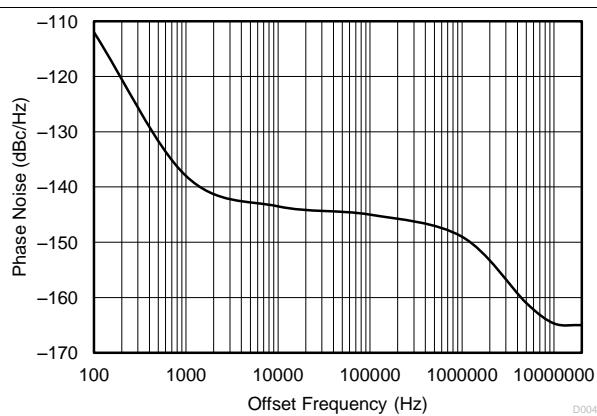

## 8.11 PLL Characteristics

VDD\_IN, VDD\_PLL, VDD\_LDO, VDD\_DIG = 3.3 V  $\pm$  5%, VDDO\_x = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5%, T<sub>A</sub> = -40°C to +85°C

| PARAMETER           | TEST CONDITIONS                                                   | MIN                                             | TYP  | MAX  | UNIT   |

|---------------------|-------------------------------------------------------------------|-------------------------------------------------|------|------|--------|

| f <sub>PD</sub>     | Phase detector frequency                                          | 1                                               | 150  | 150  | MHz    |

| PN1Hz               | PLL figure of merit <sup>(1)</sup>                                |                                                 | -231 |      | dBc/Hz |

| PN10kHz             | PLL 1/f noise at 10 kHz offset normalized to 1 GHz <sup>(2)</sup> | I <sub>CP</sub> = 6.4 mA, 25 MHz phase detector |      | -136 | dBc/Hz |

| I <sub>CP-HIZ</sub> | Charge-pump leakage in Hi-Z Mode                                  |                                                 | 55   |      | nA     |

(1) PLL flat phase noise = PN1 Hz + 20  $\times$  log(N) + 10  $\times$  log(f<sub>PD</sub>), with wide loop bandwidth and away from 1/f noise region.

(2) Phase noise normalized to 1 GHz. PLL 1/f phase noise = PN10 kHz + 20  $\times$  log(f<sub>OUT</sub>/1 GHz) - 10  $\times$  log(offset/10 kHz)

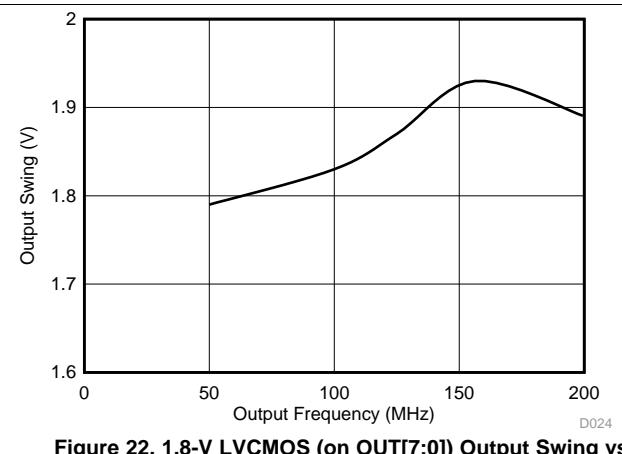

## 8.12 1.8-V LVC MOS Output Characteristics (OUT[7:0])

VDD\_IN, VDD\_PLL, VDD\_LDO, VDD\_DIG = 3.3 V  $\pm$  5%, VDDO\_x = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5%, T<sub>A</sub> = -40°C to +85°C, outputs loaded with 2 pF to GND<sup>(1)</sup>

| PARAMETER                        | TEST CONDITIONS                                         | MIN        | TYP  | MAX  | UNIT     |

|----------------------------------|---------------------------------------------------------|------------|------|------|----------|

| f <sub>OUT</sub>                 | Output frequency                                        | 1          | 200  | 200  | MHz      |

| V <sub>OH</sub> <sup>(2)</sup>   | I <sub>OH</sub> = 1 mA                                  | 1.35       |      |      | V        |

| V <sub>OL</sub>                  | I <sub>OL</sub> = 1 mA                                  |            | 0.35 | 0.35 | V        |

| I <sub>OH</sub>                  |                                                         |            | 21   | 21   | mA       |

| I <sub>OL</sub>                  |                                                         |            | -21  | -21  | mA       |

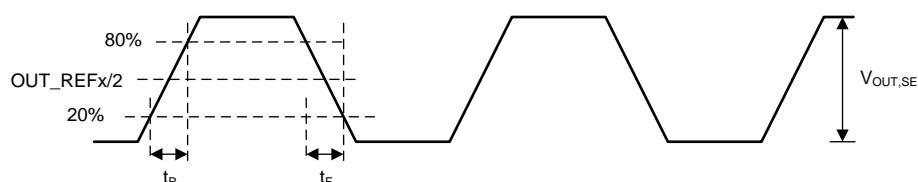

| t <sub>R</sub> /t <sub>F</sub>   | 20% to 80%                                              |            | 250  | 250  | ps       |

| t <sub>SKew</sub> <sup>(3)</sup> | same divide value                                       |            | 100  | 100  | ps       |

| t <sub>SKew</sub> <sup>(3)</sup> | LVC MOS-to-differential; same divide value              |            | 1.5  | 1.5  | ns       |

| t <sub>PROP-CMOS</sub>           | IN-to-OUT propagation delay                             | PLL bypass | 1    | 1    | ns       |

| PN-Floor                         | Output phase noise floor (f <sub>OFFSET</sub> > 10 MHz) | 66.66 MHz  |      | -155 | dBc/Hz   |

| ODC <sup>(3)</sup>               | Output Duty Cycle                                       |            | 45%  | 55%  |          |

| R <sub>OUT</sub>                 | Output Impedance                                        |            | 50   | 50   | $\Omega$ |

(1) Refer to [Parameter Measurement Information](#) for relevant test conditions.

(2) The 1.8-V LVC MOS driver supports rail-to-rail output swing only when powered from VDDO = 1.8 V +/- 5% (recommended VDDO for use with LVC MOS output format). V<sub>OH</sub> level is NOT rail-to-rail for VDDO = 2.5 V or 3.3 V due to the dropout voltage of the output channel's internal LDO regulator.

(3) Ensured by characterization.

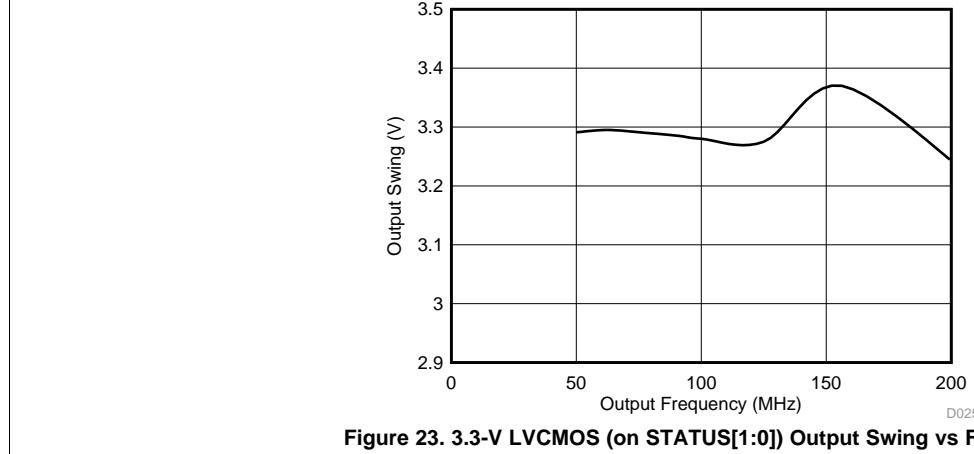

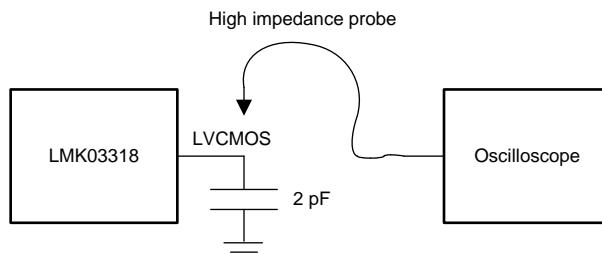

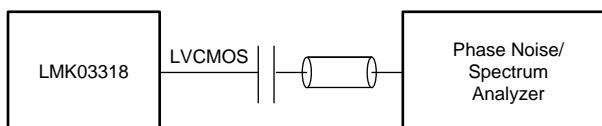

## 8.13 LVC MOS Output Characteristics (STATUS[1:0])

VDD\_IN, VDD\_PLL, VDD\_LDO, VDD\_DIG = 3.3 V  $\pm$  5%, VDD\_O = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5%, T<sub>A</sub> = -40°C to 85°C, outputs loaded with 2 pF to GND<sup>(1)</sup>

| PARAMETER                                     | TEST CONDITIONS                                         | MIN       | TYP  | MAX  | UNIT     |

|-----------------------------------------------|---------------------------------------------------------|-----------|------|------|----------|

| f <sub>OUT</sub>                              | Output frequency                                        | 3.75      | 200  | 200  | MHz      |

| V <sub>OH</sub>                               | I <sub>OH</sub> = 1 mA                                  | 2.5       |      |      | V        |

| V <sub>OL</sub>                               | I <sub>OL</sub> = 1 mA                                  |           | 0.6  | 0.6  | V        |

| I <sub>OH</sub>                               |                                                         |           | 33   | 33   | mA       |

| I <sub>OL</sub>                               |                                                         |           | -33  | -33  | mA       |

| t <sub>R</sub> /t <sub>F</sub> <sup>(2)</sup> | 20% to 80%, R49[3-2], R49[1:0] = 10                     |           | 2.1  | 2.1  | ns       |

|                                               | 20% to 80%, R49[3-2], R49[1-0] = 00                     |           | 0.35 | 0.35 | ns       |

| PN-Floor                                      | Output phase noise floor (f <sub>OFFSET</sub> > 10 MHz) | 66.66 MHz |      | -148 | dBc/Hz   |

| ODC <sup>(2)</sup>                            | Output duty cycle                                       |           | 45%  | 55%  |          |

| R <sub>OUT</sub>                              | Output impedance                                        |           | 50   | 50   | $\Omega$ |

(1) Refer to [Parameter Measurement Information](#) for relevant test conditions.

(2) Ensured by characterization.

## 8.14 Open-Drain Output Characteristics (STATUS[1:0])

VDD\_IN, VDD\_PLL, VDD\_LDO, VDD\_DIG = 3.3 V  $\pm$  5%, VDDO\_x = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5%, T<sub>A</sub> = -40°C to 85°C

| PARAMETER                             | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------------------------|-----------------|-----|-----|-----|------|

| V <sub>OL</sub><br>Output low voltage |                 |     |     | 0.6 | V    |

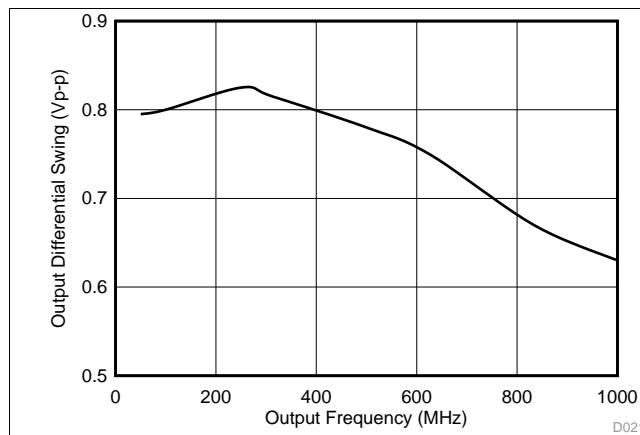

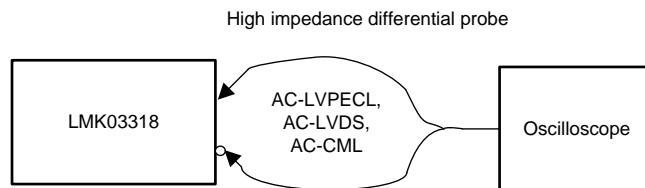

## 8.15 AC-LVPECL Output Characteristics

VDD\_IN, VDD\_PLL, VDD\_LDO, VDD\_DIG = 3.3 V  $\pm$  5%, VDDO\_x = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5%, T<sub>A</sub> = -40°C to 85°C, output pair AC-coupled to 100- $\Omega$  differential load<sup>(1)</sup>

| PARAMETER                                                                 | TEST CONDITIONS                             | MIN | TYP                         | MAX  | UNIT   |

|---------------------------------------------------------------------------|---------------------------------------------|-----|-----------------------------|------|--------|

| f <sub>OUT</sub><br>Output frequency <sup>(2)</sup>                       |                                             | 1   |                             | 1000 | MHz    |

| V <sub>OD</sub><br>Output voltage swing                                   |                                             | 500 | 800                         | 1000 | mV     |

| V <sub>OUT-PP</sub><br>Differential output peak-to-peak swing             |                                             |     | 2 $\times$  V <sub>OD</sub> |      | V      |

| V <sub>OS</sub><br>Output common mode                                     |                                             | 300 |                             | 700  | mV     |

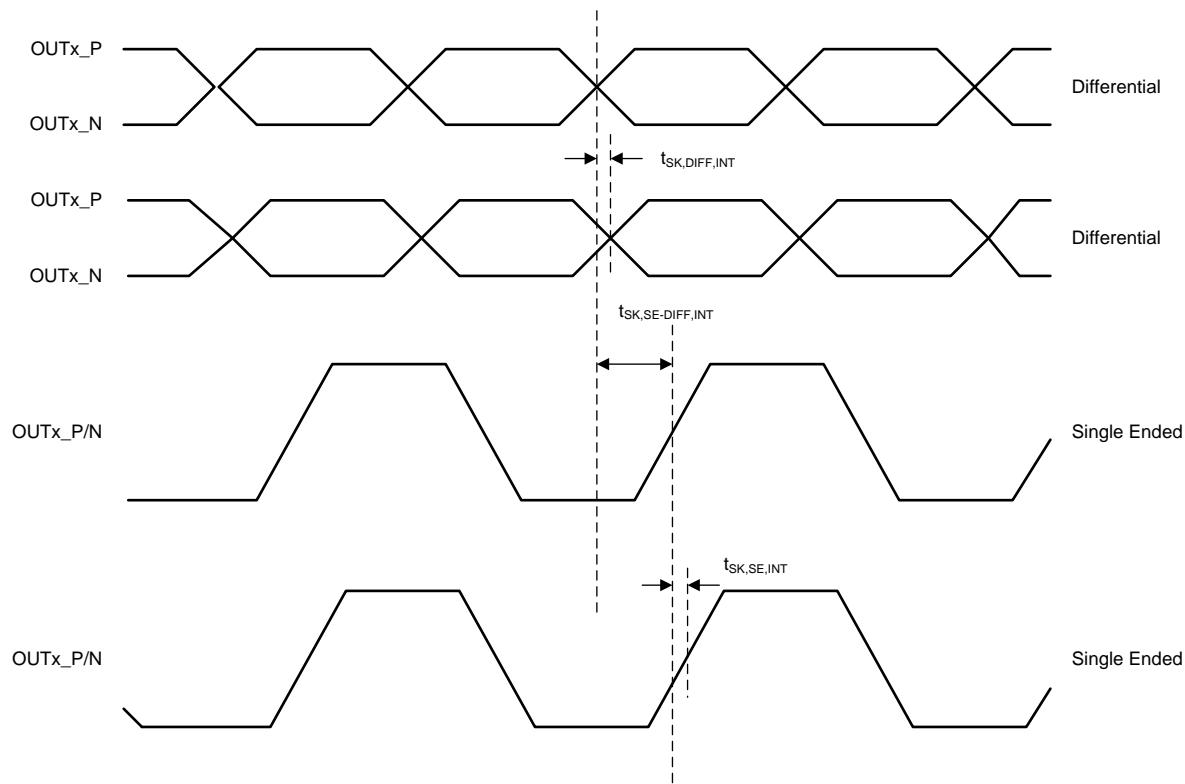

| t <sub>SKew</sub> <sup>(3)</sup><br>Output-to-output skew                 | LVPECL-to-LVPECL; same divide value         |     |                             | 60   | ps     |

| t <sub>PROP-DIFF</sub><br>IN-to-OUT propagation delay                     | PLL bypass                                  |     | 400                         |      | ps     |

| t <sub>R</sub> /t <sub>F</sub> <sup>(3)</sup><br>Output rise or fall time | 20% to 80%, < 300 MHz                       |     | 175                         | 300  | ps     |

|                                                                           | $\pm$ 100 mV around center point, > 300 MHz |     |                             | 200  | ps     |

| PN-Floor<br>(f <sub>OFFSET</sub> > 10 MHz)                                | 156.25 MHz                                  |     |                             | -164 | dBc/Hz |

| ODC <sup>(3)</sup><br>Output duty cycle                                   |                                             | 45% |                             | 55%  |        |

(1) Refer to [Parameter Measurement Information](#) for relevant test conditions.

(2) An output frequency over f<sub>OUT</sub> maximum specification is possible, but output swing may be less than V<sub>OD</sub> minimum specification.

(3) Ensured by characterization.

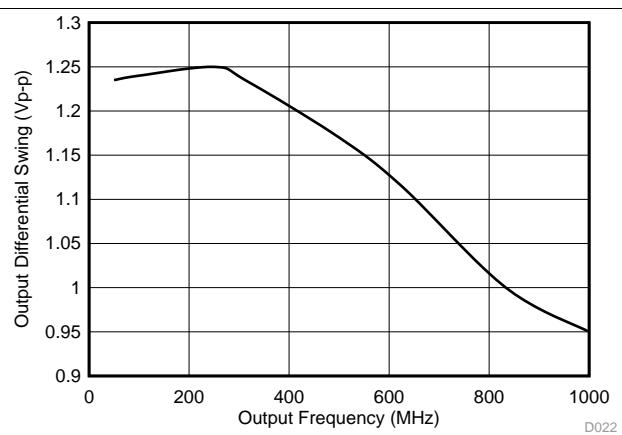

## 8.16 AC-LVDS Output Characteristics

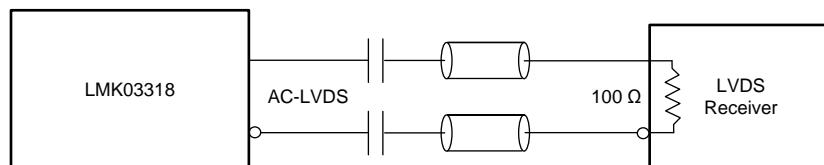

VDD\_IN, VDD\_PLL, VDD\_LDO, VDD\_DIG = 3.3 V  $\pm$  5%, VDDO\_x = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5%, T<sub>A</sub> = -40°C to 85°C, output pair AC-coupled to 100- $\Omega$  differential load<sup>(1)</sup>

| PARAMETER                                                              | TEST CONDITIONS                             | MIN | TYP                         | MAX  | UNIT   |

|------------------------------------------------------------------------|---------------------------------------------|-----|-----------------------------|------|--------|

| f <sub>OUT</sub><br>Output frequency <sup>(2)</sup>                    |                                             | 1   |                             | 800  | MHz    |

| V <sub>OD</sub><br>Output voltage swing                                |                                             | 250 | 400                         | 450  | mV     |

| V <sub>OUT-PP</sub><br>Differential output peak-to-peak swing          |                                             |     | 2 $\times$  V <sub>OD</sub> |      | V      |

| V <sub>OS</sub><br>Output common mode                                  |                                             | 150 |                             | 350  | mV     |

| t <sub>SKew</sub> <sup>(2)</sup><br>Output-to-output skew              | LVDS-to-LVDS; same divide value             |     |                             | 60   | ps     |

| t <sub>PROP-DIFF</sub><br>IN-to-OUT propagation delay                  | PLL bypass                                  |     | 400                         |      | ps     |

| t <sub>R</sub> /t <sub>F</sub> <sup>(3)</sup><br>Output rise/fall time | 20% to 80%, < 300 MHz                       |     | 200                         | 300  | ps     |

|                                                                        | $\pm$ 100 mV around center point, > 300 MHz |     |                             | 200  | ps     |

| PN-Floor<br>(f <sub>OFFSET</sub> > 10 MHz)                             | 156.25 MHz                                  |     |                             | -160 | dBc/Hz |

| ODC <sup>(3)</sup><br>Output duty cycle                                |                                             | 45% |                             | 55%  |        |

(1) Refer to [Parameter Measurement Information](#) for relevant test conditions.

(2) An output frequency over f<sub>OUT</sub> maximum specification is possible, but output swing may be less than V<sub>OD</sub> minimum specification.

(3) Ensured by characterization.

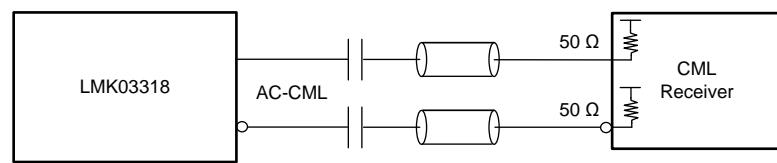

## 8.17 AC-CML Output Characteristics

VDD\_IN, VDD\_PLL, VDD\_LDO, VDD\_DIG = 3.3 V  $\pm$  5%, VDDO\_x = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5%, T<sub>A</sub> = -40°C to +85°C, output pair AC-coupled to 100- $\Omega$  differential load<sup>(1)</sup>

| PARAMETER                                   | TEST CONDITIONS                                         | MIN                                         | TYP                         | MAX  | UNIT   |

|---------------------------------------------|---------------------------------------------------------|---------------------------------------------|-----------------------------|------|--------|

| f <sub>OUT</sub>                            | Output frequency <sup>(2)</sup>                         | 1                                           |                             | 1000 | MHz    |

| V <sub>OD</sub>                             | Output voltage swing                                    | 400                                         | 600                         | 800  | mV     |

| V <sub>SS</sub>                             | Differential output peak-to-peak swing                  |                                             | 2 $\times$  V <sub>OD</sub> |      | V      |

| V <sub>OS</sub>                             | Output common mode                                      | 250                                         |                             | 550  | mV     |

| t <sub>SKew</sub> <sup>(3)</sup>            | CML-to-CML; same divide value                           |                                             |                             | 60   | ps     |

| t <sub>PROP-DIFF</sub>                      | IN-to-OUT propagation delay                             | PLL bypass                                  |                             | 400  | ps     |

| t <sub>R/t<sub>F</sub></sub> <sup>(3)</sup> | Output rise/fall time                                   | 20% to 80%, < 300 MHz                       | 190                         | 300  | ps     |

|                                             |                                                         | $\pm$ 100 mV around center point, > 300 MHz |                             | 200  | ps     |

| PN-Floor                                    | Output phase noise floor (f <sub>OFFSET</sub> > 10 MHz) | 156.25 MHz                                  |                             | -160 | dBc/Hz |

| ODC <sup>(3)</sup>                          | Output duty cycle                                       |                                             | 45%                         | 55%  |        |

(1) Refer to [Parameter Measurement Information](#) for relevant test conditions.

(2) An output frequency over f<sub>OUT</sub> maximum specification is possible, but output swing may be less than V<sub>OD</sub> minimum specification.

(3) Ensured by characterization.

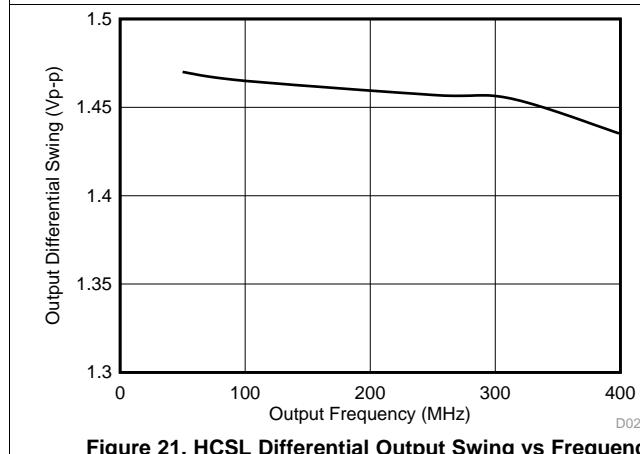

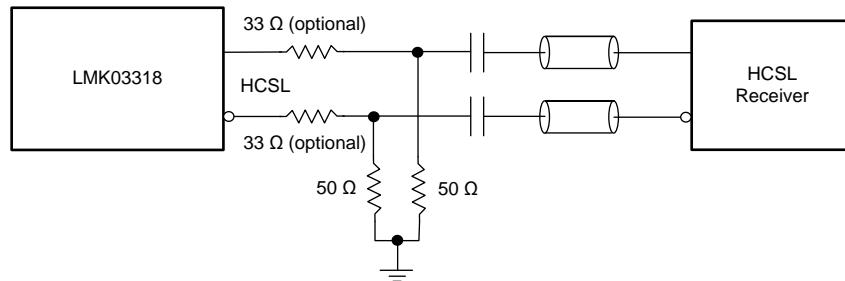

## 8.18 HCSL Output Characteristics

VDD\_IN, VDD\_PLL, VDD\_LDO, VDD\_DIG = 3.3 V  $\pm$  5%, VDDO\_x = 1.8 V  $\pm$  5%, 2.5 V  $\pm$  5%, 3.3 V  $\pm$  5%, T<sub>A</sub> = -40°C to +85°C, outputs with 50  $\Omega$  || 2 pF to GND<sup>(1)</sup>

| PARAMETER                        | TEST CONDITIONS                                         | MIN               | TYP | MAX  | UNIT   |

|----------------------------------|---------------------------------------------------------|-------------------|-----|------|--------|

| f <sub>OUT</sub>                 | Output frequency                                        | 1                 |     | 400  | MHz    |

| V <sub>OH</sub>                  | Output high voltage <sup>(2)</sup>                      | 660               |     | 850  | mV     |

| V <sub>OL</sub>                  | Output low voltage <sup>(2)</sup>                       | -150              |     | 150  | mV     |

| V <sub>CROSS</sub>               | Absolute crossing voltage <sup>(3)</sup>                | 250               |     | 550  | mV     |

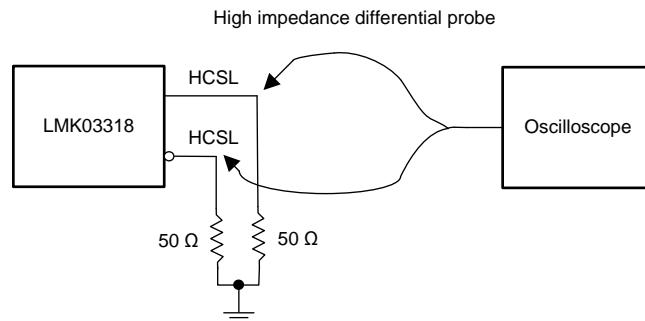

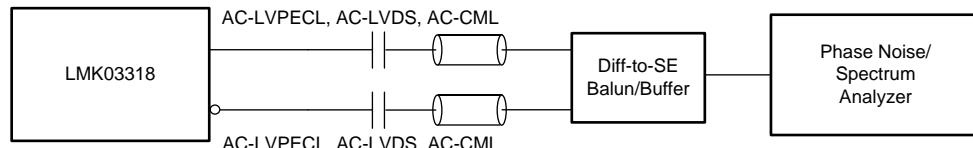

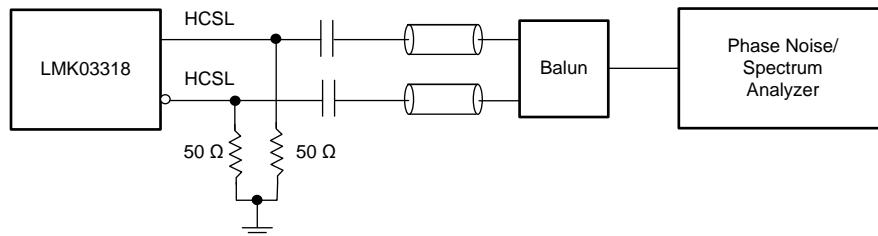

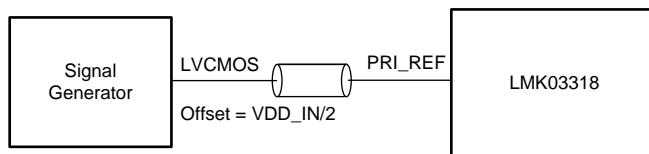

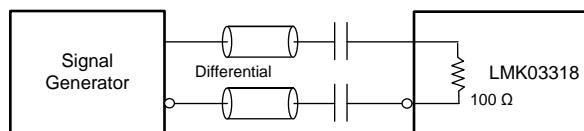

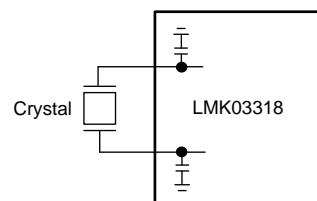

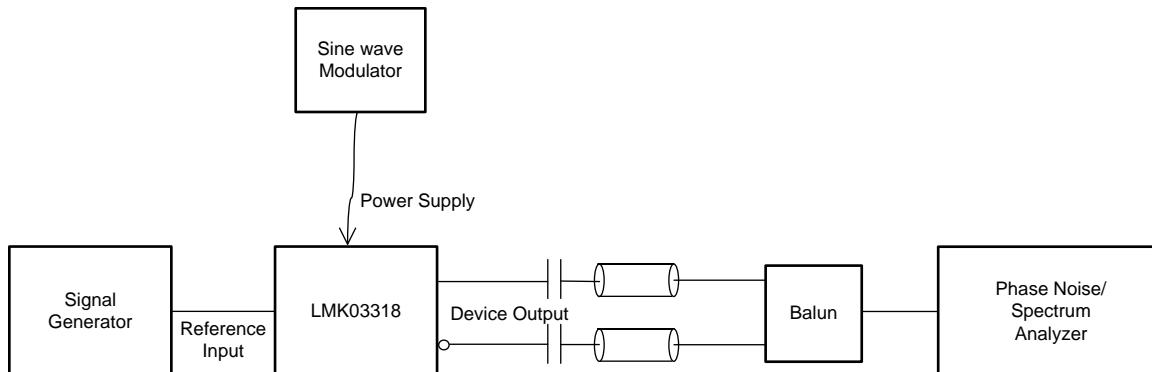

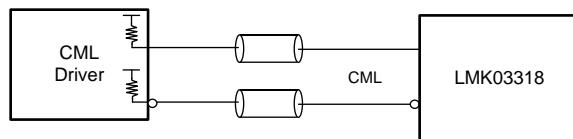

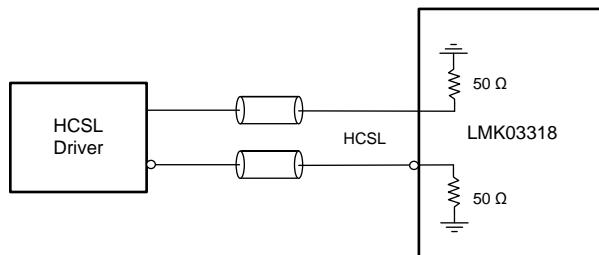

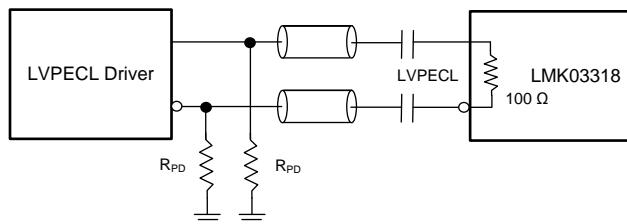

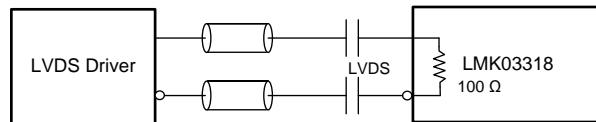

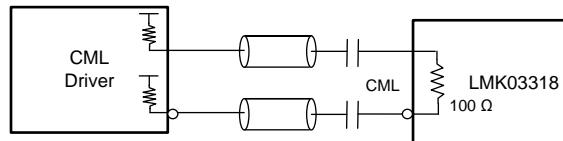

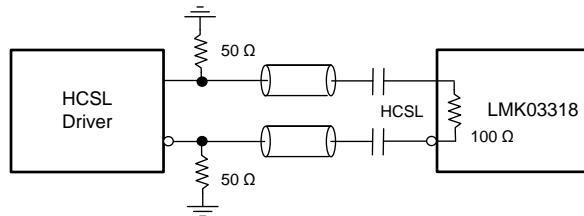

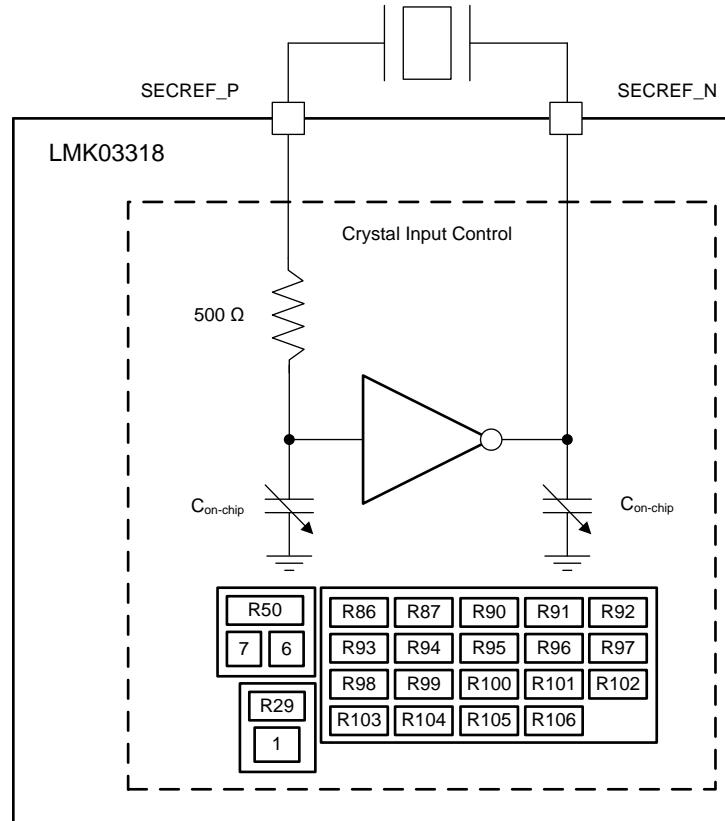

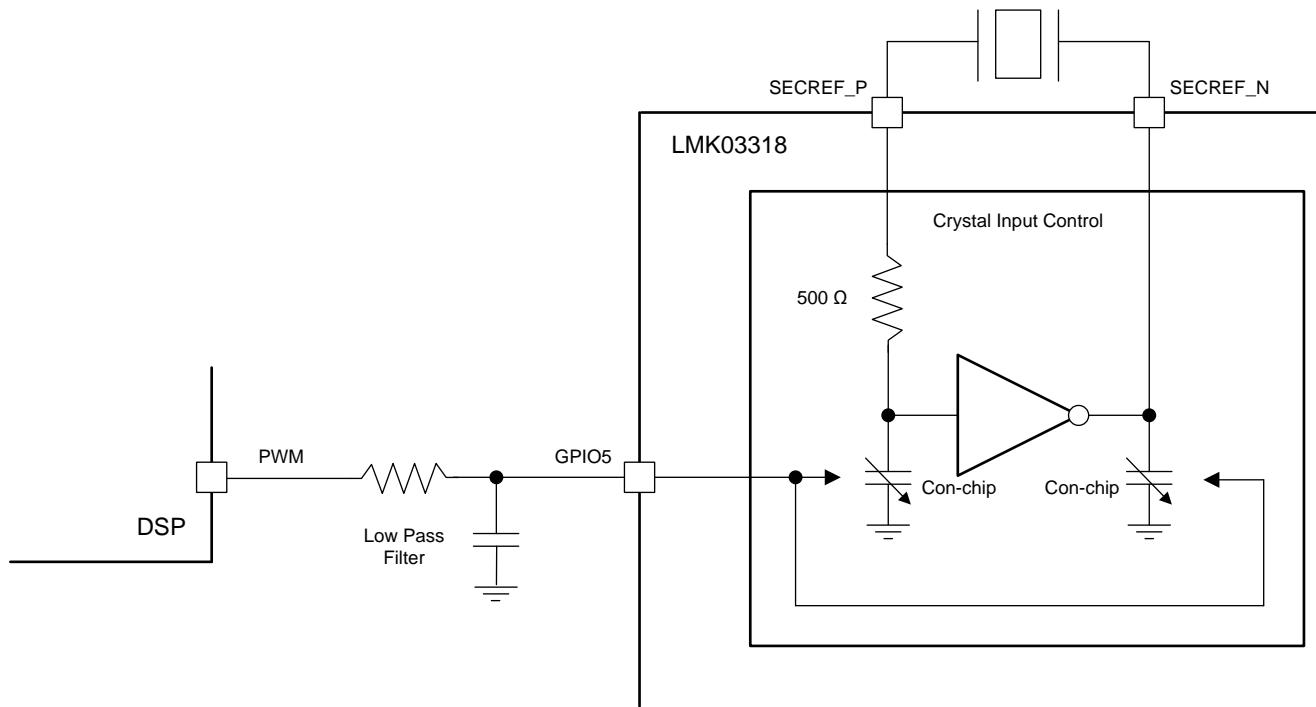

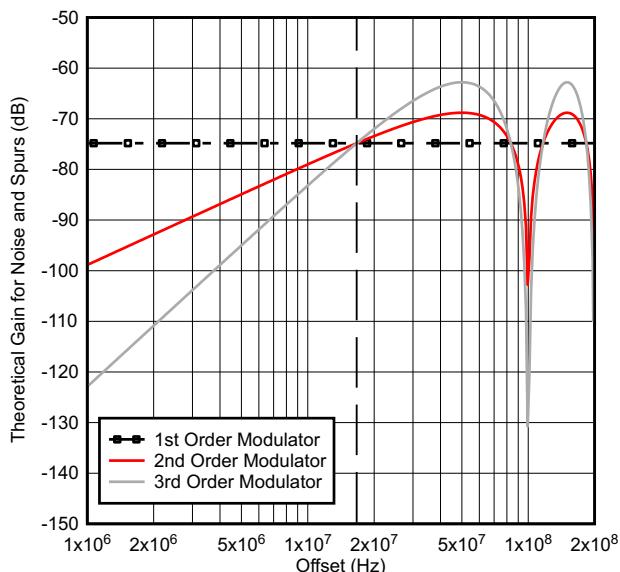

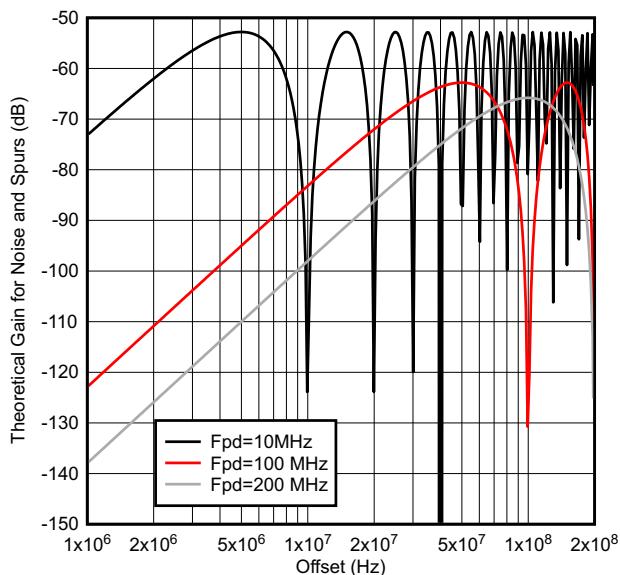

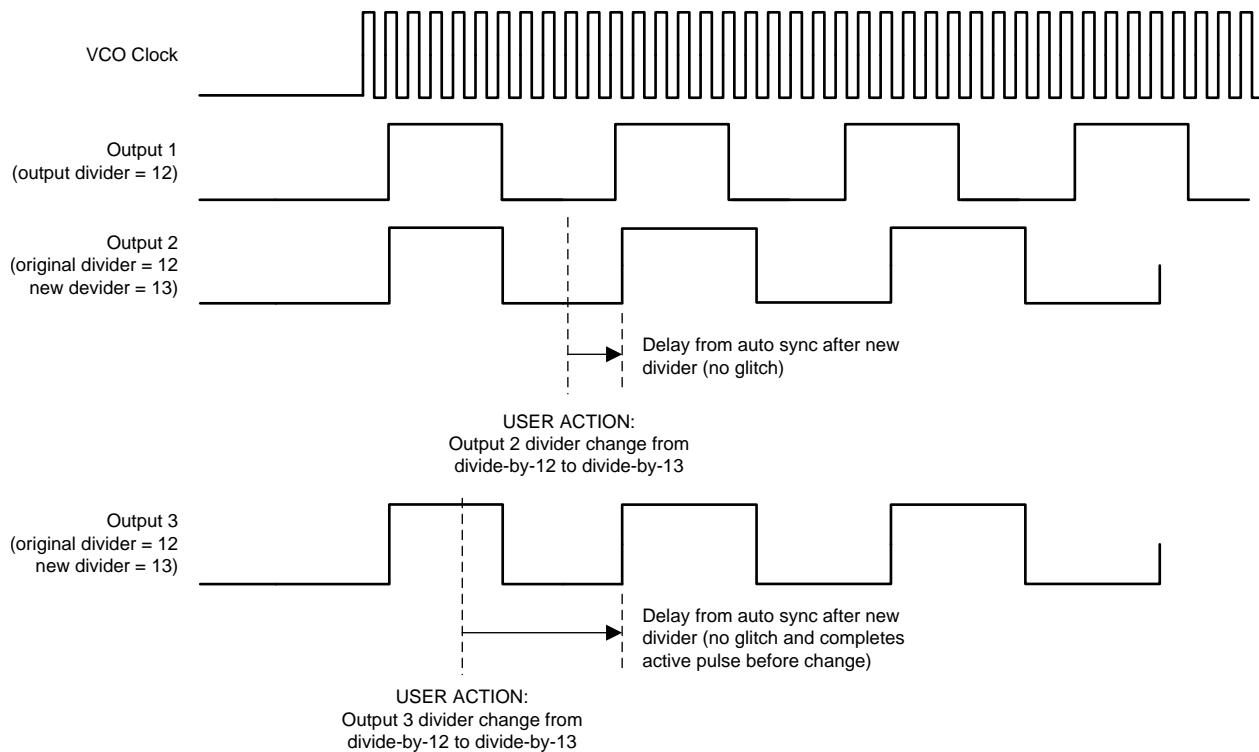

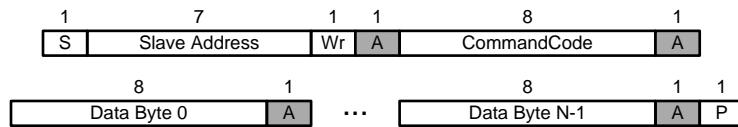

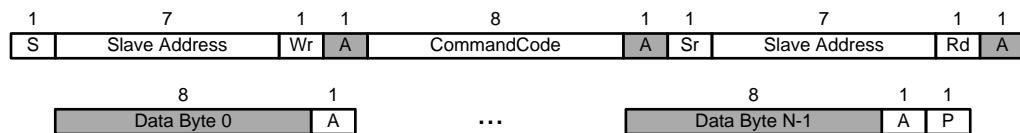

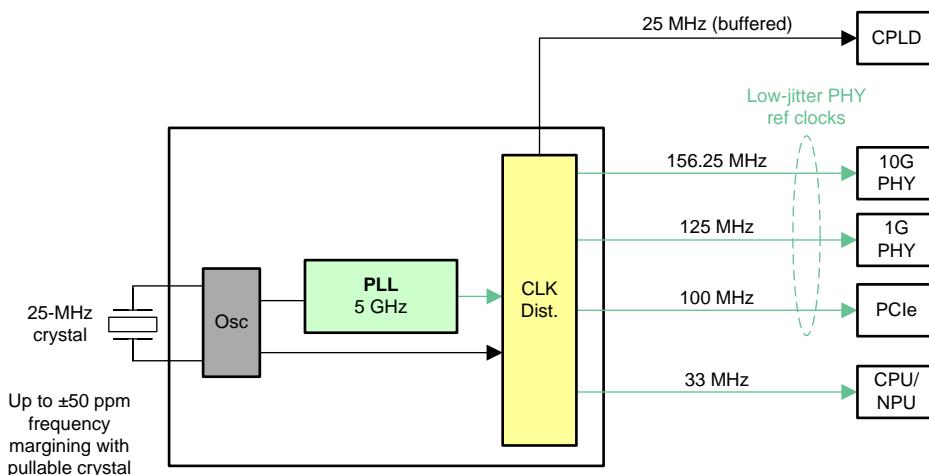

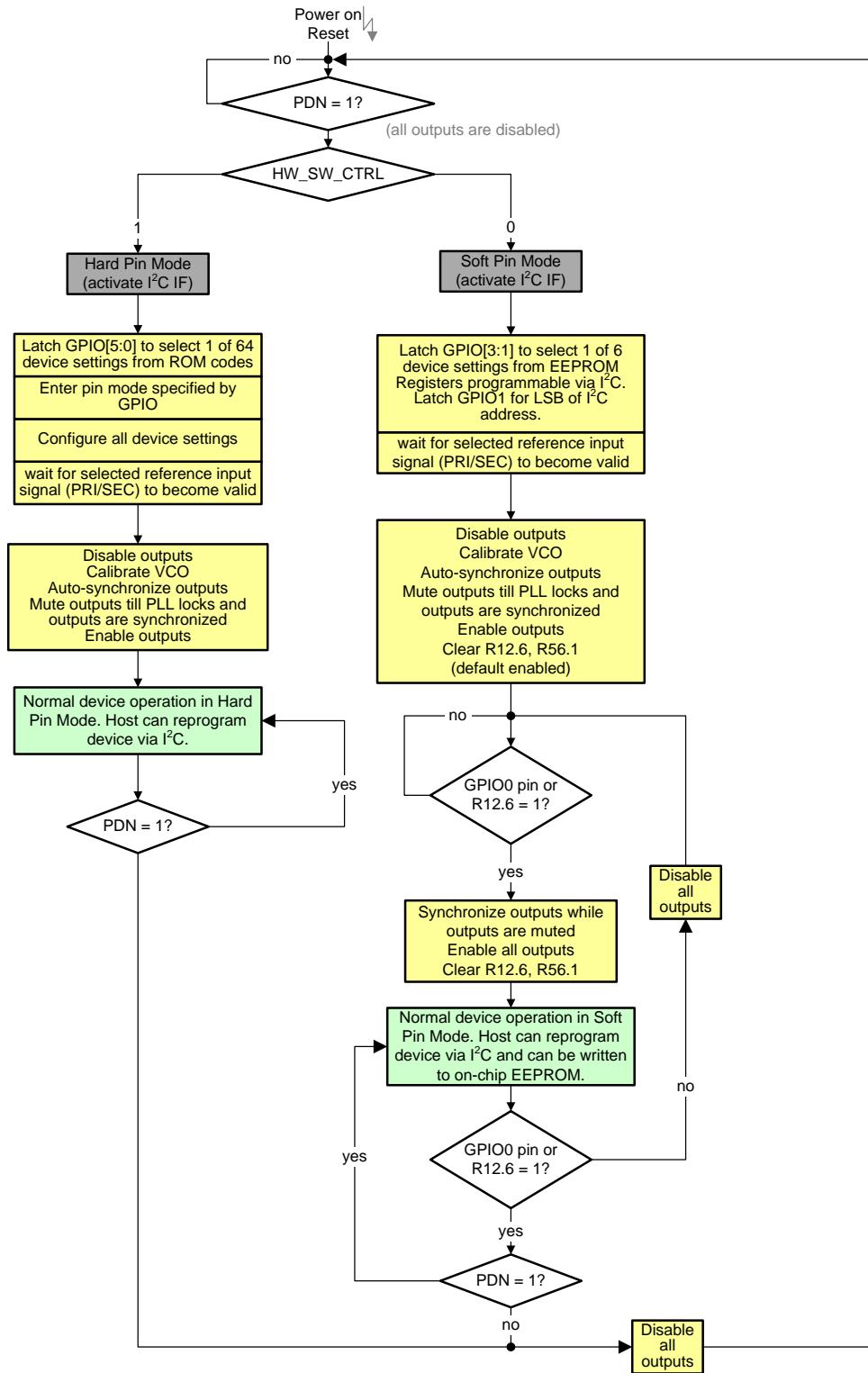

| V <sub>CROSS-DELTA</sub>         | Variation of V <sub>CROSS</sub> <sup>(3)</sup>          | 0                 |     | 140  | mV     |