## Battery management system solution

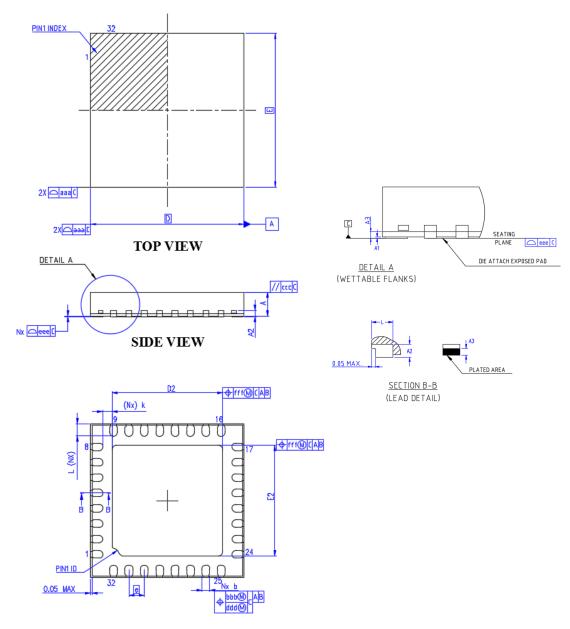

VFQFPN32 (5x5x1.00 mm)

**Features**

- (with VREG LDO active) standby consumption (with VREG LDO active) Integrated 3.3 V VREG LDO for supplying MCU and LEDs

- Measures cell voltage (3 to 5 cells), with over/undervoltage detection and balance undervoltage protection

- 12-bit voltage measurement with maximum error of ±15 mV in the [1.5 4.5] V range, for -40 °C < T<sub>J</sub> < 105 °C

2 μA shipment - DEEP SLEEP mode current and 5 μA standby consumption

- Measures stack voltage, with over/under voltage detection and plausibility check vs. sum of cells

- Measures pack temperature via NTC, with over/undertemperature detection

- Ratiometric temperature measurement with ±0.8% max. gain error in the [0.2 VREG] V range, for -40 °C < T<sub>J</sub> < 105 °C

- Measures battery current, with Coulomb counting, overcurrent (both directions) and short-circuit in discharge protection.

- 16-bit signed current measurement with 0.1% full scale error at room temperature

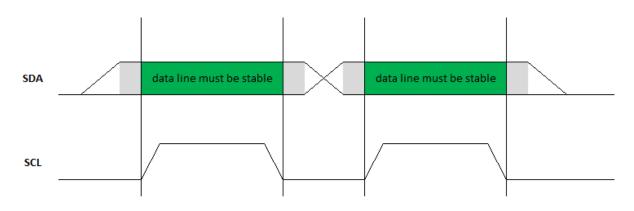

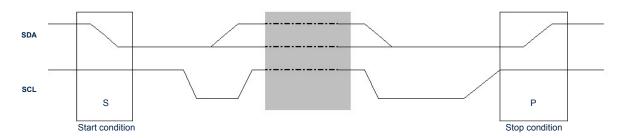

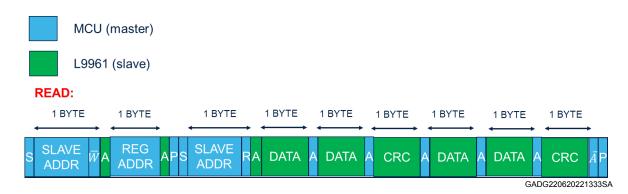

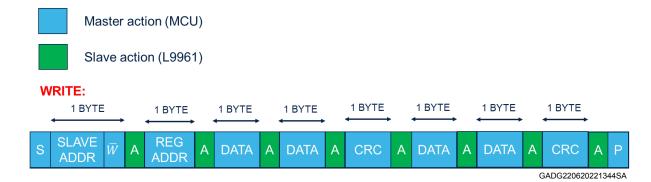

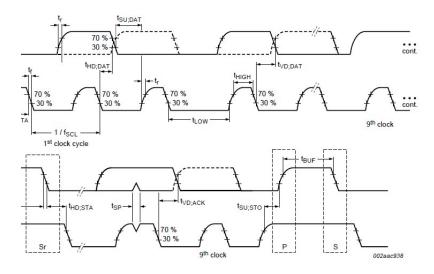

- I<sup>2</sup>C peripheral for device programming and data transfers over I<sup>2</sup>C bus

- Cell balancing supporting up to 70 mA per cell

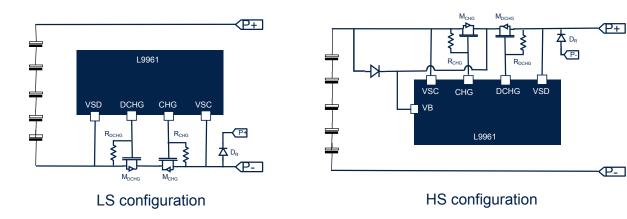

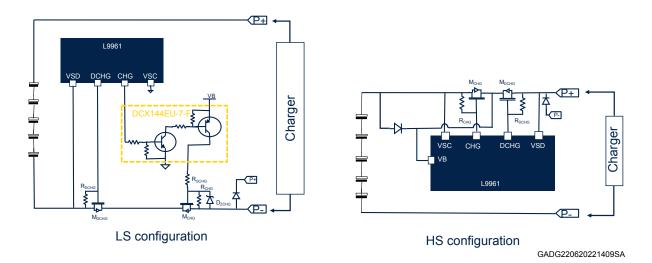

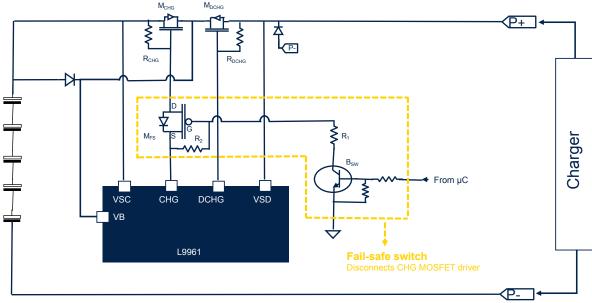

- Dual configurable HS/LS predriver for pack relay management

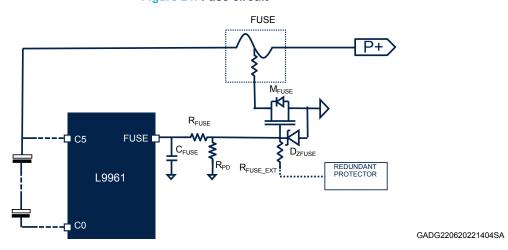

- Pack fuse management

- Embedded NVM for configuration parameters storage

- High hotplug robustness

# L9961 **Product label**

**Product status link**

| Product summary |          |                  |  |  |  |  |

|-----------------|----------|------------------|--|--|--|--|

| Order code      | Package  | Packing          |  |  |  |  |

| L9961-TR        | VFQFPN32 | Tape and<br>Reel |  |  |  |  |

## **Applications**

- Cordless power tools

- Backup energy storage systems and UPS

- Light electric vehicles (e-bikes, scooters, etc.)

- Portable and semi-portable equipment

- Medical equipment

## **Description**

L9961 is part of a complete battery pack monitoring, balancing, and protecting system for Li-Ion and Li-Polymer cells in 3, 4 or 5 series configurations. The L9961 uses a high precision ADC to provide cell voltage, stack voltage and temperature conversion via external NTC. Voltage monitoring functions are cyclically performed with a programmable loop time. Stack current is also monitored via a high accuracy CSA, continuously running and performing also Coulomb counting. Cell balancing is available and can be simultaneously activated on all cells. IC configuration and information exchange for SOC/SOH estimation are performed via I<sup>2</sup>C peripheral. The IC also integrates a dual pre-driver programmable in both HS/LS configurations for driving pack relays. L9961 also implements battery pack fuse protection to prevent fire and explosion hazards. A 3.3 V regulator with a high current capability is available for supplying pack controller and other external circuitry in both standby and normal operation modes. The IC protects the battery pack against over/under voltage conditions and monitors for over/under temperature. It also features protection against overcurrent (both directions) and short-circuit in discharge events. Safety-relevant configurations can be stored in the internal NVM to avoid re-programming the device at each wake-up.

DS14012 - Rev 5 page 2/63

# 1 Pin description and block diagram

## 1.1 Device pinout

Table 1. Device pinout

| Pin# | Pin name    | Pin function                                              | Pin type                     | Internal PU/PD | Active |

|------|-------------|-----------------------------------------------------------|------------------------------|----------------|--------|

| 1    | C0          | Cell 1 negative terminal                                  | Analog in                    |                |        |

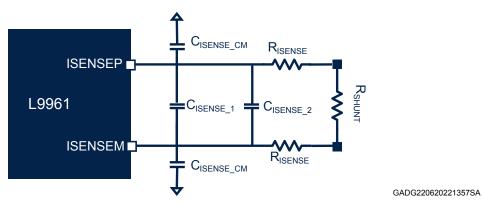

| 2    | ISENSEP     | Current sense ADC positive input terminal                 | Analog in                    |                |        |

| 3    | ISENSEM     | Current sense ADC negative input terminal                 | Analog in                    |                |        |

| 4    | GND         | Device ground                                             | Power in                     |                |        |

| 5    | SCL         | I <sup>2</sup> C clock line                               | Digital input                |                | Low    |

| 6    | SDA         | I <sup>2</sup> C data line                                | Digital input/<br>open-drain |                | Low    |

| 7    | RDY         | Ready interrupt output                                    | Push/pull                    |                |        |

| 8    | VREG        | 3.3 V LDO output                                          | Power out                    |                |        |

| 9    | NTC         | NTC sensing input                                         | Analog in                    |                |        |

| 10   | OD          | Open-drain switch for NTC connection to GND               | Open-drain                   |                | Low    |

| 11   | FAULTN_SAFE | Critical fault output                                     | Open-drain                   |                | Low    |

| 12   | FAULTN      | Fault output / external CHG/<br>DCHG shutdown trigger     | Digital input/<br>open-drain |                | Low    |

| 13   | TM_ENTER    | Reserved for debug. Connect to GND.                       |                              | PD             |        |

| 14   | WAKEUP      | Wakeup from STANDBY input                                 | Digital I/O                  | PD             | High   |

| 15   | NSHIP       | Wakeup from SHIPMENT - DEEP SLEEP input                   | Analog in                    |                | High   |

| 16   | FUSE        | Fuse pre-driver output / external fuse activation trigger | Analog out/digital in        | PD             | High   |

| 17   | DCHG        | Discharge switch gate                                     | Analog out                   |                |        |

| 18   | VSD         | Discharge switch source                                   | Analog out                   |                |        |

| 19   | VSC         | Charge switch source                                      | Analog out                   |                |        |

| 20   | CHG         | Charge switch gate                                        | Analog out                   |                |        |

| 21   | VCP1M       | Charge pump flying capacitor input                        | Analog                       |                |        |

| 22   | VCP1P       | Charge pump flying capacitor input                        | Analog                       |                |        |

| 23   | VCP2M       | Charge pump flying capacitor input                        | Analog                       |                |        |

| 24   | VCP2P       | Charge pump flying capacitor input                        | Analog                       |                |        |

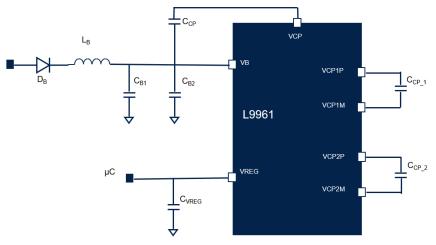

| 25   | VCP         | Charge pump output                                        | Power out                    |                |        |

| 26   | VB          | Device battery input                                      | Power in                     |                |        |

| 27   | TM1         | Reserved for debug. Connect to GND.                       |                              |                |        |

DS14012 - Rev 5 page 3/63

| Pin# | Pin name | Pin function             | Pin type  | Internal PU/PD | Active |

|------|----------|--------------------------|-----------|----------------|--------|

| 28   | C5       | Cell 5 positive terminal | Analog in |                |        |

| 29   | C4       | Cell 4 positive terminal | Analog in |                |        |

| 30   | C3       | Cell 3 positive terminal | Analog in |                |        |

| 31   | C2       | Cell 2 positive terminal | Analog in |                |        |

| 32   | C1       | Cell 1 positive terminal | Analog in |                |        |

DS14012 - Rev 5 page 4/63

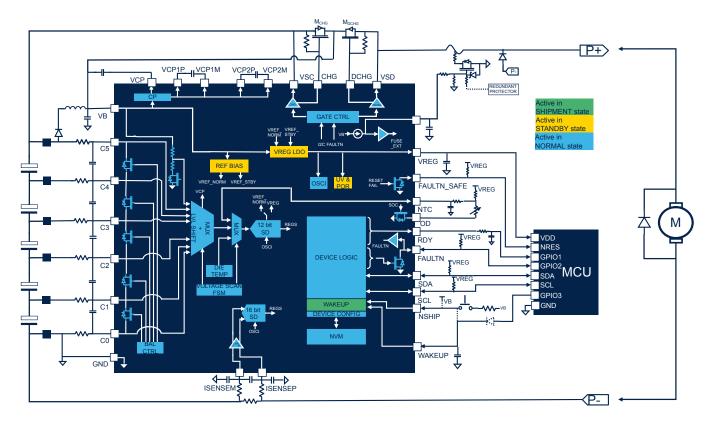

## 1.2 Block diagram

Figure 1. Block diagram

GADG230620220924SA

DS14012 - Rev 5 page 5/63

## 2 Product electrical and thermal ratings

## 2.1 Operating range (OR)

Within the operating range the part operates as specified and without parameter deviations. The device may not operate properly if maximum operating conditions are exceeded.

Once taken beyond the operative ratings and returned back within, the part will recover with no damage or degradation, unless the AMR are exceeded.

Additional supply voltage and temperature conditions are given separately at the beginning of each electrical specification table.

Table 2. Operating ranges

| Symbol                        | Parameter                          | Min.  | Тур.    | Max.                    | Unit |

|-------------------------------|------------------------------------|-------|---------|-------------------------|------|

| VB                            | Battery level                      | 4.3   |         | 25                      | V    |

| VCP                           | Charge pump tank output pin        |       | VB+12 V |                         | V    |

| VCP1P, VCP2P,<br>VCP1M, VCP2M | Charge pump flying capacitor pin   | 0     |         | VCP                     | V    |

| C1, C2, C3, C4                | Cell terminal pins                 | 0     |         | VB                      | V    |

| C5                            | Cell terminal pins                 | 0     |         | VB+0.6                  | V    |

| C1, C2, C3, C4, C5            | Cell terminal differential Voltage | 1     |         | 4.7                     | V    |

| VREG                          | 3.3 V regulated voltage            |       | 3.3     |                         | V    |

| NTC                           | Analog input pin                   | 0     |         | VREG                    | V    |

| OD                            | Open drain pin                     | 0     |         | VREG                    | V    |

| SDA, SCL                      | Digital input pins                 | 0     |         | VREG                    | V    |

| FAULTN_SAFE, RDY,<br>FAULTN   | Digital output pin                 | 0     |         | VREG                    | V    |

| WAKEUP                        | Analog input pin                   | 0     |         | VB                      | V    |

| NSHIP                         | Analog input pin                   | 0     |         | VB                      | V    |

| FUSE                          | Analog output pin                  | 0     |         | VB                      | V    |

| VSD                           | Discharge MOS source               | -1    |         | VB+1                    | V    |

| VSC                           | Charge MOS source                  | -1    |         | VB+1                    | V    |

| CHG                           | Charge MOS gate                    | VSC   |         | Min(VCP; VSC + 12<br>V) |      |

| DCHG                          | Discharge MOS gate                 | VSD   |         | Min(VCP; VSD + 12<br>V) |      |

| ISENSEP -<br> ISENSEM         | CSA input differential mode range  | -200  |         | 300                     | mV   |

| ( ISENSEPI +<br> ISENSEM ) /2 | CSA input common mode range        | -200  |         | 200                     | mV   |

| GND                           | Device ground                      |       | 0       |                         | V    |

| TM1                           | Device ground                      |       | 0       |                         | V    |

| TM_ENTER                      | Device ground                      |       | 0       |                         | V    |

| C0                            | Cell terminal voltage              | -0.15 |         | 0.15 V                  | V    |

DS14012 - Rev 5 page 6/63

## 2.2 Absolute maximum ratings (AMR)

Maximum ratings are absolute ratings; exceeding any one of these values may cause permanent damage to the integrated circuit.

All voltages are related to the potential at substrate ground GND.

Table 3. Absolute maximum ratings

| Symbol                   | Min.               | Тур. | Max.                  | Unit |

|--------------------------|--------------------|------|-----------------------|------|

| VB                       | -0.3               |      | 40                    | V    |

| VCP                      | VB-0.3             |      | VB+20                 | V    |

| VCP1P                    | VB-0.3             |      | VB+20                 | V    |

| VCP2P                    | VCP1P-0.3          |      | VB+20                 | V    |

| VCP1M,VCP2M              | Max(-0.3; VB-20 V) |      | VB+0.3                | V    |

| C1, C2, C3, C4, C5       | -0.3               |      | 40                    | V    |

| C(n)-C(n-1) for n=1 to 5 | -0.3               |      | 40 (if VB=40 V)       | V    |

| VREG                     | -0.3               |      | 4.3                   | V    |

| NTC                      | -0.3               |      | VREG + 0.3            | V    |

| OD                       | -0.3               |      | VREG + 0.3            | V    |

| SDA, SCL                 | -0.3               |      | VREG + 0.3            | V    |

| FAULTN_SAFE, RDY, FAULTN | -0.3               |      | VREG + 0.3            | V    |

| WAKEUP                   | -0.3               |      | 40                    | V    |

| NSHIP                    | -0.3               |      | 40                    | V    |

| FUSE                     | -0.3               |      | 40                    | V    |

| VSC, VSD                 | -2                 |      | 40                    | V    |

| CHG                      | VSC                |      | Min(VCP; VSC + 20 V)  | V    |

| DCHG                     | VSD                |      | Min (VCP; VSD + 20 V) | V    |

| ISENSEP, ISENSEM         | -2                 |      | VREG + 0.3            | V    |

| GND                      |                    | 0    |                       | V    |

| C0                       | -0.3               |      | 6                     | V    |

| TM_ENTER                 | -0.3               |      | 6                     | V    |

| TM1                      | -0.3               |      | 40                    | V    |

|                          | - I                |      | 1                     |      |

## 2.3 ESD ratings

Table 4 lists the device ESD ratings.

Table 4. ESD protection

| Item     | Parameter | Condition                                 | Min. | Max. | Unit |

|----------|-----------|-------------------------------------------|------|------|------|

| All pins | НВМ       | Tested per AEC-Q100-002                   | -2   | 2    | kV   |

| All pins | CDM       | Tested per AEC-Q100-011                   | -500 | 500  | V    |

| All pins | Latch-up  | Tested per AEC-Q100-004, Class-2, Level-A | -100 | 100  | mA   |

DS14012 - Rev 5 page 7/63

## 2.4 Thermal ratings

Table 5 lists the device thermal ratings.

Table 5. Thermal ratings

| Symbol            | Parameter                               | Test conditions                         | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------------------|-----------------------------------------|------|------|------|------|

| T <sub>A</sub>    | Operating and testing temperature       |                                         | -40  |      | 85   | °C   |

| TJ                | Operating junction temperature range    |                                         | -40  |      | 120  | °C   |

| T <sub>stg</sub>  | Storage temperature range               |                                         | -55  |      | 150  | °C   |

| R <sub>thJA</sub> | Thermal resistance, junction-to-ambient | According to JEDEC standard on 2s2p PCB |      | 38   |      | °C/W |

| MINIA             |                                         | ON L9961 EVAL Board                     |      | TBD  |      | °C/W |

DS14012 - Rev 5 page 8/63

## 3 Functional description

#### 3.1 Device funcional states

L9961 can operate in 3 different states when battery is applied: SHIPMENT - DEEP SLEEP, STANDBY or NORMAL.

Battery pack OFF Battery pack connected SHIPMENT VREG STBY UV Trigger from NSHIP GO2SHIP command or V<sub>NSHIP</sub> > V<sub>NSHIP\_TH</sub> for t > T<sub>NSHIP\_FIL</sub> NVM Trimming & **STANDBY** GO2STBY Calibration corruption command or Trigger from WAKEUP VREG NORM U' V<sub>WAKEUP</sub> > V<sub>WAKEUP\_TH</sub> NSHIP=V<sub>B</sub> event for t > T<sub>WAKEUP\_FIL</sub> GO2SHIP command NORMAL GADG220620221208SA

Figure 2. Device FSM

#### 3.1.1 Shipment - DEEP SLEEP

The SHIPMENT - DEEP SLEEP state is recommended for pack shipping and storage purposes. When in this state, L9961 current consumption from VB pin is reduced to just  $I_{VB\_SHIP}$ , allowing long periods of inactivity to reduce battery pack discharge.

When the battery pack is first applied (L9961 receives VB supply for the first time), the device transitions to either shipment - DEEP SLEEP state or NORMAL state depending on NSHIP pin. If NSHIP is biased to VB pin, the device starts in NORMAL State, otherwise the device begins in SHIPMENT - DEEP SLEEP state.

The device can enter SHIPMENT - DEEP SLEEP from NORMAL state upon receiving a GO2SHIP command through  $I^2C$  communications (GO2SHIP command is asserted by setting the GO2SHIP bit to '10' in the register 0x21) or if VREG voltage drops below the minimum level ( $V_{VREG\ STBY\_UV}$ ) required to supply the device.

To avoid inadvertent reactivation, the NSHIP pin shall be set low before sending the GO2SHIP command, and it shall be kept low during the transition to SHIPMENT - DEEP SLEEP.

Sending a GO2SHIP command while NSHIP is high will cause the device to move to STANDBY state.

## 3.1.2 STANDBY

The STANDBY state is recommended to manage short periods of inactivity, where wakeup from MCU is needed. While in STANDBY, L9961 current consumption from VB pin is reduced to  $I_{VB\ STBY}$ .

The device is powered but no system functions are available, except WAKEUP sensing and VREG regulator which operates with reduced performance characteristics. While VREG is operational, the FAULTN\_SAFE pin is released allowing the MCU to operate in lower power mode.

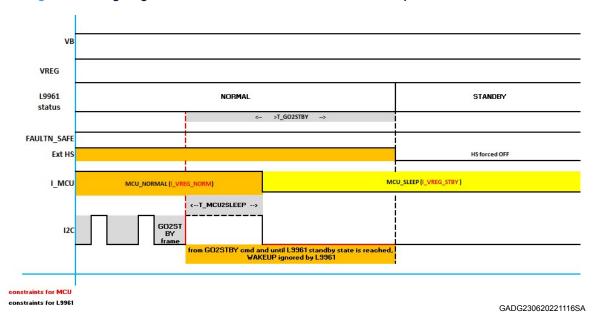

STANDBY state can be reached from NORMAL state, upon receiving a GO2STBY command through I<sup>2</sup>C communications (GO2STBY command is asserted by setting the GO2STBY bit to '10' in the register 0x22) or if VREG drops below the minimum level (V<sub>VREG\_NORM\_UV</sub>) required for L9961 to correctly perform its normal features.

DS14012 - Rev 5 page 9/63

Once L9961 acknowledges the GO2STBY command, it moves to STANDBY state after T<sub>GO2STBY</sub>. To allow a smooth transition, MCU must move to a low power state (where its average current consumption is less than  $I_{VREG\_STBY}$ ) within  $T_{MCU2STBY}$  after sending GO2STBY command to L9961.

To avoid inadvertent reactivation, the WAKEUP pin shall be set low before sending the GO2STBY command, and it shall be kept low during the transition to STANDBY.

Figure 3. Timing diagram: transition from NORMAL to STANDBY upon GO2STBY command

#### 3.1.3 **NORMAL**

The NORMAL state is recommended when the system is working. All IC functions are active, including voltage/ temperature/current monitoring and protection. Pack relay management and I<sup>2</sup>C peripheral are also available. L9961 current consumption from VB pin while in NORMAL state varies over time, due to the execution of periodical tasks, balancing activation/deactivation, pre-driver turn on/off events.

NORMAL state can be reached:

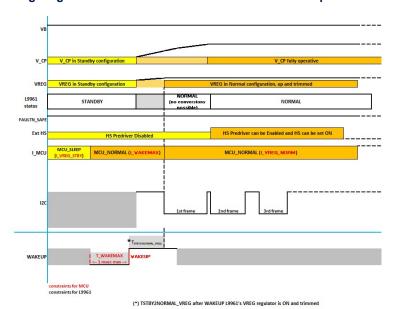

- from STANDBY state, if WAKEUP pin is higher than VWAKEUP TH for at least TWAKEUP STBY. Refer to Figure 4

- The wake-up source can be either an external stimulus (pushbutton or other) or the system MCU asserting the WAKEUP pin via GPIO (refer to Figure 1)

- Transition from STANDBY to NORMAL must be properly handled, as VREG regulator needs to switch from reduced performance to full power within a defined time window. Such an operation requires T<sub>STBY2NORMAL</sub> from the receival of the WAKEUP condition to be accomplished

- During T<sub>STBY2NORMAL</sub>, VREG can sustain a load current up to IWAKEMAX for a maximum T<sub>WAKEMAX</sub> time interval, within which the MCU must wakeup L9961

- After T<sub>STBY2NORMAL</sub>, the VREG regulator has reached its NORMAL state specification. After T<sub>I2C READY</sub> a RDY pulse is generated to mark the transition to NORMAL. This allows the MCU to fully operate in its normal state, respond to watchdog, serve interrupts, and so on. L9961 is capable of decoding I<sup>2</sup>C commands and receive new configurations

- It takes T<sub>CP</sub> STARTUP from the receival of WAKEUP condition for the charge pump to be ready. After T<sub>CP</sub> STARTUP. L9961 will run monitoring/diagnostic tasks and manage the pre-driver stage

- Once L9961 is in NORMAL the MCU is expected to set the WAKEUP pin low to reduce current consumption.

DS14012 - Rev 5 page 10/63

- From SHIPMENT DEEP SLEEP state, if NSHIP pin is higher than V<sub>NSHIP\_TH</sub> for at least T<sub>WAKEUP\_NSHIP</sub>.

- After T<sub>SHIP2NORMAL</sub>, the VREG regulator has reached its NORMAL state specification. After T<sub>I2C\_READY</sub> an RDY pulse is generated to mark the transition to NORMAL. This allows the MCU to fully operate in its normal state, respond to watchdog, serve interrupts, and so on. L9961 is capable of decoding I<sup>2</sup>C commands and receives new configurations

- MCU should still wait for T<sub>CP</sub> STARTUP when out of reset, before trying to operate the pre-driver stage

Upon receival of wake-up condition, transitions to other states are masked until NORMAL state has been fully reached. Once the device enters NORMAL state, the logic starts a T<sub>VREG\_UV\_BLK</sub> blanking time on the VREG UV comparator in order to prevent erroneously flagging UV conditions that would bring L9961 back to STANDBY state.

Figure 4. Timing diagram: transition from STANDBY to NORMAL upon WAKEUP detection

GADG230620221116SA

#### 3.1.4 Electrical parameters

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: VB according to the operating range of Table 2; T<sub>J</sub> according to the operating range of Table 5.

Table 6. L9961 operating states electrical parameters

| Symbol                | Parameter                                                             | Test conditions                                                                                                                   | Min. | Тур. | Max. | Unit |

|-----------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| I <sub>VB_SHIP</sub>  | Consumption from VB pin when in SHIPMENT - DEEP SLEEP                 | -30 °C< T <sub>AMB</sub> =T <sub>J</sub> <60 °C                                                                                   |      |      | 2    | μΑ   |

| I <sub>VB</sub> _STBY | Consumption from VB pin when in STANDBY                               | -30 °C< T <sub>AMB</sub> =T <sub>J</sub> <60°C<br>No load on VREG                                                                 |      |      | 5    | μA   |

| I <sub>VB_NORM</sub>  | Consumption from VB pin when in NORMAL                                | NORMAL state, CHG/DHCG<br>OFF, no load on VREG, no<br>communication, Balancing<br>OFF, NRES and FAULTN<br>released, CSA disabled. |      | 155  | 190  | μА   |

| Ivb_norm_delta_csa    | Additional current consumption from VB when current ADC is converting | CSA_EN = 1<br>CC_ACC_EN = 1<br>OVC_EN = 1<br>SC_EN = 1                                                                            |      | 90   | 125  | μА   |

DS14012 - Rev 5 page 11/63

| Symbol                    | Parameter                                                                          | Test conditions                                                                                | Min. | Тур. | Max. | Unit |

|---------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|------|

| IVB_NORM_DELTA_CONV       | Additional current consumption from VB when Voltage ADC is continuously converting |                                                                                                |      | 135  | 190  | μА   |

| dc <sub>ADC_</sub> CONV   | Percentage time for which<br>lvb_NORM_DELTA_CONV is active <sup>(1)</sup>          |                                                                                                | 3    |      | 80   | %    |

| IVB_NORM_DELTA_BAL        | Additional current consumption from VB pin due to 1 Balance ON                     | Normal condition, additional contribution for 1 Balance ON                                     |      | 8    | 12   | μA   |

| VB_NORM_DELTA_FET_HS (2)  | Additional current consumption from VB pin due to 1 Ext FET HS ON                  | Normal condition, additional contribution for 1 Ext FET ON.  HS configuration No ext R mounted |      | 9    | 20   | μΑ   |

| IVB_NORM_DELTA_FET_LS     | Additional current consumption from VB pin due to 1 Ext FET LS ON                  | Normal condition, additional contribution for 1 Ext FET ON. LS configuration No ext R mounted  |      | 15   | 20   | μA   |

|                           | Current consumption from VB pin when voltage ADC is converting                     | Application info                                                                               |      |      |      |      |

| I <sub>VB_DELTA</sub>     | Current ADC is converting                                                          |                                                                                                |      | 350  | 420  | μA   |

| _                         | Ext. FETs enabled                                                                  |                                                                                                |      |      |      |      |

|                           | T <sub>MEAS_CYCLE</sub> = 10 ms                                                    |                                                                                                |      |      |      |      |

| V <sub>VB_TRAN_NORM</sub> | Max allowed transient slope on VB pin                                              | Application info                                                                               |      |      | 1    | V/µs |

The current consumption linked to voltage conversion can be calculated as (I<sub>VB\_NORM\_DELTA\_CONV</sub> \* Duty\_cycle\_voltage\_conversion)/100.

## 3.2 Wakeup sources (NSHIP/WAKEUP)

L9961 can be woken up via two dedicated pins:

- NSHIP can be used as wake-up from SHIPMENT DEEP SLEEP

- WAKEUP can be used as wake-up from STANDBY

## 3.2.1 Electrical parameters

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: VB according to the operating range of Table 2; T<sub>J</sub> according to the operating range of Table 5.

Table 7. VREG electrical parameters

| Symbol                  | Parameter                                                           | Test conditions  | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------------------------------------------------------|------------------|------|------|------|------|

| V <sub>WAKEUP_TH</sub>  | WAKEUP wakeup threshold                                             |                  | 0.8  |      | 1.8  | V    |

| V <sub>NSHIP_TH</sub>   | NSHIP wakeup threshold                                              |                  | 1    |      | 3    | V    |

| T <sub>WAKEUP_FIL</sub> | WAKEUP filter time                                                  |                  |      |      | 40   | μs   |

| T <sub>NSHIP_FIL</sub>  | NSHIP filter time                                                   |                  |      |      | 20   | μs   |

| R <sub>WAKEUP_PD</sub>  | WAKEUP pulldown resistor                                            |                  | 60   | 100  | 150  | kΩ   |

| T <sub>MCU2STBY</sub>   | Maximum delay from sending GO2STBY command to MCU in low power mode | Application info |      |      | 1    | ms   |

DS14012 - Rev 5 page 12/63

In HS case an additional current contribution must be added to include the effect of charge pump switching activity at increased frequency. This contribution is impacted by the ext parasistic capacitances between each CP pin and GND in the range of 3 μA/pF.

| Symbol                   | Parameter                                                                                           | Test conditions                                                                      | Min. | Тур. | Max. | Unit |

|--------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------|------|------|------|

| T <sub>GO2STBY</sub>     | Maximum delay from receival of GO2STBY command to L9961 in STANDBY state                            | Application info                                                                     | 2    |      | 4    | ms   |

| T <sub>GO2SHIP</sub>     | Time delay for L9961 from received GO2SHIP command from MCU to enter SHIPMENT - DEEP SLEEP state    | Application info                                                                     | 0    |      | 10   | ms   |

| I <sub>WAKEMAX</sub>     | VREG current capability in STANDBY to NORMAL state transition, during T <sub>WAKEMAX</sub> interval | Application info                                                                     |      |      | 15   | mA   |

| T <sub>WAKEMAX</sub>     | MCU time in NORMAL mode to send a WAKEUP command to L9961                                           | Application info                                                                     |      |      | 1    | ms   |

| T <sub>STBY2NORMAL</sub> | Time to complete STANDBY to NORMAL transition                                                       | From WAKEUP assertion to VREG_UV release                                             |      |      | 1    | ms   |

| T <sub>SHIP2NORMAL</sub> | Time to complete SHIPMENT - DEEP SLEEP to normal transition                                         | From NSHIP assertion to VREG UV release. No load on VREG, 4.7uF capacitance present. |      |      | 5    | ms   |

| T <sub>I2C_READY</sub>   | I <sup>2</sup> C settling time                                                                      | From WAKEUP/NSHIP assertion to I <sup>2</sup> C ready                                |      |      | 15   | ms   |

| T <sub>CP_STARTUP</sub>  | Charge pump startup time                                                                            | From VREG_UV release (T <sub>VREG_UV_BLK</sub> expired) to VCP in range              |      |      | 8    | ms   |

## 3.3 VREG LDO

L9961 provides a system regulator capable of providing power to the system MCU and other peripheral devices or circuits. Performances of the regulator vary according to L9961 state:

- In STANDBY State, the regulated voltage is V<sub>VREG\_STBY</sub> and average current capability is limited to

I<sub>VREG\_STBY</sub>. Line/load regulation performances are reduced to V<sub>VREG\_LIN\_REG\_STBY</sub> and

V<sub>VREG\_LOAD\_REG\_STBY</sub> respectively. VREG current limit is still active with a I<sub>VREG\_CURR\_LIM\_STBY</sub> threshold

- In NORMAL State, the regulated voltage is V<sub>VREG\_NORM</sub>, with a I<sub>VREG\_NORM</sub> average current capability.

Line/load regulation performances are defined by V<sub>VREG\_LIN\_REG\_NORM</sub> and V<sub>VREG\_LOAD\_REG\_NORM</sub> respectively. VREG current limit is active with a I<sub>VREG\_CURR\_LIM</sub> threshold.

#### 3.3.1 Electrical parameters

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: VB according to the operating range of Table 2;  $T_J$  according to the operating range of Table 5.

**Table 8. VREG electrical parameters**

| Symbol                 | Parameter          | Test conditions                                                                                          | Min. | Тур. | Max. | Unit |

|------------------------|--------------------|----------------------------------------------------------------------------------------------------------|------|------|------|------|

| Vvreg_norm             | Regulated voltage  | NORMAL state<br>10 μA <lload<30 ma<="" td=""><td>3.23</td><td>3.3</td><td>3.37</td><td>V</td></lload<30> | 3.23 | 3.3  | 3.37 | V    |

| I <sub>VREG_NORM</sub> | Current load range | NORMAL state Design info                                                                                 | 0.01 |      | 35   | mA   |

| IVREG_CURR_LIM         | Current limitation | NORMAL state<br>VREG=2.7 V                                                                               | 40   |      |      | mA   |

| IVREG_CURR_LIM_STBY    | Current limitation | STANDBY state<br>VREG=2.6 V                                                                              | 15   |      | 85   | mA   |

| Vvreg_lin_reg_norm     | Line regulation    | NORMAL state VB from 4.3V to 22 V in 100 μs Ilload=100 μA, 30 mA guaranteed by design                    | -150 |      | +150 | mV   |

DS14012 - Rev 5 page 13/63

| Symbol                         | Parameter                                             | Test conditions                                                         | Min. | Тур.        | Max.                         | Unit |

|--------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------|------|-------------|------------------------------|------|

|                                |                                                       | NORMAL state                                                            |      |             |                              |      |

| Vvreg_load_reg_norm            | Load regulation                                       | lload from 0 μA to 15 mA (and viceversa), with ideal step transition    | -160 |             | +160                         | mV   |

| V                              | D                                                     | STANDBY state                                                           | 0.0  |             | 0.0                          | .,   |

| V <sub>VREG_STBY</sub>         | Regulated voltage                                     | -30 °C< T <sub>AMB</sub> =T <sub>J</sub> <60 °C                         | 2.8  |             | 3.0                          | V    |

|                                |                                                       | STANDBY state                                                           |      |             |                              |      |

| I <sub>VREG_STBY</sub>         | Output current                                        | -30 °C< T <sub>AMB</sub> =T <sub>J</sub> <60 °C                         | 1    |             | 300                          | μA   |

|                                |                                                       | Application info                                                        |      |             | +160                         |      |

|                                |                                                       | STANDBY state                                                           |      |             | 3.6<br>300<br>+250<br>+400   |      |

| V <sub>VREG_LIN_REG_STBY</sub> | Line reg stby                                         | VB from 4.3V to 22 V in 100 μs                                          | -250 |             |                              | mV   |

|                                |                                                       | lload=0, 50 μA guaranteed by design                                     |      | +400        |                              |      |

| V                              | Load regulation in                                    | STANDBY state                                                           | 400  |             | 1400                         | mV   |

| Vvreg_load_reg_stby            | STANDBY                                               | lload= step 0-50 μA in 100 μs                                           | -400 | -400 +400 r | IIIV                         |      |

|                                |                                                       | STANDBY state                                                           |      |             | . 400                        |      |

| Vvreg_load_reg_stby_ovl        | Overload regulation in STANDBY                        | Iload= step 0-l <sub>WAKEMAX</sub> , pulse lasting T <sub>WAKEMAX</sub> | 2.7  |             |                              | V    |

|                                |                                                       | -30 °C< T <sub>AMB</sub> =T <sub>J</sub> <60 °C                         |      |             | 300<br>+250<br>+400<br>7 2.9 |      |

| V <sub>VREG_NORM_UV</sub>      | VREG Undervoltage<br>threshold in NORMAL<br>state     |                                                                         | 2.6  | 2.7         | 2.9                          | V    |

| T <sub>VREG_UV_FIL</sub>       | VREG UV filter time in NORMAL state                   |                                                                         |      | 20          |                              | μs   |

| T <sub>VREG_UV_BLK</sub>       | VREG UV blanking time upon transition to NORMAL state |                                                                         | 8    |             |                              | ms   |

| Vvreg_stby_uv                  | VREG Undervoltage<br>threshold in STANDBY<br>state    | STANDBY state                                                           | 2.1  | 2.5         | 2.8                          | V    |

| C <sub>REG</sub>               | External LDO capacitance                              | Application info, required for stability                                | -20% | 4.7         | +20%                         | μF   |

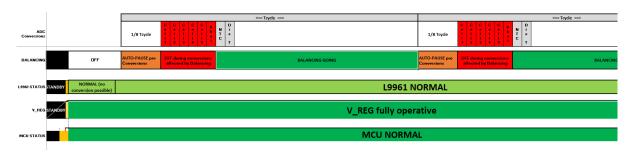

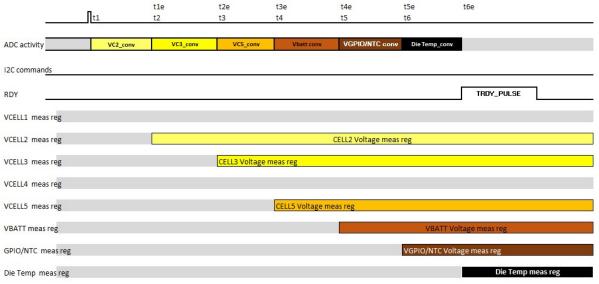

## 3.4 Voltage conversion routine

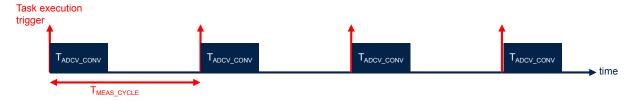

While in NORMAL state, L9961 cyclically executes the voltage conversion routine as shown in Figure 6. Task execution time is  $T_{ADCV\_CONV}$ , which is the sum of the individual step duration:

- N<sub>CELL</sub> represents the number of enabled cells. The T<sub>CELL\_FILTER</sub> filter time is applied to each cell conversion. At least 3 cells must be converted

- The T<sub>CELL</sub> FILTER filter time is also applied to VB pin conversion (if enabled)

- The T<sub>TEMP</sub> FILTER filter time is applied to NTC conversion (if enabled)

- The T<sub>TEMP FILTER</sub> filter time is applied to Die Temperature conversion, which is always performed

- The task is scheduled to run every T<sub>MEAS\_CYCLE</sub> (programmable in TCYCLE field). Changing configuration

parameters while a conversion is ongoing may result in inadvertent faults and reactions. MCU is supposed

to disable the voltage conversion routine programming T<sub>MEAS\_CYCLE</sub> = 0x0 before applying a new

configuration set.

DS14012 - Rev 5 page 14/63

Figure 5. Voltage conversion routine steps

GADG220620221212SA

Table 9. Voltage conversion routine execution parameters

| Symbol                  | Parameter                                                                                       | Test conditions | Min. | Тур. | Max. | Unit |

|-------------------------|-------------------------------------------------------------------------------------------------|-----------------|------|------|------|------|

| T <sub>MEAS_CYCLE</sub> | Programmable voltage conversion routine execution period (5 bit) $T_{MEAS_{CYCLE}} = 10ms*CODE$ | -               | 10   | -    | 310  | ms   |

Task execution period  $T_{MEAS\_CYCLE}$ , must always be greater than the task duration. In case the task execution period is programmed shorter than the task duration, this will result in the task being executed with random periodicity.

Figure 6. Correct management of the task execution periodicity

GADG220620221219SA

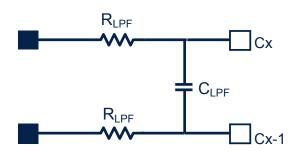

#### 3.4.1 Cell voltage monitor (Cx)

During cells voltage monitoring step, the voltage conversion routine measures differential voltages at Cx pins and stores results in VCELL<x> registers. The digital sum of cells is stored in the VCELL\_SUM\_MEAS register.

A cell is converted only if its corresponding VCELL<x>\_EN bit is enabled. By default, all cells are disabled. At least 3 cells must be enabled in order to guarantee proper operation.

If less than 5 cells are used:

Mount the cells starting from the bottom-most (C0-C1)

Measurements are compared to programmable thresholds to detect the failures listed in Table 12.

Table 10. Cell voltage monitor diagnostics

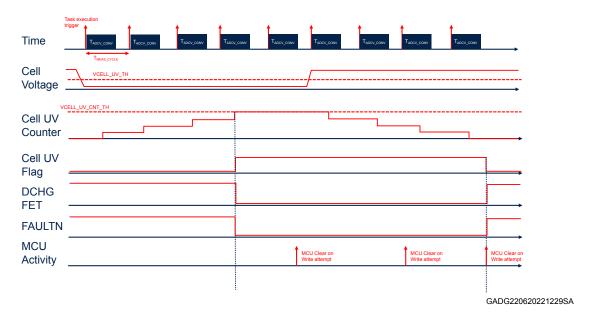

| Fault<br>type | Assertion condition                                                                                     | IC reaction to assertion        | Release condition                                                                             | IC reaction to flag clear                                              | Maskable                                                                                                           |

|---------------|---------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Cell UV       | If a cell voltage falls<br>below VCELL_UV_TH,<br>the corresponding UV<br>counter is incremented<br>by 1 | The CELL <x>_UV flag is set</x> | If a cell voltage raises above VCELL_UV_TH, the corresponding UV counter is decremented by 1. | The discharge FET is restored to the status defined by the DCHG_ON bit | VCELL <x>_EN masks<br/>measurement<br/>execution. The UV flag<br/>of a disabled cell can<br/>always be cleared</x> |

DS14012 - Rev 5 page 15/63

| Fault<br>type        | Assertion condition                                                                                      | IC reaction to assertion                                                                                                                                                                 | Release condition                                                                                        | IC reaction to flag<br>clear                                           | Maskable                                                                                                                      |

|----------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Cell UV              | If the UV counter reaches VCELL_UV_CNT_TH, it                                                            | The discharge FET is turned OFF                                                                                                                                                          | If the UV counter reaches zero, the cell                                                                 | FAULTN line is released                                                | CELL_UV_PRDRV_MS<br>K masks reaction on<br>DCHG pin                                                                           |

| OCII O V             | saturates and the cell UV fault is acknowledged.                                                         | FAULTN line is asserted                                                                                                                                                                  | UV flag can be cleared<br>by MCU                                                                         | FAULTN line is released                                                | CELL_UV_FAULTN_MS<br>K masks reaction on<br>FAULTN pin                                                                        |

|                      | If a cell voltage falls                                                                                  | The CELL <x>_SEVERE_UV flag is set</x>                                                                                                                                                   | If a cell voltage raises                                                                                 | The discharge FET is restored to the status defined by the DCHG_ON bit | VCELL <x>_EN masks<br/>measurement<br/>execution. The severe<br/>UV flag of a disabled<br/>cell can always be<br/>cleared</x> |

| Cell<br>severe<br>UV | below VCELL_SEVERE_UV_T H, the severe UV fault is                                                        | The discharge FET is turned OFF                                                                                                                                                          | above VCELL_SEVERE_UV_T H, the cell severe UV                                                            | FUSE pre-driver is disabled                                            | CELL_SEVERE_UV_P<br>RDRV_MSK masks<br>reaction on DCHG pin                                                                    |

|                      | acknowledged                                                                                             | FUSE pre-driver is enabled                                                                                                                                                               | flag can be cleared by MCU                                                                               | FAULTN line is released                                                | CELL_SEVERE_UV_F<br>USE_MSK masks<br>reaction on FUSE pin                                                                     |

|                      |                                                                                                          | FAULTN line is asserted                                                                                                                                                                  |                                                                                                          | FAULT N line is released                                               | CELL_SEVERE_UV_FA<br>ULTN_MSK masks<br>reaction on FAULTN pin                                                                 |

|                      | If a cell voltage raises<br>above VCELL_OV_TH,<br>the corresponding OV<br>counter is incremented<br>by 1 | The CELL <x>_OV flag is set</x>                                                                                                                                                          | If a cell voltage falls<br>below VCELL_OV_TH,<br>the corresponding OV<br>counter is decremented<br>by 1. | The charge FET is restored to the status defined by the CHG_ON bit     | VCELL <x>_EN masks<br/>measurement<br/>execution. The OV flag<br/>of a disabled cell can<br/>always be cleared</x>            |

|                      | If the OV counter reaches VCELL_OV_CNT_TH, it saturates and the cell OV fault is acknowledged.           | The charge FET is turned OFF                                                                                                                                                             |                                                                                                          |                                                                        | CELL_OV_PRDRV_MS<br>K masks reaction on<br>CHG pin                                                                            |

| Cell OV              |                                                                                                          | FAULTN_SAFE is pulled low for  TFAULTN_SAFE_LOW (if a pulse on FAULTN_SAFE pin was not already generated after a previous not masked and not cleared Cell OV / Cell Severe OV detection) | If the OV counter reaches zero, the cell OV flag can be cleared by MCU                                   | FAULTN line is released                                                | CELL_OV_RST_MSK masks reaction FAULTN_SAFE pin                                                                                |

|                      |                                                                                                          | FAULTN line is asserted                                                                                                                                                                  |                                                                                                          |                                                                        | CELL_OV_FAULTN_MS<br>K masks reaction on<br>FAULTN pin                                                                        |

| Cell                 | If a cell voltage raises above                                                                           | The CELL <x>_SEVERE_OV flag is set</x>                                                                                                                                                   | If a cell voltage falls below                                                                            | The charge FET is restored to the status defined by the CHG_ON bit     | VCELL <x>_EN masks<br/>measurement<br/>execution. The severe<br/>OV flag of a disabled<br/>cell can always be<br/>cleared</x> |

| severe<br>OV         | VCELL_SEVERE_OV_<br>TH, the severe OV fault<br>is acknowledged                                           | The charge FET is turned OFF                                                                                                                                                             | VCELL_SEVERE_OV_<br>TH, the cell severe OV<br>flag can be cleared by<br>MCU                              | FUSE pre-driver is disabled                                            | CELL_SEVERE_OV_P<br>RDRV_MSK masks<br>reaction on CHG pin                                                                     |

|                      |                                                                                                          | FUSE pre-driver is enabled                                                                                                                                                               |                                                                                                          | FAULTN line is released                                                | CELL_SEVERE_OV_F<br>USE_MSK masks<br>reaction on FUSE pin                                                                     |

DS14012 - Rev 5 page 16/63

| Fault<br>type        | Assertion condition                                                                                                | IC reaction to assertion                                                                                                                                                                 | Release condition                                                                                               | IC reaction to flag<br>clear                                                                | Maskable                                                                                                               |

|----------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Cell<br>severe<br>OV | If a cell voltage raises<br>above<br>VCELL_SEVERE_OV_<br>TH, the severe OV fault<br>is acknowledged                | FAULTN_SAFE is pulled low for  TFAULTN_SAFE_LOW (if a pulse on FAULTN_SAFE pin was not already generated after a previous not masked and not cleared Cell OV / Cell Severe OV detection) | If a cell voltage falls<br>below<br>VCELL_SEVERE_OV_<br>TH, the cell severe OV<br>flag can be cleared by<br>MCU | FAULTN line is released                                                                     | CELL_SEVERE_OV_R<br>ST_MSK masks<br>reaction FAULTN_SAFE<br>pin                                                        |

|                      |                                                                                                                    | FAULTN line is asserted                                                                                                                                                                  |                                                                                                                 |                                                                                             | CELL_SEVERE_OV_FA<br>ULTN_MSK masks<br>reaction on FAULTN pin                                                          |

| Cell                 | If a cell voltage falls<br>below<br>VCELL_BAL_UV_TH,<br>the corresponding Bal<br>UV counter is<br>incremented by 1 | The BAL <x>_UV flag is set</x>                                                                                                                                                           | If a cell voltage raises above VCELL_BAL_UV_TH, the corresponding Bal UV counter is decremented by 1.           | The Balancing FET is restored to the status defined by the corresponding BAL <x>_ON bit</x> | VCELL <x>_EN masks<br/>measurement<br/>execution. The Bal UV<br/>flag of a disabled cell<br/>can always be cleared</x> |

| balance<br>UV        | If the Bal UV counter reaches VCELL_BAL_UV_CNT_                                                                    | Any ongoing balancing is stopped on the affected cell, regardless of BAL <x>_ON bit</x>                                                                                                  | If the Bal UV counter reaches zero, the Bal                                                                     | FAULTN line is released                                                                     | BAL_UV_BAL_MSK<br>masks reaction on<br>balancing                                                                       |

|                      | TH, it saturates the Bal<br>UV fault is<br>acknowledged                                                            | FAULTN line is asserted                                                                                                                                                                  | UV flag can be cleared<br>by MCU                                                                                |                                                                                             | BAL_UV_FAULTN_MSK<br>masks reaction on<br>FAULTN pin                                                                   |

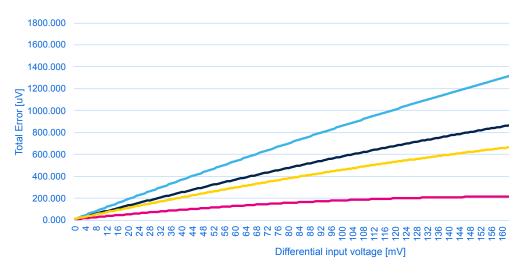

## 3.4.1.1 Electrical parameters

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: VB according to the operating range of Table 2;  $T_J$  according to the operating range of Table 5.

Table 11. Cell voltage monitor electrical parameters

| Symbol                    | Parameter                            | Test conditions                                                     | Min. | Тур.                           | Max. | Unit    |

|---------------------------|--------------------------------------|---------------------------------------------------------------------|------|--------------------------------|------|---------|

| V <sub>CELL_RANGE</sub>   | Cell voltage input measurement range | Design info                                                         | 1    |                                | 4.7  | V       |

| V <sub>CELL_RES</sub>     | Cell voltage measurement resolution  | Design info, effective range [0-5]V                                 |      | 1.22<br>(5 V/2 <sup>12</sup> ) |      | mV      |

| N <sub>BIT</sub>          | ADC bit number                       | Design info                                                         |      | 12                             |      | bit     |

| I <sub>CELL_LEAK</sub>    | Cx leakage current                   | ADC not converting                                                  |      |                                | 500  | nA      |

| V <sub>CELLERR1</sub>     | ADC total conversion error range 1   | 1 V ≤ V <sub>CELL</sub> < 1.5 V<br>-40 °C< T <sub>J</sub> <120 °C   | -25  |                                | 25   | mV      |

| V <sub>CELLERR2</sub>     | ADC total conversion error range 2   | 1.5 V ≤ V <sub>CELL</sub> ≤ 4.5 V<br>-40 °C< T <sub>J</sub> <105 °C | -15  |                                | 15   | mV      |

| V <sub>CELLERR3</sub>     | ADC total conversion error range 3   | 4.5 V ≤ V <sub>CELL</sub> ≤ 4.7 V<br>-40 °C< T <sub>J</sub> <120°C  | -25  |                                | 25   | mV      |

| V <sub>CELLERR4</sub>     | ADC total conversion error range 4   | 1.5 V ≤ VCELL ≤ 4.5<br>V<br>105 °C < T <sub>J</sub> < 120 °C        | -25  |                                | 25   | mV      |

| V <sub>CELL_NOISE</sub>   | Cell conversion noise                |                                                                     |      | 1                              |      | LSB rms |

| T <sub>CELL_FILTER1</sub> | Cell and VB acquisition filter time  |                                                                     |      | 0.8                            |      | ms      |

DS14012 - Rev 5 page 17/63

| Symbol                                    | Parameter                                                                                                                                                                                                                                                                | Test conditions | Min. | Тур.  | Max. | Unit   |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-------|------|--------|

| T <sub>CELL_FILTER2</sub>                 | Cell and VB acquisition filter time                                                                                                                                                                                                                                      |                 |      | 1.31  |      | ms     |

| T <sub>CELL_FILTER3</sub>                 | Cell and VB acquisition filter time                                                                                                                                                                                                                                      |                 |      | 4.38  |      | ms     |

| T <sub>CELL_FILTER4</sub>                 | Cell and VB acquisition filter time                                                                                                                                                                                                                                      |                 |      | 16.67 |      | ms     |

| V <sub>CELL_OV_TH</sub>                   | Programmable cell OV fault threshold (8 bit) $V_{CELL_{OV}} = 16V_{CELL_{RES}} * CODE$                                                                                                                                                                                   |                 | 0    |       | 5    | V      |

| N <sub>CELL_OV_CNT_TH</sub>               | Programmable cell OV event counter threshold (4 bit)                                                                                                                                                                                                                     |                 | 1    |       | 15   | events |

| V <sub>CELL_</sub> SEVERE_OV<br>_DELTA_TH | Programmable cell severe OV threshold (positive delta in respect to cell OV threshold, 8 bit) $V_{CELL_{SEVEREOV_{TH}}} = V_{CELL_{OV_{TH}}} + 16V_{CELL_{RES}*CODE}$ In case of overflow, the $V_{CELL_{SEVEREOV_{TH}}}$ is saturated to the max. specified value       |                 | 0    |       | 5    | V      |

| V <sub>CELL_UV_TH</sub>                   | Programmable cell UV fault threshold (8 bit) $V_{CELL_{UV}} = 16 V_{CELL_{RES}} * CODE$                                                                                                                                                                                  |                 | 0    |       | 5    | V      |

| N <sub>CELL_UV_CNT_TH</sub>               | Programmable cell UV event counter threshold (4 bit)                                                                                                                                                                                                                     |                 | 1    |       | 15   | events |

| V <sub>CELL_</sub> SEVERE_UV<br>_DELTA_TH | Programmable cell severe OV threshold (negative delta in respect to cell UV threshold, 8 bit) $V_{CELL_{SEVERE}UV_{TH}} = V_{CELL}UV_{TH} - 16V_{CELL_{RE}} CODE$ In case of underflow, the $V_{CELL_{SEVERE}UV_{TH}}$ is saturated to the min. specified value          |                 | 0    |       | 5    | V      |

| V <sub>CELL_BAL_UV_DE</sub>               | Programmable balancing UV threshold (positive delta in respect to cell UV threshold, 8 bit) $V_{CELL_{BAL_{UV_{TH}}}} = V_{CELL_{UV_{TH}}} \\ + 16V_{CELL_{RES}} * CODE$ In case of overflow, the $V_{CELL_{SEVERE_{UV_{TH}}}}$ is saturated to the max. specified value |                 | 0    |       | 5    | V      |

| N <sub>CELL_BAL_UV_CN</sub><br>T_TH       | Programmable balance UV event counter threshold (4 bit)                                                                                                                                                                                                                  |                 | 1    |       | 15   | events |

## 3.4.2 Battery stack monitor (VB)

The battery stack monitor, (VB), of the voltage conversion routine monitors the battery stack voltage measuring the VB pin through an internal divider.

This function is enabled by programming the corresponding VB\_EN I<sup>2</sup>C bit: if disabled, this step is skipped. To limit power consumption, the internal voltage divider is connected to VB pin at the beginning of the Section 3.4 Voltage conversion routine and it is disconnected right after the VB measurement step is completed.

Stack voltage measurements are stored in the VB\_MEAS register and compared to programmable thresholds in order to detect the failures listed in Table 12.

Table 12. Battery stack monitor diagnostics

| Fault type                            | Assertion condition                                                                               | IC reaction to assertion                            | Release condition                                                                                  | IC reaction to flag<br>clear                                                               | Maskable                                                                                                                        |

|---------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                                       | If VB voltage falls<br>below VB_UV_TH,<br>the corresponding UV<br>counter is<br>incremented by 1  | The VB_UV flag is set                               | If VB voltage raises<br>above VB_UV_TH,<br>the corresponding UV<br>counter is<br>decremented by 1. | The discharge FET is restored to the status defined by the DCHG_ON bit                     | VB_EN masks<br>measurement<br>execution. When<br>disabled, the VB_UV<br>flag can always be<br>cleared upon read                 |

| VB UV                                 | If the UV counter reaches VB_UV_CNT_TH, it                                                        | The discharge FET is turned OFF                     | If the UV counter reaches zero, the                                                                | FAULTN line is                                                                             | VB_UV_PRDRV_MS<br>K masks reaction on<br>DCHG pin                                                                               |

|                                       | saturates and the VB<br>UV fault is<br>acknowledged                                               | FAULTN line is asserted                             | VB_UV flag can be cleared by MCU                                                                   | released                                                                                   | VB_UV_FAULTN_MS<br>K masks reaction on<br>FAULTN pin                                                                            |

|                                       | If VB voltage raises<br>above VB_OV_TH,<br>the corresponding OV<br>counter is<br>incremented by 1 | The VB_OV flag is set                               | If VB voltage falls<br>below VB_OV_TH,<br>the corresponding OV<br>counter is<br>decremented by 1.  | The charge FET is restored to the status defined by the corresponding I <sup>2</sup> C bit | VB_EN masks<br>measurement<br>execution. When<br>disabled, the VB_OV<br>flag can always be<br>cleared upon read                 |

| VB OV                                 | If the OV counter                                                                                 | The charge FET is turned OFF                        |                                                                                                    |                                                                                            | VB_OV_PRDRV_MS<br>K masks reaction on<br>CHG pin                                                                                |

|                                       | reaches VB_OV_CNT_TH, it saturates and the VB OV fault is acknowledged                            | FAULTN_SAFE is pulled low for TFAULTN_SAFE_LOW      | If the OV counter<br>reaches zero, the VB<br>OV flag can be<br>cleared by MCU                      | FAULTN line is released                                                                    | VB_OV_RST_MSK<br>masks reaction<br>FAULTN_SAFE pin                                                                              |

|                                       |                                                                                                   | FAULTN line is asserted                             |                                                                                                    |                                                                                            | VB_OV_FAULTN_MS<br>K masks reaction on<br>FAULTN pin                                                                            |

|                                       | If the absolute value                                                                             | The VB_SUM_CHECK_F AIL flag is set                  | If the absolute value of the difference                                                            | The charge FET is restored to the status defined by the CHG_ON bit                         | VB_EN masks<br>measurement<br>execution. When<br>disabled, the<br>VB_SUM_CHECK_F<br>AIL flag can always<br>be cleared upon read |

| VB vs. sum of cells plausibility fail | of the difference<br>between VB_MEAS<br>and VCELL_SUM is<br>greater than<br>VB_VSUM_MAX_DIF       | Both charge and<br>Discharge FETs are<br>turned OFF | between VB_MEAS<br>and VCELL_SUM<br>falls below the<br>VB_VSUM_MAX_DIF                             | The discharge FET is restored to the status defined by the DCHG_ON bit                     | VB_SUM_CHEC_PR<br>DRV_MSK masks<br>reaction on CHG/<br>DCHG pins                                                                |

|                                       | F_TH, the plausibility check fail is acknowledged                                                 | Balancing is interrupted on all cells               | F_TH, the VB_SUM_CHECK_F AIL flag can be cleared by MCU                                            | FUSE pre-driver is disabled                                                                | VB_SUM_CHEC_FU<br>SE_MSK masks<br>reaction on FUSE pin                                                                          |

|                                       |                                                                                                   | FUSE pre-driver is enabled                          |                                                                                                    | Balancing FETs are restored to the status defined by the corresponding BAL <x>_ON bit</x>  | VB_SUM_CHEC_BA<br>L_MSK masks<br>reaction on balancing                                                                          |

DS14012 - Rev 5 page 19/63

| Fault type                               | Assertion condition                                                                                                                                    | IC reaction to assertion | Release condition                                                                                                                                           | IC reaction to flag<br>clear | Maskable                                                       |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------------------------------|

| VB vs. sum of cells<br>plausibility fail | If the absolute value of the difference between VB_MEAS and VCELL_SUM is greater than VB_VSUM_MAX_DIFF_TH, the plausibility check fail is acknowledged | FAULTN line is asserted  | If the absolute value of the difference between VB_MEAS and VCELL_SUM falls below the VB_VSUM_MAX_DIFF_TH, the VB_SUM_CHECK_FAIL flag can be cleared by MCU | FAULTN line is released      | VB_SUM_CHECK_F<br>AULTN_MSK masks<br>reaction on FAULTN<br>pin |

#### 3.4.2.1 Electrical parameters

All parameters are tested and guaranteed in the following conditions, unless otherwise noted: VB according to the operating range of Table 2; T<sub>J</sub> according to the operating range of Table 5.

Table 13. Battery stack monitor external parameters

| Symbol                    | Parameter                                                                          | Test conditions                                                     | Min. | Тур.                        | Max. | Unit   |

|---------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|-----------------------------|------|--------|

| V <sub>B_</sub> RANGE     | VB voltage input measurement range                                                 | Design info                                                         | 4.3  |                             | 25   | V      |

| V <sub>B_RES</sub>        | VB voltage measurement resolution                                                  | Design info                                                         |      | 6.1 (25 V/2 <sup>12</sup> ) |      | mV     |

| N <sub>BIT</sub>          | ADC bit number                                                                     | Design info                                                         |      | 12                          |      | bit    |

| V <sub>BERR_1</sub>       | VB voltage measurement total                                                       | 4.3 V <vb<7.5 v<br="">-40 °C&lt; T<sub>J</sub>&lt;105 °C</vb<7.5>   | -150 |                             | 150  | mV     |

| V <sub>BERR_2</sub>       | VB voltage measurement total                                                       | 7.5 V <vb<22.5 v<br="">-40 °C&lt; T<sub>J</sub>&lt;105 °C</vb<22.5> | -100 |                             | 100  | mV     |

| V <sub>BERR_3</sub>       | VB voltage measurement total                                                       | 22.5 V <vb<25 v<br="">-40 °C&lt; T<sub>J</sub>&lt;105 °C</vb<25>    | -150 |                             | 150  | mV     |

| V <sub>В_ОV_ТН</sub>      | Programmable VB OV fault threshold (8 bit) $V_{BOV_{TH}} = 16V_{B\_RES} * CODE$    | Tested by SCAN                                                      | 0    |                             | 25   | V      |

| N <sub>VB_OV_CNT_TH</sub> | Programmable VB OV event counter threshold (4 bit)                                 | Tested by SCAN                                                      | 1    |                             | 15   | events |

| V <sub>B_UV_TH</sub>      | Programmable VB UV fault threshold (8 bit) $V_{B_{UV_{TH}}} = 16V_{B\_RES} * CODE$ | Tested by SCAN                                                      | 0    |                             | 25   | V      |

| N <sub>VB_UV_CNT_TH</sub> | Programmable VB UV event counter threshold (4 bit)                                 | Tested by SCAN                                                      | 1    |                             | 15   | events |

| VB_SUM_MAX_DIFF_TH        | Programmable plausibility check threshold between VB and sum of cells (8 bit)      | Tested by SCAN                                                      | 0    |                             | 25   | V      |

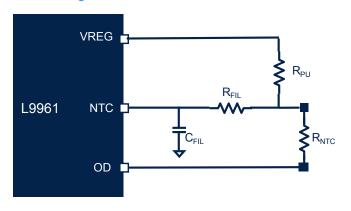

#### 3.4.3 Cell temperature monitor (NTC)

The NTC cell temperature monitoring voltage conversion routine monitors pack temperature by sensing the NTC pin. This function is enabled by programming the NTC\_EN bit: if disabled, no conversion occurs.

When NTC\_EN = 1, the OD open-drain is switched ON at the beginning of the voltage conversion routine, prior to the cells step execution. This allows voltage on the NTC pin to settle before NTC acquisition is performed. Once the NTC is completed, the OD open-drain switch is released, reducing overall current consumption from VREG.

DS14012 - Rev 5 page 20/63

NTC measurements are stored in the NTC\_MEAS register and are compared to programmable thresholds in order to detect the failures listed in Table 14.

Table 14. NTC temperature monitor diagnostics