# 16-Channel Low-Harmonic-Distortion High-Voltage Analog Switch with Bleed Resistors

#### **Features**

- · Low Harmonic Distortion

- · Integrated Bleed Resistors on the Outputs

- · 3.3V or 5.5V CMOS Input Logic Level

- 20 MHz Data Shift Clock Frequency

- -10 µA Low-quiescent Power Dissipation

- · Low Parasitic Capacitance

- DC to 50 MHz Small-signal Frequency Response

- · CMOS Logic Circuitry for Low Power

- · Excellent Noise Immunity

- · Cascadable Serial Data Register with Latches

- · Flexible Operating Supply Voltages

#### **Applications**

- Medical Ultrasound Imaging

- · Non-destructive Testing Metal Flaw Detection

- Piezoelectric Transducer Drivers

- · Optical MEMS Modules

#### **General Description**

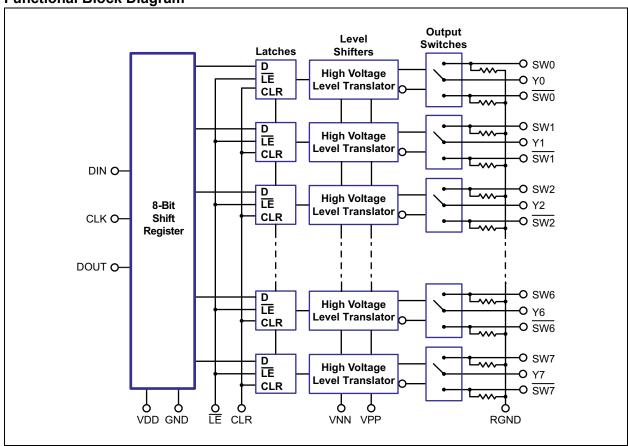

The HV2733 is a low-charge injection, 16-channel, low-harmonic-distortion, high-voltage analog switch integrated circuit (IC) intended for applications requiring high-voltage switching controlled by low-voltage control signals such as medical ultrasound imaging, piezoelectric transducer drivers, and printers. The bleed resistors eliminate voltage built up on capacitive loads such as piezoelectric transducers.

The outputs are configured as single-pole double-throw analog switches. Data are shifted into an 8-bit Shift register using an external clock. The  $\overline{LE}$  latches the Shift register data into the individual switch latches. A logic high connects a switch common YX to SWX. On the other hand, a logic low connects YX to SWX. A logic high in CLR resets all switches to SWX simultaneously.

To reduce any possible clock feed-through noise, the latch enable bar (LE) should be left high until all bits are clocked in. Data are clocked in during the rising edge of the clock. The HV2733 combines high-voltage bilateral DMOS switches and low-power CMOS logic to provide efficient control of high-voltage analog signals.

#### **Functional Block Diagram**

#### 1.0 ELECTRICAL CHARACTERISTICS

### Absolute Maximum Ratings(†)

| Logic Power Supply Voltage, V <sub>DD</sub>                   | –0.5V to +7V         |

|---------------------------------------------------------------|----------------------|

| Differential Supply Voltage, V <sub>PP</sub> -V <sub>NN</sub> | 220V                 |

| High-voltage Positive Supply, V <sub>PP</sub>                 | –0.5V to +200V       |

| High-voltage Negative Supply, V <sub>NN</sub>                 | +0.5V to –200V       |

| Logic Input Voltage                                           |                      |

| Analog Signal Range, V <sub>SIG</sub>                         | $V_{NN}$ to $V_{PP}$ |

| Peak Analog Signal Current/Channel                            |                      |

| Storage Temperature, T <sub>S</sub>                           |                      |

| Power Dissipation:                                            |                      |

| 48-lead LQFP                                                  | 1W                   |

|                                                               |                      |

Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

| Parameter                          | Sym.             | Min.                 | Тур. | Max.                 | Unit | Conditions     |

|------------------------------------|------------------|----------------------|------|----------------------|------|----------------|

| Logic Power Supply Voltage         | $V_{DD}$         | 3                    | _    | 5.5                  | V    | Note 1, Note 3 |

| High-voltage Positive Supply       | $V_{PP}$         | +40                  | _    | V <sub>NN</sub> +200 | V    | Note 1, Note 3 |

| High-voltage Negative Supply       | V <sub>NN</sub>  | -40                  | _    | -160                 | V    | Note 1, Note 3 |

| High-level Input Voltage           | V <sub>IH</sub>  | 0.9 V <sub>DD</sub>  | _    | $V_{DD}$             | V    |                |

| Low-level Input Voltage            | $V_{IL}$         | 0                    | _    | 0.1 V <sub>DD</sub>  | V    |                |

| Analog Signal Voltage Peak-to-peak | V <sub>SIG</sub> | V <sub>NN</sub> +10V | _    | V <sub>PP</sub> –10V | V    | Note 2         |

| Operating Ambient Temperature      | T <sub>A</sub>   | 0                    | _    | 70                   | °C   |                |

- Note 1: Power-up/down sequence is arbitrary except GND must be powered up first and powered down last.

- 2:  $V_{SIG}$  must be  $V_{NN} \le V_{SIG} \le V_{PP}$  or floating during power-up/down transition.

- 3: Rise and fall times of power supplies  $V_{DD},\,V_{PP}$  and  $V_{NN}$  should not be less than 1 millisecond.

# DC ELECTRICAL CHARACTERISTICS

| Electrical Specification                      | is: Unles         |      |      |      |       |      |      |      | ating co | onditions.                                                                    |  |  |

|-----------------------------------------------|-------------------|------|------|------|-------|------|------|------|----------|-------------------------------------------------------------------------------|--|--|

| Parameter                                     | Sum               | 0    | °C   |      | +25°C | ;    | +7   | 0°C  |          |                                                                               |  |  |

| Parameter                                     | Sym.              | Min. | Max. | Min. | Тур.  | Max. | Min. | Max. | Unit     | Conditions                                                                    |  |  |

|                                               |                   | _    | 30   | _    | 26    | 38   | _    | 48   |          | $I_{SIG} = 5 \text{ mA}$ $V_{PP} = +40 \text{V}$                              |  |  |

|                                               |                   | _    | 25   | _    | 22    | 27   | _    | 32   |          | I <sub>SIG</sub> = 200 mA V <sub>NN</sub> = -160                              |  |  |

| Small Signal Switch                           | D                 | _    | 25   | _    | 22    | 27   | _    | 30   | Ω        | $I_{SIG} = 5 \text{ mA}$ $V_{PP} = +100^{\circ}$                              |  |  |

| On-resistance                                 | R <sub>ONS</sub>  | _    | 18   | _    | 18    | 24   | _    | 27   | 12       | $I_{SIG} = 200 \text{ mA}$ $V_{NN} = -100$                                    |  |  |

|                                               |                   | _    | 23   | _    | 20    | 25   | —    | 30   |          | $I_{SIG} = 5 \text{ mA}$ $V_{PP} = +160^{\circ}$                              |  |  |

|                                               |                   |      | 22   | _    | 16    | 25   | _    | 27   |          | $I_{SIG} = 200 \text{ mA}  V_{NN} = -40 \text{ V}$                            |  |  |

| Small Signal Switch<br>On-resistance Matching | ΔR <sub>ONS</sub> |      | 20   | _    | 5     | 20   | _    | 20   | %        | $I_{SIG}$ = 5 mA, $V_{PP}$ = +100V, $V_{NN}$ = -100V                          |  |  |

| Large Signal Switch<br>On-resistance          | R <sub>ONL</sub>  | _    | _    | _    | 15    | _    | _    | _    | Ω        | $V_{SIG} = V_{PP} - 10V$ , $I_{SIG} = 1A$                                     |  |  |

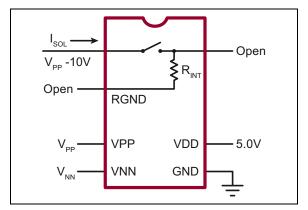

| Output Switch Shunt<br>Resistance             | R <sub>INT</sub>  | _    | _    | 35   | 50    | 65   | _    | _    | kΩ       | Output switch to R <sub>GND</sub><br>I <sub>RINT</sub> = 0.5 mA               |  |  |

| Switch-off Leakage per<br>Switch              | I <sub>SOL</sub>  | _    | 5    | _    | 1     | 10   | _    | 15   | μA       | $V_{SIG} = V_{PP}-10V$ and $V_{NN}+10V$                                       |  |  |

| DC Offset Switch Off                          | Vos               | _    | 50   | _    |       | 50   | _    | 50   | mV       | No load, R <sub>GND</sub> = 0V                                                |  |  |

| DC Offset Switch On                           | vos               | _    | 50   | _    | _     | 50   | _    | 50   | mV       | No load, R <sub>GND</sub> = 0V                                                |  |  |

| V <sub>PP</sub> Supply Quiescent<br>Current   | I <sub>PPQ</sub>  | _    | _    | _    | 10    | 50   | _    | _    | μA       | All switches off                                                              |  |  |

| V <sub>NN</sub> Supply Quiescent<br>Current   | I <sub>NNQ</sub>  | _    | _    | _    | -10   | -50  | _    | _    | μA       | All switches off                                                              |  |  |

| V <sub>PP</sub> Supply Quiescent<br>Current   | I <sub>PPQ</sub>  |      |      | _    | 10    | 50   | _    |      | μΑ       | All switches on, I <sub>SW</sub> = 5 mA                                       |  |  |

| V <sub>NN</sub> Supply Quiescent<br>Current   | I <sub>NNQ</sub>  | _    | _    | _    | -10   | -50  | _    | _    | μA       | All switches on, I <sub>SW</sub> = 5 mA                                       |  |  |

| Switch Output Peak<br>Current                 | I <sub>SW</sub>   |      | 2    | _    | 1     | 2    |      | 2    | Α        | V <sub>SIG</sub> duty cycle < 0.1%,<br>pulse width ≤1 μs                      |  |  |

| Output Switching<br>Frequency                 | f <sub>SW</sub>   |      | _    | _    | 1     | 50   |      |      | kHz      | Duty cycle = 50%                                                              |  |  |

|                                               |                   | _    | 5.2  | _    | _     | 5.6  | _    | 6.4  |          | $V_{PP} = +40V$<br>$V_{NN} = -160V$ All output                                |  |  |

| Average V <sub>PP</sub> Supply<br>Current     | I <sub>PP</sub>   | _    | 3.2  | _    | _     | 4.5  |      | 4.5  | mA       | $V_{PP}$ = +100V switches tur<br>$V_{NN}$ = -100V on and off a<br>50 kHz with |  |  |

|                                               |                   | _    | 3.2  | _    | _     | 4    | _    | 4.5  |          | $V_{PP} = +160V$ no load. $V_{NN} = -40V$                                     |  |  |

|                                               |                   | _    | 5.2  | _    | _     | 5.6  | _    | 6.4  |          | $V_{PP} = +40V$ $V_{NN} = -160V$ All output switches tur                      |  |  |

| Average V <sub>NN</sub> Supply<br>Current     | I <sub>NN</sub>   | _    | 3.2  | _    | _     | 4    | _    | 4.5  | mA       | $V_{\text{NN}} = +100V$ on and off a 50 kHz with                              |  |  |

|                                               |                   | _    | 3.2  | _    | _     | 4    | _    | 4.5  |          | $V_{PP} = +160V$ no load.                                                     |  |  |

| Logic Supply Average<br>Current               | I <sub>DD</sub>   | _    | 2    |      | _     | 2    | _    | 2    | mA       | f <sub>CLK</sub> = 5 MHz, V <sub>DD</sub> = 5V                                |  |  |

| Logic Supply Quiescent<br>Current             | I <sub>DDQ</sub>  | _    | 10   | _    | _     | 10   | _    | 10   | μA       | All logic inputs are static                                                   |  |  |

| Data Out Source<br>Current                    | I <sub>SOR</sub>  | 0.45 | _    | 0.45 | 0.7   |      | 0.4  | _    | mA       | $V_{OUT} = V_{DD} - 0.7V$                                                     |  |  |

# DC ELECTRICAL CHARACTERISTICS (CONTINUED)

| <b>Electrical Specification</b> | Electrical Specifications: Unless otherwise specified, all values are over operating conditions. |      |      |       |      |      |       |      |      |                         |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------------|------|------|-------|------|------|-------|------|------|-------------------------|--|--|

| Parameter                       |                                                                                                  | 0°C  |      | +25°C |      |      | +70°C |      |      |                         |  |  |

|                                 | Sym.                                                                                             | Min. | Max. | Min.  | Тур. | Max. | Min.  | Max. | Unit | Conditions              |  |  |

| Data Out Sink Current           | I <sub>SINK</sub>                                                                                | 0.45 | _    | 0.45  | 0.7  | _    | 0.4   | _    | mA   | V <sub>OUT</sub> = 0.7V |  |  |

| Logic Input Capacitance         | C <sub>IN</sub>                                                                                  | _    | 10   | _     | _    | 10   | _     | 10   | pF   |                         |  |  |

### **AC ELECTRICAL CHARACTERISTICS**

**Electrical Specifications:** Over operating conditions,  $V_{DD}$  = 5V,  $t_R$  =  $t_F \le 5$  ns, 50% duty cycle,  $C_{LOAD}$  = 20 pF unless otherwise specified.

| uniess onerwise specified.               |                                 | 0    | °C   |      | +25°C |      | +70  | 0°C  |      |                                                               |

|------------------------------------------|---------------------------------|------|------|------|-------|------|------|------|------|---------------------------------------------------------------|

| Parameter                                | Sym.                            | Min. | Max. | Min. | Тур.  | Max. | Min. | Max. | Unit | Conditions                                                    |

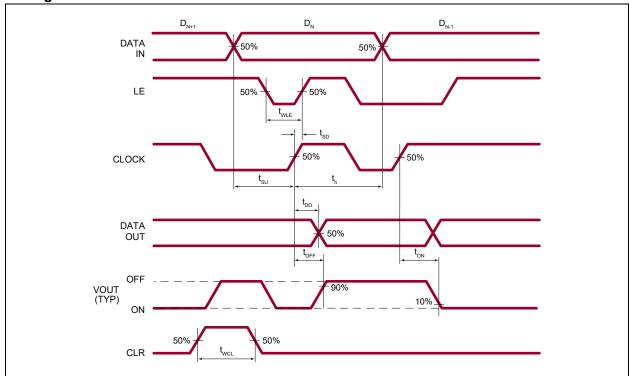

| Set-up Time before LE Rises              | t <sub>SD</sub>                 | 25   | _    | 25   | _     |      | 25   | _    | ns   |                                                               |

| Time Width of LE                         | t <sub>WLE</sub>                | 12   | _    | _    | 12    | _    | 12   | _    | ns   | V <sub>DD</sub> = 5V                                          |

| Clock Delay Time to Data Out             | t <sub>DO</sub>                 | 15   | 40   | 15   | 30    | 40   | 15   | 40   | ns   | V <sub>DD</sub> = 5V                                          |

| Time Width of CLR                        | t <sub>WCL</sub>                | 55   | _    | 55   | _     | _    | 55   | _    | ns   |                                                               |

| Set-up Time Data to Clock                | t <sub>SU</sub>                 | 7    | 1    | _    | 7     | 1    | 7    | _    | ns   | V <sub>DD</sub> = 5V                                          |

| Hold Time Data from Clock                | t <sub>H</sub>                  | 2    |      | 2    | _     |      | 2    | _    | ns   |                                                               |

| Clock Frequency                          | f <sub>CLK</sub>                | _    | 20   | _    | 1     | 20   | 1    | 20   | MHz  | 50% duty cycle,<br>f <sub>DATA</sub> = f <sub>CLK</sub> /2    |

| Clock Rise and Fall Times                | t <sub>r</sub> , t <sub>f</sub> | _    | 50   | _    |       | 50   |      | 50   | ns   |                                                               |

| Turn-on Time                             | t <sub>ON</sub>                 | _    | 5    |      | 1     | 5    | 1    | 5    | μs   | $V_{SIG} = V_{PP} - 10V$ ,<br>$R_{LOAD} = 10 \text{ k}\Omega$ |

| Turn-off Time                            | t <sub>OFF</sub>                | _    | 5    | _    | 1     | 5    |      | 5    | μs   | $V_{SIG} = V_{PP} - 10V$ ,<br>$R_{LOAD} = 10 \text{ k}\Omega$ |

|                                          |                                 | _    | 20   | _    |       | 20   |      | 20   |      | $V_{PP} = +40V,$<br>$V_{NN} = -160V$                          |

| Maximun V <sub>SIG</sub> Slew Rate       | dv/dt                           | _    | 20   | _    | _     | 20   | _    | 20   | V/ns | $V_{PP} = +100V,$<br>$V_{NN} = -100V$                         |

|                                          |                                 | _    | 20   | _    | _     | 20   | _    | 20   |      | V <sub>PP</sub> = +160V,<br>V <sub>NN</sub> = -40V            |

| Off lealation                            |                                 | -30  |      | -30  | -33   |      | -30  | _    | dB   | f=5MHz,<br>1 kΩ//15 pF load                                   |

| Off Isolation                            | K <sub>O</sub>                  | -58  | ı    | -58  |       |      | -58  | _    | В    | f = 5 MHz,<br>50Ω load                                        |

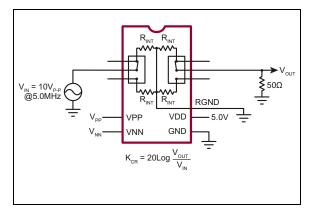

| Switch Crosstalk                         | K <sub>CR</sub>                 | -60  |      | -60  | -70   |      | -60  | _    | dB   | f = 5 MHz,<br>50Ω load                                        |

| Output Switch Isolation Diode<br>Current | I <sub>ID</sub>                 | _    | 300  | _    | _     | 300  | _    | 300  | mA   | 300 ns pulse<br>width, 2% duty<br>cycle                       |

| Off Capacitance SW to GND                | C <sub>SG(OFF)</sub>            | 5    | 17   | 5    | 12    | 17   | 5    | 17   | pF   | 0V, f = 1 MHz                                                 |

| On Capacitance SW to GND                 | C <sub>SG(ON)</sub>             | 25   | 50   | 25   | 38    | 50   | 25   | 50   | pF   | 0V, f = 1 MHz                                                 |

# **AC ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Specifications:** Over operating conditions,  $V_{DD}$  = 5V,  $t_R$  =  $t_F$  ≤ 5 ns, 50% duty cycle,  $C_{LOAD}$  = 20 pF unless otherwise specified.

|                      |                   | 0    | °C   | +25°C |      |      | +70°C |      |      |                                             |  |

|----------------------|-------------------|------|------|-------|------|------|-------|------|------|---------------------------------------------|--|

| Parameter            | Sym.              | Min. | Max. | Min.  | Тур. | Max. | Min.  | Max. | Unit | Conditions                                  |  |

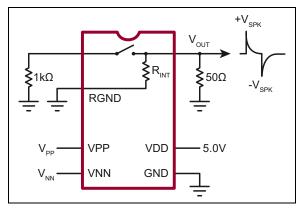

|                      | +V <sub>SPK</sub> | _    | _    | _     | _    | 150  |       | _    |      | V <sub>PP</sub> = +40V,                     |  |

|                      | -V <sub>SPK</sub> |      | _    | _     | _    | 150  |       |      | mV   | $V_{NN} = -160V,$ $R_{LOAD} = 50\Omega$     |  |

|                      | +V <sub>SPK</sub> | _    | _    |       | _    | 150  |       | _    |      | V <sub>PP</sub> = +100V,                    |  |

| Output Voltage Spike | -V <sub>SPK</sub> | _    | _    | _     | _    | 150  | 1     | _    | mV   | $V_{NN} = -100V$ ,<br>$R_{LOAD} = 50\Omega$ |  |

|                      | +V <sub>SPK</sub> | _    | _    | _     | _    | 150  |       | _    |      | V <sub>PP</sub> = +160V,                    |  |

|                      | -V <sub>SPK</sub> | _    | _    | _     | _    | 150  | _     | _    | mV   | $V_{NN} = -40V$ ,<br>$R_{LOAD} = 50\Omega$  |  |

#### **TEMPERATURE SPECIFICATIONS**

| Parameter                     | Sym.           | Min. | Тур. | Max. | Unit | Conditions |

|-------------------------------|----------------|------|------|------|------|------------|

| TEMPERATURE RANGE             |                |      |      |      |      |            |

| Operating Ambient Temperature | T <sub>A</sub> | 0    | _    | 70   | °C   |            |

| Storage Temperature           | T <sub>S</sub> | -65  | _    | +150 | °C   |            |

| PACKAGE THERMAL RESISTANCE    |                |      |      |      |      |            |

| 48-lead LQFP                  | $\theta_{JA}$  | _    | 52   | _    | °C/W |            |

# **Timing Waveforms**

#### TRUTH FUNCTION TABLE

| D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | LE | CLR | Y0                  | Y1  | Y2  | Y3  | Y4  | Y5  | Y6  | <b>Y</b> 7 |

|----|----|----|----|----|----|----|----|----|-----|---------------------|-----|-----|-----|-----|-----|-----|------------|

| L  |    |    |    |    |    |    |    | L  | L   | SW0                 |     |     |     |     |     |     |            |

| Н  |    |    |    |    |    |    |    | L  | L   | SW0                 |     |     |     |     |     |     |            |

|    | L  |    |    |    |    |    |    | L  | L   |                     | SW1 |     |     |     |     |     |            |

|    | Н  |    |    |    |    |    |    | L  | L   |                     | SW1 |     |     |     |     |     |            |

|    |    | L  |    |    |    |    |    | L  | L   |                     |     | SW2 |     |     |     |     |            |

|    |    | Н  |    |    |    |    |    | L  | L   |                     |     | SW2 |     |     |     |     |            |

|    |    |    | L  |    |    |    |    | L  | L   |                     |     |     | SW3 |     |     |     |            |

|    |    |    | Н  |    |    |    |    | L  | L   |                     |     |     | SW3 |     |     |     |            |

|    |    |    |    | L  |    |    |    | L  | L   |                     |     |     |     | SW4 |     |     |            |

|    |    |    |    | Н  |    |    |    | L  | L   |                     |     |     |     | SW4 |     |     |            |

|    |    |    |    |    | L  |    |    | L  | L   |                     |     |     |     |     | SW5 |     |            |

|    |    |    |    |    | Н  |    |    | L  | L   |                     |     |     |     |     | SW5 |     |            |

|    |    |    |    |    |    | L  |    | L  | L   |                     |     |     |     |     |     | SW6 |            |

|    |    |    |    |    |    | Н  |    | L  | L   |                     |     |     |     |     |     | SW6 |            |

|    |    |    |    |    |    |    | L  | L  | L   |                     |     |     |     |     |     |     | SW7        |

|    |    |    |    |    |    |    | Н  | L  | L   |                     |     |     |     |     |     |     | SW7        |

| X  | Х  | Х  | Х  | Х  | X  | X  | Х  | Н  | L   | HOLD PREVIOUS STATE |     |     |     |     |     |     |            |

| X  | Х  | Х  | X  | X  | X  | X  | X  | Х  | Н   | SW0                 | SW1 | SW2 | SW3 | SW4 | SW5 | SW6 | SW7        |

Note 1: Serial data is clocked in on the L to H transition clock.

- 2: All switches go to a state retaining their present condition at the rising edge of  $\overline{LE}$ .

- **3:** When  $\overline{LE}$  is low, the Shift register data flow through the latch.

- **4:** D<sub>OUT</sub> is high when data in the Shift register 7 is high.

- **5**: Shift register clocking has no effect on the switch states if  $\overline{LE}$  is high.

- **6:** The CLR clear input overrides all other inputs.

#### 2.0 PIN DESCRIPTION

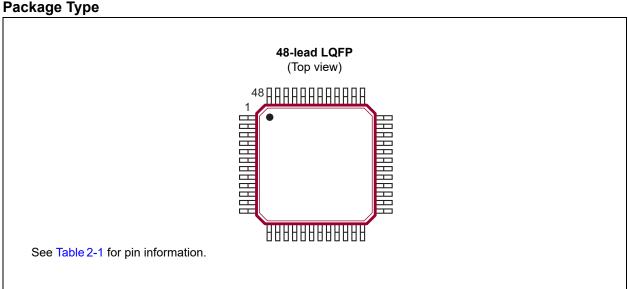

The description of pins in HV2733 are listed in Table 2-1. Refer to **Package Type** for the location of pins.

TABLE 2-1: PIN FUNCTION TABLE

| Pin Number | Pin Name | Description                    |

|------------|----------|--------------------------------|

| 1          | SW0      | SW terminal of analog switch 0 |

| 2          | Y0       | Y terminal of analog switch 0  |

| 3          | SW0      | SW terminal of analog switch 0 |

| 4          | NC       | No connection                  |

| 5          | SW1      | SW terminal of analog switch 1 |

| 6          | Y1       | Y terminal of analog switch 1  |

| 7          | SW1      | SW terminal of analog switch 1 |

| 8          | NC       | No connection                  |

| 9          | SW2      | SW terminal of analog switch 2 |

| 10         | Y2       | Y terminal of analog switch 2  |

| 11         | SW2      | SW terminal of analog switch 2 |

| 12         | NC       | No connection                  |

| 13         | SW3      | SW terminal of analog switch 3 |

| 14         | Y3       | Y terminal of analog switch 3  |

| 15         | SW3      | SW terminal of analog switch 3 |

| 16         | NC       | No connection                  |

| 17         | VNN      | High-voltage negative supply   |

| 18         | NC       | No connection                  |

| 19         | NC       | No connection                  |

| 20         | VPP      | High-voltage positive supply   |

| 21         | NC       | No connection                  |

| 22         | SW4      | SW terminal of analog switch 4 |

| 23         | Y4       | Y terminal of analog switch 4  |

| 24         | SW4      | SW terminal of analog switch 4 |

| 25         | NC       | No connection                  |

| 26         | SW5      | SW terminal of analog switch 5 |

| 27         | Y5       | Y terminal of analog switch 5  |

| 28         | SW5      | SW terminal of analog switch 5 |

| 29         | NC       | No connection                  |

| 30         | SW6      | SW terminal of analog switch 6 |

| 31         | Y6       | Y terminal of analog switch 6  |

| 32         | SW6      | SW terminal of analog switch 6 |

| 33         | NC       | No connection                  |

| 34         | SW7      | SW terminal of analog switch 7 |

| 35         | Y7       | Y terminal of analog switch 7  |

| 36         | SW7      | SW terminal of analog switch 7 |

| 37         | RGND     | Ground for bleed resistor      |

# HV2733

# TABLE 2-1: PIN FUNCTION TABLE (CONTINUED)

| Pin Number | Pin Name | Description                           |

|------------|----------|---------------------------------------|

| 38         | GND      | Ground                                |

| 39         | VDD      | Logic supply voltage                  |

| 40         | DOUT     | Data out logic output                 |

| 41         | NC       | No connection                         |

| 42         | NC       | No connection                         |

| 43         | NC       | No connection                         |

| 44         | CLR      | Latch clear logic input               |

| 45         | ĪĒ       | Latch enable logic input, low active  |

| 46         | CLK      | Clock logic input for shift registers |

| 47         | DIN      | Data in logic input                   |

| 48         | RGND     | Ground for bleed resistor             |

#### 3.0 FUNCTIONAL DESCRIPTION

#### 3.1 Test Circuits

Figure 3-1 to Figure 3-7 show the test circuits for HV2733.

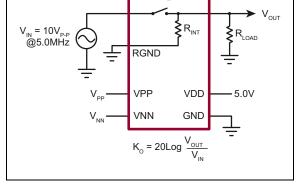

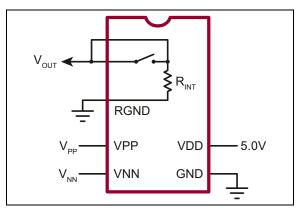

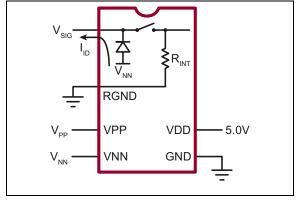

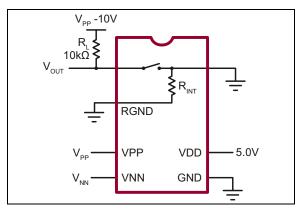

FIGURE 3-1: Switch Off Leakage.

FIGURE 3-4: Off Isolation.

FIGURE 3-2: DC Offset On/Off.

FIGURE 3-5: Isolation Diode Current.

**FIGURE 3-3:**  $T_{ON}/T_{OFF}$  Test Circuit.

FIGURE 3-6: Crosstalk.

FIGURE 3-7: Output Voltage Spike.

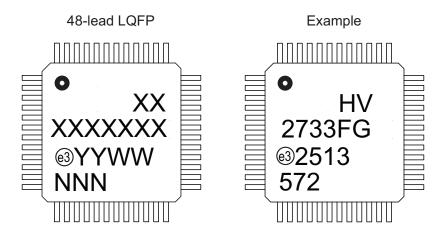

#### 4.0 PACKAGE MARKING INFORMATION

#### 4.1 Package Marking Information

Legend:XX...XProduct Code or Customer-specific informationYYear code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

e3 Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for product code or customer-specific information. Package may or not include the corporate logo.

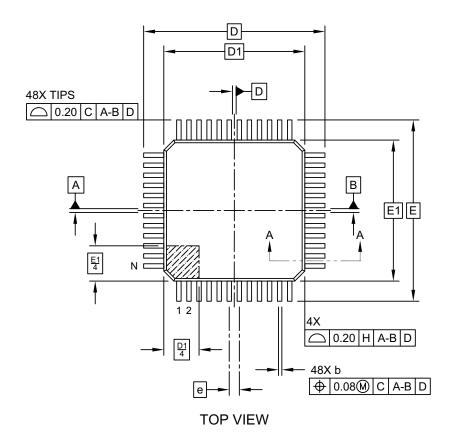

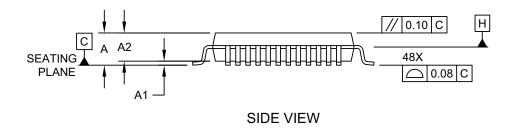

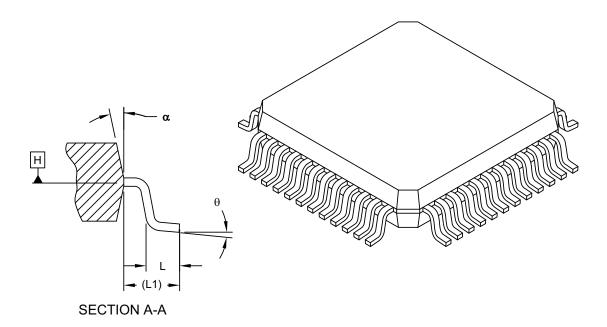

# 48-Lead Low-profile Plastic Quad Flat Pack Package (R8) -7x7 mm Body [LQFP] Supertex Legacy Package

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-278 Rev A Sheet 1 of 2

# 48-Lead Low-profile Plastic Quad Flat Pack Package (R8) -7x7 mm Body [LQFP] Supertex Legacy Package

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units  | MILLIMETERS |           |      |  |  |  |

|--------------------------|--------|-------------|-----------|------|--|--|--|

| Dimension                | Limits | MIN         | NOM       | MAX  |  |  |  |

| Number of Leads          | Ν      |             | 48        |      |  |  |  |

| Lead Pitch               | е      |             | 0.50 BSC  |      |  |  |  |

| Overall Height           | Α      | 1.40        | 1.50      | 1.60 |  |  |  |

| Standoff                 | A1     | 0.05        | 0.10      | 0.15 |  |  |  |

| Molded Package Thickness | A2     | 1.35        | 1.40      | 1.45 |  |  |  |

| Foot Length              | L      | 0.45        | 0.45 0.60 |      |  |  |  |

| Footprint                | L1     |             | 1.00 REF  |      |  |  |  |

| Foot Angle               | θ      | 0°          | 3.5°      | 7°   |  |  |  |

| Overall Width            | Е      |             | 9.00 BSC  |      |  |  |  |

| Overall Length           | D      |             | 9.00 BSC  |      |  |  |  |

| Molded Package Width     | E1     | 7.00 BSC    |           |      |  |  |  |

| Molded Package Length    | D1     | 7.00 BSC    |           |      |  |  |  |

| Lead Width               | b      | 0.17        | 0.27      |      |  |  |  |

| Mold Draft Angle Top     | α      | 11°         | 12°       | 13°  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensioning and tolerancing per ASME Y14.5M  $\,$

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

$\label{lem:REF:Reference Dimension, usually without tolerance, for information purposes only. \\$

Microchip Technology Drawing C04-278 Rev A Sheet 2 of 2

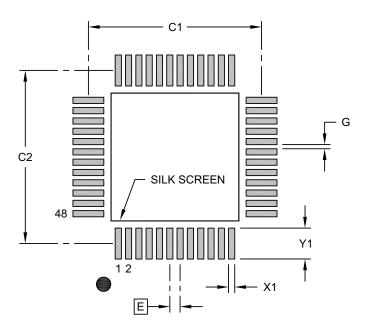

# 48-Lead Low-profile Plastic Quad Flat Pack Package (R8) -7x7 mm Body [LQFP] Supertex Legacy Package

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                                  | MILLIMETERS |      |          |      |  |

|----------------------------------|-------------|------|----------|------|--|

| Dimension                        | Limits      | MIN  | NOM      | MAX  |  |

| Contact Pitch                    | Е           |      | 0.50 BSC |      |  |

| Contact Pad Spacing              | C1          |      | 8.40     |      |  |

| Contact Pad Spacing              | C2          |      | 8.40     |      |  |

| Contact Pad Width (X48)          | X1          |      |          | 0.30 |  |

| Contact Pad Length (X48)         | Y1          |      |          | 1.50 |  |

| Contact Pad to Contact Pad (X44) | G           | 0.20 |          |      |  |

#### Notes:

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2278 Rev A

### **APPENDIX A: REVISION HISTORY**

#### **Revision A (February 2025)**

- Converted Supertex Doc # DSFP-HV2733 to Microchip DS20005838A

- Removed "HVCMOS® Technology for high performance" in the Features and General Description sections

- Removed the 48-lead LQFP M931 media type to align packaging specifications with the actual BQM

- Changed the package marking format

- · Updated package outline drawings

- · Made minor changes throughout the document

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

| PART NO.       | XX                 |   | - х - х                                                                                | Example:       |                                                                                                                          |

|----------------|--------------------|---|----------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------|

| Device         | Package<br>Options |   | Environmental Media Type                                                               | a) HV2733FG-G: | 16-Channel Low-Harmonic-<br>Distortion High-Voltage Ana-<br>log Switch with Bleed Resis-<br>tors, 48-lead LQFP, 250/Tray |

| Device:        | HV2733             | = | 16-Channel Low-Harmonic-Distortion High-<br>Voltage Analog Switch with Bleed Resistors |                | 1013, 40-1000 EQTT, 200/11dy                                                                                             |

| Package:       | FG                 | = | 48-lead LQFP                                                                           |                |                                                                                                                          |

| Environmental: | G                  | = | Lead (Pb)-free/RoHS-compliant Package                                                  |                |                                                                                                                          |

| Media Type:    | (blank)            | = | 250/Tray for an FG Package                                                             |                |                                                                                                                          |

|                |                    |   |                                                                                        |                |                                                                                                                          |

|                |                    |   |                                                                                        |                |                                                                                                                          |

|                |                    |   |                                                                                        |                |                                                                                                                          |

|                |                    |   |                                                                                        |                |                                                                                                                          |

|                |                    |   |                                                                                        |                |                                                                                                                          |

NOTES:

# **Microchip Information**

#### **Trademarks**

The "Microchip" name and logo, the "M" logo, and other names, logos, and brands are registered and unregistered trademarks of Microchip Technology Incorporated or its affiliates and/or subsidiaries in the United States and/or other countries ("Microchip Trademarks"). Information regarding Microchip Trademarks can be found at <a href="https://www.microchip.com/en-us/about/legal-information/microchip-trademarks">https://www.microchip.com/en-us/about/legal-information/microchip-trademarks</a>.

ISBN: 979-8-3371-0632-8

#### **Legal Notice**

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip products:

- · Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code.

Code protection does not mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to continuously improving the code protection features of our products.