# **ZL70103 Medical Implantable RF Transceiver MICS-Band RF Telemetry**

#### **Features**

- 402–405 MHz (10 MICS-band channels) and 433–434 MHz (2 ISM-band channels)

- Raw Data Rates: 800/400/200/40/18.18kbit/s

- High-Performance MAC with Automatic Error Handling and Flow Control

- Very Few External Components (crystal, decoupling, and antenna matching)

- · Ultra-Low-Power Operation

- Average TX/RX Current (typical 5mA)

- Sleep/Sniff State Average Current (typical 290nA at 1-second sniff interval)

- Standards Compatible (MICS<sup>1</sup>, ETSI, FCC, IEC)

- RoHS Compliant

# **Applications**

- · Implantable Medical Devices

- Cardiac Rhythm Management

- Neurostimulators

- Drug Delivery, Sensors, and Diagnostics

# **Description**

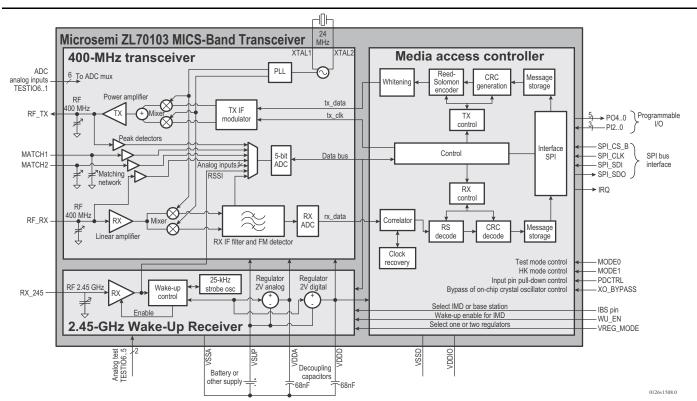

The ZL70103 is a high-performance, half-duplex, RF communications link for medical implantable applications.

The system is very flexible and supports two low-power wake-up options. Extremely low power is achievable using the 2.45-GHz ISM-band wake-up receiver option. The high level of integration includes a Media Access Controller, providing complete control of the device along with coding and decoding of RF messages. A standard SPI bus interface provides for easy access by the application.

# **Ordering Information**

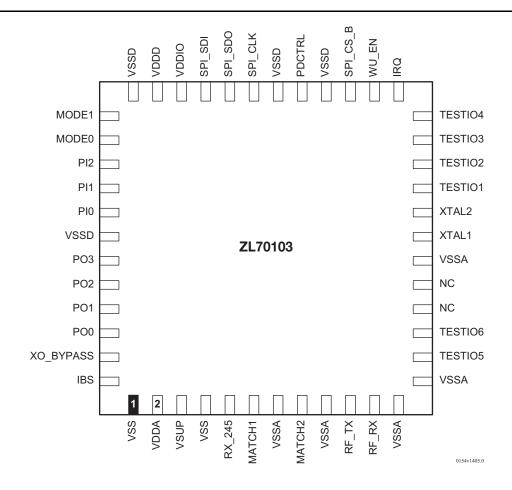

ZL70103LDG1 48-pin QFN (for base station applications only)

ZL70103UEJ2 49-pin CSP, SAC405 (for implant applications only)

ZL70103UBJ Bare die (for implant applications only)

Please see chapter "2 – Ordering and Package Overview" on page 2-1 for details.

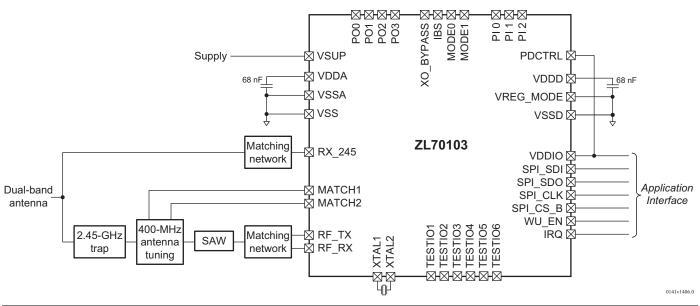

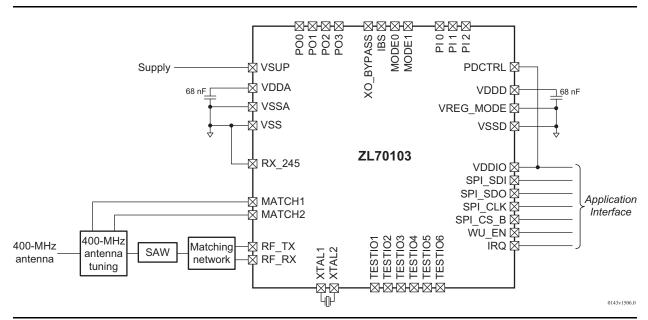

Figure 1 • ZL70103 Block Diagram

<sup>1</sup> The MICS band is a subset of the designated MedRadio frequency band.

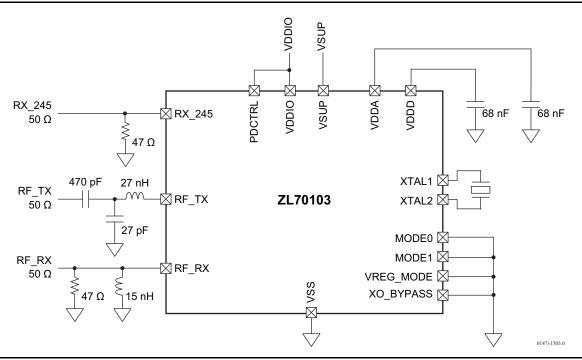

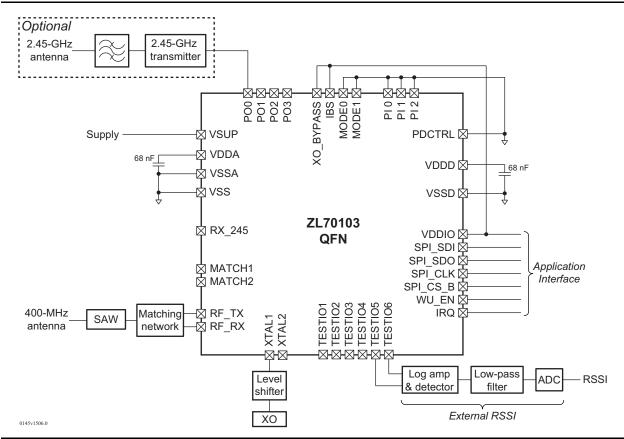

#### Schematic Interconnect Diagram of the ZL70103

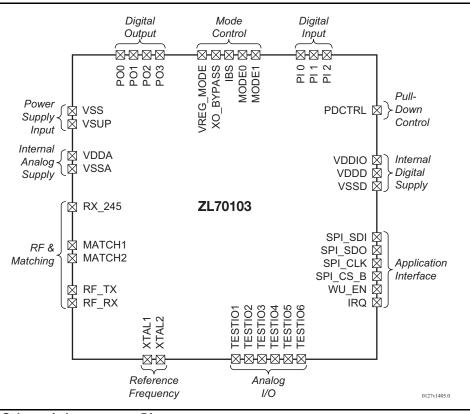

Figure 2 • ZL70103 Schematic Interconnect Diagram

The schematic interconnect diagram above shows all of the important connections that are available. Please note that the diagram does not show all connections (for example, ground connections) and that the available connections differ for each package option. Please see Table 8-1 on page 8-1 and chapter "9 – Mechanical Reference" on page 9-1 for details.

Revision 2

Table 1 • Schematic Overview of the ZL70103 Interconnects

| Symbol                  | Description                                                                                                                                                                                                                         |  |  |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Internal Analog Supply  |                                                                                                                                                                                                                                     |  |  |  |  |

| VSSA                    | Analog ground                                                                                                                                                                                                                       |  |  |  |  |

| VDDA                    | Analog on-chip voltage regulator output (internal analog 2-V domain); connects to an external 68- to 100-nF capacitor for voltage regulator stability                                                                               |  |  |  |  |

| Power Supply Input      |                                                                                                                                                                                                                                     |  |  |  |  |

| VSS                     | Common chip ground                                                                                                                                                                                                                  |  |  |  |  |

| VSUP                    | Power supply input                                                                                                                                                                                                                  |  |  |  |  |

| RF and Matching         |                                                                                                                                                                                                                                     |  |  |  |  |

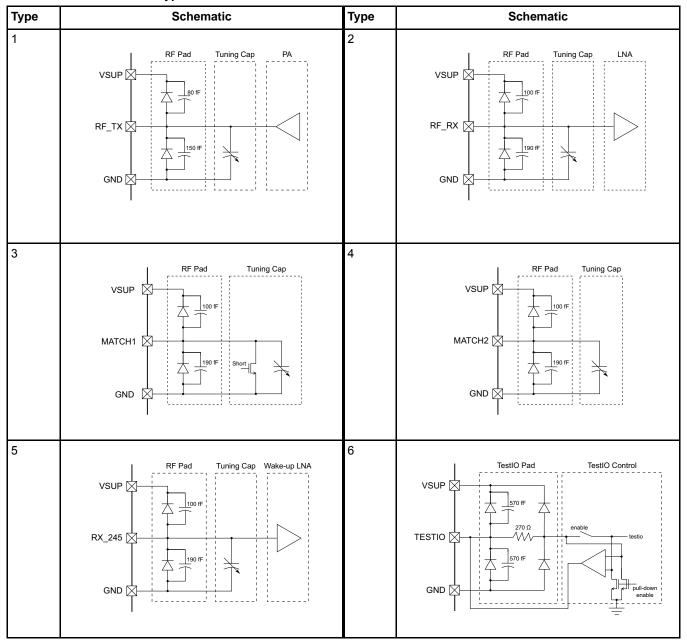

| RX_245                  | 2.45-GHz wake-up receiver input                                                                                                                                                                                                     |  |  |  |  |

| MATCH1<br>MATCH2        | Antenna/matching network tuning capacitors                                                                                                                                                                                          |  |  |  |  |

| RF_TX                   | 400-MHz RF transmitter output to matching network                                                                                                                                                                                   |  |  |  |  |

| RF_RX                   | 400-MHz RF receiver input from matching network                                                                                                                                                                                     |  |  |  |  |

| Reference Frequency     |                                                                                                                                                                                                                                     |  |  |  |  |

| XTAL1<br>XTAL2          | Connection to the reference frequency crystal. The chip can also use an external oscillator connected to XTAL1 (controlled by XO_BYPASS).                                                                                           |  |  |  |  |

| Analog I/O              |                                                                                                                                                                                                                                     |  |  |  |  |

| TESTIO1 to TESTIO6      | Analog input/output. Mainly used during electrical testing in chip production.                                                                                                                                                      |  |  |  |  |

| Application Interface   |                                                                                                                                                                                                                                     |  |  |  |  |

| IRQ                     | Master interrupt request                                                                                                                                                                                                            |  |  |  |  |

| WU_EN                   | Wake-up enable signal used to initiate the 2.45-GHz wake-up receiver to perform a sniff or for a direct wake-up of the device                                                                                                       |  |  |  |  |

| SPI_CS_B                | SPI chip select (active low)                                                                                                                                                                                                        |  |  |  |  |

| SPI_CLK                 | SPI serial clock                                                                                                                                                                                                                    |  |  |  |  |

| SPI_SDO                 | SPI serial data out                                                                                                                                                                                                                 |  |  |  |  |

| SPI_SDI                 | SPI serial data in                                                                                                                                                                                                                  |  |  |  |  |

| Internal Digital Supply |                                                                                                                                                                                                                                     |  |  |  |  |

| VDDIO                   | Digital I/O supply input to internal level shifters                                                                                                                                                                                 |  |  |  |  |

| VDDD                    | Digital on-chip voltage regulator output (internal digital 2-V domain); connects to an external 68- to 100-nF capacitor for voltage regulator stability                                                                             |  |  |  |  |

| VSSD                    | Digital ground                                                                                                                                                                                                                      |  |  |  |  |

| Digital Input Mode      |                                                                                                                                                                                                                                     |  |  |  |  |

| PDCTRL                  | Digital input pull-down control for the following pins: MODE0, MODE1, IBS, XO_BYPASS, and PI0 to PI2. If PDCTRL = VDDIO, then these inputs are pulled low with a 90-kΩ internal resistor and do not need to be grounded externally. |  |  |  |  |

| Digital Input           |                                                                                                                                                                                                                                     |  |  |  |  |

| PI0 to PI2              | Programmable digital inputs (three inputs)                                                                                                                                                                                          |  |  |  |  |

|                         |                                                                                                                                                                                                                                     |  |  |  |  |

Revision 2 III

Table 1 • Schematic Overview of the ZL70103 Interconnects (continued)

| Symbol         | Description                                                                                                                                                                                                          |  |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Mode Control   | •                                                                                                                                                                                                                    |  |  |  |  |

| MODE0          | The MODE0 input selects normal operation mode or test mode (for Microsemi use only). Should be tied low for normal operation.                                                                                        |  |  |  |  |

| MODE1          | Controls whether HK messages can write to registers. MODE1 = 0 disables HK writes (recommended).                                                                                                                     |  |  |  |  |

| IBS            | Implant/base mode selection                                                                                                                                                                                          |  |  |  |  |

| XO_BYPASS      | When high, the internal oscillator is bypassed and an external oscillator clock is fed to the XTAL1 pin                                                                                                              |  |  |  |  |

| VREG_MODE      | Voltage regulator selection of <i>either</i> VDDA <i>or</i> VDDA and VDDD (VREG_MODE = 0 for VDDA and VDDD, recommended). Note that this pin is not available on the QFN package and is hardwired to VSS internally. |  |  |  |  |

| Digital Output |                                                                                                                                                                                                                      |  |  |  |  |

| PO0 to PO3     | Programmable digital outputs (four outputs).                                                                                                                                                                         |  |  |  |  |

Revision 2 IV

# **Table of Contents**

| ZL70103 Medical Implantable RF Transceiver                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 - Product Description         Introduction       1-         Typical Applications       1-                                                                                                                                                         |

| 2 – Ordering and Package Overview                                                                                                                                                                                                                   |

| 3 - Functional Description         General       3-         Wake-Up Modes and Operational States       3-         400-MHz Transceiver Subsystem       3-         2.45-GHz Wake-Up Receiver       3-         Media Access Controller (MAC)       3-1 |

| 4 - System Reliability Features         System Integrity — Watchdogs       4-         Memory Integrity — CRC Check of Registers       4-         Communication Link Integrity       4-                                                              |

| 5 - Application Interface         Serial Peripheral Interface       5-         Housekeeping Messages       5-         Interrupts       5-         Programmable I/O       5-                                                                         |

| 6 – Calibrations                                                                                                                                                                                                                                    |

| 7 - Electrical Reference         Absolute Maximum Ratings       7-         Nominal Environment       7-         Conditions       7-         Electrical Characteristics       7-         Typical Performance       7-1                               |

| 8 – Pin List Pin Types                                                                                                                                                                                                                              |

| 9 – Mechanical Reference         48-Pin QFN Package       9-         49-Pin CSP Package       9-         Bare Die       9-                                                                                                                          |

| 10 - Typical Application Examples         Ultra-Low-Power Implant Device       10-         Low-Power Implant Device       10-         External Device       10-                                                                                     |

# 11 – Quality

# 12 - Datasheet Information

| List of Changes                                                         | 12-1 |

|-------------------------------------------------------------------------|------|

| Datasheet Categories                                                    | 12-2 |

| Safety Critical. Life Support, and High-Reliability Applications Policy | 12-2 |

Revision 2 VI

# **List of Figures**

| Figure 1 • ZL70103 Block Diagram                                              |      |

|-------------------------------------------------------------------------------|------|

| Figure 2 • ZL70103 Schematic Interconnect Diagram                             |      |

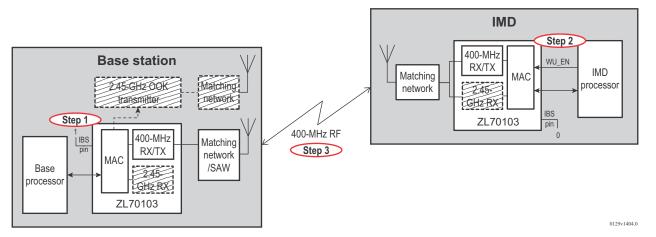

| Figure 1-1 • Application Example                                              |      |

| Figure 3-1 • Wake-Up Method Using 2.45 GHz                                    |      |

| Figure 3-2 • Wake-Up Method Using IMD Pin Control                             |      |

| Figure 3-3 • Operating Modes and States                                       |      |

| Figure 3-4 • 400-MHz Transceiver Subsystem                                    |      |

| Figure 3-5 • 2.45-GHz Wake-Up Receiver Subsystem                              |      |

| Figure 3-6 • Strobing of Wake-Up System                                       |      |

| Figure 3-7 • The Data Packet Definition                                       |      |

| Figure 3-8 • Media Access Controller Subsystem                                | 3-12 |

| Figure 3-9 • Packet Definition (first in time on the left side)               | 3-13 |

| Figure 5-1 • SPI Bus Interface                                                | 5-1  |

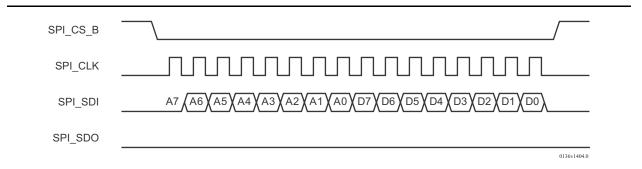

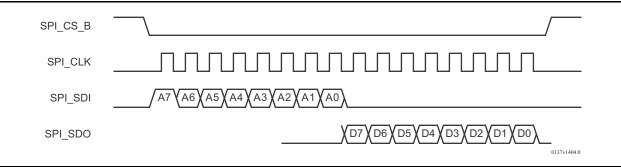

| Figure 5-2 • Timing for SPI Write of One Byte Using Seven-Bit Addressing Mode |      |

| Figure 5-3 • Timing for SPI Read of One Byte Using Seven-Bit Addressing Mode  | 5-2  |

| Figure 7-1 • Nominal Environment Schematic                                    |      |

| Figure 7-2 • Operating Conditions Overview                                    |      |

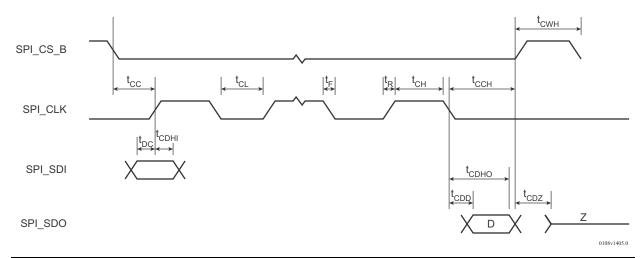

| Figure 7-3 • SPI Timing Parameters                                            |      |

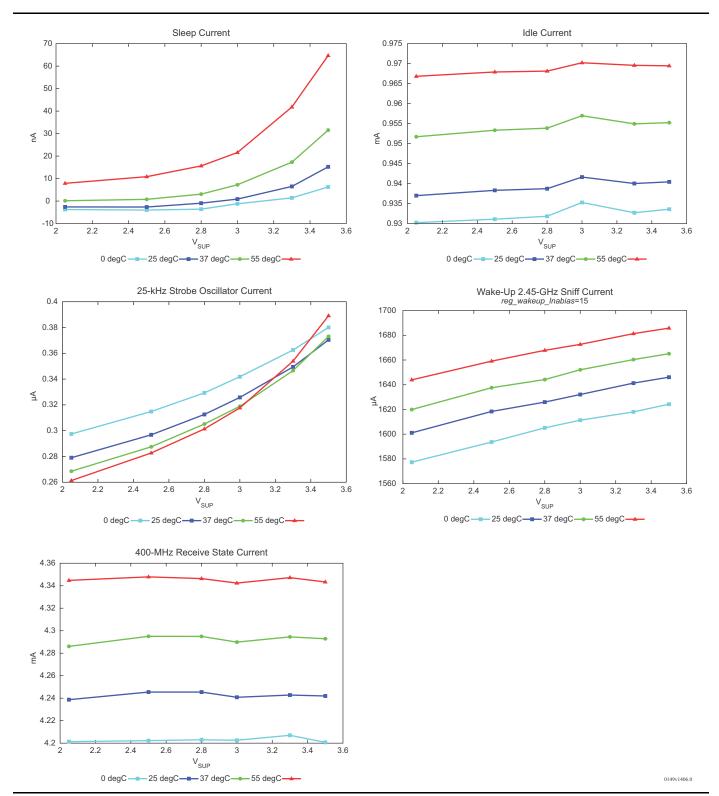

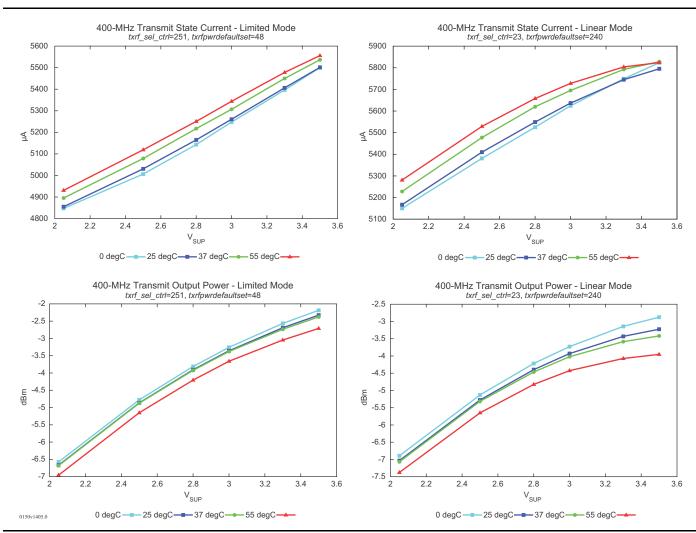

| Figure 7-4 • Typical Performance Graphs                                       | 7-15 |

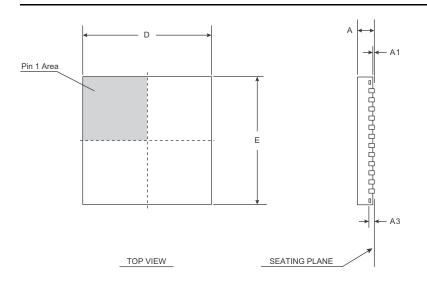

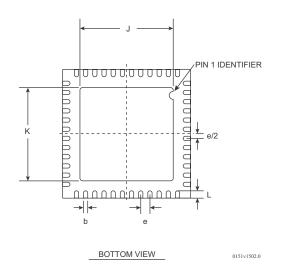

| Figure 9-1 • Package Drawing and Package Dimensions for 48-Pin QFN            | 9-1  |

| Figure 9-2 • Footprint (top view) and Markings for 48-Pin QFN                 |      |

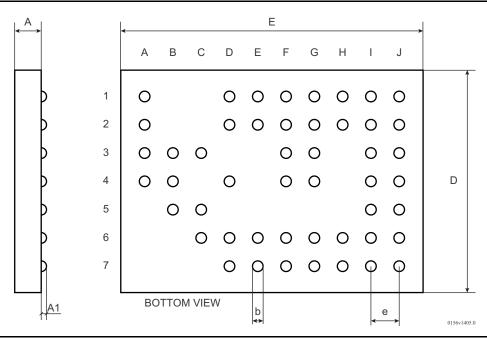

| Figure 9-3 • Package Drawing of 49-Pin CSP                                    |      |

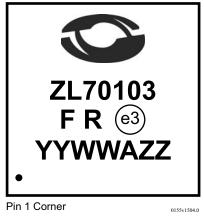

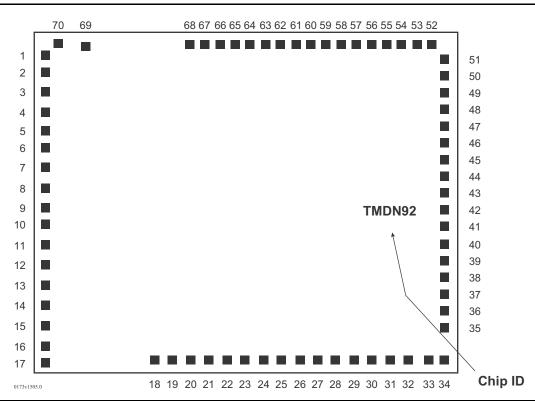

| Figure 9-4 • Markings for 49-Pin CSP                                          |      |

| Figure 9-5 • Pad Locations for Bare Die                                       |      |

| Figure 10-1 • Ultra-Low-Power Implant Device                                  |      |

| Figure 10-2 • Low-Power Implant Device                                        | 10-2 |

| Figure 10-3 • External Device                                                 |      |

# **List of Tables**

| Table 1 • Schematic Overview of the ZL70103 Interconnects                          | III  |

|------------------------------------------------------------------------------------|------|

| Table 2-1 • Ordering and Package Overview                                          | 2-1  |

| Table 3-1 • Current Consumption for Different Conditions of Each Operational State | 3-5  |

| Table 3-2 • Average Sleep/Sniff Current Consumption While Sniffing                 | 3-5  |

| Table 3-3 • Options for Modulation Modes, Data Rates, and Receiver Sensitivity     | 3-7  |

| Table 3-4 • MICS/ISM Channel Table                                                 | 3-8  |

| Table 4-1 • Summary of Watchdogs                                                   | 4-1  |

| Table 5-1 • Summary of Base Station Control Signals                                | 5-4  |

| Table 7-1 • Absolute Maximum Ratings                                               | 7-1  |

| Table 7-2 • Recommended Operating Conditions                                       | 7-4  |

| Table 7-3 • Operating Conditions for External Applications                         | 7-4  |

| Table 7-4 • Extended Temperature Operating Conditions                              | 7-4  |

| Table 7-5 • Implant Conditions                                                     | 7-5  |

| Table 7-6 • Register Settings for Implant Conditions                               | 7-5  |

| Table 7-7 • External Device Conditions                                             | 7-5  |

| Table 7-8 • Register Settings for External Conditions                              | 7-5  |

| Table 7-9 • General Notes on Limits                                                | 7-6  |

| Table 7-10 • On-Chip Voltage Regulators                                            | 7-6  |

| Table 7-11 • Digital Interface                                                     | 7-7  |

| Table 7-12 • SPI Timing Requirements                                               | 7-8  |

| Table 7-13 • General RF Parameters                                                 | 7-9  |

| Table 7-14 • Current Consumption                                                   |      |

| Table 7-15 • Synthesizer                                                           | 7-11 |

| Table 7-16 • 400-MHz Transmitter                                                   | 7-11 |

| Table 7-17 • 400-MHz Receiver                                                      | 7-12 |

| Table 7-18 • 2.45-GHz Receiver                                                     |      |

| Table 7-19 • Crystal Oscillator                                                    |      |

| Table 7-20 • General-Purpose ADC                                                   |      |

| Table 7-21 • Internal RSSI                                                         |      |

| Table 7-22 • RF Ports                                                              |      |

| Table 8-1 • ZL70103 Pin List                                                       |      |

| Table 8-2 • ZL70103 Pin Type Schematics                                            |      |

| Table 9-1 • Package Dimensions for 49-Pin CSP                                      |      |

| Table 9-2 • Bump Locations for 49-Pin CSP                                          |      |

| Table 9-3 • Dimensions for Bare Die                                                | 9-5  |

| Table 9-4 • Pad Coordinates for Bare Die                                           | 9-6  |

# 1 - Product Description

# Introduction

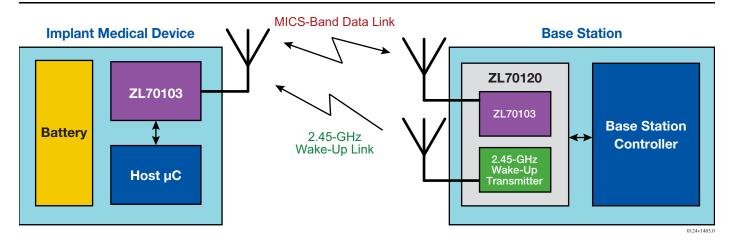

The ZL70103 is an ultra-low-power RF transceiver for implantable medical applications. It operates in the Medical Implantable Communication Service<sup>1</sup> (MICS) band at 402–405 MHz and provides a complete radio modem enabling communication with a medical device in the body. The *wireless* RF telemetry link replaces the traditional inductively coupled wand and enables benefits including:

- · Higher data rates

- · Placement of the programmer further away from the body (outside the sterile area) during surgery

- · Remote monitoring outside the medical clinic

- Body-worn applications allowing patient control and monitoring

- · Link to other nonimplanted medical devices and sensors for more advanced applications

The ZL70103 RF transceiver provides a complete MICS-band solution and can be used in both ends of the link, that is, both in the Implantable Medical Device (IMD) and in the external device (base station, programmer, remote monitor, etc.).

Figure 1-1 • Application Example

# **Dedicated for the Medical Implant Market**

The ZL70103 has been developed specifically for the medical implant market and is optimized for the requirements driven by these types of products. Robustness, quality, and ultralow power have been cornerstones in the ZL70103 system definition.

The ZL70103 RF transceiver is designed, from the bottom up, to be a true ultra-low-power device. Implantable medical devices normally have very limited battery resources, and longevity is one of the core values of the application. The RF telemetry link is expected to use a fraction of the battery resources from the target treatment of the IMD.

Low current consumption during transmission is essential, but even more important is that the radio can be kept in a sleep state for as much time as possible while maintaining responsiveness. Every block of the ZL70103 has therefore been carefully designed with ultralow power consumption in mind, and advanced power management is implemented on all levels.

<sup>1</sup> The MICS band is a dedicated band for nonaudio, implantable applications. One side of the link has to be implanted.

## **Innovative Wake-Up System**

To conserve battery power it is essential to provide an ultra-low-power wake-up system. The ZL70103 is very versatile and supports three wake-up methods:

2.45-GHz wake-up receiver: Fully autonomous, ultra-low-power wake-up receiver, utilizing the higher

transmitted power allowed for by the 2.45-GHz ISM band. Modulation and

protocol are optimized for ultralow power and robustness.

In-band (MICS-band) wake-up: Advanced support for in-band wake-up in the MICS band enables a simple

hardware implementation (some support from the host required).

Wake-up by host: Wake-up by the host controller, in combination with support for the low duty-

cycle mode, enables scheduled communication schemes or ad hoc wake-up

initiated by the implant.

# **High-Performance MAC and Autonomous Operation**

The ZL70103 has a packet-level interface that is simple to use and supported by a high-performance MAC with automatic error correction and flow control. The host controller can concentrate on the treatment and delegate the communication to the ZL70103 transceiver. The radio can be controlled remotely through the link and could in principle operate with no host controller using the on-chip general purpose I/Os to control a simple application.

#### **Self-Contained**

The ZL70103 transceiver is highly integrated and self-contained. Very few external components are required to make a complete radio system:

- Antenna with suitable matching network

- SAW filter to suppress unwanted blockers

- · Crystal for the reference frequency (on-chip oscillator)

- Decoupling capacitors for power supply (on-chip regulators)

# **Typical Applications**

Three typical applications are presented below. Chapter "10 – Typical Application Examples" on page 10-1 provides schematics and more details. These three typical applications are intended as a starting point for the target application.

# **Ultra-Low-Power Implant Devices**

This application area has been dominated by cardiac rhythm management products like pacemakers and Implantable Cardioverter Defibrillators (ICD) where low power and device longevity were very important characteristics of the device market long before RF telemetry was introduced. This means that the industry is willing to take extra efforts to save power even if this results in a moderate increase in complexity. There are other new applications that also fall into this category.

To address this need, the ZL70103 is equipped with an ultra-low-power 2.45-GHz wake-up system that provides by far the lowest power consumption. The 2.45-GHz wake-up system is also autonomous and fully integrated when the ZL70103 is used in an implant.

# **Low-Power Implant Devices**

Many neurostimulators, drug delivery systems, sensors, and diagnostic applications are operated in a mode allowing higher power consumption since the core function itself consumes more power, requiring use of larger or rechargeable batteries. This allows alternative wake-up solutions to be used, like the in-band wake-up in the MICS band, that simplify the hardware design (the matching network and antenna use only the 400-MHz band).

#### **External Devices**

This is the other side of the MICS-band link with a higher allowed power budget in comparison with the implanted device. The external device, acting as a base station, also has to fulfill other requirements of the MICS standard such as Clear Channel Assessment (CCA), and it is required to transmit the 2.45-GHz wake-up packet if the 2.45-GHz wake-up option is used. Applications include:

- · Programming base stations

- · Home/remote monitoring devices

- · Handheld, mobile, and belt-worn applications

# 2 - Ordering and Package Overview

The ZL70103 RF transceiver is available in several package options. Some of these packages are intended for implant devices and some for external devices (base stations). Depending on the application there are some differences in the electrical specifications, please refer to chapter "7 – Electrical Reference" on page 7-1 for details.

Table 2-1 • Ordering and Package Overview

|                                                     | Temp          |            |                           | ě                | ıt.              | Application Area   |                                  |

|-----------------------------------------------------|---------------|------------|---------------------------|------------------|------------------|--------------------|----------------------------------|

| Ordering Code                                       | Range<br>(°C) | Package    | Delivery Form             | Pb Free          | Implant<br>Grade | Implant<br>Devices | External<br>Devices <sup>1</sup> |

| ZL70103LDG1                                         | 0 to +55      | 48-pin QFN | trays, bake, and dry-pack | YES <sup>2</sup> | NO <sup>3</sup>  |                    | Х                                |

| ZL70103UEJ2 (contact<br>Microsemi for availability) | 0 to +55      | 49-pin CSP | trays                     | YES <sup>4</sup> | YES              | Х                  |                                  |

| ZL70103UBJ (contact<br>Microsemi for availability)  | 0 to +55      | bare die   | trays                     | N/A              | YES              | Х                  |                                  |

#### Notes:

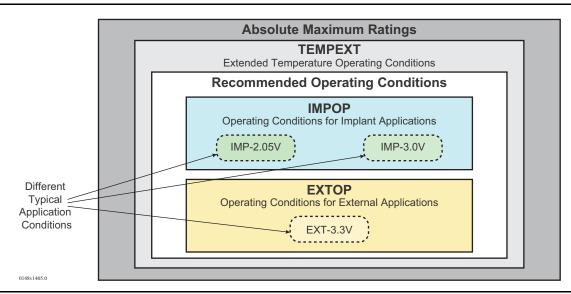

- 1. Conditions that are applicable only for external applications are marked with "EXTOP" or "EXT-3.3V"; please refer to the "Conditions" section on page 7-3 for details.

- 2. Matte tin.

- 3. The QFN device is intended ONLY for external devices that are configured as controllers, such as base stations, programmers, patient controllers, and bedside monitors. The QFN device is NOT intended to be used in implant applications inside or outside the body. Implant applications such as trial devices that are functionally equivalent to implants but are worn outside the body should use bare die, CSP, or Microsemi modules. Testing of the 2.45-GHz wake-up receiver (RX\_245 pin) is limited on QFN devices and, therefore, its operation and/or specifications are not guaranteed.

- 4. SAC405.

# 3 - Functional Description

#### General

The ZL70103 is an ultra-low-power, high-bandwidth, RF transceiver for medical implantable applications. It operates in the Medical Implantable Communication Service (MICS) band at 402–405 MHz. It uses a forward error correction scheme together with CRC error detection to achieve an extremely reliable link.

#### **Basic Modes**

The ZL70103 transceiver is designed for operation in either an implant or a base station application. These systems have different requirements, especially with regard to power consumption. Therefore the ZL70103 transceiver has two basic modes (the mode is selected at power-up by the IBS pin):

IMD mode The device is asleep waiting for a wake-up event

Base mode The device is powered up and idle

When configured in IMD mode, the transceiver is usually asleep and in an ultra-low-current state. The IMD may be woken up to initiate communications either by receipt of a specially coded 2.45-GHz wake-up message or directly by the IMD processor via the WU\_EN pin. These two methods of starting a communication session with an IMD are summarized below.

### **Power-Up Sequence**

To ensure proper operation, the device must be powered-up in the correct order:

- 1. VDDIO and all digital inputs should have a defined low state

- 2. Provide supply voltage on the VSUP pin

- 3. Provide supply for the digital interface on the VDDIO pin and define digital inputs according to the configuration used

It is OK to provide supply to VDDIO at the same time as VSUP when they are connected together; however, VDDIO must never exceed VSUP.

### Wake-Up Method Using 2.45-GHz Sent from a Base Station

Figure 3-1 shows the steps in setting up communication between a base station and an IMD woken up by using the ultra-low-power 2.45-GHz wake-up method. Details of this wake-up method are available in the ZL70103 Design Manual.

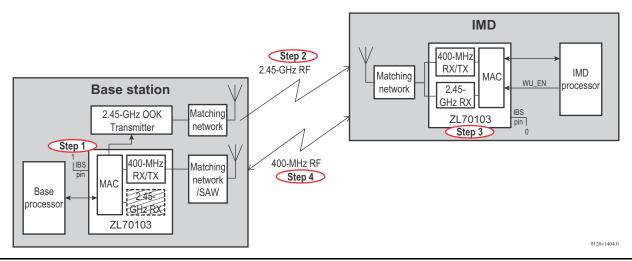

Figure 3-1 • Wake-Up Method Using 2.45 GHz

#### Steps:

- 1. START UP BASE STATION: Set the IBS pin equal to 1 and power up the base station. MAC starts and waits in IDLE state. Base station application performs Clear Channel Assessment (CCA) as described in the ZL70103 Design Manual. Base station application sets up important link parameters including registers for modulation mode, channel to use, IMD transceiver ID, and company ID as described in the "2.45-GHz Wake-Up Receiver" section on page 3-9 as well as in the ZL70103 Design Manual.

- 2. SEND 2.45-GHz WAKE-UP MESSAGE: The base station application initiates wake-up by writing to a communication control register in the ZL70103. This simultaneously provides the On-Off Keyed (OOK) pattern to the external 2.45-GHz transmitter and starts the 400-MHz transmitter and receiver to transmit 400-MHz wake-up messages and to receive 400-MHz wake-up responses, respectively.

- 3. IMD RECEIVES 2.45-GHz MESSAGE: The IMD's 2.45-GHz receiver is usually in a sleep state but is configured to periodically be powered up to look for a 2.45-GHz wake-up message. The interval between power-up strobes is user defined. The user may select one or both of the following two strobe mechanisms: (a) program a low-power oscillator available in the ZL70103 to generate the strobe, or (b) toggle the WU\_EN pin to initiate a strobe.

- 4. IMD SENDS 400-MHz WAKE-UP RESPONSES: The IMD begins transmitting 400-MHz wake-up responses to the base station while listening for 400-MHz wake-up messages. The interval between response packets is randomized to minimize collisions between multiple IMDs and the base station. The base station may then begin a full MICS-band communication session with the desired IMD by writing to a communication control register in the ZL70103.

### **Wake-Up Method Using IMD Pin Control**

Figure 3-2 shows the steps in setting up communication between a base station and an IMD woken up using the pin control in the IMD. This method is used for the following wake-up schemes:

- IMD woken up to sniff for a 400-MHz link. The ZL70103 supports such a mode of operation, although the 2.45-GHz wake-up system described in the previous "Wake-Up Method Using 2.45-GHz Sent from a Base Station" section on page 3-2 has a much lower power consumption.

- IMD woken to send an emergency message, in which case no CCA by the base station is required.

- IMD woken up by a low-frequency inductive link (as typically used in pacemakers/ICDs) or some other alternative mechanism.

In all these cases, the IMD transceiver is started by applying a positive pulse on WU\_EN longer than 1.5 ms as described in the following steps.

Figure 3-2 • Wake-Up Method Using IMD Pin Control

#### Steps:

- 1. START UP BASE STATION: Set the IBS pin equal to 1 and power up the base station. MAC starts and waits in the IDLE state. Base station application is set to monitor a channel selected by the application.

- 2. IMD PROCESSOR STARTS IMD TRANSCEIVER: IMD application sets the WU\_EN pin high for greater than 1.5 ms and then low again (direct wake-up). The IMD transceiver wakes up and waits in the IDLE state. An important flag in the IMD transceiver called the IBS flag is set to 1 (IDLE). The IBS flag defines the operation of the transceiver after the MAC has woken up. The flag has two states (1 for IDLE, 0 to transmit wake-up responses).

- 3. IMD SENDS 400-MHz WAKE-UP NOTIFICATION: The IMD application then sets up the transceiver to use the desired modulation mode and channel, then changes the IBS flag to 0 (transmit wake-up responses) by writing to the appropriate control register in the IMD ZL70103. The IMD begins transmitting 400-MHz wake-up responses to the base station and the base station receives these responses. The base station may then begin a full MICS-band communication session with the desired IMD by writing to a communication control register in the ZL70103.

Details of the programming steps necessary for these steps and other operations is provided in the ZL70103 Design Manual.

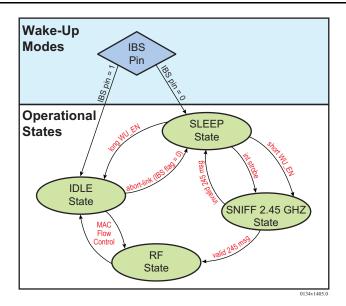

# **Wake-Up Modes and Operational States**

# **Wake-Up Modes**

The IBS pin is used to define the normal operating mode. The IBS pin is low (0) to define that the ZL70103 is used in an implant and the IBS pin is high (1) to define that the device is used in an external device like a base station.

# **Operational States**

During normal operation the device switches between the operational states depending on activity. Please refer to Figure 3-3 for an overview of the operating states.

Figure 3-3 • Operating Modes and States

# **Current Consumption Overview**

Table 3-1 summarizes the current consumption for the different operational states. Please also refer to Figure 3-6 on page 3-10.

Table 3-1 • Current Consumption for Different Conditions of Each Operational State

| Operational State | Condition                          | Typical<br>Current | Description                                                                                                                                                                                      |  |

|-------------------|------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SLEEP             | Standby                            | 10nA               | The device is in the ultra-low-power SLEEP (standby) state. In the condition, the ZL70103 can be woken up only by an external strotto the WU_EN pin.                                             |  |

|                   | 25-kHz strobe oscillator (enabled) | 320nA              | Internal strobe pulse generator that can be used as an alternative to an external pulse on WU_EN. This current does include the SLEEP state current given for the Standby condition above.       |  |

| IDLE              | IDLE                               | 0.95mA             | The MAC is running but the RF and wake-up blocks are inactive.                                                                                                                                   |  |

| RF                | 400-MHz receive                    | 4.3mA              | The device is running and in the 400-MHz receive state.                                                                                                                                          |  |

|                   | 400-MHz transmit                   | 5.3mA              | The device is running and in the 400-MHz transmit state (default configuration). Note that this current varies based on the transmitter output setting and based on the load on the transmitter. |  |

|                   | 400-MHz RSSI sniff                 | 4.0mA              | The device is running in the receive state and sniffing for energy in the 400-MHz band as part of a 400-MHz wake-up mode.                                                                        |  |

| SNIFF 245<br>GHZ  | 2.45-GHz RX sniff                  | 1.4 mA             | The device is receiving on 2.45 GHz to decode and identify valid wake-up messages from the base station (default configuration). The typical sniff period is 200 µs. See Note 1.                 |  |

#### Note:

Based on the wake-up method, Table 3-2 gives the typical average current consumption for each method.

Table 3-2 • Average Sleep/Sniff Current Consumption While Sniffing

| Sniff Mode | Condition                                                                       | Typical<br>Average<br>Current | Description                                                                                                                                                                           |

|------------|---------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 400-MHz    | Direct wake-up with fast startup enabled                                        | <5µA                          | Average sleep/sniff current consumption for a 400-MHz sniff based on a sniff interval of 5 seconds and a sniff period of 9.375ms.                                                     |

| 2.45-GHz   | External strobe of the WU_EN pin once a second                                  | 290 nA                        | Average sleep/sniff current consumption based on a sniff interval of 1 second and a sniff period of 200 µs. The sniff is triggered by a short pulse on the WU_EN pin. See Note 1.     |

|            | Internal strobe once a<br>second by the 25-kHz<br>strobe oscillator<br>(strosc) | 600nA                         | Average sleep/sniff current consumption based on a sniff interval 1 second and a sniff period of 200 µs. The sniff is triggered by the internal 25-kHz strobe oscillator. See Note 1. |

#### Note:

1. This feature is not tested on the QFN package for the ZL70103 since the QFN is intended for external applications only (for example, base station, programmer, patient controller, or bedside monitoring).

The communication protocol features a power-save timer, which allows the transceiver to enter the IDLE state for a user defined time (0 to 14 seconds) following the transmission of a packet. This is a very useful power saving feature in applications where the IMD does not immediately have data to send and the effective required data rate is lower than the high data rate provided by the ZL70103.

<sup>1.</sup> This feature is not tested on the QFN package for the ZL70103 since the QFN is intended for external applications only (for example, base station, programmer, patient controller, or bedside monitoring).

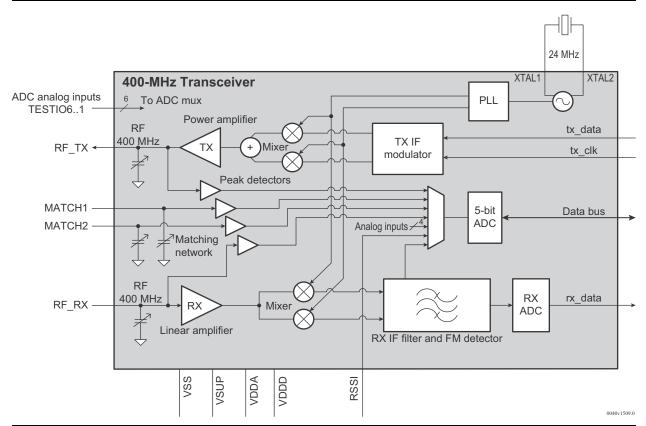

# **400-MHz Transceiver Subsystem**

The transceiver uses a low-intermediate-frequency, superheterodyne architecture with image reject mixers. The low-IF architecture minimizes filter and modulator power consumption without the flicker noise issues associated with zero-IF architectures. An FSK modulation scheme reduces amplifier linearity requirements thereby reducing power consumption. In addition, FSK offers spectral efficiency by producing a high data rate given the MICS band spectrum mask requirements. Image rejection improves the adjacent channel rejection of the system.

Figure 3-4 • 400-MHz Transceiver Subsystem

Due to the relatively high RF path loss in implant applications, it is recommended that customers use the lowest possible data rate to ensure the best possible link quality. The sensitivity for different data rates can be seen in Table 3-3 on page 3-7.

The ZL70103 allows the user to select from a wide range of data rates (18.1818, 40, 200, 400, 800 kbit/s) with varying receiver sensitivity. To facilitate this flexibility, the system uses either 2FSK or 4FSK modulation with 200 or 400kSymbols/s and varying frequency deviations and spreading factors. Table 3-3 on page 3-7 summarizes the allowable modulation modes, respective data rates, and corresponding receiver sensitivity. Please refer to the ZL70103 Design Manual for further information.

| Modulation Mode | Maximum Raw Radio Data<br>Rate (kbit/s) | Maximum Effective<br>Data Rate (kbit/s) | Typical Receiver<br>Sensitivity (Note 1) |

|-----------------|-----------------------------------------|-----------------------------------------|------------------------------------------|

| 2FSK-Barker11   | 18.18                                   | 12.2                                    | −110dBm                                  |

| 2FSK-Barker5    | 40                                      | 26.8                                    | −107dBm                                  |

| 2FSK-fallback   | 200                                     | 134                                     | −102dBm                                  |

| 2FSK            | 400                                     | 265                                     | -91dBm                                   |

| 4FSK (Note 2)   | 800                                     | 515<br>(Note 3)                         | −79dBm                                   |

#### Notes:

- 1. The sensitivity is based on the application circuit in Figure 10-1 on page 10-1, at the reference point of the dual-band antenna (500hm). This value represents a packet error rate of 10%.

- 2. 4FSK is an unevaluated mode for the ZL70103. Specifications for this mode are provided for guidance only. Contact Microsemi Application Support if use of this mode is required.

- 3. Requires calibration of the RX ADC. Refer to the ZL70103 Design Manual for the calibration procedure.

#### **Transmitter Section**

The ZL70103 transmitter consists of an IF modulator, I and Q mixer, and power amplifier.

The IF modulator converts a one-bit (2FSK) or two-bit (4FSK) asynchronous digital input data stream to a 450-kHz FSK-modulated I and Q signal. The IF center frequency of 450 kHz is automatically calibrated using a frequency locked loop (FLL) each time the transceiver is woken up.

An up-converting mixer transforms the IF to RF. Note that the local oscillator frequency is the same for both transmit and receive modes, facilitating a minimum dead time between receiving and transmitting packets. Both low- and high-side injection is used to always keep the image in the MICS band to relax the demands on phase and amplitude matching of the I and Q signals. When the RF is in the lower half of the MICS band, the LO frequency is higher than the transmitted radio frequency. When the RF is in the upper half of the MICS band, the LO frequency is lower than the transmitted radio frequency.

The output power of the TX power amplifier is register-programmable from approximately  $-3\,dBm$  to  $-30\,dBm$  (into a 500-ohm load, dependent on supply voltage). An antenna-matching capacitor bank is provided to fine tune the matching network for maximum delivered output power for a given power setting. The antenna tuning is an automatic calibration that uses a peak detector coupled to an ADC along with a state machine for calibration control.

#### **Receiver Section**

The ZL70103 400-MHz receiver amplifies the MICS-band signal and down-converts from the carrier frequency to the intermediate frequency (IF) using an I/Q image reject mixer. The LNA gain is programmable from 11 to 33dB in approximately 3-dB steps. The maximum gain settings are recommended for IMD transceivers, while the lower gain settings may be applicable to base station transceivers that choose to use an external LNA. Programmability of LNA and mixer bias currents provides further flexibility in optimizing for desired linearity (IIP3), power consumption, and noise figure.

An image-rejecting I/Q polyphase IF filter is used to suppress interference at the image frequency and adjacent channels and limit the noise bandwidth. The polyphase filter is followed by limiters and a Received Signal Strength Indicator (RSSI) block. The RSSI measurement is converted by a five-bit ADC and may be read by the SPI bus interface. To fulfill the regulatory requirements for performing the MICS-band clear channel assessment, the user has to port out the IF signal via the TESTIO pins. The RSSI measurement then uses off-chip components, available in the base station, to perform a measurement with higher resolution than the on-chip RSSI.

The RSSI block on the ZL70103 can be trimmed to obtain an optimum absolute accuracy. This is done once in production by applying a known external signal on RX and calibrating the RSSI offset with the trim bits.

An FM detector converts frequency deviation to voltage levels. The resulting baseband signal is subsequently low-pass filtered to remove the fourth harmonic of the IF and then digitized by a two-bit quantizer. The resulting data stream is provided to the MAC for correlation and clock recovery.

Before the packet, a sequence of training words are received. A DC removal circuit prior to the quantizer adjusts the DC level during the training phase. The purpose of this adjustment is to remove DC offset due to reference frequency differences between the base station and IMD transceivers.

Each packet begins with a 40-bit correlation sequence. If the frame sync match criteria is met, the DC level is fixed for the remainder of the packet. The value of the training and correlation word is programmable as well as the number of training bytes. A programmable capacitor bank is provided on RX to fine-tune the matching network. This function is intended to be used when RX and TX are separated in the matching network, as is typical in a base station.

Two additional programmable capacitor banks (MATCH1 and MATCH2) are provided to further facilitate tuning of the matching network. Refer to the ZL70103 Design Manual for further details.

### **Frequency Synthesizer**

The frequency synthesizer is a PLL structure with an RF Voltage Controlled Oscillator (VCO) running at four times the LO frequency. The I/Q Local Oscillator (LO) signals are derived from the VCO signal and distributed to the receive and transmit front-end. The VCO is divided down and locked to the reference frequency, which is supplied by the crystal oscillator running at 24MHz with an external crystal. The synthesizer uses both high- and low-side injection to ensure that the image frequency is always within the MICS band. The channel number is programmable from 0 to 9 for the 402- to 405-MHz MICS band and from 10 to 11 for 433.65 and 434.25MHz in the ISM band; please refer to Table 3-4 for details.

Table 3-4 • MICS/ISM Channel Table

| Channel Number | Center Frequency (MHz) | Frequency Band |  |  |

|----------------|------------------------|----------------|--|--|

| 0              | 402.15                 | MICS           |  |  |

| 1              | 402.45                 | MICS           |  |  |

| 2              | 402.75                 | MICS           |  |  |

| 3              | 403.05                 | MICS           |  |  |

| 4              | 403.35                 | MICS           |  |  |

| 5              | 403.65                 | MICS           |  |  |

| 6              | 403.95                 | MICS           |  |  |

| 7              | 404.25                 | MICS           |  |  |

| 8              | 404.55                 | MICS           |  |  |

| 9              | 404.85                 | MICS           |  |  |

| 10             | 433.65                 | ISM            |  |  |

| 11             | 434.25                 | ISM            |  |  |

# **Crystal Oscillator**

The 24-MHz crystal oscillator (XO) is responsible for generating the system clock used by both the 400-MHz transceiver and the MAC. The required characteristics of the crystal are discussed in detail in the ZL70103 Design Manual. Microsemi has worked closely with leading IMD crystal manufacturers to ensure the availability of implant-grade 24-MHz crystals.

The required XO tolerance is determined by the transmitter and receiver frequency alignment requirements. Analysis of the ZL70103 indicates that the total frequency misalignment should be limited to 31 ppm. The ZL70103 XO has the facility for trimming a  $\pm$ 60-ppm oscillator to within  $\pm$ 10 ppm.

The oscillator may be bypassed by asserting the XO\_BYPASS pin. This enables an external oscillator connected to XTAL1 to provide the 24-MHz frequency. Base stations may then choose to use a very accurate external crystal oscillator (XO) to provide engineering margin in the frequency budget and reduce on-chip frequency trimming requirements. When XO\_BYPASS is asserted, the XO core is powered down and the signal from XTAL1 is provided directly to internal circuitry.

The 24-MHz clock divided by two (12MHz) and a variety of subfrequencies are available on the buffered programmable output pins PO3 and PO4 via register programming.

### **General-Purpose ADC**

A five-bit general-purpose successive approximation ADC with a conversion time of 2µs is provided for the following purposes:

- Measurement of the peak voltage at the 400-MHz PA output. This measurement is used for tuning the antenna matching network.

- Measurement of the peak voltage at the MATCH1 capacitor bank. This is used for tuning the antenna matching network.

- 3. Measurement of the peak voltage at the MATCH2 capacitor bank. This is used for tuning the antenna matching network.

- Measurement of the peak voltage at the 400-MHz RX input. This is used for tuning the antenna matching network.

- Measurement of the internal 400-MHz RSSI signal. The application may find the RSSI measurement useful for automatic gain control or other system optimization methods that require a measurement of received 400-MHz signal strength.

- 6. Measurement of the internal 2.45-GHz RSSI signal. The application may also use this RSSI measurement for system optimization methods that require a measurement of received 2.45-GHz signal strength.

- 7. Supply voltage input. This is a useful system diagnostic measurement. The voltage on VSUP is divided by a resistive divider and measured using the ADC. The resistor divider is disconnected from the battery voltage when the ADC measurement is not selected or the ADC is disabled. Other ADC inputs do not have a resistor divider.

- 8. Measurement of inputs from analog TESTIO bus. One of four TESTIO pins, TESTIO4 to TESTIO1, may be selected for input into the ADC. This provides a useful general-purpose ADC function for the application. The ADC may be used to measure application specific physiological signals or system diagnostic signals.

A programmable multiplexer on the input of the ADC selects between the different measurements.

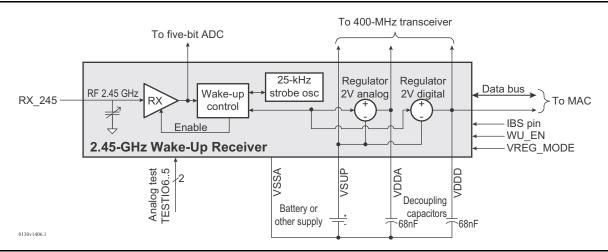

# 2.45-GHz Wake-Up Receiver

The 2.45-GHz receiver is used for a low-power wake-up system. The block diagram is shown as Figure 3-5, followed by a description of the basic operation.

Figure 3-5 • 2.45-GHz Wake-Up Receiver Subsystem

Note: This feature is not tested on the QFN package for the ZL70103 since the QFN is intended for external applications only (for example, base station, programmer, patient controller, or bedside monitoring).

### **Basic Operation**

Most implant applications use the MICS-band RF link infrequently due to the overriding need to conserve battery power. In very low-power applications, the ZL70103 spends most of the time asleep in a very low-current state. Except for the sending of an emergency command in case of a medical event or using the low-duty-cycle mode, systems that use the MICS band must first wait for the base station to initiate communications following a CCA procedure in which the base station determines which channel to use.

Therefore, periodically, the IMD transceiver should listen for a base station that wants to begin communication. This sniffing operation should be frequent enough to provide reasonable startup latency, consume a very low current since it occurs regularly, and be immune to noise sources that invoke an erroneous startup.

For a very low-power receiver, an OOK modulation scheme is used since it removes the need for a local oscillator and synthesizer in the receiver. Further simplification, and hence power savings, is gained by using a frequency band that is of reasonable power for the startup process. The 2.45-GHz ISM band satisfies such a requirement by allowing up to 36dBm (100mW) or 26dBm (10mW) EIRP higher power than the MICS band, depending on each country's regulatory limits.

The wake-up system uses a novel ultra-low-power RF receiver, operating in the 2.45-GHz ISM band, to read OOK transmitted data. The main functions are: to detect and decode a specific data packet that is transmitted from a base station, and then to switch on the supply to the rest of the chip (the MAC block and the RF block, referred to collectively as the *core* in this document).

To reduce the average current consumption of the wake-up subsystem, the wake-up system is strobed by either:

- 1. An application-generated strobe pulse applied to the WU\_EN pin to enable the wake-up circuitry. This minimizes the sleep current (I<sub>sleep</sub> typically approximately 10nA) to the leakage current.

- 2. An internally generated strobe pulse created using a low-power (typically 310-nA), internal, 25-kHz strobe oscillator. The total sleep current with the 25-kHz strobe oscillator is therefore typically 320 nA (I<sub>strosc</sub>).

The average sleep/sniff current consumption for a system using an external strobe is:

$$I_{wu245\_ext} = I_{sleep} + I_{wu245} = 10 + 280 = 290 \text{ nA}$$

The average sleep/sniff current consumption for a system using the internal 25-kHz strobe oscillator is:

$$I_{wu245 \text{ int}} = I_{strosc} + I_{wu245} = 320 + 280 = 600 \text{ nA}$$

Figure 3-6 • Strobing of Wake-Up System

The actual current depends significantly on the timing of the strobe and the programming of the 2.45-GHz receiver. The power supply to both the digital and analog parts in the wake-up block is the VSUP voltage (2.05V to 3.5V).

The external strobe (WU\_EN) and internal oscillator strobe are ORed such that either one (or both) may generate a wake-up strobe at any time when the device is asleep.

The data packet that is sent from the base station to the IMD transceiver is Manchester encoded and OOK modulated. The transmitted data packet is encoded with clock and data information. A simple decoder block is used to extract the clock information and sample the data using the recovered clock.

If an OOK-modulated signal with the correct timing is detected during the sniff period (T<sub>strobe\_width</sub>), the system continues to operate and searches for the start of the pattern indicated by a unique non-Manchester-encoded pattern of 11110000. After the start sequence is found, a complete packet of data is analyzed. If corrupted data is received, the wake-up controller terminates reception and powers down. Furthermore, if the received signal is lost during reception, a watchdog circuit terminates reception and powers down the wake-up receiver.

On successful detection and decoding of a valid packet of data, the wake-up receiver is turned off and the on-chip 2-V voltage regulators are enabled. Two voltage regulators are used (one for the analog core supply and one for the digital core supply) to separate the digital and analog supplies. The two voltage regulator outputs are available on two pins, VDDA and VDDD. Each voltage regulator requires one 68- to 200-nF capacitor for regulator stability.

After the regulators are fully on, the wake-up receiver is shut down and the crystal oscillator starts up, followed by the MAC. On successful core power up (where success is defined by whether the MAC is running) the MAC replies to the wake-up subsystem that it is ready and performs a CRC check of the wake-up memory, copies registers to the MAC, and performs calibrations. A communication session then occurs at 400MHz. When the communication session is no longer required, the application puts the IMD into the SLEEP state via register control, thus powering down the core and returning the wake-up subsystem to periodic sniffing for a wake-up packet.

As mentioned in the "Basic Modes" section on page 3-1, there are various methods for waking up the transceiver. The wake-up controller, by monitoring the IBS and WU\_EN pins, controls the selection of the various wake-up methods. Note that when the IBS pin is high (base-idle mode), the wake-up controller enables the regulated supply (VDDA and VDDD) throughout operation and the wake-up receiver remains disabled.

When the battery is connected for the first time, a POR block (wake\_por) resets all digital registers and flip flops in the wake-up subsystem.

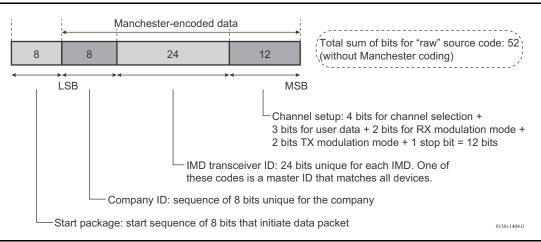

### 2.45-GHz Wake-Up Data Packet Definition

The data packet content is shown in Figure 3-7. The information is used by the IMD to set up the 400-MHz transceiver for communication on the appropriate channel and modulation mode.

The raw data is Manchester encoded (where a 0 is encoded as 01, a 1 is encoded as 10) since such a coding scheme can convey clock information, thus permitting the wake-up receiver to operate without a high-frequency clock and therefore save power. The OOK modulation pattern is provided on the PO0 pin by appropriately programming the output and writing a 1 to bit 0 of  $reg_mac_initcom$ . This OOK modulation pattern may be used by the external base station's 2.45-GHz transmitter. The contents of the wake-up pattern are set by programming various registers in the base station ZL70103 transceiver. The total wake-up packet length is typically 3.072ms. Further details of the wake-up packet are described in the ZL70103 Design Manual.

Figure 3-7 • The Data Packet Definition

The wake-up packet contains a company ID (assigned by Microsemi) and a IMD transceiver ID to identify the target IMD for communication.

The 12 bits after the IMD transceiver ID consist of channel setup information required to establish a 400-MHz communication session. This information is sent to the MAC if a correct company ID and IMD transceiver ID is detected.

The channel setup information is Manchester encoded as per the rest of the data packet and therefore no additional error checking is considered necessary. The probability is very low that these last 12 bits would be incorrectly detected following a correct company ID and IMD transceiver ID. Furthermore, any error would simply manifest as a delayed wake-up (it would need to be repeated).

# **Media Access Controller (MAC)**

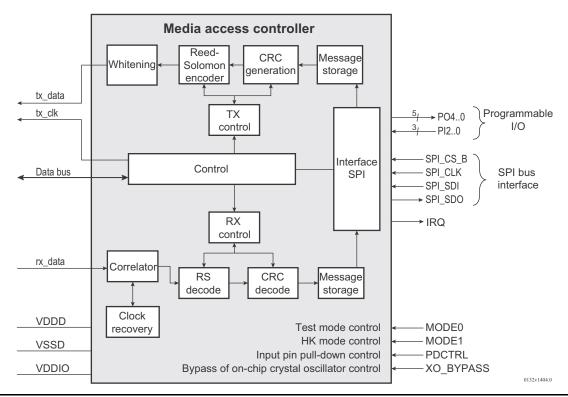

The MAC is a digital subsystem that controls the data communication and application interface. The block diagram in Figure 3-8 is followed by a description of the basic operation.

Figure 3-8 • Media Access Controller Subsystem

# **Basic Operation**

The MAC consists of four main subsystems including:

- 1. Transmitter processing

- 2. Receiver processing

- 3. Communication control sequencer

- 4. Application interface

The <u>transmit processing</u> is fed by a 64×113-bit storage buffer capable of storing two maximally sized packets. The buffer is written through the SPI bus interface. The TX control constructs a data packet when more than one block of data exists in the transmit buffer. The definition of a data packet is contained in the "400-MHz Packet Definition" section on page 3-13. A cyclic redundancy code (CRC) is appended to the data and the result is passed through a Reed-Solomon (RS) block that provides extensive forward error correction. The final stage of transmission processing is to perform whitening using a pseudonoise (PN) method. Whitening ensures that the data has sufficient transitions for accurate operation of the clock recovery.

The <u>receiver processing</u> fills up a 64×113-bit storage buffer capable of storing two maximally sized packets. Again, the buffer is read through the SPI bus interface. The receiver performs clock recovery and identifies the correlation word signifying the start of a packet. Upon receipt of a packet, a Reed-Solomon decoder performs forward error correction on the header and each of the blocks that constitute a packet. The RS is capable of correcting up to 15 consecutive bit errors within a block. After error correction, a CRC decoder identifies blocks that contain uncorrectable errors and forwards the information on which blocks require retransmission to the transmit controller and main sequencer.

The <u>communication control sequencer</u> implements and controls the overall ZL70103 communication protocol. The features offered by the protocol include:

- Correction and detection of errors (FEC and CRC)

- Automatic retransmission of data blocks in error (ACK/NACK)

- · Automatic flow control to prevent buffer overflow

- Automatic setup of modulation modes and reply to wake-up responses

- · Facility to flush old data (which is useful when sending real-time ECG data in poor link conditions)

- · Capable of sending MICS-band emergency command

- Minimization of collisions from multiple implants during wake-up responses

- Ability to send high-priority housekeeping messages

- · Handling of link watchdog to ensure link is shut down after 5 seconds without successful communication

- Provision of link quality diagnostics

- · Backup of important registers to wake-up block and CRC checking of memory

- · Control of automatic calibrations

- Low-duty-cycle mode

The rich feature set of the ZL70103 communication protocol relieves the user application of many link maintenance activities. The communication link is simply viewed as a receive-and-transmit buffer accessible via the SPI bus interface. Buffer conditions that require user attention are flagged by interrupts, allowing the user to optimally maintain data flow. The user may also choose to poll buffer status registers as an alternative to handling interrupts.

The <u>application interface</u> is discussed in more detail in chapter "5 – Application Interface" on page 5-1.

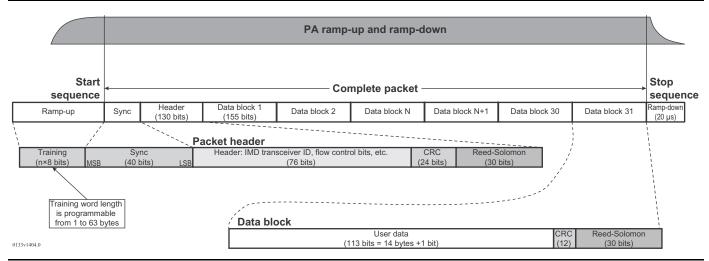

#### 400-MHz Packet Definition

The packet definition is chosen to enable a high effective data rate. The packet header should be kept as small as possible and the payload should be as large as possible. The same packet definition is used in both the uplink and downlink. The basis for the packet definition and the link protocol is fully described in the ZL70103 Design Manual.

Figure 3-9 • Packet Definition (first in time on the left side)

Before the packet is transmitted a start sequence is applied to allow the PA to ramp up to full amplitude. During this period, training words are generated (and transmitted when the PA starts to ramp). The training words serve two purposes:

- 1. To form the signal during PA ramp

- 2. To provide the DC removal circuit with a training word for calibration after the PA is fully ramped

It is necessary to send sufficient training words so that the DC removal circuit can settle after the PA is fully ramped and before the packet is transmitted. The chip is preconfigured with default values for number of training words depending on chosen modulation.

The training sequence is followed by a 40-bit synchronization word defined by the registers  $reg\_mac\_sync5..1$ . The number of bits that must match in the synchronization word is specified by the register  $reg\_mac\_syncmatch$ . The default value of this register is 36 (8'h24), which allows a maximum of four errors in the synchronization word. The sliding correlator in the receiver checks against a known pattern. The synchronization word has been chosen so that its auto correlation is high only for zero lag.

The packet header contains flow control information that handles the automatic retransmissions of blocks in error, the prevention of receiver buffer overflow, packet acknowledgement, HK-related bits, channel info, and other protocol details. These are fully described in the ZL70103 Design Manual. The header also contains the IMD transceiver ID, which is a unique 24-bit code that identifies the implant, and the company ID, which is a code with eight bits that are unique to the company. The entire header is protected by a Reed-Solomon code and 24-bit CRC.

The header has a stronger CRC protection than the data since it is important that there are no undetected header errors. Undetected header errors would cause erroneous link operation depending on the header bits in error.

Each data block consists of 113 bits of effective data (14 bytes plus 1 bit). The single additional bit may be used by the application in a transport layer for indicating the start of the users packet. The data block is protected by a 12-bit CRC. The resulting bits are protected by 30 bits of RS error correcting code.

The maximum number of blocks in a data packet is programmable (1 to 31) via the register  $reg\_txbuff\_maxpacksize$ . The system sends less than the maximum number of blocks if data is available in the TX buffer. In other words, data is sent as soon as it is available, provided that at least one block exists in the TX buffer. The register  $reg\_txbuff\_maxpacksize$  only sets a limit on the maximum blocks in a packet.

The number of bytes in a TX or RX block that needs to be transferred from the SPI bus interface is programmable (reg\_rxbuff\_bsize, reg\_txbuff\_bsize) as described in the "Serial Peripheral Interface" section on page 5-1. There are always 113 bits sent in a data block but some of these bits are padded zeroes if the number of bytes in a block is set to less than the maximum value of 15. When using all 113 bits (14 bytes plus 1 bit, where block size set to 15) then the LSB of the first byte sent by the SPI bus interface is used for the additional single bit. This single bit is not used when the block size is less than 15.

# 4 - System Reliability Features

# System Integrity — Watchdogs

The ZL70103 has three watchdogs that prevent the device from consuming power under fault conditions or during different operating states.

The system timing varies at different stages of the ZL70103 transceiver operation, which leads to three different watchdogs as described in Table 4-1. A watchdog of some type is always operating in the ZL70103.

Table 4-1 • Summary of Watchdogs

| Watchdog                                                   | Purpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Wake-up watchdog<br>(IMD only)                             | <ul> <li>Ensures that the wake-up block is not unnecessarily active. The block is shut do</li> <li>a loss of the 2.45-GHz signal and clock is detected.</li> <li>a wake-up signal with valid modulation and timing is received but no start pais found within a time longer than 2.5 times the wake-up packet width.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Transceiver initialization watchdog (base station and IMD) | Ensures that the system is put to sleep (IMD) or restarted (base station) in the event of failure of the 24-MHz crystal or in some other condition in which the MAC fails to start. This does not prevent the application from unwanted power consumption if the application firmware is trying to wake up the chip again.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Main watchdog<br>(base station and IMD)                    | Ensures that the link is shut down after 5 seconds if no header is received. The MICS standard requires that a previously established link must cease transmission if no communication has occurred for a period of 5 seconds. This watchdog also ensures that a device in the IDLE state has serial interface communication with the application. The application is notified by an interrupt that occurs 0.6 second before the link is shutdown and the IMD is put to sleep. The application may override the shutdown by resetting the watchdog. During initial software development, it is very convenient to disable the watchdog. Methods of disabling the watchdog are discussed in the ZL70103 Design Manual. |  |  |  |  |

# **Memory Integrity — CRC Check of Registers**

The MAC or application can perform a CRC check of selected registers in the wake-up block. The MAC normally does this action automatically at startup and the user may also perform the CRC check anytime the MAC is powered. The CRC check includes all registers labelled in the memory map for CRC checking.

The CRC operation is controlled by the register  $reg\_wakeup\_crcctrl$ . The user may initiate a check of the CRC using a control bit, and status bits indicate whether the CRC check passed or failed. The user can also calculate a new CRC word using a control bit, and a status bit indicates that the calculation is complete. The application should control the copying of registers to the wake-up stack using the "copy registers" control bit in  $reg\_mac\_ctrl$ . It is recommended that such copying only occur following a successful communication session, since the register settings have been verified as operational; however, the application processor should always keep a duplicate copy of the registers in the wake-up block in case either a CRC error is detected at wake-up or a full chip reset is required. It is also possible to read and write to a single register in the wake-up stack since the stack is addressable using the register  $reg\_wakeup\_stack\_addr$ . See the memory map in the ZL70103 Design Manual for more details and requirements regarding the operation of the CRC control register.

# **Communication Link Integrity**

The following features of the ZL70103 contribute to a high communication link integrity:

- The RS forward error correction and CRC provide for excellent final BER performance.

- Individual acknowledgement and retransmission of data blocks is automatically handled.

- · The variable receiver sensitivity obtained by different modulation modes is useful for poor link conditions.

- · Link quality diagnostics are available including:

- number of corrected blocks.

- number of blocks with errors detected.

- number of received blocks.

- A link quality interrupt is generated when either the block error or retransmission indicator exceeds programmable thresholds (evaluated per packet).

Details of these features are found in the ZL70103 Design Manual.

# 5 – Application Interface

This section describes the application interface including:

- Serial Peripheral Interface (SPI)

- · Housekeeping messages

- · Interrupts

- Programmable I/O

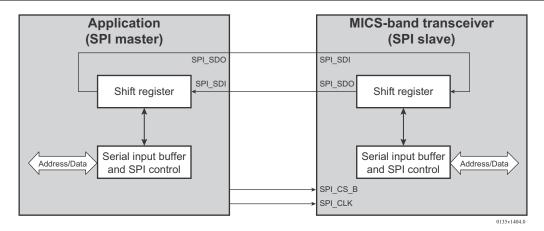

# **Serial Peripheral Interface**

Registers and the TX/RX buffers are programmed via a standard SPI slave interface. The ZL70103 Design Manual contains the full memory map and programming details for the device.

The interface supports "MODE0 slave" operation where data is valid on the first rising edge of SPI\_CLK; the idle state of SPI\_CLK is low as shown in the basic timing diagrams in Figure 5-2 and Figure 5-3 on page 5-2. The default maximum SPI\_CLK rate is 4MHz. A register (*reg\_interface\_mode*) may be programmed to decrease this operating speed down to 1 or 2MHz to reduce power consumption.