#### DAC7568, DAC8168, DAC8568

SBAS430F - JANUARY 2009 - REVISED APRIL 2018

# DAC7568, DAC8168, DAC8568 12-/14-/16-Bit, Octal-Channel, Ultralow Glitch, Voltage Output, Digital-to-Analog Converters with 2.5-V 2-ppm/°C Internal Reference

#### **Features**

Relative Accuracy:

DAC7568 (12-Bit): 0.3 LSB INL

DAC8168 (14-Bit): 1 LSB INL

DAC8568 (16-Bit): 4 LSB INL

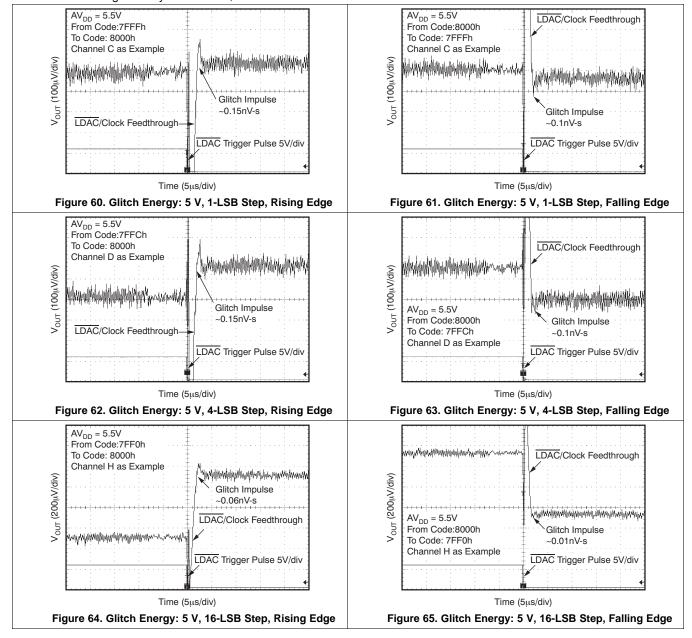

Glitch Energy: 0.1nV-s

Internal Reference:

2.5V Reference Voltage (disabled by default)

0.004% Initial Accuracy (typ)

2ppm/°C Temperature Drift (typ)

5ppm/°C Temperature Drift (max)

20mA Sink/Source Capability

Power-On Reset to Zero Scale or Midscale

Ultralow Power Operation: 1.25mA at 5V Including Internal Reference Current

Wide Power-Supply Range: +2.7V to +5.5V

Monotonic Over Entire Temperature Range

Low-Power Serial Interface with Schmitt-Triggered Inputs: Up to 50MHz

On-Chip Output Buffer Amplifier with Rail-to-Rail Operation

Temperature Range: -40°C to +125°C

# **Applications**

- Portable Instrumentation

- Closed-Loop Servo-Control/Process Control

- **Data Acquisition Systems**

- Programmable Attenuation, Digital Gain, and Offset Adjustment

- Programmable Voltage and Current Sources

# Description

The DAC7568, DAC8168, and DAC8568 are lowpower, voltage-output, eight-channel, 12-, 14-, and digital-to-analog 16-bit converters (DACs), respectively. These devices include a 2.5V, 2ppm/°C internal reference (disabled by default), giving a fullscale output voltage range of 2.5V or 5V. The internal reference has an initial accuracy of 0.004% and can source up to 20mA at the  $\dot{V}_{REF}IN/V_{REF}OUT$  pin. These devices are monotonic, providing excellent linearity and minimizing undesired code-to-code transient voltages (glitch). They use a versatile 3-wire serial interface that operates at clock rates up to 50MHz. The interface is compatible with standard SPI™, QSPI™, Microwire™, and digital signal processor (DSP) interfaces.

The DAC7568, DAC8168, and DAC8568 incorporate a power-on-reset circuit that ensures the DAC output powers up at either zero scale or midscale until a valid code is written to the device. These devices contain a power-down feature, accessed over the serial interface, that reduces current consumption to typically 0.18µA at 5V. Power consumption (including internal reference) is typically 2.9mW at 3V, reducing to less than 1µW in power-down mode. The low power consumption, internal reference, and small footprint make these devices ideal for portable, battery-operated equipment.

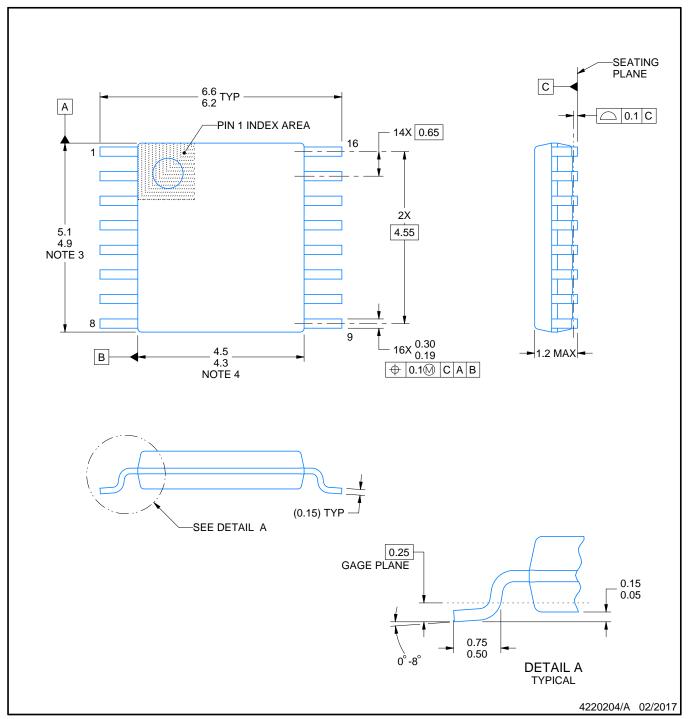

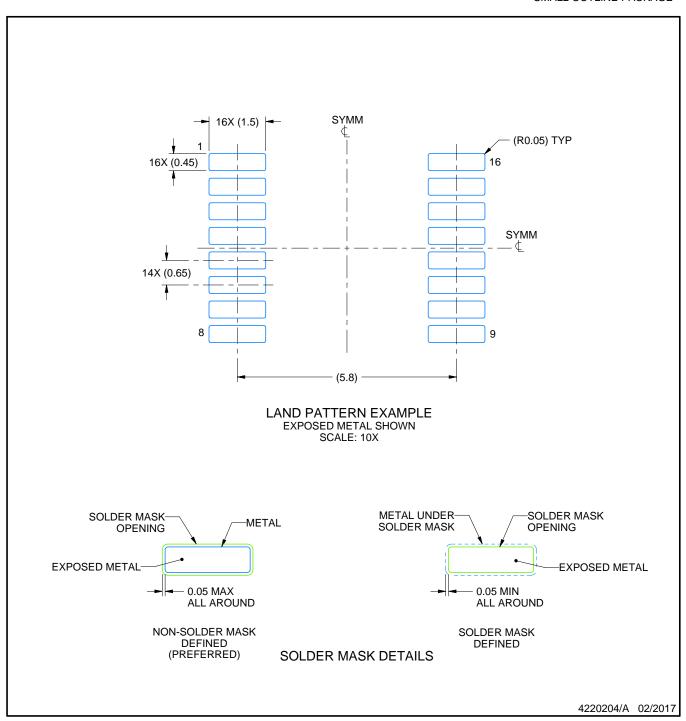

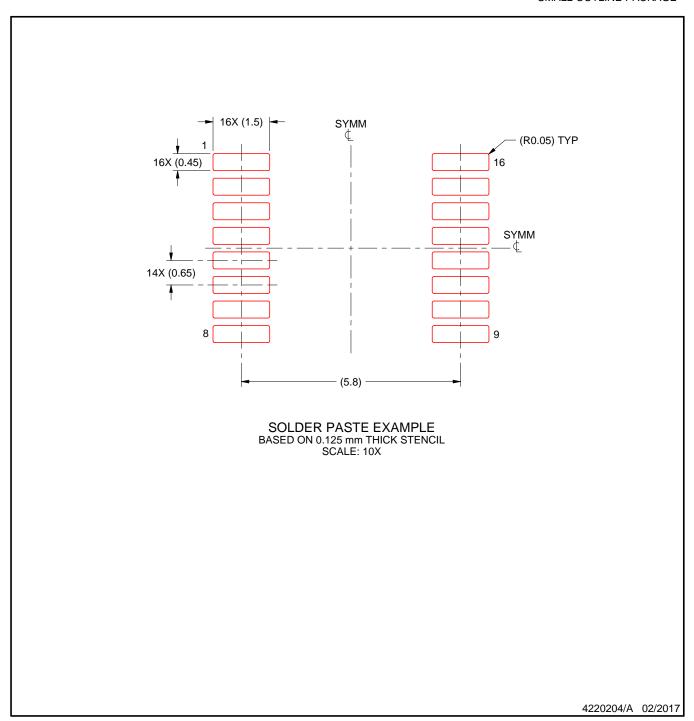

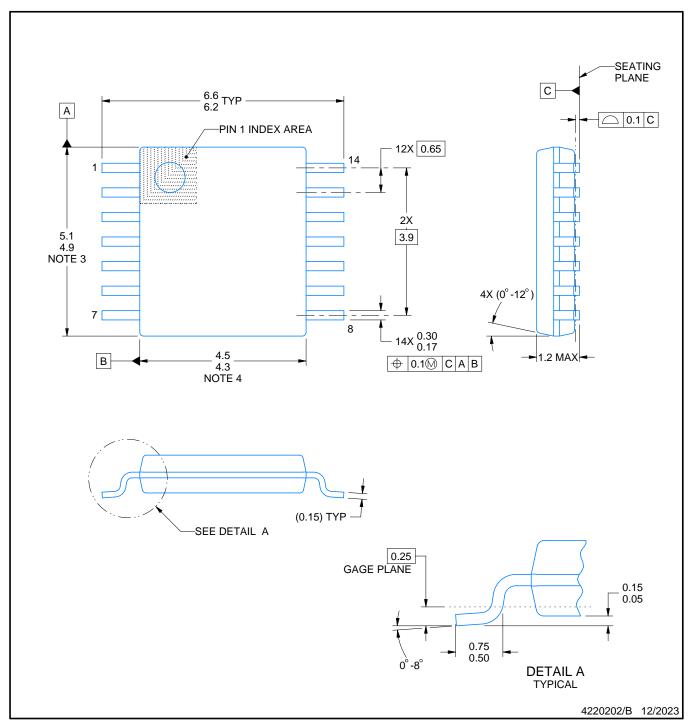

The DAC7568, DAC8168, and DAC8568 are drop-in and function-compatible with each other, and are available in TSSOP-16 and TSSOP-14 packages.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |  |  |  |  |  |

|-------------|------------|-------------------|--|--|--|--|--|

| DAC7568     | TSSOP (14) | 5.00 mm x 4.40 mm |  |  |  |  |  |

| DAC7506     | TSSOP (16) | 5.00 mm x 4.40 mm |  |  |  |  |  |

| DAC8168     | TSSOP (14) | 5.00 mm x 4.40 mm |  |  |  |  |  |

| DAC8168     | TSSOP (16) | 5.00 mm x 4.40 mm |  |  |  |  |  |

| DAC8568     | TSSOP (16) | 5.00 mm x 4.40 mm |  |  |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

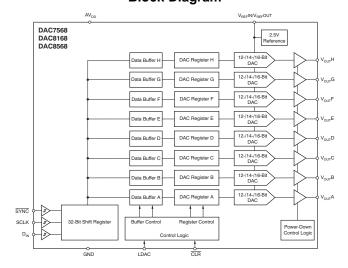

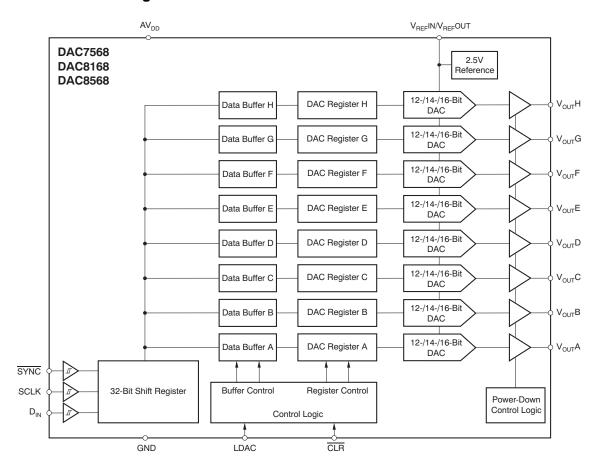

## **Block Diagram**

| Table of Contents |

|-------------------|

|-------------------|

| 1 | Features 1                                                                                  |    | 8.2 Feature Description                               | . 31                         |

|---|---------------------------------------------------------------------------------------------|----|-------------------------------------------------------|------------------------------|

| 2 | Applications 1                                                                              |    | 8.3 Device Functional Modes                           | . 44                         |

| 3 | Description 1                                                                               | 9  | Application and Implementation                        | 48                           |

| 4 | Revision History2                                                                           |    | 9.1 Application Information                           | . 48                         |

| 5 | Device Comparison Table 3                                                                   |    | 9.2 Typical Applications - Microprocessor Interfacing | . 48                         |

| 6 | Pin Configuration and Functions 4                                                           | 10 | Layout                                                | 53                           |

| 7 | Specifications5                                                                             |    | 10.1 Layout Guidelines                                | . 53                         |

| • | 7.1 Absolute Maximum Ratings                                                                | 11 | Device and Documentation Support                      | . 54<br>. 57<br>. 57<br>. 57 |

| 8 | 7.7 Typical Characteristics: DAC at AV <sub>DD</sub> = 2.7 V 23 <b>Detailed Description</b> | 12 | 11.6 Electrostatic Discharge Caution                  |                              |

|   | 8.1 Functional Block Diagram31                                                              |    | Information                                           | 58                           |

|   |                                                                                             |    |                                                       |                              |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C        | changes from Revision E (January 2014) to Revision F                                                                                                              | Page |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •        | Updated data sheet to SDS standard                                                                                                                                | 1    |

| •        | Added External reference current grades and updated typ values                                                                                                    | 6    |

| •        | Added Reference input impedance grades and updated typ values                                                                                                     | 6    |

| •        | Changed $I_{DD}$ Normal mode, internal reference switched on, $AV_{DD} = 3.6V$ to 5.5V, $V_{IN}H = AV_{DD}$ and $V_{IN}L = GNE$ maximum value from 2.0mA to 2.5mA |      |

| C        | changes from Revision D (May 2012) to Revision E                                                                                                                  | Page |

| <u>.</u> | Changed bit value in last three rows of Power-Down Commands section in from '0' to '1'                                                                            | 38   |

| C        | Changes from Revision C (February 2011) to Revision D                                                                                                             | Page |

| <u>.</u> | Changed Logic Input HIGH Voltage parameter test condition into two rows                                                                                           | 7    |

| C        | changes from Revision B (November 2010) to Revision C                                                                                                             | Page |

| •        | Changed Output Voltage parameter min/max values from 2.4895 and 2.5005 to 2.4975 and 2.5025, respective                                                           | 6    |

| •        | Changed Initial Accuracy parameter min/max values from -0.02 and 0.02 to -0.1 and 0.1, respectively                                                               | 6    |

| C        | Changes from Revision A (April 2009) to Revision B                                                                                                                | Page |

| •        | Changed Logic Input LOW Voltage parameter maximum value from 0.8 to 0.3 × AV <sub>DD</sub>                                                                        | 7    |

| •        | Changed Logic Input HIGH Voltage parameter minimum value from 1.8 to 0.7 × AV <sub>DD</sub>                                                                       | 7    |

| •        | Updated Figure 122                                                                                                                                                | 33   |

Submit Documentation Feedback

Copyright © 2009–2018, Texas Instruments Incorporated

# 5 Device Comparison Table

| PRODUCT  | MAXIMUM RELATIVE<br>ACCURACY (LSB) | MAXIMUM DIFFERENTIAL<br>NONLINEARITY (LSB) | MAXIMUM<br>REFERENCE DRIFT<br>(ppm/°C) | OUTPUT VOLTAGE<br>FULL-SCALE RANGE | RESET TO | RESOLUTION |

|----------|------------------------------------|--------------------------------------------|----------------------------------------|------------------------------------|----------|------------|

| DAC8568A | ±12                                | ±1                                         | 25                                     | 2.5V                               | Zero     | 16         |

| DAC8568B | ±12                                | ±1                                         | 25                                     | 2.5V                               | Midscale | 16         |

| DAC8568C | ±12                                | ±1                                         | 5                                      | 5V                                 | Zero     | 16         |

| DAC8568D | ±12                                | ±1                                         | 5                                      | 5V                                 | Midscale | 16         |

| DAC8168A | ±4                                 | ±0.5                                       | 25                                     | 2.5V                               | Zero     | 14         |

| DAC8168C | ±4                                 | ±0.5                                       | 5                                      | 5V                                 | Zero     | 14         |

| DAC7568A | ±1                                 | ±0.25                                      | 25                                     | 2.5V                               | Zero     | 12         |

| DAC7568C | ±1                                 | ±0.25                                      | 5                                      | 5V                                 | Zero     | 12         |

Submit Documentation Feedback

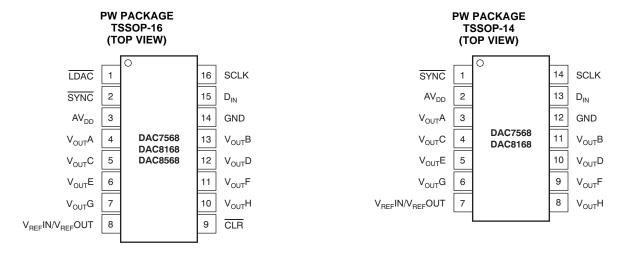

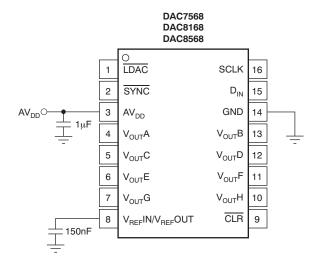

# 6 Pin Configuration and Functions

## **Pin Functions**

| 16-PIN | 14-PIN | NAME                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|--------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | _      | LDAC                                         | Load DACs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2      | 1      | SYNC                                         | Level-triggered control input (active low). This input is the frame synchronization signal for the input data. When \$\overline{SYNC}\$ goes low, it enables the input shift register, and data are sampled on subsequent falling clock edges. The DAC output updates following the 32nd clock. If \$\overline{SYNC}\$ is taken high before the 31st clock edge, the rising edge of \$\overline{SYNC}\$ acts as an interrupt, and the write sequence is ignored by the DAC7568/DAC8168/DAC8568. Schmitt-Trigger logic input. |

| 3      | 2      | $AV_DD$                                      | Power-supply input, 2.7V to 5.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4      | 3      | $V_{OUT}A$                                   | Analog output voltage from DAC A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5      | 4      | $V_{OUT}C$                                   | Analog output voltage from DAC C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6      | 5      | $V_{OUT}E$                                   | Analog output voltage from DAC E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7      | 6      | $V_{OUT}G$                                   | Analog output voltage from DAC G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8      | 7      | V <sub>REF</sub> IN/<br>V <sub>REF</sub> OUT | Positive reference input / reference output 2.5V if internal reference used. (1)                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 9      |        | CLR                                          | Asynchronous clear input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10     | 8      | V <sub>OUT</sub> H                           | Analog output voltage from DAC H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11     | 9      | $V_{OUT}F$                                   | Analog output voltage from DAC F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12     | 10     | $V_{OUT}D$                                   | Analog output voltage from DAC D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 13     | 11     | $V_{OUT}B$                                   | Analog output voltage from DAC B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14     | 12     | GND                                          | Ground reference point for all circuitry on the device                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15     | 13     | D <sub>IN</sub>                              | Serial data input. Data are clocked into the 32-bit input shift register on each falling edge of the serial clock input. Schmitt-Trigger logic input.                                                                                                                                                                                                                                                                                                                                                                        |

| 16     | 14     | SCLK                                         | Serial clock input. Data can be transferred at rates up to 50MHz. Schmitt-Trigger logic input.                                                                                                                                                                                                                                                                                                                                                                                                                               |

(1) Grades A and B, external  $V_{REF}IN$  (max)  $\leq AV_{DD}$ ; grades C and D, external  $V_{REF}IN$  (max)  $\leq AV_{DD}/2$ .

Submit Documentation Feedback

Copyright © 2009–2018, Texas Instruments Incorporated

# 7 Specifications

# 7.1 Absolute Maximum Ratings<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted).

| PARAMETER                                       | MIN                | MAX                     | UNIT |

|-------------------------------------------------|--------------------|-------------------------|------|

| AV <sub>DD</sub> to GND                         | -0.3               | 6                       | V    |

| Digital input voltage to GND                    | -0.3               | AV <sub>DD</sub> + 0.3  | V    |

| V <sub>OUT</sub> to GND                         | -0.3               | AV <sub>DD</sub> + 0.3  | V    |

| V <sub>REF</sub> to GND                         | -0.3               | AV <sub>DD</sub> + 0.3  | V    |

| Operating temperature range                     | -40                | 125                     | °C   |

| Storage temperature range                       | -65                | 150                     | °C   |

| Junction temperature range (T <sub>J</sub> max) |                    | 150                     | °C   |

| Power dissipation                               | (T <sub>J</sub> ma | $ax - T_A)/\theta_{JA}$ | W    |

| Thermal impedance, R <sub>θJA</sub>             |                    | 118                     |      |

| Thermal impedance, $R_{\theta JC}$              |                    | 29                      | °C/W |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 Electrical Characteristics

At AV<sub>DD</sub> = 2.7V to 5.5V and over  $-40^{\circ}$ C to  $+125^{\circ}$ C (unless otherwise noted).

|                 | PARAMETER                 | TEST CONDITIONS                                            | MIN | TYP   | MAX   | UNIT             |

|-----------------|---------------------------|------------------------------------------------------------|-----|-------|-------|------------------|

| STATIC PER      | RFORMANCE <sup>(1)</sup>  |                                                            |     |       | '     |                  |

|                 | Resolution                |                                                            | 16  |       |       | Bits             |

| DAC8568         | Relative accuracy         | Measured by the line passing through codes 485 and 64714   |     | ±4    | ±12   | LSB              |

|                 | Differential nonlinearity | 16-bit monotonic                                           |     | ±0.2  | ±1    | LSB              |

|                 | Resolution                |                                                            | 14  |       |       | Bits             |

| DAC8168         | Relative accuracy         | Measured by the line passing through codes 120 and 16200   |     | ±1    | ±4    | LSB              |

|                 | Differential nonlinearity | 14-bit monotonic                                           |     | ±0.1  | ±0.5  | LSB              |

|                 | Resolution                |                                                            | 12  |       |       | Bits             |

| DAC7568         | Relative accuracy         | Measured by the line passing through codes 30 and 4050     |     | ±0.3  | ±1    | LSB              |

| DAC7568         | Differential nonlinearity | 12-bit monotonic                                           |     | ±0.05 | ±0.25 | LSB              |

| Offset error    |                           | Extrapolated from two-point line <sup>(1)</sup> , unloaded |     | ±1    | ±4    | mV               |

| Offset error of | drift                     |                                                            |     | ±0.5  |       | μV/°C            |

| Full-scale err  | or                        | DAC register loaded with all '1's                          |     | ±0.03 | ±0.2  | % of FSR         |

| Zero-code er    | ror                       | DAC register loaded with all '0's                          |     | 1     | 4     | mV               |

| Zero-code er    | ror drift                 |                                                            |     | ±2    |       | μV/°C            |

| Gain error      |                           | Extrapolated from two-point line <sup>(1)</sup> , unloaded |     | ±0.01 | ±0.15 | % of FSR         |

| Gain tempera    | ature coefficient         |                                                            |     | ±1    |       | ppm of<br>FSR/°C |

(1) 16-bit: codes 485 and 64714; 14-bit: codes 120 and 16200; 12-bit: codes 30 and 4050

Copyright © 2009–2018, Texas Instruments Incorporated Submit Documentation Feedback

## **Electrical Characteristics (continued)**

At  $AV_{DD} = 2.7V$  to 5.5V and over  $-40^{\circ}$ C to  $+125^{\circ}$ C (unless otherwise noted).

| PARAMETER                                          | TEST CONDI                                                                     | TIONS                          | MIN    | TYP    | MAX                                                                           | UNIT               |

|----------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------|--------|--------|-------------------------------------------------------------------------------|--------------------|

| OUTPUT CHARACTERISTICS <sup>(2)</sup>              |                                                                                |                                |        |        |                                                                               |                    |

| Output valtage reage                               | AV <sub>DD</sub> ≥ 2.7V; grades A and B: m<br>2.5V when using internal referer |                                | ٥      |        | ۸۱/                                                                           | V                  |

| Output voltage range                               | AV <sub>DD</sub> ≥ 5V; grades C and D: ma<br>5V when using internal reference  |                                | 0      |        | AV <sub>DD</sub> 10  AV <sub>DD</sub> AV <sub>DD</sub> /2  2.5025  0.1  25  5 | V                  |

|                                                    | DACs unloaded; 1/4 scale to 3/4                                                | scale to ±0.024%               |        | 5      | 10                                                                            |                    |

| Output voltage settling time                       | $R_L = 1M\Omega$                                                               |                                |        | 10     |                                                                               | μS                 |

| Slew rate                                          |                                                                                |                                |        | 0.75   |                                                                               | V/μs               |

| 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2            | R <sub>L</sub> = ∞                                                             |                                |        | 1000   |                                                                               | -                  |

| Capacitive load stability                          | $R_L = 2k\Omega$                                                               |                                |        | 3000   |                                                                               | pF                 |

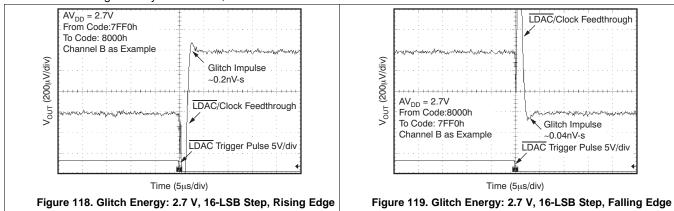

| Code change glitch impulse                         | 1LSB change around major carr                                                  | у                              |        | 0.1    |                                                                               | nV-s               |

| Digital feedthrough                                | SCLK toggling, SYNC high                                                       |                                |        | 0.1    |                                                                               | nV-s               |

|                                                    | $R_L = 2k\Omega, C_L = 470pF, AV_{DD} = 5$                                     | 5.5V                           |        | 10     |                                                                               | mV                 |

| Power-on glitch impulse                            | $R_L = 2k\Omega, C_L = 470pF, AV_{DD} = 2$                                     | 2.7V                           |        | 6      |                                                                               | mV                 |

| Channel-to-channel dc crosstalk                    | Full-scale swing on adjacent cha                                               | annel                          |        | 0.1    |                                                                               | LSB                |

| Channel-to-channel ac crosstalk                    | $R_L = 2k\Omega$ , $C_L = 420pF$ , 1kHz full outputs unloaded                  | -scale sine wave,              |        | -109   |                                                                               | dB                 |

| OC output impedance                                | At mid-code input 4                                                            |                                | Ω      |        |                                                                               |                    |

| Short-circuit current                              | DAC outputs at full-scale, DAC of                                              | outputs shorted to GND         |        | 11     |                                                                               | mA                 |

| Power-up time, including settling time             | Coming out of power-down mod                                                   | е                              |        | 50     |                                                                               | μS                 |

| AC PERFORMANCE <sup>(2)</sup>                      | <u> </u>                                                                       | <br>                           |        |        |                                                                               |                    |

| SNR                                                |                                                                                |                                |        | 83     |                                                                               | dB                 |

| THD                                                | $T_A = +25$ °C, BW = 20kHz, AV <sub>DD</sub>                                   | = 5V, f <sub>OUT</sub> = 1kHz, |        | -63    |                                                                               | dB                 |

| SFDR                                               | first 19 harmonics removed for SNR calculation, at 16-bit level                |                                |        | 63     |                                                                               | dB                 |

| SINAD                                              |                                                                                |                                |        | 62     |                                                                               | dB                 |

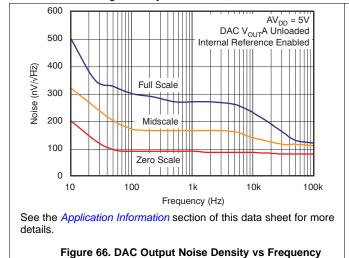

| DAC output noise density                           | T <sub>A</sub> = +25°C, at zero-code input,                                    | f <sub>OUT</sub> = 1kHz        |        | 90     |                                                                               | nV/√ <del>Hz</del> |

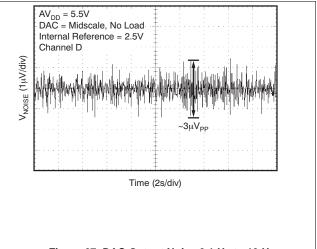

| DAC output noise                                   | $T_A = +25$ °C, at mid-code input, 0                                           |                                |        | 2.6    |                                                                               | μV <sub>PP</sub>   |

| REFERENCE                                          |                                                                                |                                |        |        |                                                                               |                    |

|                                                    | $AV_{DD} = 5.5V$                                                               |                                |        | 360    |                                                                               | μА                 |

| nternal reference current consumption              | AV <sub>DD</sub> = 3.6V                                                        |                                |        | 348    |                                                                               | μА                 |

|                                                    | External V <sub>REF</sub> = 2.5V (when                                         | Grades A/B                     |        | 60     |                                                                               | •                  |

| External reference current                         | internal reference is disabled), all eight channels active                     | Grades C/D                     |        | 115    |                                                                               | μА                 |

| / IN Deference input rongs                         | Grades A/B, AV <sub>DD</sub> = 2.7V to 5.5                                     | V                              | 0      |        | $AV_{DD}$                                                                     | V                  |

| / <sub>REF</sub> IN Reference input range          | Grades C/D, $AV_{DD} = 5.0V$ to 5.5                                            | V                              | 0      |        | AV <sub>DD</sub> /2                                                           | V                  |

| Poforonoo input impadanas                          | Grades A/B                                                                     |                                |        | 44     |                                                                               | 1.0                |

| Reference input impedance                          | Grades C/D                                                                     |                                |        | 22     |                                                                               | kΩ                 |

| REFERENCE OUTPUT                                   |                                                                                |                                |        |        |                                                                               |                    |

| Output voltage                                     | T <sub>A</sub> = +25°C; all grades                                             |                                | 2.4975 | 2.5    | 2.5025                                                                        | V                  |

| nitial accuracy                                    | T <sub>A</sub> = +25°C, all grades                                             |                                | -0.1   | ±0.004 | 0.1                                                                           | %                  |

| Output walks as Assess 1 177                       | DAC7568/DAC8168/DAC8568 <sup>(3)</sup>                                         | ),grades A/B                   |        | 5      | 25                                                                            | 100                |

| Output voltage temperature drift                   | DAC7568/DAC8168/DAC8568 <sup>(4)</sup>                                         | ), grades C/D                  |        | 2      | 5                                                                             | ppm/°C             |

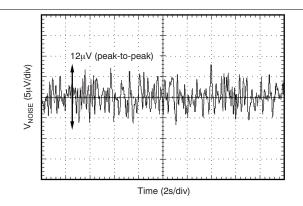

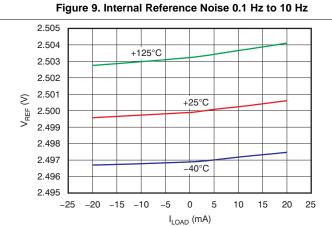

| Output voltage noise                               | f = 0.1Hz to 10Hz                                                              |                                |        | 12     |                                                                               | $\mu V_{PP}$       |

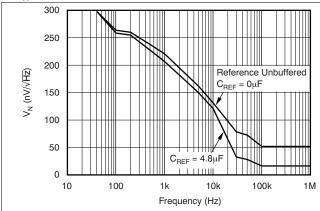

|                                                    | $T_A = +25^{\circ}C$ , $f = 1MHz$ , $C_L = 0\mu F$                             |                                |        | 50     |                                                                               |                    |

| Output voltage noise density high-frequency noise) | $T_A = +25$ °C, $f = 1$ MHz, $C_L = 1$ $\mu$ F                                 |                                |        | 20     |                                                                               | nV/√ <del>Hz</del> |

| ingi nequency noise)                               | $T_A = +25$ °C, $f = 1$ MHz, $C_L = 4\mu$ F                                    |                                |        | 16     |                                                                               |                    |

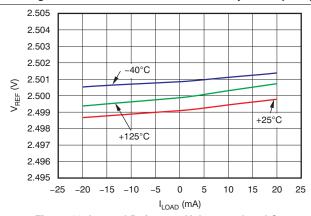

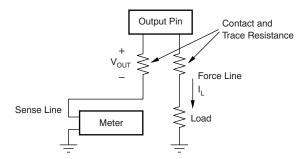

| Load regulation, sourcing <sup>(5)</sup>           | T <sub>A</sub> = +25°C                                                         |                                |        | 30     |                                                                               | μV/mA              |

| Load regulation, sinking <sup>(5)</sup>            | T <sub>A</sub> = +25°C                                                         |                                |        | 15     |                                                                               | μV/mA              |

|                                                    |                                                                                |                                |        |        |                                                                               | •                  |

- (2) Specified by design or characterization; not production tested.

- (3) Reference is trimmed and tested at room temperature, and is characterized from -40°C to +125°C.

- (4) Reference is trimmed and tested at two temperatures (+25°C and +105°C), and is characterized from -40°C to +125°C.

- (5) Explained in more detail in the *Application Information* section of this data sheet.

Submit Documentation Feedback

Copyright © 2009–2018, Texas Instruments Incorporated

6

# **Electrical Characteristics (continued)**

At  $AV_{DD}$  = 2.7V to 5.5V and over -40°C to +125°C (unless otherwise noted).

|                                   | PARAMETER                                   | TEST CONDITIONS                                                         | MIN                      | TYP  | MAX                  | UNIT |

|-----------------------------------|---------------------------------------------|-------------------------------------------------------------------------|--------------------------|------|----------------------|------|

| Output current                    | load capability (2)                         |                                                                         |                          | ±20  |                      | mA   |

| Line regulation                   | 1                                           | $T_A = +25$ °C                                                          |                          | 10   |                      | μV/V |

| Long-term stat                    | oility/drift (aging) (5)                    | $T_A = +25$ °C, time = 0 to 1900 hours                                  |                          | 50   |                      | ppm  |

| Thermal hysteresis <sup>(5)</sup> |                                             | First cycle                                                             |                          | 100  |                      |      |

| i nermai nyste                    | resis                                       | Additional cycles                                                       |                          | 25   |                      | ppm  |

| LOGIC INPUT                       | S <sup>(2)</sup>                            |                                                                         | 1                        |      |                      |      |

| Input current                     |                                             |                                                                         |                          | ±1   |                      | μА   |

| V <sub>IN</sub> L                 | Logic input LOW voltage                     | $2.7V \le AV_{DD} \le 5.5V$                                             |                          |      | $0.3 \times AV_{DD}$ | V    |

|                                   |                                             | $2.7V \le AV_{DD} < 4.5V$                                               | $0.7 \times AV_{DD}$     |      |                      | V    |

| V <sub>IN</sub> H                 | Logic input HIGH voltage                    | $4.5V \le AV_{DD} \le 5.5V$                                             | 0.625 × AV <sub>DD</sub> |      |                      | V    |

| Pin capacitano                    | e                                           |                                                                         |                          |      | 3                    | pF   |

| POWER REQU                        | UIREMENTS                                   |                                                                         | 1                        |      |                      |      |

| AV <sub>DD</sub>                  |                                             |                                                                         | 2.7                      |      | 5.5                  | V    |

|                                   | Normal mode, internal                       | $AV_{DD} = 3.6V$ to $5.5V$<br>$V_{IN}H = AV_{DD}$ and $V_{IN}L = GND$   |                          | 0.95 | 1.4                  | mA   |

| -                                 | reference switched off                      | $AV_{DD}$ = 2.7V to 3.6V<br>$V_{IN}H$ = $AV_{DD}$ and $V_{IN}L$ = GND   |                          | 0.81 | 1.3                  |      |

| IDD (9)                           | Normal mode, internal reference switched on | $AV_{DD} = 3.6V$ to $5.5V$<br>$V_{IN}H = AV_{DD}$ and $V_{IN}L = GND$   |                          | 1.25 | 2.5                  | mA   |

|                                   |                                             | $AV_{DD}$ = 2.7V to 3.6V<br>$V_{IN}H$ = $AV_{DD}$ and $V_{IN}L$ = GND   |                          | 1.1  | 1.9                  |      |

|                                   |                                             | $AV_{DD} = 3.6V$ to $5.5V$<br>$V_{IN}H = AV_{DD}$ and $V_{IN}L = GND$   |                          | 0.18 | 3                    |      |

|                                   | All power-down modes                        | $AV_{DD}$ = 2.7V to 3.6V<br>$V_{IN}H$ = $AV_{DD}$ and $V_{IN}L$ = $GND$ |                          | 0.10 | 2.5                  | μА   |

|                                   | Normal mode, internal                       | $AV_{DD} = 3.6V$ to $5.5V$<br>$V_{IN}H = AV_{DD}$ and $V_{IN}L = GND$   |                          | 3.4  | 7.7                  | 10/  |

|                                   | reference switched off                      | $AV_{DD} = 2.7V$ to 3.6V<br>$V_{IN}H = AV_{DD}$ and $V_{IN}L = GND$     |                          | 2.2  | 4.7                  | mW   |

| Power                             | Normal mode, internal                       | $AV_{DD} = 3.6V$ to $5.5V$<br>$V_{IN}H = AV_{DD}$ and $V_{IN}L = GND$   |                          | 4.5  | 11                   |      |

| dissipation <sup>(6)</sup>        | reference switched on                       | $AV_{DD}$ = 2.7V to 3.6V<br>$V_{IN}H$ = $AV_{DD}$ and $V_{IN}L$ = $GND$ |                          | 2.9  | 6.8                  | mW   |

|                                   | All power-down modes                        | $AV_{DD} = 3.6V$ to $5.5V$<br>$V_{IN}H = AV_{DD}$ and $V_{IN}L = GND$   |                          | 0.6  | 16                   | μW   |

|                                   |                                             | $AV_{DD}$ = 2.7V to 3.6V<br>$V_{IN}H$ = $AV_{DD}$ and $V_{IN}L$ = $GND$ |                          | 0.3  | 9                    | μνν  |

| TEMPERATUI                        | RE RANGE                                    |                                                                         |                          |      |                      |      |

| Specified perfo                   | ormance                                     |                                                                         | -40                      |      | +125                 | °C   |

<sup>(6)</sup> Input code = midscale, no load.

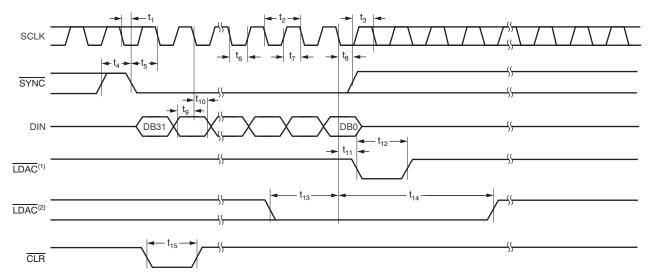

# 7.3 Timing Requirements (1) (2)

At  $AV_{DD}$  = 2.7V to 5.5V and over -40°C to +125°C (unless otherwise noted).

|                    | PARAMETER                                                                  | TEST CONDITIONS                   | MIN | TYP MAX | UNIT |

|--------------------|----------------------------------------------------------------------------|-----------------------------------|-----|---------|------|

| t <sub>1</sub>     | SCLK falling edge to SYNC falling edge (for successful write operation)    | $AV_{DD} = 2.7V \text{ to } 5.5V$ | 10  |         | ns   |

| t <sub>2</sub> (3) | SCLK cycle time                                                            | $AV_{DD} = 2.7V \text{ to } 5.5V$ | 20  |         | ns   |

| t <sub>3</sub>     | SYNC rising edge to 31st SCLK falling edge (for successful SYNC interrupt) | $AV_{DD} = 2.7V \text{ to } 5.5V$ | 13  |         | ns   |

| t <sub>4</sub>     | Minimum SYNC HIGH time                                                     | $AV_{DD} = 2.7V$ to 5.5V          | 80  |         | ns   |

<sup>(1)</sup> All input signals are specified with t<sub>R</sub> = t<sub>F</sub> = 3ns (10% to 90% of AV<sub>DD</sub>) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>)/2.

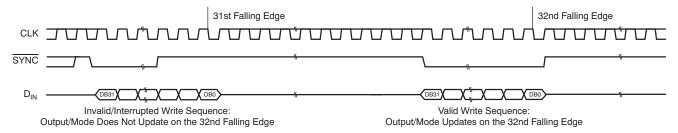

(2) See the Serial Write Operation timing diagram.

(3) Maximum SCLK frequency is 50MHz at AV<sub>DD</sub> = 2.7V to 5.5V.

Submit Documentation Feedback

# Timing Requirements<sup>(1)</sup> (continued)

At  $AV_{DD} = 2.7V$  to 5.5V and over  $-40^{\circ}C$  to  $+125^{\circ}C$  (unless otherwise noted).

|                 | PARAMETER                                                                | TEST CONDITIONS                   | MIN                | TYP | MAX | UNIT |

|-----------------|--------------------------------------------------------------------------|-----------------------------------|--------------------|-----|-----|------|

| t <sub>5</sub>  | SYNC to SCLK falling edge setup time                                     | $AV_{DD} = 2.7V \text{ to } 5.5V$ | 13                 |     |     | ns   |

| t <sub>6</sub>  | SCLK LOW time                                                            | $AV_{DD} = 2.7V \text{ to } 5.5V$ | 8                  |     |     | ns   |

| t <sub>7</sub>  | SCLK HIGH time                                                           | $AV_{DD} = 2.7V \text{ to } 5.5V$ | 8                  |     |     | ns   |

| t <sub>8</sub>  | SCLK falling edge to SYNC rising edge                                    | $AV_{DD} = 2.7V \text{ to } 5.5V$ | 10                 |     |     | ns   |

| t <sub>9</sub>  | Data setup time                                                          | $AV_{DD} = 2.7V \text{ to } 5.5V$ | 6                  |     |     | ns   |

| t <sub>10</sub> | Data hold time                                                           | $AV_{DD} = 2.7V \text{ to } 5.5V$ | 4                  |     |     | ns   |

| t <sub>11</sub> | SCLK falling edge to LDAC falling edge for asynchronous LDAC update mode | $AV_{DD} = 2.7V \text{ to } 5.5V$ | 40                 |     |     | ns   |

| t <sub>12</sub> | LDAC pulse width LOW time                                                | $AV_{DD} = 2.7V \text{ to } 5.5V$ | 80                 |     |     | ns   |

| t <sub>13</sub> | LDAC falling edge to SCLK falling edge for synchronous LDAC update mode  | AV <sub>DD</sub> = 2.7V to 5.5V   | 4 × t <sub>1</sub> |     |     | ns   |

| t <sub>14</sub> | 32nd SCLK falling edge to LDAC rising edge                               | $AV_{DD} = 2.7V \text{ to } 5.5V$ | 40                 |     |     | ns   |

| t <sub>15</sub> | CLR pulse width LOW time                                                 | AV <sub>DD</sub> = 2.7V to 5.5V   | 80                 |     |     | ns   |

- (1) Asynchronous LDAC update mode. For more information and details, see the LDAC Functionality section.

- (2) Synchronous LDAC update mode. For more information and details, see the LDAC Functionality section.

Figure 1. Serial Write Operation

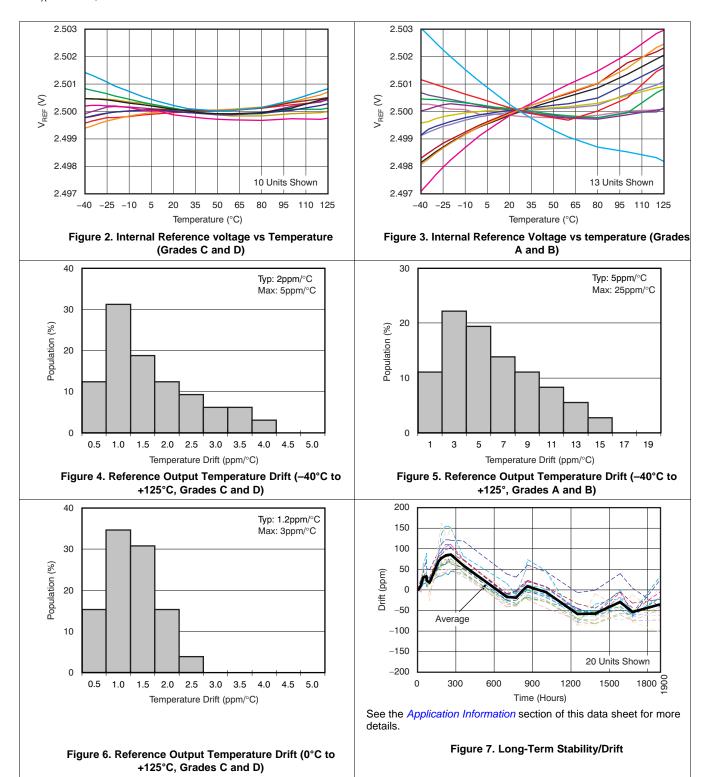

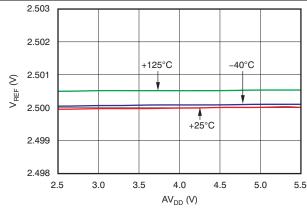

# 7.4 Typical Characteristics: Internal Reference

At  $T_A = +25$ °C, unless otherwise noted.

Product Folder Links: DAC7568 DAC8168 DAC8568

# TEXAS INSTRUMENTS

# Typical Characteristics: Internal Reference (continued)

At  $T_A = +25$ °C, unless otherwise noted.

See the *Application Information* section of this data sheet for more details

See the *Application Information* section of this data sheet for more details.

Figure 8. Internal Reference Noise Density vs Frequency

Figure 10. Internal Reference Voltage vs Load Current (Grades C and D)

Figure 11. Internal Reference Voltage vs Load Current (Grades A and B)

Figure 12. Internal Reference Voltage vs Supply Voltage (Grades C and D)

Figure 13. Internal Reference Voltage vs Supply Voltage (Grades A and B)

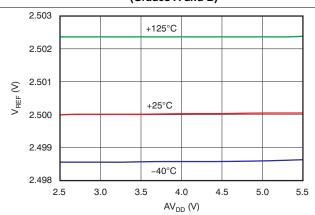

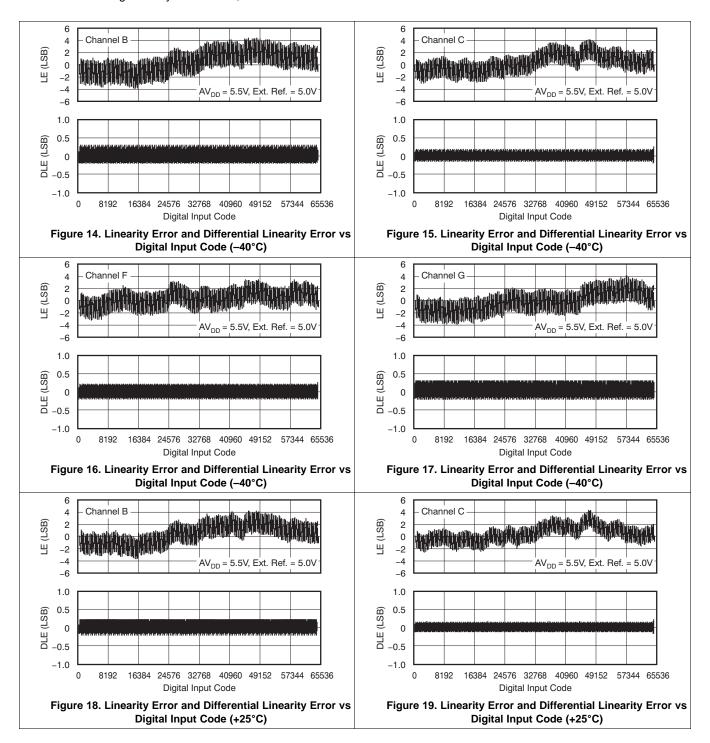

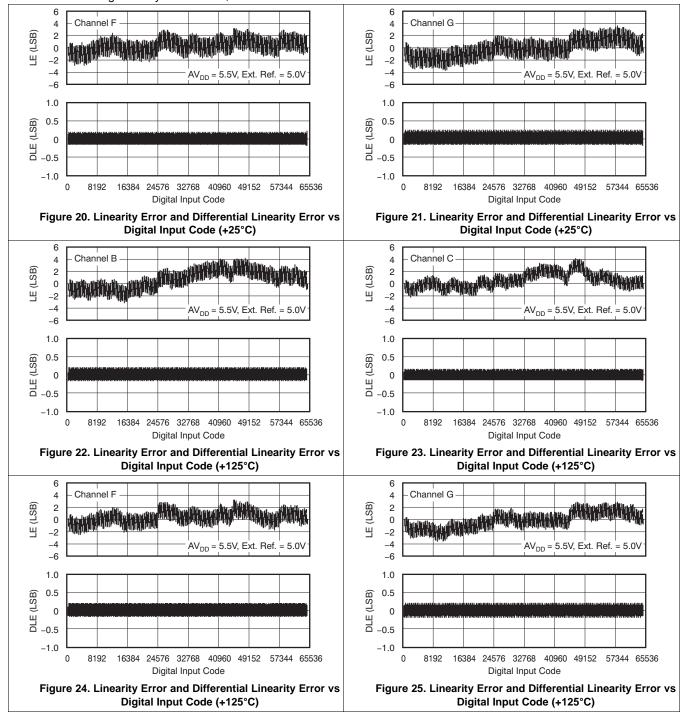

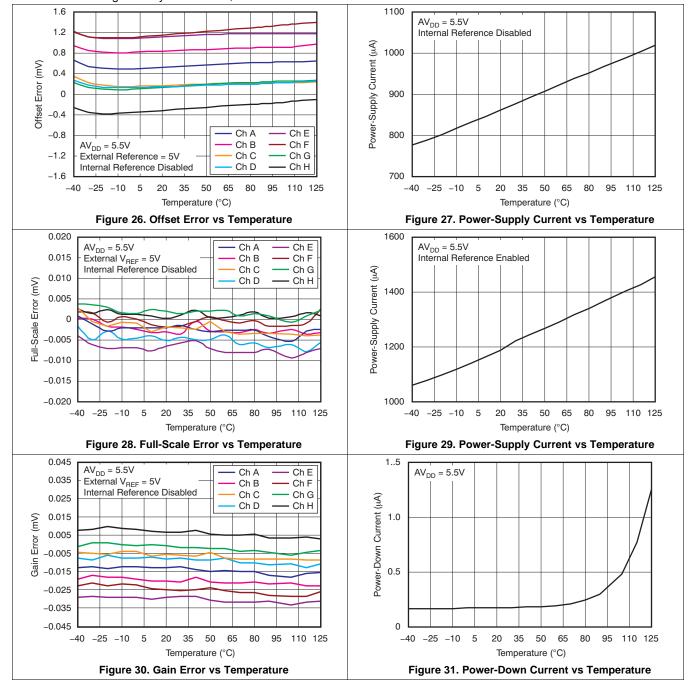

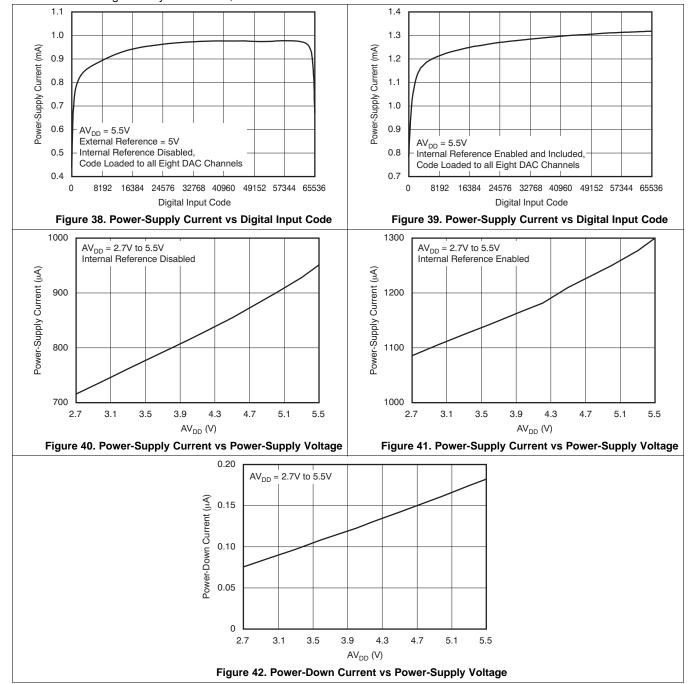

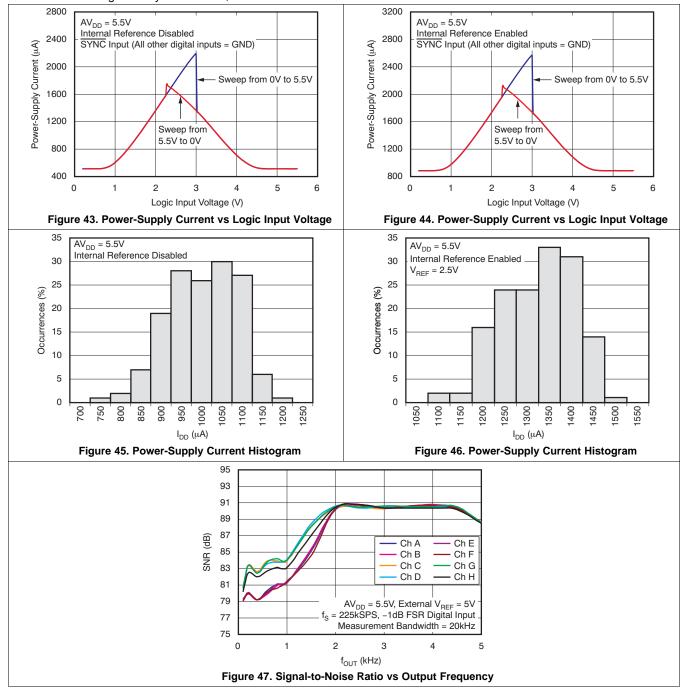

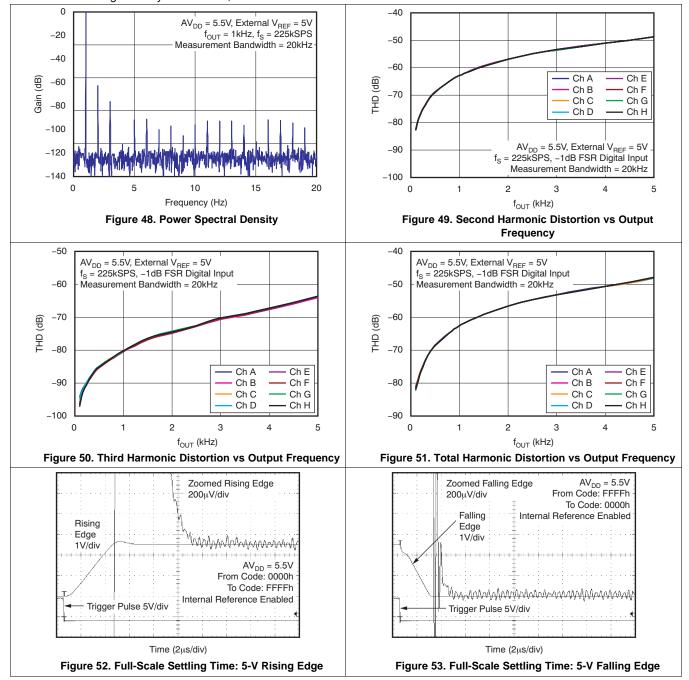

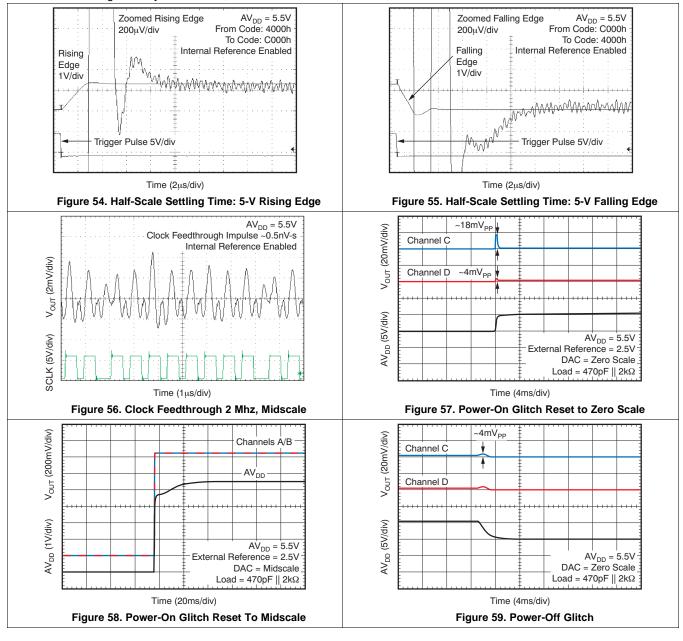

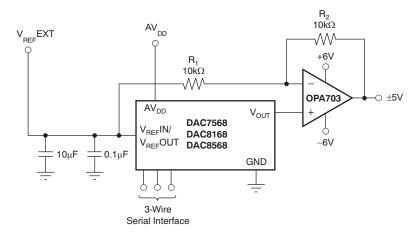

# 7.5 Typical Characteristics: DAC at $AV_{DD} = 5.5 \text{ V}$

Channel-specific information provided as examples. At  $T_A = +25^{\circ}$ C, external reference used, DAC output not loaded, and all DAC codes in straight binary data format, unless otherwise noted.

Copyright © 2009–2018, Texas Instruments Incorporated

Submit Documentation Feedback

Channel-specific information provided as examples. At  $T_A = +25^{\circ}$ C, external reference used, DAC output not loaded, and all DAC codes in straight binary data format, unless otherwise noted.

Submit Documentation Feedback

Copyright © 2009–2018, Texas Instruments Incorporated

Channel-specific information provided as examples. At  $T_A = +25$ °C, external reference used, DAC output not loaded, and all DAC codes in straight binary data format, unless otherwise noted.

Product Folder Links: DAC7568 DAC8168 DAC8568

Submit Documentation Feedback

Figure 67. DAC Output Noise 0.1 Hz to 10 Hz

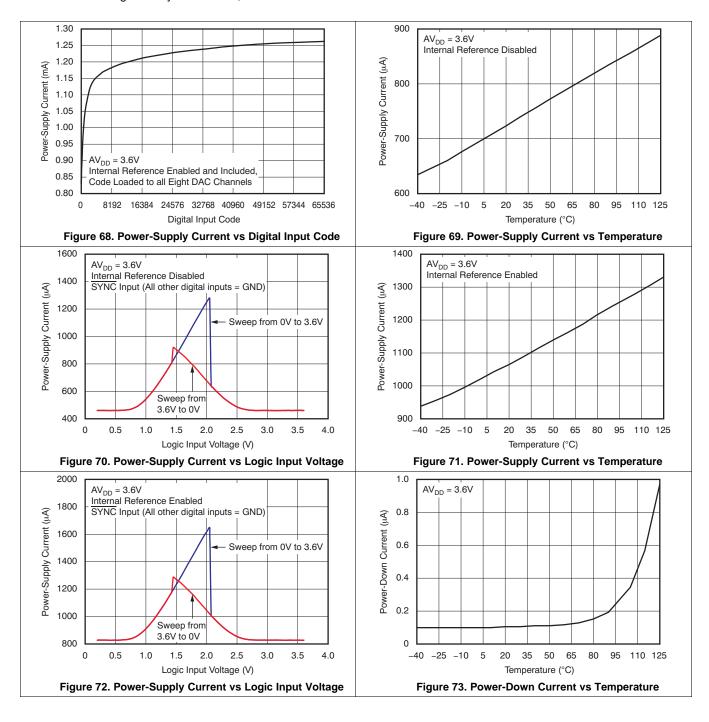

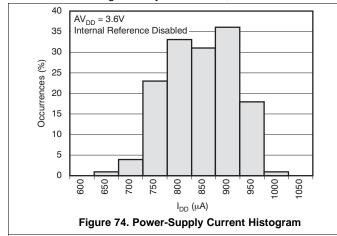

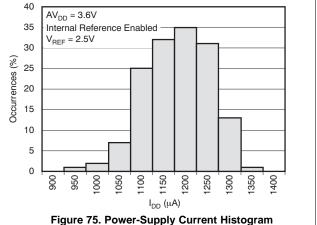

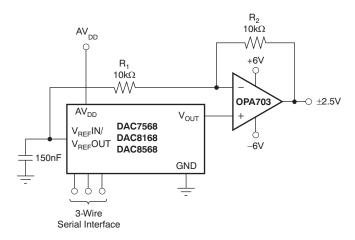

# 7.6 Typical Characteristics: DAC at $AV_{DD} = 3.6 \text{ V}$

Channel-specific information provided as examples. At  $T_A = +25$ °C, internal reference used, and DAC output not loaded, all DAC codes in straight binary data format, unless otherwise noted

Copyright © 2009–2018, Texas Instruments Incorporated

Submit Documentation Feedback

# Typical Characteristics: DAC at AV<sub>DD</sub> = 3.6 V (continued)

# 7.7 Typical Characteristics: DAC at $AV_{DD} = 2.7 \text{ V}$

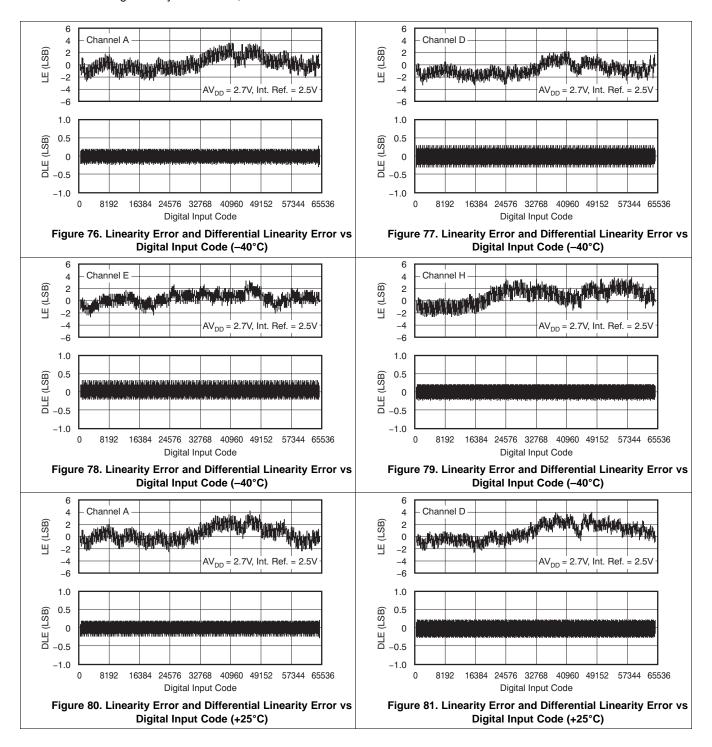

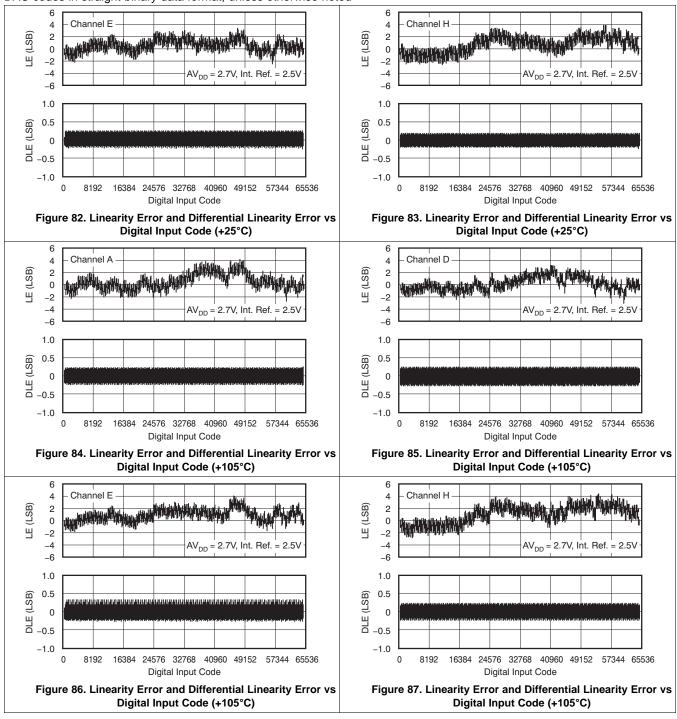

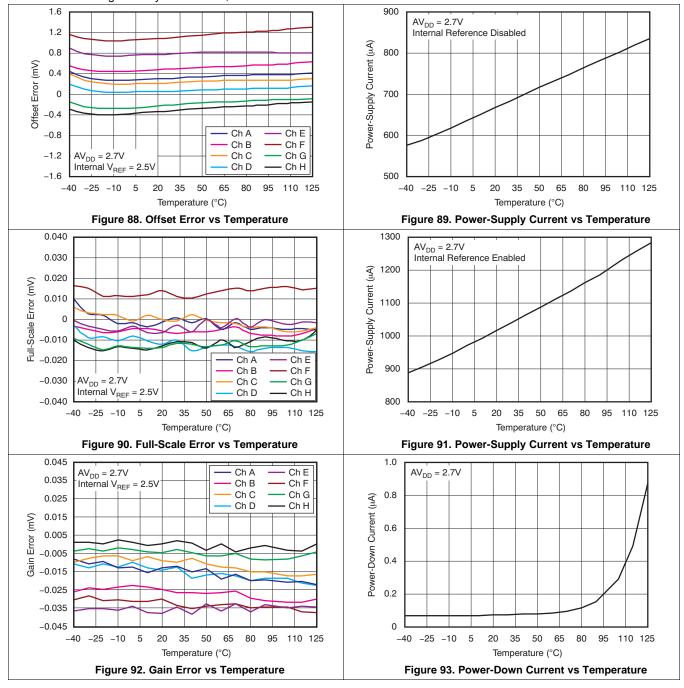

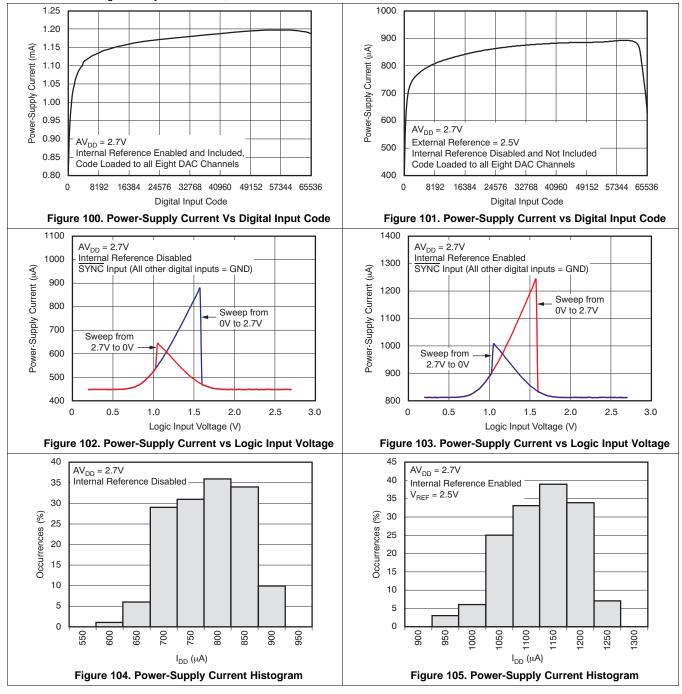

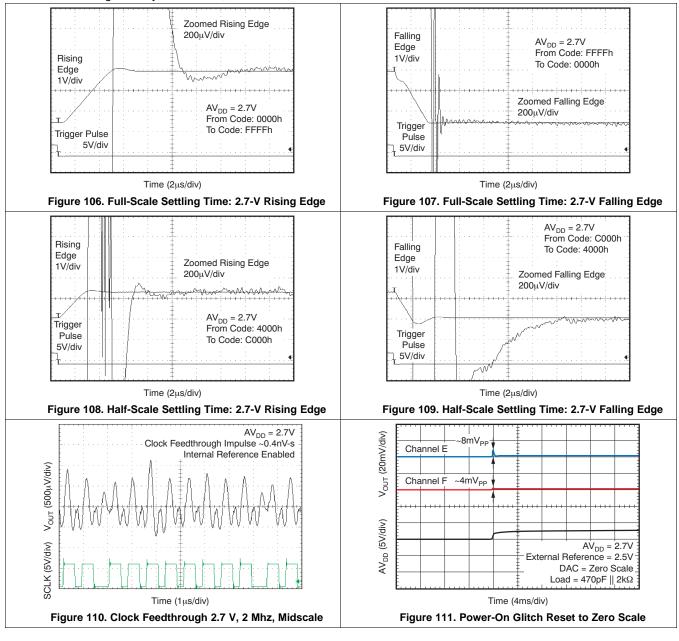

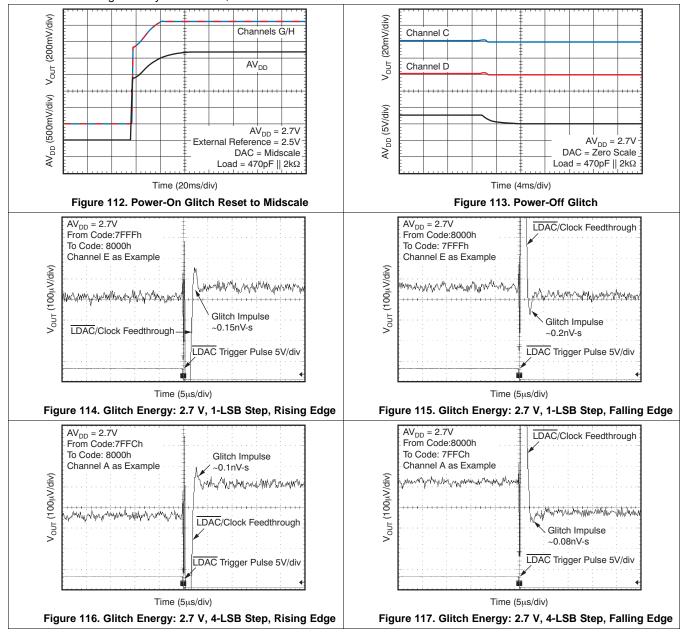

Channel-specific information provided as examples. At  $T_A = +25$ °C, internal reference used, and DAC output not loaded, all DAC codes in straight binary data format, unless otherwise noted

Copyright © 2009–2018, Texas Instruments Incorporated

Submit Documentation Feedback

Channel-specific information provided as examples. At  $T_A = +25$ °C, internal reference used, and DAC output not loaded, all DAC codes in straight binary data format, unless otherwise noted

Submit Documentation Feedback

Copyright © 2009–2018, Texas Instruments Incorporated

# Typical Characteristics: DAC at AV<sub>DD</sub> = 2.7 V (continued)

Channel-specific information provided as examples. At  $T_A = +25$ °C, internal reference used, and DAC output not loaded, all DAC codes in straight binary data format, unless otherwise noted

Product Folder Links: DAC7568 DAC8168 DAC8568

## 8 Detailed Description

#### 8.1 Functional Block Diagram

## 8.2 Feature Description

#### 8.2.1 Digital-to-Analog Converter (DAC)

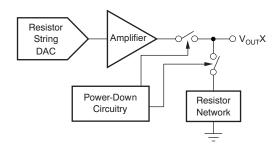

The DAC7568, DAC8168, and DAC8568 architecture consists of eight string DACs each followed by an output buffer amplifier. The devices include an internal 2.5V reference with 2ppm/°C temperature drift performance, and offer either 5V or 2.5V full scale output voltage. Figure 120 shows a principal block diagram of the DAC architecture.

Figure 120. Device Architecture

The input coding to the DAC7568, DAC8168, and DAC8568 is straight binary, so the ideal output voltage is given by Equation 1:

Copyright © 2009–2018, Texas Instruments Incorporated Submit Documentation Feedback

$$V_{OUT} = \left(\frac{D_{IN}}{2^n}\right) \times V_{REF} \times Gain$$

(1)

Where:

$D_{IN}$  = decimal equivalent of the binary code that is loaded to the DAC register. It can range from 0 to 4095 for DAC7568 (12 bit), 0 to 16,383 for DAC8168 (14 bit), and 0 to 65535 for DAC8568 (16 bit).

n = resolution in bits; either 12 (DAC7568), 14 (DAC8168) or 16 (DAC8568)

Gain = 1 for A/B grades or 2 for C/D grades.

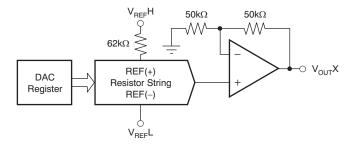

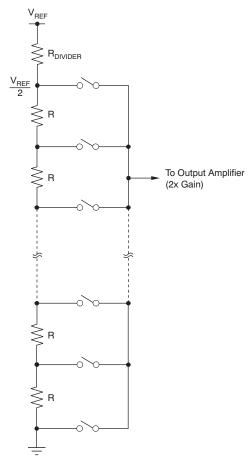

### 8.2.2 Resistor String

The resistor string section is shown in Figure 121. It is simply a string of resistors, each of value *R*. The code loaded into the DAC register determines at which node on the string the voltage is tapped off to be fed into the output amplifier by closing one of the switches connecting the string to the amplifier. It is monotonic because it is a string of resistors.

Figure 121. Resistor String

#### 8.2.3 Output Amplifier

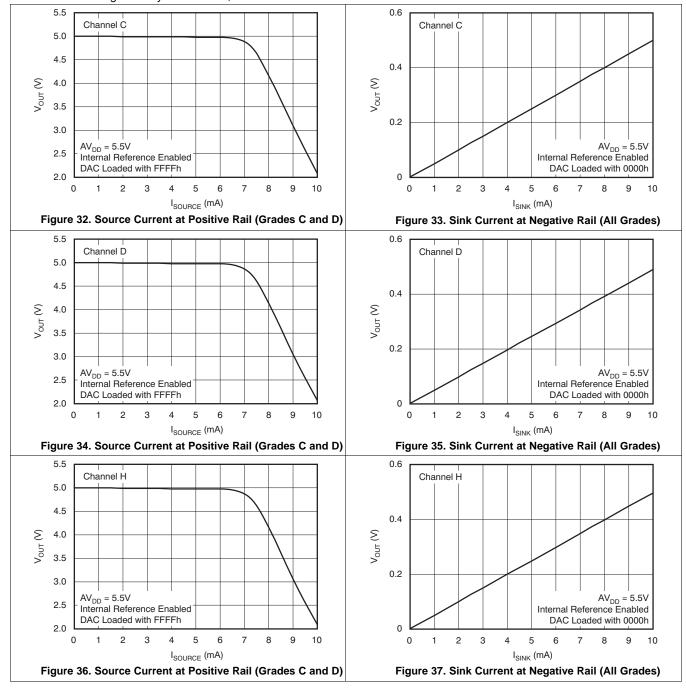

The output buffer amplifier is capable of generating rail-to-rail voltages on its output, giving a maximum output range of 0V to  $AV_{DD}$ . It is capable of driving a load of  $2k\Omega$  in parallel with 3000pF to GND. The source and sink capabilities of the output amplifier can be seen in the *Typical Characteristics*. The typical slew rate is  $0.75V/\mu s$ , with a typical full-scale settling time of  $5\mu s$  with the output unloaded.

Submit Documentation Feedback

Copyright © 2009–2018, Texas Instruments Incorporated

#### 8.2.4 Internal Reference

The DAC7568, DAC8168, and DAC8568 include a 2.5V internal reference that is disabled by default. The internal reference is externally available at the V<sub>REF</sub>IN/V<sub>REF</sub>OUT pin. A minimum 100nF capacitor is recommended between the reference output and GND for noise filtering.

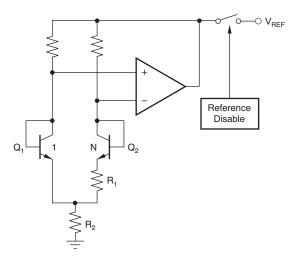

The internal reference of the DAC7568, DAC8168, and DAC8568 is a bipolar, transistor-based, precision bandgap voltage reference. Figure 122 shows the basic bandgap topology. Transistors  $Q_1$  and  $Q_2$  are biased such that the current density of  $Q_1$  is greater than that of  $Q_2$ . The difference of the two base-emitter voltages ( $V_{BE1} - V_{BE2}$ ) has a positive temperature coefficient and is forced across resistor  $R_1$ . This voltage is gained up and added to the base-emitter voltage of  $Q_2$ , which has a negative temperature coefficient. The resulting output voltage is virtually independent of temperature. The short-circuit current is limited by design to approximately 100mA.

Figure 122. Bandgap Reference Simplified Schematic

Refer to *Enable/Disable Internal Reference* section for information on enabling and disabling the internal reference.

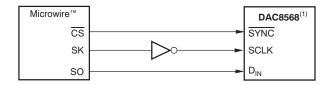

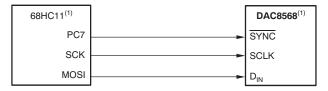

#### 8.2.5 Serial Interface

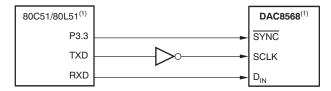

The DAC7568, DAC8168, and DAC8568 have a 3-wire serial interface (SYNC, SCLK, and D<sub>IN</sub>; see the *Pin Configurations*) compatible with SPI, QSPI, and Microwire interface standards, as well as most DSPs. See the Serial Write Operation timing diagram (Figure 1) for an example of a typical write sequence.

The DAC7568, DAC8168, and DAC8568 input shift register is 32-bits wide, consisting of four prefix bits (DB31 to DB28), four control bits (DB27 to DB24), 16 data bits (DB23 to DB4), and four feature bits. The 16 data bits comprise the 16-, 14-, or 12-bit input code. When writing to the DAC register (data transfer), bits DB0 to DB3 (for 16-bit operation), DB0 to DB5 (for 14-bit operation), and DB0 to DB7 (for 12-bit operation) are ignored by the DAC and should be treated as *don't care* bits (see Table 1 to Table 3). All 32 bits of data are loaded into the DAC under the control of the serial clock input, SCLK.

DB31 (MSB) is the first bit that is loaded into the DAC shift register and must be always set to '0'. It is followed by the rest of the 32-bit word pattern, left-aligned. This configuration means that the first 32 bits of data are latched into the shift register and any further clocking of data is ignored. When the DAC registers are being written to, the DAC7568, DAC8168, and DAC8568 receive all 32 bits of data, ignore DB31 to DB28, and decode the second set of four bits (DB27 to DB24) in order to determine the DAC operating/control mode (see ). Bits DB23 to DB20 are used to address selected DAC channels. The next 16/14/12 bits of data that follow are decoded by the DAC to determine the equivalent analog output. The last four data bits (DB0 to DB3 for DAC8568), last data six bits (DB0 to DB5 for DAC8168), or last eight data bits (DB0 to DB7 for DAC7568) are ignored in this case. For more details on these and other commands (such as write to LDAC register, power down DACs, etc.), see Table 4.

Copyright © 2009–2018, Texas Instruments Incorporated

Submit Documentation Feedback

The data format is straight binary with all '0's corresponding to 0V output and all '1's corresponding to full-scale output. For all documentation purposes, the data format and representation used here is a true 16-bit pattern (that is, FFFFh for data word for full-scale) that the DAC7568, DAC8168, and DAC8568 require.

The write sequence begins by bringing the \$\overline{\text{SYNC}}\$ line low. Data from the \$D\_{IN}\$ line are clocked into the 32-bit shift register on each falling edge of SCLK. The serial clock frequency can be as high as 50MHz, making the DAC7568, DAC8168, and DAC8568 compatible with high-speed DSPs. On the 32nd falling edge of the serial clock, the last data bit is clocked into the shift register and the shift register locks. Further clocking does not change the shift register data. After receiving the 32nd falling clock edge, the DAC7568, DAC8168, and DAC8568 decode the four control bits and four address bits and 16/14/12 data bits to perform the required function, without waiting for a \$\overline{\text{SYNC}}\$ rising edge. A new write sequence starts at the next falling edge of \$\overline{\text{SYNC}}\$. A rising edge of \$\overline{\text{SYNC}}\$ before the 31st-bit sequence is complete resets the SPI interface; no data transfer occurs. After the 32nd falling edge of \$\overline{\text{SCLK}}\$ is received, the \$\overline{\text{SYNC}}\$ line may be kept low or brought high. In either case, the minimum delay time from the 32nd falling \$\overline{\text{SCLK}}\$ edge to the next falling \$\overline{\text{SYNC}}\$ edge must be met in order to properly begin the next cycle; see the \$\overline{\text{Serial Write Operation timing diagram (Figure 1). To assure the lowest power consumption of the device, care should be taken that the levels are as close to each rail as possible. Refer to the 5.5V, 3.6V, and 2.7V Typical Characteristics sections for the *Power-Supply Current vs Logic Input Voltage* graphs (Figure 43, Figure 44, Figure 70, Figure 72, Figure 102, and Figure 103).

#### 8.2.6 Input Shift Register

The input shift register (SR) of the DAC7568, DAC8168, and DAC8568 is 32 bits wide (as shown in Table 1, Table 2, and Table 3, respectively), and consists of four Prefix bits (DB31 to DB28), four control bits (DB27 to DB24), 16 data bits (DB23 to DB4), and four additional feature bits. The 16 data bits comprise the 16-, 14-, or 12-bit input code.

The DAC7568, DAC8168, and DAC8568 support a number of different load commands. The load commands are summarized in Table 4.

## Table 1. DAC8568 Data Input Register Format

| DI | 331 |       |      | I | DB2 | 7     |       | I    | DB2 | 3    |      | [   | DB19 | 9   |     |     |     |     |    |      |      |    |    |    |    |    |    | DB4 |    |      | [     | DB0 |

|----|-----|-------|------|---|-----|-------|-------|------|-----|------|------|-----|------|-----|-----|-----|-----|-----|----|------|------|----|----|----|----|----|----|-----|----|------|-------|-----|

| 0  | Х   | 2     | Х    | Х | СЗ  | C2    | C1    | C0   | А3  | A2   | A1   | A0  | D15  | D14 | D13 | D12 | D11 | D10 | D9 | D8   | D7   | D6 | D5 | D4 | D3 | D2 | D1 | D0  | F3 | F2   | F1    | F0  |

|    | Pre | fix E | Bits | ; | - C | Contr | ol Bi | ts - | A   | ddre | ss B | its |      |     |     |     |     |     |    | Data | Bits | ;  |    |    |    |    |    |     | F  | eatu | re Bi | its |

#### Table 2. DAC8168 Data Input Register Format

| DB31 DB27 |   |      |       |   |     |       | DB23 DE |      |    |      |       |     | 19  |     |     |     |    |    |      |      |    |    |    |    |    |    | DB4 |   |     |      |       |    |

|-----------|---|------|-------|---|-----|-------|---------|------|----|------|-------|-----|-----|-----|-----|-----|----|----|------|------|----|----|----|----|----|----|-----|---|-----|------|-------|----|

|           | 0 | Х    | х     | х | СЗ  | C2    | C1      | CO   | A3 | A2   | A1    | A0  | D13 | D12 | D11 | D10 | D9 | D8 | D7   | D6   | D5 | D4 | D3 | D2 | D1 | D0 | Х   | Х | F3  | F2   | F1    | F0 |

|           | F | refi | x Bit | s | - C | Contr | ol Bi   | ts - | A  | ddre | ss Bi | its |     |     |     |     |    |    | Data | Bits | ;  |    |    |    |    |    |     |   | Į F | eatu | re Bi | ts |

#### Table 3. DAC7568 Data Input Register Format

| DB3 | 31 | 1 DB27 DB23 DB19 |   |    |    |    |    |    |    |    |    |     |     |    |    |    | DB4 |    |    |    | DB0 |    |    |   |   |   |   |    |    |    |    |

|-----|----|------------------|---|----|----|----|----|----|----|----|----|-----|-----|----|----|----|-----|----|----|----|-----|----|----|---|---|---|---|----|----|----|----|

| 0   | Х  | х                | х | C3 | C2 | C1 | C0 | А3 | A2 | A1 | A0 | D11 | D10 | D9 | D8 | D7 | D6  | D5 | D4 | D3 | D2  | D1 | D0 | х | х | х | х | F3 | F2 | F1 | F0 |

|-- Prefix Bits -- | |- Control Bits - | | Address Bits | | ------ Data Bits ----- | | Feature Bits |

SBAS430F - JANUARY 2009-REVISED APRIL 2018 www.ti.com

# Table 4. Control Matrix for the DAC7568, DAC8168, and DAC8568

| DB31     | DB30-<br>DB28 | DB27      | DB26      | DB25 | DB24 | DB23 | DB22 | DB21       | DB20     | DB19 | DB18 | DB17 | DB16-<br>DB10 | DB9  | DB8 | DB7      | DB6      | DB5      | DB4      | DB3      | DB2      | DB1      | DB0      | DESCRIPTION                                                                                                                                                     |

|----------|---------------|-----------|-----------|------|------|------|------|------------|----------|------|------|------|---------------|------|-----|----------|----------|----------|----------|----------|----------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | Don't<br>Care | C3        | C2        | C1   | C0   | А3   | A2   | <b>A</b> 1 | A0       | D16  | D15  | D14  | D13-<br>D7    | D6   | D5  | D4       | D3       | D2       | D1       | F3       | F2       | F1       | F0       | GENERAL DATA FORMAT FOR 16-BIT DAC8568                                                                                                                          |

| 0        | Don't<br>Care | C3        | C2        | C1   | C0   | А3   | A2   | <b>A</b> 1 | Α0       | D14  | D13  | D12  | D11-<br>D5    | D4   | D3  | D2       | D1       | х        | х        | F3       | F2       | F1       | F0       | GENERAL DATA FORMAT FOR 14-BIT DAC8168                                                                                                                          |

| 0        | Don't<br>Care | C3        | C2        | C1   | C0   | А3   | A2   | <b>A</b> 1 | A0       | D12  | D11  | D10  | D9-D3         | D2   | D1  | х        | х        | х        | х        | F3       | F2       | F1       | F0       | GENERAL DATA FORMAT FOR 12-BIT DAC7568                                                                                                                          |

| 1        | Х             | х         | Х         | Х    | Х    | Х    | Х    | Х          | Х        | Х    | Х    | Х    | Х             | х    | Х   | х        | Х        | х        | Х        | х        | Х        | Х        | Х        | Reserved Bit - Not valid; device does not perform to specified conditions                                                                                       |

| Write to | Selected      | DAC Inp   | out Regis | ster |      | •    |      |            |          |      |      |      |               |      | •   |          | •        |          |          |          |          |          |          |                                                                                                                                                                 |

| 0        | Х             | 0         | 0         | 0    | 0    | 0    | 0    | 0          | 0        |      |      |      |               | Data |     |          |          |          |          | Х        | Χ        | Χ        | Х        | Write to input register - DAC Channel A                                                                                                                         |

| 0        | Х             | 0         | 0         | 0    | 0    | 0    | 0    | 0          | 1        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Write to input register - DAC Channel B                                                                                                                         |

| 0        | Х             | 0         | 0         | 0    | 0    | 0    | 0    | 1          | 0        |      |      |      |               | Data |     |          |          |          |          | Х        | Χ        | Х        | Х        | Write to input register - DAC Channel C                                                                                                                         |

| 0        | Х             | 0         | 0         | 0    | 0    | 0    | 0    | 1          | 1        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Write to input register - DAC Channel D                                                                                                                         |

| 0        | Χ             | 0         | 0         | 0    | 0    | 0    | 1    | 0          | 0        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Χ        | Х        | Write to input register - DAC Channel E                                                                                                                         |

| 0        | Х             | 0         | 0         | 0    | 0    | 0    | 1    | 0          | 1        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Write to input register - DAC Channel F                                                                                                                         |

| 0        | Χ             | 0         | 0         | 0    | 0    | 0    | 1    | 1          | 0        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Write to input register - DAC Channel G                                                                                                                         |

| 0        | Х             | 0         | 0         | 0    | 0    | 0    | 1    | 1          | 1        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Write to input register - DAC Channel H                                                                                                                         |

| 0        | Х             | 0         | 0         | 0    | 0    | 1    | Х    | Х          | Х        |      |      |      |               | Χ    |     |          |          |          |          | Х        | Χ        | Х        | Х        | Invalid code - No DAC channel is updated                                                                                                                        |

| 0        | Х             | 0         | 0         | 0    | 0    | 1    | 1    | 1          | 1        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Broadcast mode - Write to all DAC channels                                                                                                                      |

| Update   | Selected      | DAC Reg   | gisters   |      | 1    |      |      |            |          |      |      |      |               |      |     |          |          |          |          | Į.       |          |          |          |                                                                                                                                                                 |

| 0        | Х             | 0         | 0         | 0    | 1    | 0    | 0    | 0          | 0        |      |      |      |               | Data |     |          |          |          |          | Х        | Χ        | Χ        | Х        | Update DAC register - DAC Channel A                                                                                                                             |

| 0        | Х             | 0         | 0         | 0    | 1    | 0    | 0    | 0          | 1        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Update DAC register - DAC Channel B                                                                                                                             |

| 0        | Х             | 0         | 0         | 0    | 1    | 0    | 0    | 1          | 0        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Update DAC register - DAC Channel C                                                                                                                             |

| 0        | X             | 0         | 0         | 0    | 1    | 0    | 0    | 1          | 1        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Update DAC register - DAC Channel D                                                                                                                             |

| 0        | Х             | 0         | 0         | 0    | 1    | 0    | 1    | 0          | 0        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Update DAC register - DAC Channel E                                                                                                                             |

| 0        | Х             | 0         | 0         | 0    | 1    | 0    | 1    | 0          | 1        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Update DAC register - DAC Channel F                                                                                                                             |

| 0        | Х             | 0         | 0         | 0    | 1    | 0    | 1    | 1          | 0        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Update DAC register - DAC Channel G                                                                                                                             |

| 0        | Х             | 0         | 0         | 0    | 1    | 0    | 1    | 1          | 1        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Update DAC register - DAC Channel H                                                                                                                             |

| 0        | Х             | 0         | 0         | 0    | 1    | 1    | Х    | Х          | Х        |      |      |      |               | Х    |     |          |          |          |          | Х        | Х        | Х        | Х        | Invalid code - No DAC channel is updated                                                                                                                        |

| 0        | Х             | 0         | 0         | 0    | 1    | 1    | 1    | 1          | 1        |      |      |      |               | Data |     |          |          |          |          | Х        | Х        | Х        | Х        | Broadcast mode - Update all DAC registers                                                                                                                       |

|          |               | ode Regis | ster      | 1    | 1    | 1    |      |            |          | 1    |      |      |               |      |     |          |          |          |          | ļ        |          | 1        | 1        |                                                                                                                                                                 |

| 0        | Х             | 0         | 1         | 0    | 1    | Х    | Х    | Х          | Х        | Χ    | Χ    | Х    | Х             | Х    | Х   | Х        | Х        | Х        | Χ        | Х        | Χ        | 0        | 0        | Write to clear code register; clear to zero scale                                                                                                               |

| 0        | Х             | 0         | 1         | 0    | 1    | X    | Х    | X          | X        | X    | X    | X    | X             | X    | Х   | X        | X        | Х        | Х        | Х        | Х        | 0        | 1        | Write to clear code register; clear to midscale                                                                                                                 |