# Programmable USB Type-C Controller w/PD

# FUSB302T

## **Description**

The FUSB302T targets system designers looking to implement USB Type-C wall charger or Travel adaptor. In addition to the default SRC function, the device supports DRP/ SRC/ SNK with low amount of programmability.

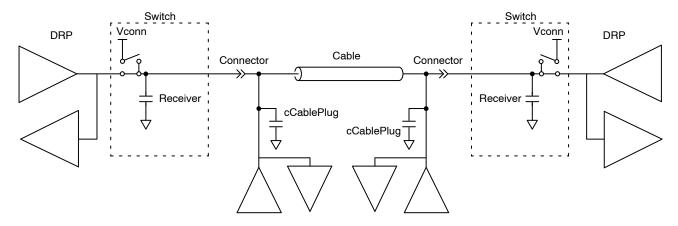

The FUSB302T enables the USB Type-C detection including attach/detach, and orientation. The FUSB302T integrates the physical layer of the USB BMC power delivery protocol to allow up to 100 W of power and role swap. The BMC PD block enables full support for alternative interfaces of the Type-C specification.

#### **Features**

- Dual-role Functionality with Autonomous DRP Toggle

- Ability to Connect as Either a Host or a Device Based on What Has Been Attached

- Software Configurable Either as a Dedicated Host, Dedicated Device, or Dual Role

- Dedicated Devices can Operate both on a Type-C Receptacle or a Type-C Plug with a Fixed CC and VCONN Channel

- Full Type-C 1.2 Support. Integrates the Following Functionality of the CC Pin:

- Attach/Detach Detection as Host

- Current Capability Indication as Host

- Current Capability Detection as Device

- Audio Adapter Accessory Mode

- Debug Accessory Mode

- Active Cable Detection

- Integrates CCx to VCONN Switch with Over-current Limiting for Powering USB3.1 Full Featured Cables

- USB Power Delivery (PD) 2.0 Support:

- ◆ Automatic GoodCRC Packet Response

- Automatic Retries of Sending a Packet if a GoodCRC is Not Received

- Automatic Soft Reset Packet Sent with Retries if Needed

- Automatic Hard Reset Ordered Set Sent

- Default CC Open for SRC Application

- Low Power Operation:  $I_{CC} = 25 \mu A$  (Typical)

- AEC-Q100 Qualified and PPAP Capable

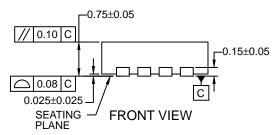

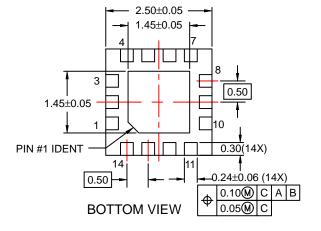

- Packaged in:

- ◆ 14-lead WQFN (2.5 mm × 2.5 mm, 0.5 mm Pitch)

## **Applications**

- Charging/Wall Adaptors

- Automotive Cigarette Adapters

- Laptops, Notebooks

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 2 of this data sheet.

Power Adapters

Automotive

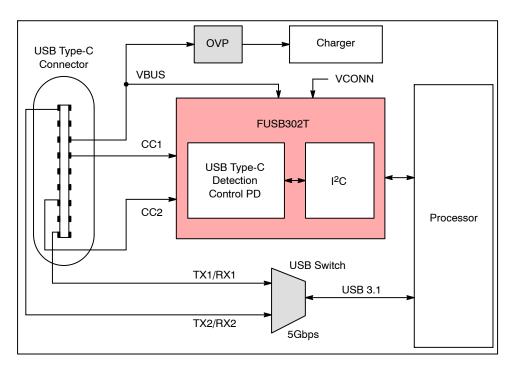

Figure 1. Block Diagram

**Table 1. ORDERING INFORMATION**

| Part Number    | Top Mark | Operating<br>Temperature Range | Package                                            | Packing Method <sup>†</sup> |

|----------------|----------|--------------------------------|----------------------------------------------------|-----------------------------|

| FUSB302TMPX    | GS       | −40 to 85°C                    |                                                    |                             |

| FUSB302TVMPX   | YD       |                                |                                                    |                             |

| FUSB302TV01MPX | YE       | Automotive                     | WQFN14 2.5 mm × 2.5 mm,<br>0.5 mm Pitch, (Pb–Free) | Tape and Reel               |

| FUSB302TV10MPX | YF       | −40 to 105°C                   | .,, (. = )                                         |                             |

| FUSB302TV11MPX | YG       |                                |                                                    |                             |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

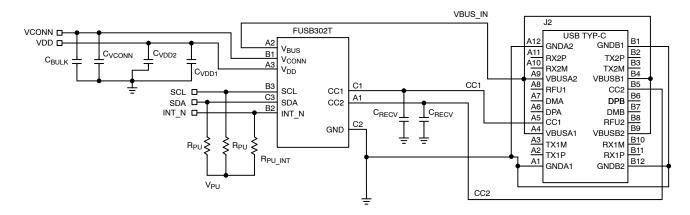

## **TYPICAL APPLICATION**

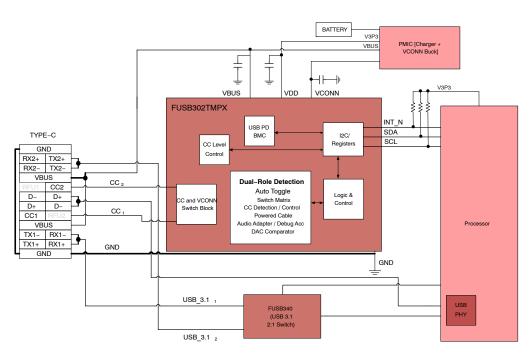

Figure 2. Typical Application

# **BLOCK DIAGRAM**

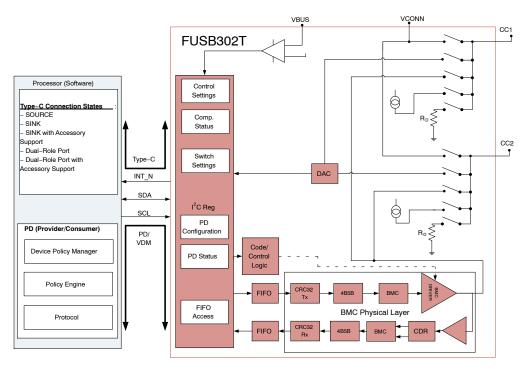

Figure 3. Functional Block Diagram

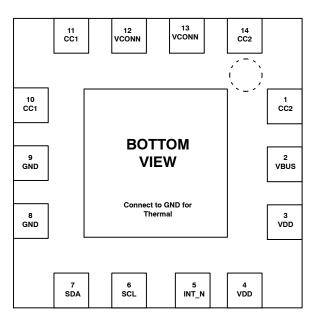

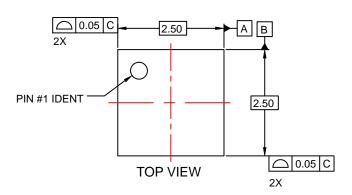

## **PIN CONFIGURATION**

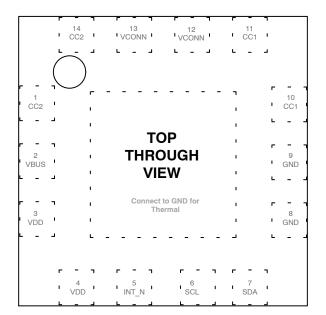

Figure 4. FUSB302TMPX Pin Assignment

# **Table 2. PIN DESCRIPTION**

| Name         | Туре           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB TYPE-C C | ONNECTOR INTER | RFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CC1/CC2      | I/O            | Type-C connector Configuration Channel (CC) pins. Initially used to determine when an attach has occurred and what the orientation of the insertion is. Functionality after attach depends on mode of operation detected.  Operating as a host:  Sets the allowable charging current for VBUS to be sensed by the attached device  Used to communicate with devices using USB BMC Power Delivery  Used to detect when a detach has occurred Operating as a device:  Indicates what the allowable sink current is from the attached host. Used to communicate with devices using USB BMC Power Delivery |

| GND          | Ground         | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VBUS         | Input          | VBUS input pin for attach and detach detection when operating as an upstream facing port (Device). Expected to be an OVP protected input.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| POWER INTER  | FACE           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VDD          | Power          | Input supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VCONN        | Power Switch   | Regulated input to be switched to correct CC pin as VCONN to power USB3.1 full-featured cables and other accessories.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SIGNAL INTER | FACE           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

I<sup>2</sup>C serial clock signal to be connected to the phone-based I<sup>2</sup>C master.

I<sup>2</sup>C serial data signal to be connected to the phone-based I<sup>2</sup>C master

Active LOW open drain interrupt output used to prompt the processor to read the I<sup>2</sup>C register bits

SCL

SDA

INT\_N

Input

Open-Drain I/O

Open-Drain

Output

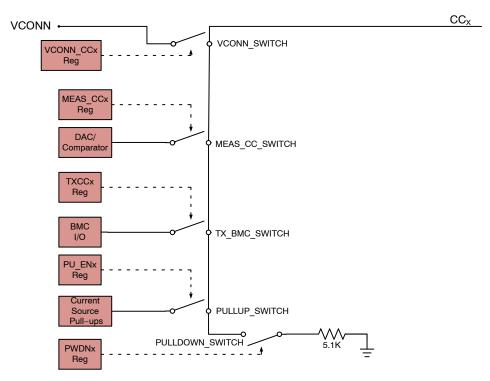

## **CONFIGURATION CHANNEL SWITCH**

The FUSB302T integrates the control and detection functionality required to implement a USB Type-C host, device or dual-role port including:

- Device Port Pull-Down (R<sub>D</sub>)

- Host Port Pull-Up (I<sub>P</sub>)

- VCONN Power Switch with OCP for Full-Featured USB3.1 Cables

- USB BMC Power Delivery Physical Layer

- Configuration Channel (CC) Threshold Comparators

Each CC pin contains a flexible switch matrix that allows the host software to control what type of Type-C port is implemented. The switches are shown in Figure 5.

Figure 5. Configuration Channel Switch Functionality

## **TYPE-C DETECTION**

The FUSB302T implements multiple comparators and a programmable DAC that can be used by software to determine the state of the CC and VBUS pins. This status information provides the processor all of the information required to determine attach, detach and charging current configuration of the Type-C port connection.

The FUSB302T has three fixed threshold comparators that match the USB Type-C specification for the three charging current levels that can be detected by a Type-C device. These comparators automatically cause BC\_LVL and COMP interrupts to occur when there is a change of state. In addition to the fixed threshold comparators, the host software can use the 6-bit DAC to determine the state of the CC lines more accurately.

The FUSB302T also has a fixed comparator that monitors if VBUS has reached a valid threshold or not. The DAC can be used to measure VBUS up to 20 V which allows the software to confirm that changes to the VBUS line have

occurred as expected based on PD or other communication methods to change the charging level.

## **Default Float on CC**

With or without VDD, The default CC status of FUSB302T is float/open. The FUSB302T is suitable for charger (wall) adaptor application which needs source only mode and shouldn't be seen as sink mode even with no power on the device. The FUSB302T, however, can be set to sink mode, which has Rd (pull-down) on CCx by software program.

### **Detection through Autonomous Device Toggle**

The FUSB302T has the capability to do autonomous DRP toggle. In autonomous toggle the FUSB302T internally controls the PDWN1, PDWN2, PU\_EN1 and PU\_EN2, MEAS\_CC1 and MEAS\_CC2 and implements a fixed DRP toggle between presenting as a SRC and presenting as a SNK. Alternately, it can present as a SRC or SNK only and poll CC1 and CC2 continuously.

Table 3. PROCESSOR CONFIGURES THE FUSB302T THROUGH I<sup>2</sup>C

| I <sup>2</sup> C Registers/Bits                          | Value |

|----------------------------------------------------------|-------|

| TOGGLE                                                   | 1     |

| PWR                                                      | 07H   |

| HOST_CUR0                                                | 1     |

| HOST_CUR1                                                | 0     |

| MEAS_VBUS                                                | 0     |

| VCONN_CC1                                                | 0     |

| VCONN_CC2                                                | 0     |

| Mask Register                                            | 0xFE  |

| Maska Register                                           | 0xBF  |

| Maskb Register (Except I_TOGDONE and I_BC_LVL Interrupt) | 0x01  |

| PWR[3:0]                                                 | 0x07  |

Once it has been determined what the role is of the FUSB302T, it returns I TOGDONE and TOGSS1/2.

## **Manual Device Toggle**

The FUSB302T has the capability to do manual DRP toggle. In manual toggle the FUSB302T is configurable by the processor software by  $I^2C$  and setting TOGGLE = 0.

**Manual Device Detection and Configuration**

A Type-C device must monitor VBUS to determine if it is attached or detached. The FUSB302T provides this information through the VBUSOK interrupt. After the Type-C device knows that a Type-C host/device has been attached, it needs to determine what type of termination is applied to each CC pin. The software determines if an Ra or Rd termination is present based on the BC\_LVL and COMP interrupt and status bits.

Additionally, for Rd terminations, the software can further determine what charging current is allowed by the Type-C host by reading the BC\_LVL status bits. This is summarized in Table 4.

# **Toggle Functionality**

When TOGGLE bit (Control2 register) is set the FUSB302T implements a fixed DRP toggle between presenting as a SRC and as a SNK. It can also be configured to present as a SRC only or SNK only and poll CC1 and CC2 continuously. This operation is turned on with TOGGLE = 1 and the processor should initially write HOST\_CUR1 = 0, HOST\_CUR0 = 1 (for default current), VCONN\_CC1 = VCONN\_CC2 = 0, Mask Register = 0xFE, Maska register = 0xBF, and Maskb register = 0x01, and PWR = 0x01. The processor should also read the interrupt register to clear them prior to setting the TOGGLE bit.

**Table 4. DEVICE INTERRUPT SUMMARY**

|              | Interrupt Status |      |                        |        |                             |

|--------------|------------------|------|------------------------|--------|-----------------------------|

| Status Type  | BC_LVL[1:0]      | COMP | COMP Setting           | VBUSOK | Meaning                     |

| CC Detection | 2'b00            | NA   | NA                     | 1      | vRA                         |

|              | 2'b01            | NA   | NA                     | 1      | vRd-Connect and vRd-USB     |

|              | 2'b10            | NA   | NA                     | 1      | vRd-Connect and vRd-1.5     |

|              | 2'b11            | 0    | 6'b11_0100<br>(2.05 V) | 1      | vRd-Connect and vRd-3.0     |

| Attach       | NA               | NA   | NA                     | 1      | Host Attached, VBUS Valid   |

| Detach       | NA               | NA   | NA                     | 0      | Host Detached, VBUS Invalid |

## **Manual Host Detection and Configuration**

When the FUSB302T is configured as a Type-C host, the software can use the status of the comparators and DAC to determine when a Type-C device has been attached or detached and what termination type has been attached to each CC pin.

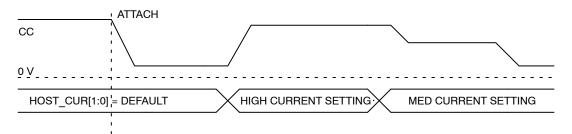

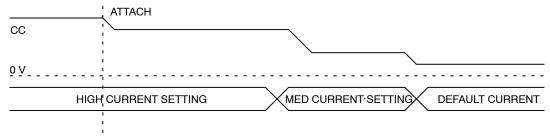

The FUSB302T allows the host software to change the charging current capabilities of the port through the

HOST\_CUR control bits. If the HOST\_CUR bits are changed prior to attach, the FUSB302T automatically indicates the programmed current capability when a device is attached. If the current capabilities are changed after a device is attached, the FUSB302T immediately changes the CC line to the programmed capability.

<sup>2.</sup> Processor then can perform a final manual check through I<sup>2</sup>C.

Figure 6. HOST\_CUR Changed After Attach

Figure 7. HOST\_CUR Changed Prior to Attach

The Type-C specification outlines different attach and detach thresholds for a Type-C host that are based on how much current is supplied to each CC pin. Based on the programmed HOST\_CUR setting, the software adjusts the

DAC comparator threshold to match the Type-C specification requirements. The BC\_LVL comparators can also be used as part of the Ra detection flow. This is summarized in Table 5.

**Table 5. HOST INTERRUPT SUMMARY**

|             |               | Interrupt Status |      |                     |               |

|-------------|---------------|------------------|------|---------------------|---------------|

| Termination | HOST_CUR[1:0] | BC_LVL[1:0]      | COMP | COMP Setting        | Attach/Detach |

| Ra          | 2'b01         | 2'b00            | NA   | NA                  | NA            |

|             | 2'b10         | 2'b01            | 0    | 6'b00_1010 (0.42 V) |               |

|             | 2'b11         | 2'b10            | 0    | 6'b01_0011 (0.8 V)  |               |

| Rd          | 2'b01, 2'b10  | NA               | 0    | 6'b10_0110 (1.6 V)  | Attach        |

|             |               | NA               | 1    | 6'b10_0110 (1.6 V)  | Detach        |

|             | 2'b11         | NA               | 0    | 6'b11_1110 (2.6 V)  | Attach        |

|             |               | NA               | 1    | 6'b11_1110 (2.6 V)  | Detach        |

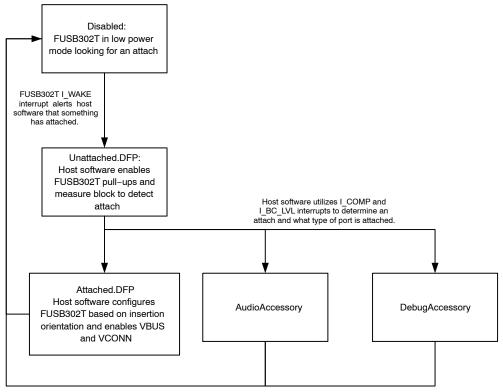

The high level software flow diagram for a Type-C Host (SRC) is shown below in Figure 8.

FUSB302T I\_COMP and I\_VBUSOK interrupts alert host software when accessory detach has occured

Figure 8. SRC Software Flow

## **Manual Dual-Role Detection and Configuration**

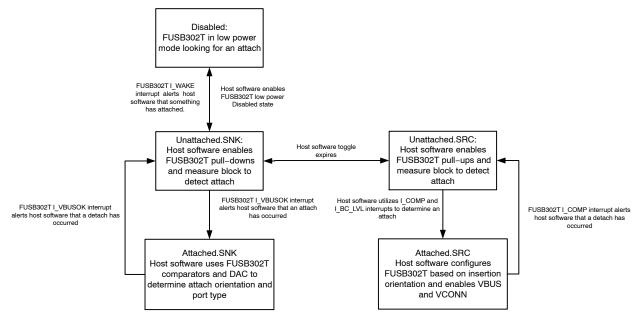

The Type-C specification allows ports to be both a device and a host depending on what type of port has attached. This functionality is similar to USB OTG ports with the current USB connectors and is called a dual-role port. The FUSB302T can be used to implement a dual-role port. A Type-C dual role port toggles between presenting as a Type-C device and a Type-C host. The host software controls the toggle time and configuration of the FUSB302T in each state as shown in Figure 9.

Figure 9. DRP Software Flow

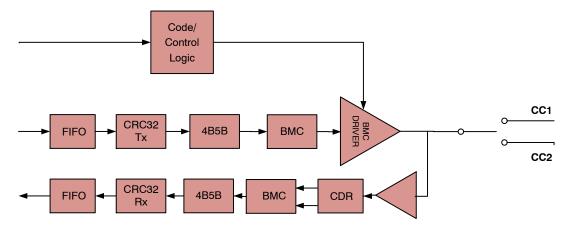

### **BMC POWER DELIVERY**

The Type-C connector allows USB Power Delivery (PD) to be communicated over the connected CC pin between two ports. The communication method is the BMC Power Delivery protocol and is used for many different reasons with the Type-C connector. Possible uses are outlined below.

- Negotiating and controlling charging power levels

- Alternative Interfaces such as MHL, Display Port

- Vendor specific interfaces for use with custom docks or accessories

- Role swap for dual-role ports that want to switch who is the host or device

- Communication with USB3.1 full featured cables

The FUSB302T integrates a thin BMC PD client which includes the BMC physical layer and packet FIFOs (48 bytes for transmit and 80 bytes for receive) which allows packets to be sent and received by the host software through I<sup>2</sup>C accesses. The FUSB302T allows host software to implement all features of USB BMC PD through writes and

reads of the FIFO and control of the FUSB302T physical interface.

The FUSB302T uses tokens to control the transmission of BMC PD packets. These tokens are written to the transmit FIFO and control how the packet is transmitted on the CC pin. The tokens are designed to be flexible and support all aspects of the USB PD specification. The FUSB302T additionally enables control of the BMC transmitter through tokens. The transmitter can be enabled or disabled by specific token writes which allow faster packet processing by burst writing the FIFO with all the information required to transmit a packet.

The FUSB302T receiver stores the received data and the received CRC in the receive FIFO when a valid packet is received on the CC pin. The BMC receiver automatically enables the internal oscillator when an Activity is sensed on the CC pin and load to the FIFO when a packet is received. The I\_ACTIVITY and I\_CRC\_CHK interrupts alert the host software that a valid packet was received.

Figure 10. USB BMC Power Delivery Blocks

### **Power Level Determination**

The Type-C specification outlines the order of precedence for power level determination which covers power levels from basic USB2.0 levels to the highest levels of USB PD. The host software is expected to follow the USB Type-C specification for charging current priority based on feedback from the FUSB302T detection, external BC1.2 detection and any USB Power Delivery communication.

The FUSB302T does not integrate BC1.2 charger detection which is assumed available in the USB transceiver or USB charger in the system.

## Power Up, Initialization and Reset

When power is first applied through VDD, the FUSB302T is reset and registers are initialized to the default values shown in the register map.

The FUSB302T can be reset through software by programming the SW\_RES bit in the RESET register.

### PD Automatic Receive GoodCRC

The power delivery packets require a GoodCRC acknowledge packet to be sent for each received packet where the calculated CRC is the correct value. This calculation is done by the FUSB302T and triggers the I\_CRC\_CHK interrupt if the CRC is good. If the AUTO\_CRC (Switches1 register bit) is set and AUTO\_PRE = 0, then the FUSB302T will automatically send the GoodCRC control packet in response to alleviate the local processor from responding quickly to the received packet. If GoodCRC is required for anything beyond SOP, then enable SOP\*.

#### PD Send

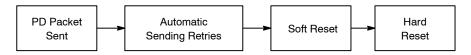

The FUSB302T implements part of the PD protocol layer for sending packets in an autonomous fashion.

Figure 11.

### **PD Automatic Sending Retries**

If GoodCRC packet is not received and AUTO\_RETRY is set, then a retry of the same message that was in the TxFIFO written by the processor is executed within t<sub>Retry</sub> and that is repeated for NRETRY times.

### **PD Send Soft Reset**

If the correct GoodCRC packet is still not received for all retries then I\_RETRYFAIL interrupt is triggered and if AUTO\_SOFT\_RESET is set, then a Soft Reset packet is created (MessageID is set to 0 and the processor upon servicing I\_RETRYFAIL would set the true MessageIDCounter to 0.

If this Soft Reset is sent successfully where a GoodCRC control packet is received with a MessageID = 0 then I\_TXSENT interrupt occurs.

If not, this Soft Reset packet is retried NRETRIES times (MessageID is always 0 for all retries) if a GoodCRC acknowledge packet is not received with CRCReceiveTimer expiring (t<sub>Receive</sub> of 1.1 ms max). If all retries fail, then I\_SOFTFAIL interrupt is triggered.

## **PD Send Hard Reset**

If all retries of the soft reset packet fail and if AUTO\_HARD\_RESET is set, then a hard reset ordered set is sent by loading up the TxFIFO with RESET1, RESET1, RESET1, RESET2 and sending a hard reset. Note only one

hard reset is sent since the typical retry mechanism doesn't apply. The processor's policy engine firmware is responsible for retrying the hard reset if it doesn't receive the required response.

## Flush Rx-FIFO with Built-In Self Test (BIST) Test Data

During PD compliance testing, BIST test packets are used to test physical layer of the PD interface such as, frequency derivation, Amplitude measure and etc. The one BIST test data packet has 7 data objects (28byte data), header and CRC, but the message ID doesn't change, the packet should be ignored and not acted on by the PD policy engine. The PD protocol layer does need to send a GoodCRC message back after every packet. The BIST data can arrive continuously from a tester, which could cause the FUSB302T Rx FIFO to overflow and the PD protocol layer to stop sending GoodCRC messages unless the FIFO is read or cleared quickly. The FUSB302T has a special register bit in the I<sup>2</sup>C registers, bit[5] of address 0x09, that when the bit is set, all the data received next will be flushed from the RxFIFO automatically and the PD protocol layer will keep sending GoodCRC messages back. Once BIST test is done, tester sends HardReset, so with the HardReset, processor has to write the bit back to disable. Also, if the bit can be de-selected anytime, then the coming packet has to be managed by protocol layer and policy engine.

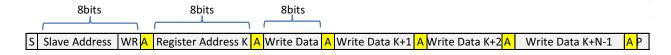

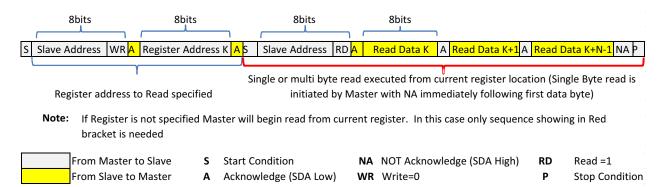

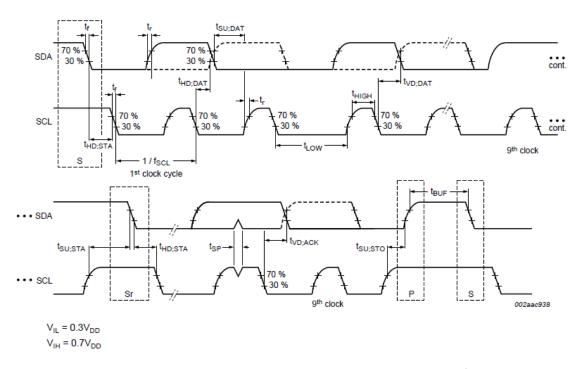

## I<sup>2</sup>C INTERFACE

The FUSB302T includes a full I<sup>2</sup>C slave controller. The I<sup>2</sup>C slave fully complies with the I<sup>2</sup>C specification version 6 requieremnts. This block is designed for Fast Mode Plus traffic up to 1 MHz SCL operation.

The TOGGLE features allow for very low power operation with slow clocking thus may not be fully

compliant to the 1 MHz operation. Examples of an I<sup>2</sup>C write and read sequence are shown in Figure 12 and Figure 13 respectively.

Figure 12. I<sup>2</sup>C Write Example

Figure 13. I<sup>2</sup>C Read Example

### **Table 6. ABSOLUTE MAXIMUM RATINGS**

| Symbol                | Parameter                                                 | Parameter |      |      | Unit |

|-----------------------|-----------------------------------------------------------|-----------|------|------|------|

| Vv <sub>DD</sub>      | Supply Voltage from V <sub>DD</sub>                       |           |      | 6.0  | V    |

| V <sub>CC_HDDRP</sub> | CC pins when configured as Host, Device or Dual Role Port |           | -0.5 | 6.0  | V    |

| V <sub>VBUS</sub>     | VBUS Supply Voltage                                       | -0.5      | 28.0 | V    |      |

| T <sub>STORAGE</sub>  | Storage Temperature Range                                 |           |      | +150 | °C   |

| $T_J$                 | Maximum Junction Temperature                              |           | -    | +150 | °C   |

| T <sub>L</sub>        | Lead Temperature (Soldering, 10 Seconds)                  |           |      | +260 | °C   |

| ESD                   | Human Body Model, ANSI/ESDA/JEDEC JS-001-2012 All Pins    |           | 4    | -    | kV   |

|                       | Charged Device Model, JEDEC JESD22-C101                   | All Pins  | 1    | -    |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

**Table 7. RECOMMENDED OPERATING CONDITIONS**

| Symbol             | Parameter                      | Min          | Тур | Max  | Unit |

|--------------------|--------------------------------|--------------|-----|------|------|

| V <sub>VBUS</sub>  | VBUS Supply Voltage            | 4.0          | 5.0 | 21.0 | V    |

| V <sub>VDD</sub>   | VDD Supply Voltage             | 2.7 (Note 3) | 3.3 | 5.5  | V    |

| V <sub>VCONN</sub> | VCONN Supply Voltage           | 2.7          | -   | 5.5  | V    |

| I <sub>VCONN</sub> | VCONN Supply Current           | -            | -   | 560  | mA   |

| T <sub>A</sub>     | Operating Temperature          | -40          | -   | +85  | °C   |

| T <sub>A</sub>     | Operating Temperature (Note 4) | -40          | -   | +105 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

<sup>3.</sup> This is for functional operation only and not the lowest limit for all subsequent electrical specifications below. All electrical parameters have a minimum of 3.0 V operation.

<sup>4.</sup> Automotive part only, FUSB302TVMPX, FUSB302TV01MPX, FUSB302TV10MPX, FUSB302TV11MPX

# **DC AND TRANSIENT CHARACTERISTICS**

All typical values are at  $T_A = 25^{\circ}C$  unless otherwise specified.

Table 8. BASEBAND PD

|                         |                                                                                                          | T <sub>A</sub> = -40 to +85°C<br>T <sub>A</sub> = -40 to +105°C (Note 9)<br>T <sub>J</sub> = -40 to +125°C |     |      |      |

|-------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|------|------|

| Symbol                  | Parameter                                                                                                | Min                                                                                                        | Тур | Max  | Unit |

| UI                      | Unit Interval                                                                                            | 3.03                                                                                                       | -   | 3.70 | μs   |

| TRANSMITTER             | ł                                                                                                        |                                                                                                            |     |      |      |

| zDriver                 | Transmitter Output Impedance                                                                             | 33                                                                                                         | -   | 75   | Ω    |

| tEndDriveBMC            | Time to Cease Driving the Line after the end of the last bit of the Frame                                | -                                                                                                          | -   | 23   | μs   |

| t <sub>HoldLowBMC</sub> | Time to Cease Driving the Line after the final High-to-Low Transition                                    | 1                                                                                                          | -   | -    | μs   |

| V <sub>OH</sub>         | Logic High Voltage                                                                                       | 1.05                                                                                                       | -   | 1.20 | V    |

| V <sub>OL</sub>         | Logic Low Voltage                                                                                        | 0                                                                                                          | -   | 75   | mV   |

| t <sub>StartDrive</sub> | Time before the start of the first bit of the preamble when the transmitter shall start driving the line | -1                                                                                                         | -   | 1    | μs   |

| t <sub>RISE_TX</sub>    | Rise Time                                                                                                | 300                                                                                                        | -   | -    | ns   |

| t <sub>FALL_TX</sub>    | Fall Time                                                                                                | 300                                                                                                        | -   | -    | ns   |

| RECEIVER                |                                                                                                          |                                                                                                            |     |      |      |

| cReceiver               | Receiver Capacitance when Driver isn't Turned On                                                         | -                                                                                                          | 50  | -    | pF   |

| zBmcRx                  | Receiver Input Impedance                                                                                 | 1                                                                                                          | -   | -    | MΩ   |

| tRxFilter               | Rx Bandwidth Limiting Filter (Note 5)                                                                    | 100                                                                                                        | -   | -    | ns   |

<sup>5.</sup> Guaranteed by Characterization and/or Design. Not production tested.

Figure 14. Transmitter Test Load

Table 9. TYPE-C CC SWITCH

| R <sub>SW_CCX</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      |                                                                  | $T_A = -40$      | = -40 to +89<br>to +105°C<br>: -40 to +12 | (Note 9)         |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------|------------------|-------------------------------------------|------------------|------|

| Isw_CCX   Over-Current Protection (OCP) limit at which VCONN switch shuts off over the entire VCONN voltage range (OCPreg = 0Fh)   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1000   1  | Symbol               | Parameter                                                        | Min              | Тур                                       | Max              | Unit |

| Time taken for the VCONN switch to turn on during which                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R <sub>SW_CCx</sub>  | R <sub>DSON</sub> for SW1_CC1 and SW1_CC2, VCONN to CC1 & CC2    | -                | 0.4                                       | 1.2              | Ω    |

| Over-Current Protection is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | lsw_ccx              |                                                                  | 600              | 800                                       | 1000             | mA   |

| I_180_CCX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | tSoftStart           |                                                                  | -                | 1.5                                       | -                | ms   |

| Sa30_CCX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I <sub>80_CCX</sub>  | SRC 80 µA CC current (Default) HOST_CUR1 = 0, HOST_CUR0 = 1      | 64               | 80                                        | 96               | μΑ   |

| R_DEVICE   Device Pull-down Resistance (Note 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I <sub>180_CCX</sub> | SRC 180 µA CC Current (1.5 A) HOST_CUR1 = 1, HOST_CUR0 = 0       | 166              | 180                                       | 194              | μΑ   |

| ZOPEN   CC Resistance for Disabled State   126   -   -   KC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I <sub>330_CCX</sub> | SRC 330 µA CC Current (3 A) HOST_CUR1 = 1, HOST_CUR0 = 1         | 304              | 330                                       | 356              | μΑ   |

| WAKE <sub>low</sub> Wake threshold for CC pin SRC or SNK LOW value. Assumes bandgap and wake circuit turned on ie PWR[0] = 1         -         0.25         -         V           WAKE <sub>high</sub> Wake threshold for CC pin SRC or SNK HIGH value. Assumes bandgap and wake circuit turned on ie PWR[0] = 1         -         1.45         -         V           vBC_LVLhys         Hysteresis on the Ra and Rd Comparators (Note 8)         -         20         -         mN           vBC_LVL         CC Pin Thresholds, Assumes PWR = 4'h7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R <sub>DEVICE</sub>  | Device Pull-down Resistance (Note 6)                             | 4.6              | 5.1                                       | 5.6              | kΩ   |

| WAKE   bandgap and wake circuit turned on ie PWR[0] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | zOPEN                | CC Resistance for Disabled State                                 | 126              | -                                         | -                | kΩ   |

| bandgap and wake circuit turned on ie PWR[0] = 1   vBC_LVLhys                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | WAKE <sub>low</sub>  |                                                                  | -                | 0.25                                      | _                | V    |

| VBC_LVL         CC Pin Thresholds, Assumes PWR = 4'h7         0.15         0.20         0.25           BC = 2'b01         0.61         0.66         0.70           BC = 2'b10         1.16         1.23         1.31           VMDACstepCC         Measure block MDAC step size for each code in MDAC[5:0] register         -         42         -         m\           VMDACstepVBUS         Measure block MDAC step size for each code in MDAC[5:0] register         -         420         -         m\           VVBUSthr         VBUS threshold at which I VBUSOK interrupt is triggered. Assumes measure block on ie PWR[2] = 1         -         -         4.0         V           tTOG1         When TOGGLE = 1, time at which internal versions of PU_EN1 = 1 or PU_EN1 = PU_EN2 = 0 and PWDN1 = PDWN2 = 1 selected to present externally as a SNK in the DRP toggle         30         45         60         ms           tTOG2         When TOGGLE = 1, time at which internal versions of PU_EN1 = 1 or PU_EN2 = 1 and PWDN1 = PDWN2 = 0 selected to present externally as a SRC in the DRP toggle         30         40         ms           tDIS         Disable time after a full toggle (tTOG1 + tTOG2) cycle so as to save power         -         0         -           TOG_SAVE_PWR2:1 = 00         -         -         40         -           TOG_SAVE_PWR2:1 = 10         -         40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | WAKE <sub>high</sub> |                                                                  | -                | 1.45                                      | _                | V    |

| BC = 2'b00   BC = 2'b01   D.25   D.25   D.61   D.66   D.66   D.70   D.66   D.70   D.66   D.70   D.66   D.61   D.66   D.70   D.70   D.66   D.70   D.70   D.66   D.70   D.70   D.66   D.70   D.70   D.70   D.66   D.70   D.70   D.66   D.70   D. | vBC_LVLhys           | Hysteresis on the Ra and Rd Comparators (Note 8)                 | -                | 20                                        | -                | mV   |

| vMDACstepVBUS       Measure block MDAC step size for each code in MDAC[5:0] register for VBUS measurement       -       420       -       m\         vVBUSthr       VBUS threshold at which I_VBUSOK interrupt is triggered. Assumes measure block on ie PWR[2] = 1       -       -       4.0       V         tTOG1       When TOGGLE = 1, time at which internal versions of PU_EN1 = PU_EN2 = 0 and PWDN1 = PDWN2 = 1 selected to present externally as a SNK in the DRP toggle       30       45       60       ms         tTOG2       When TOGGLE = 1, time at which internal versions of PU_EN1 = 1 or PU_EN2 = 1 and PWDN1 = PDWN2 = 0 selected to present externally as a SRC in the DRP toggle       20       30       40       ms         tDIS       Disable time after a full toggle (tTOG1 + tTOG2) cycle so as to save power TOG_SAVE_PWR2:1 = 00 TOG_SAVE_PWR2:1 = 01 TOG_SAVE_PWR2:1 = 01 TOG_SAVE_PWR2:1 = 01 TOG_SAVE_PWR2:1 = 10       -       0       -       0       -       -       40       -       -       -       -       40       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | vBC_LVL              | BC = 2'b00<br>BC = 2'b01                                         | 0.61             | 0.66                                      | 0.70             | V    |

| for VBUS measurement  VBUS threshold at which I_VBUSOK interrupt is triggered. Assumes measure block on ie PWR[2] = 1  tTOG1  When TOGGLE = 1, time at which internal versions of PU_EN1 = PU_EN2 = 0 and PWDN1 = PDWN2 = 1 selected to present externally as a SNK in the DRP toggle  tTOG2  When TOGGLE = 1, time at which internal versions of PU_EN1 = 1 or PU_EN2 = 1 and PWDN1 = PDWN2 = 0 selected to present externally as a SRC in the DRP toggle  tDIS  Disable time after a full toggle (tTOG1 + tTOG2) cycle so as to save power TOG_SAVE_PWR2:1 = 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | vMDACstepCC          | Measure block MDAC step size for each code in MDAC[5:0] register | _                | 42                                        | -                | mV   |

| TOG1   When TOGGLE = 1, time at which internal versions of   30   45   60   ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | vMDACstepVBUS        |                                                                  | -                | 420                                       | _                | mV   |

| PU_EN1 = PU_EN2 = 0 and PWDN1 = PDWN2 = 1 selected to present externally as a SNK in the DRP toggle  tTOG2  When TOGGLE = 1, time at which internal versions of PU_EN1 = 1 or PU_EN2 = 1 and PWDN1 = PDWN2 = 0 selected to present externally as a SRC in the DRP toggle  tDIS  Disable time after a full toggle (tTOG1 + tTOG2) cycle so as to save power TOG_SAVE_PWR2:1 = 00 - 0 - 0 - 0 - 0 - 0 - 0 - 0 - 0 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | vVBUSthr             |                                                                  | -                | -                                         | 4.0              | V    |

| or PU_EN2 = 1 and PWDN1 = PDWN2 = 0 selected to present externally as a SRC in the DRP toggle  tDIS  Disable time after a full toggle (tTOG1 + tTOG2) cycle so as to save power  TOG_SAVE_PWR2:1 = 00  TOG_SAVE_PWR2:1 = 01  TOG_SAVE_PWR2:1 = 10  TOG_SAVE_PWR2:1 = 10  TOG_SAVE_PWR2:1 = 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | tTOG1                | PU_EN1 = PU_EN2 = 0 and PWDN1 = PDWN2 = 1 selected to            | 30               | 45                                        | 60               | ms   |

| power<br>  TOG_SAVE_PWR2:1 = 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | tTOG2                | or PU_EN2 = 1 and PWDN1 = PDWN2 = 0 selected to present          | 20               | 30                                        | 40               | ms   |

| TOG_SAVE_PWR2:1 = 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | tDIS                 |                                                                  |                  |                                           |                  | ms   |