### **Freescale Semiconductor**

Data Sheet: Technical Data

## Document Number: P2040EC

Rev. 2, 02/2013

## P2040

# P2040 QorlQ Integrated Processor Hardware Specifications

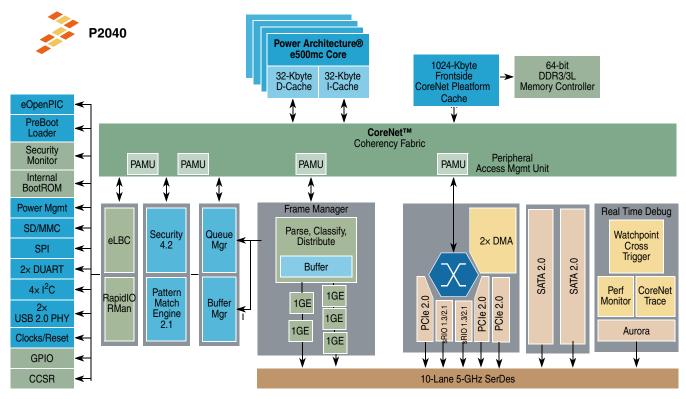

The P2040 QorIQ integrated communication processor combines four Power Architecture® processor cores with high performance data path acceleration logic and network and peripheral bus interfaces required for networking, telecom/datacom, wireless infrastructure, and aerospace applications.

This chip can be used for combined control, data path, and application layer processing in routers, switches, base station controllers, and general-purpose embedded computing. Its high level of integration offers significant performance benefits compared to multiple discrete devices, while also greatly simplifying board design.

This chip includes the following functions and features:

- Four e500mc Power Architecture cores

- Three levels of instructions: User, supervisor, and hypervisor

- Independent boot and reset

- Secure boot capability

- CoreNet fabric supporting coherent and non-coherent transactions amongst CoreNet endpoints

- One 1 MB CoreNet platform cache with ECC

- CoreNet bridges between the CoreNet fabric the I/Os, data path accelerators, and high and low speed peripheral interfaces

- Five 1-Gigabit Ethernet controllers

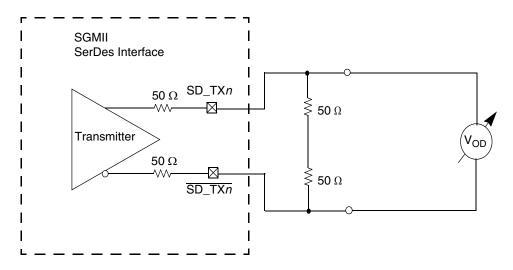

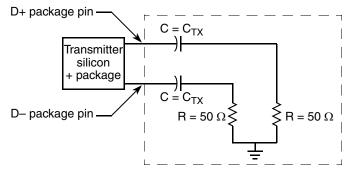

- 2.5 Gbps SGMII interfaces

- RGMII interfaces

- One 64-bit DDR3 and DDR3L SDRAM memory controller with ECC

- Multicore programmable interrupt controller

- Four I<sup>2</sup>C controllers

- Four 2-pin UARTs or two 4-pin UARTs

- Two 4-channel DMA engines

- Enhanced local bus controller (eLBC)

- Three PCI Express 2.0 controllers/ports

- Two serial RapidIO® controllers/ports (sRIO port) supporting version 1.3 with features 2.1

- Two serial ATA (SATA 2.0) controllers

- Enhanced secure digital host controller (SD/MMC)

- Enhanced serial peripheral interface (eSPI)

- 2× high-speed USB 2.0 controllers with integrated PHYs

\* freescale™

© 2010-2013 Freescale Semiconductor, Inc. All rights reserved.

# **Table of Contents**

| 1 | Pin A | ssignments and Reset States                       |

|---|-------|---------------------------------------------------|

|   | 1.1   | 780 FC-PBGA Ball Layout Diagrams                  |

|   | 1.2   | Pinout List                                       |

| 2 | Elect | rical Characteristics37                           |

|   | 2.1   | Overall DC Electrical Characteristics             |

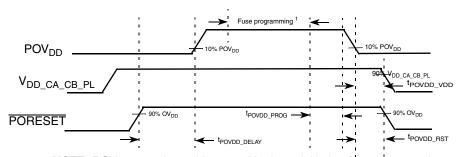

|   | 2.2   | Power Up Sequencing42                             |

|   | 2.3   | Power Down Requirements                           |

|   | 2.4   | Power Characteristics                             |

|   | 2.5   | Thermal47                                         |

|   | 2.6   | Input Clocks                                      |

|   | 2.7   | RESET Initialization51                            |

|   | 2.8   | Power-on Ramp Rate                                |

|   | 2.9   | DDR3 and DDR3L SDRAM Controller                   |

|   | 2.10  | eSPI59                                            |

|   | 2.11  | DUART61                                           |

|   | 2.12  | Ethernet: Data path Three-Speed Ethernet (dTSEC), |

|   |       | Management Interface, IEEE Std 1588 62            |

|   | 2.13  | USB69                                             |

|   | 2.14  | Enhanced Local Bus Interface                      |

|   | 2.15  | Enhanced Secure Digital Host Controller (eSDHC)74 |

|   | 2.16  | Multicore Programmable Interrupt Controller (MPIC |

|   |       | Specifications                                    |

|   | 2.17  | JTAG Controller                                   |

|   | 2.18  | l <sup>2</sup> C                                     |

|---|-------|------------------------------------------------------|

|   | 2.19  | GPIO                                                 |

|   | 2.20  | High-Speed Serial Interfaces (HSSI)                  |

| 3 | Hard  | ware Design Considerations                           |

|   | 3.1   | System Clocking                                      |

|   | 3.2   | Supply Power Default Setting                         |

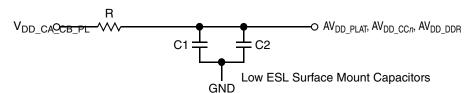

|   | 3.3   | Power Supply Design                                  |

|   | 3.4   | Decoupling Recommendations                           |

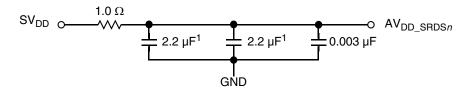

|   | 3.5   | SerDes Block Power Supply Decoupling                 |

|   |       | Recommendations                                      |

|   | 3.6   | Connection Recommendations                           |

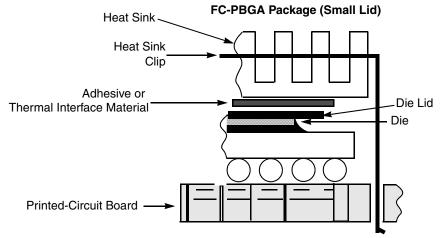

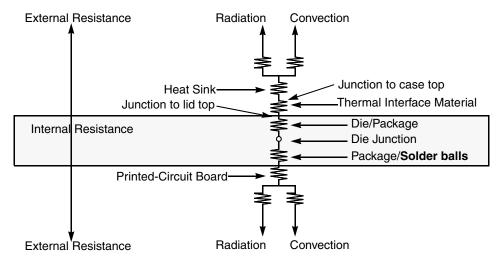

|   | 3.7   | Recommended Thermal Model 130                        |

|   | 3.8   | Thermal Management Information                       |

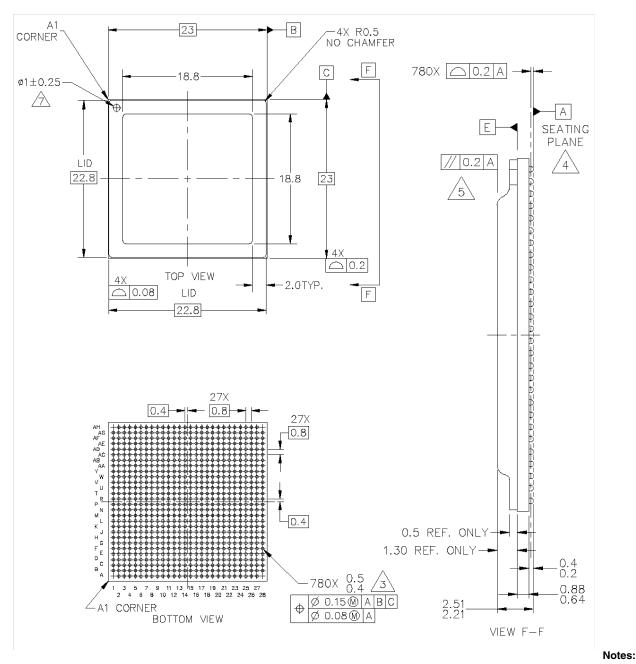

| 4 | Packa | age Information                                      |

|   | 4.1   | Package Parameters for the FC-PBGA                   |

|   | 4.2   | Mechanical Dimensions of the FC-PBGA 133             |

| 5 | Secu  | rity Fuse Processor                                  |

| 6 | Orde  | ring Information                                     |

|   | 6.1   | Part Numbering Nomenclature                          |

|   | 6.2   | Orderable Part Numbers Addressed by this Document134 |

| 7 | Revis | sion History                                         |

|   |       |                                                      |

This figure shows the major functional units within the chip.

Figure 1. Block Diagram

# 1 Pin Assignments and Reset States

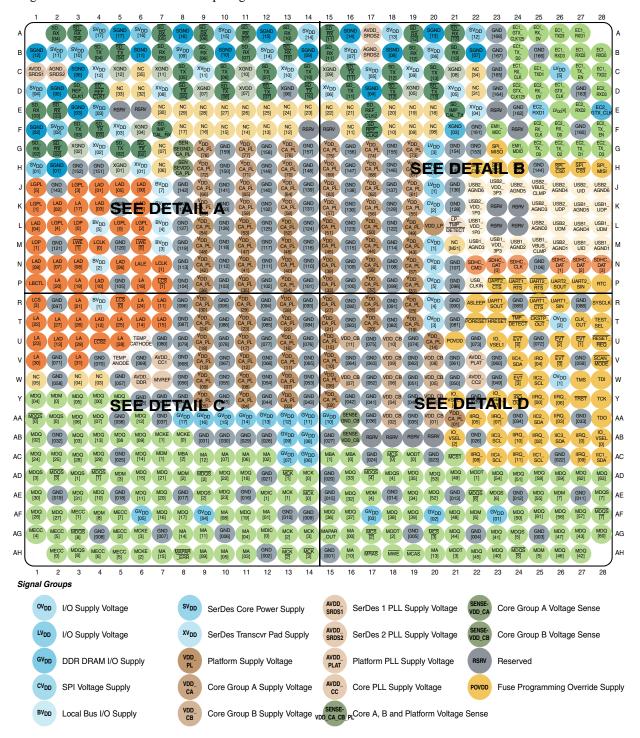

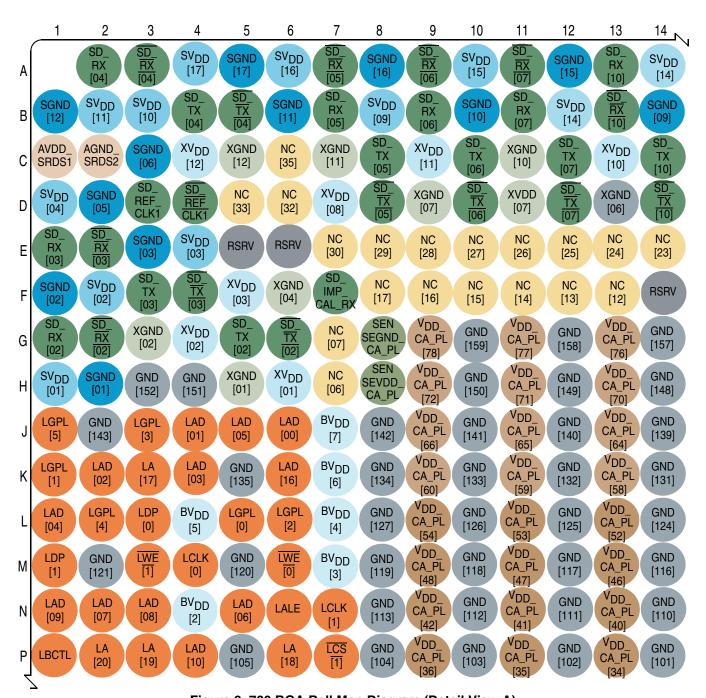

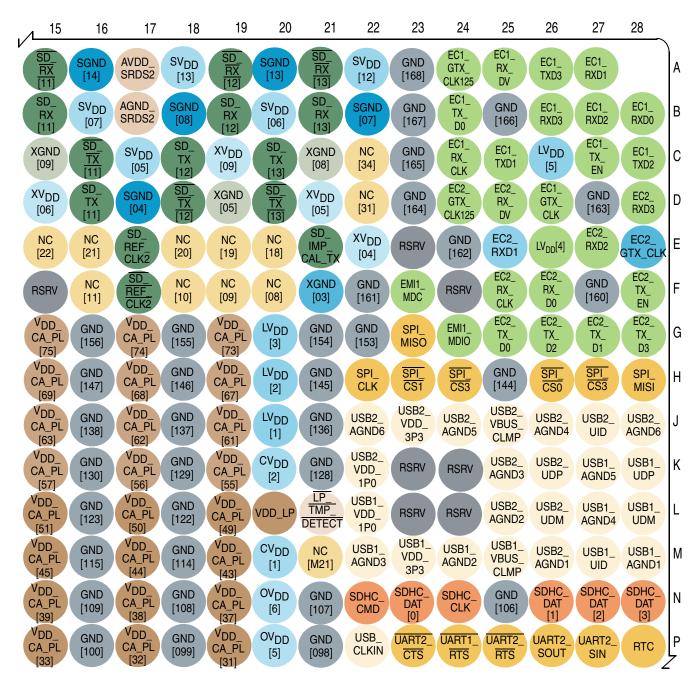

This section provides a top view of the ball layout diagram and four detailed views by quadrant. It also provides a pinout listing by bus.

## 1.1 780 FC-PBGA Ball Layout Diagrams

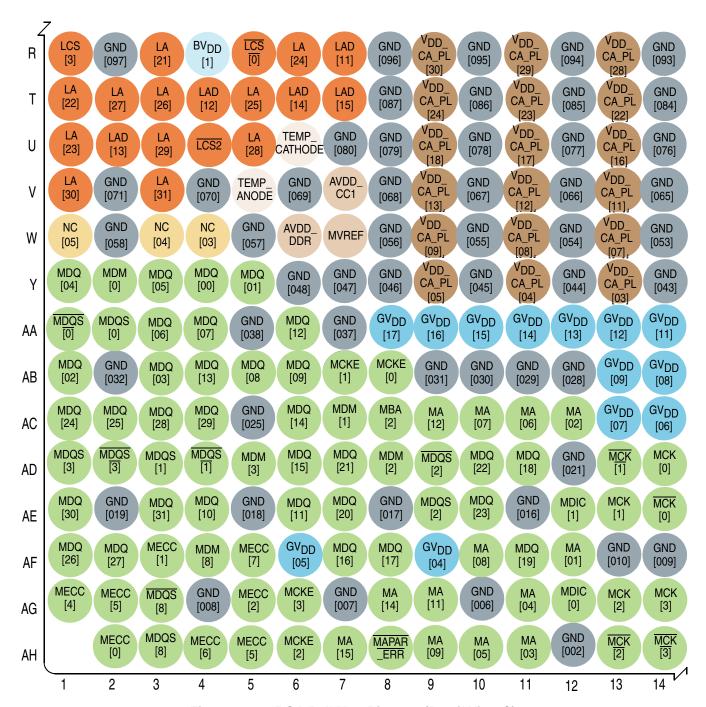

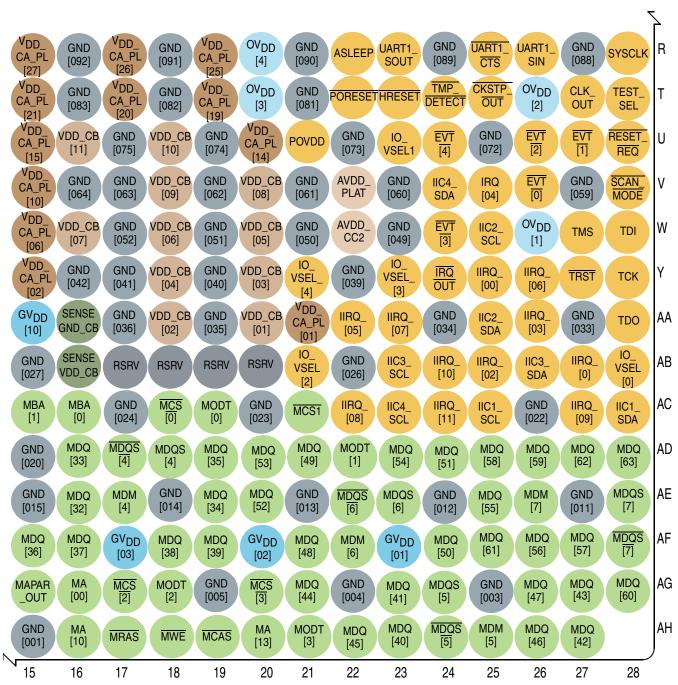

These figures show the FC-PBGA ball map diagrams.

Figure 2. 780 BGA Ball Map Diagram (Top View)

Figure 3. 780 BGA Ball Map Diagram (Detail View A)

Figure 4. 780 BGA Ball Map Diagram (Detail View B)

Figure 5. 780 BGA Ball Map Diagram (Detail View C)

Figure 6. 780 BGA Ball Map Diagram (Detail View D)

## 1.2 Pinout List

This table provides the pinout listing for the 780 FC-PBGA package by bus. Pins for multiplexed signals appear in the bus group for their default status and have a corresponding note stating that they have multiple functionality depending on the mode in which they are configured.

Table 1. Pin List by Bus

| Signal | Signal Description         | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note       |

|--------|----------------------------|-----------------------|-------------|------------------|------------|

|        | DDR SDRAM Memory Interface |                       |             |                  |            |

| MDQ00  | Data                       | Y4                    | I/O         | GV <sub>DD</sub> | _          |

| MDQ01  | Data                       | Y5                    | I/O         | $GV_DD$          | _          |

| MDQ02  | Data                       | AB1                   | I/O         | $GV_DD$          | _          |

| MDQ03  | Data                       | AB3                   | I/O         | GV <sub>DD</sub> | _          |

| MDQ04  | Data                       | Y1                    | I/O         | $GV_DD$          | _          |

| MDQ05  | Data                       | Y3                    | I/O         | $GV_DD$          | _          |

| MDQ06  | Data                       | AA3                   | I/O         | GV <sub>DD</sub> | _          |

| MDQ07  | Data                       | AA4                   | I/O         | $GV_DD$          | _          |

| MDQ08  | Data                       | AB5                   | I/O         | GV <sub>DD</sub> | <b>—</b>   |

| MDQ09  | Data                       | AB6                   | I/O         | GV <sub>DD</sub> | <b>—</b>   |

| MDQ10  | Data                       | AE4                   | I/O         | GV <sub>DD</sub> | _          |

| MDQ11  | Data                       | AE6                   | I/O         | GV <sub>DD</sub> | _          |

| MDQ12  | Data                       | AA6                   | I/O         | GV <sub>DD</sub> | _          |

| MDQ13  | Data                       | AB4                   | I/O         | GV <sub>DD</sub> | _          |

| MDQ14  | Data                       | AC6                   | I/O         | GV <sub>DD</sub> | <b>—</b>   |

| MDQ15  | Data                       | AD6                   | I/O         | GV <sub>DD</sub> | _          |

| MDQ16  | Data                       | AF7                   | I/O         | GV <sub>DD</sub> | _          |

| MDQ17  | Data                       | AF8                   | I/O         | GV <sub>DD</sub> | _          |

| MDQ18  | Data                       | AD11                  | I/O         | GV <sub>DD</sub> | _          |

| MDQ19  | Data                       | AF11                  | I/O         | GV <sub>DD</sub> | _          |

| MDQ20  | Data                       | AE7                   | I/O         | GV <sub>DD</sub> | <b>—</b>   |

| MDQ21  | Data                       | AD7                   | I/O         | GV <sub>DD</sub> | <b>—</b>   |

| MDQ22  | Data                       | AD10                  | I/O         | GV <sub>DD</sub> | _          |

| MDQ23  | Data                       | AE10                  | I/O         | GV <sub>DD</sub> | _          |

| MDQ24  | Data                       | AC1                   | I/O         | GV <sub>DD</sub> | _          |

| MDQ25  | Data                       | AC2                   | I/O         | GV <sub>DD</sub> | <b>†</b> – |

| MDQ26  | Data                       | AF1                   | I/O         | GV <sub>DD</sub> | <b>†</b> – |

| MDQ27  | Data                       | AF2                   | I/O         | GV <sub>DD</sub> | <b>†</b> – |

| MDQ28  | Data                       | AC3                   | I/O         | GV <sub>DD</sub> | _          |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal | Signal Description | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note |

|--------|--------------------|-----------------------|-------------|------------------|------|

| MDQ29  | Data               | AC4                   | I/O         | GV <sub>DD</sub> | _    |

| MDQ30  | Data               | AE1                   | I/O         | $GV_DD$          | _    |

| MDQ31  | Data               | AE3                   | I/O         | $GV_DD$          | _    |

| MDQ32  | Data               | AE16                  | I/O         | $GV_DD$          | _    |

| MDQ33  | Data               | AD16                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ34  | Data               | AE19                  | I/O         | $GV_DD$          | _    |

| MDQ35  | Data               | AD19                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ36  | Data               | AF15                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ37  | Data               | AF16                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ38  | Data               | AF18                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ39  | Data               | AF19                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ40  | Data               | AH23                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ41  | Data               | AG23                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ42  | Data               | AH27                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ43  | Data               | AG27                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ44  | Data               | AG21                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ45  | Data               | AH22                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ46  | Data               | AH26                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ47  | Data               | AG26                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ48  | Data               | AF21                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ49  | Data               | AD21                  | I/O         | $GV_DD$          | _    |

| MDQ50  | Data               | AF24                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ51  | Data               | AD24                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ52  | Data               | AE20                  | I/O         | $GV_DD$          | _    |

| MDQ53  | Data               | AD20                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ54  | Data               | AD23                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ55  | Data               | AE25                  | I/O         | $GV_DD$          | _    |

| MDQ56  | Data               | AF26                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ57  | Data               | AF27                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ58  | Data               | AD25                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ59  | Data               | AD26                  | I/O         | $GV_DD$          | _    |

| MDQ60  | Data               | AG28                  | I/O         | $GV_DD$          | _    |

| MDQ61  | Data               | AF25                  | I/O         | GV <sub>DD</sub> | _    |

| MDQ62  | Data               | AD27                  | I/O         | GV <sub>DD</sub> | _    |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal    | Signal Description    | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note |

|-----------|-----------------------|-----------------------|-------------|------------------|------|

| MDQ63     | Data                  | AD28                  | I/O         | GV <sub>DD</sub> | _    |

| MECC0     | Error Correcting Code | AH2                   | I/O         | $GV_DD$          | _    |

| MECC1     | Error Correcting Code | AF3                   | I/O         | $GV_DD$          | _    |

| MECC2     | Error Correcting Code | AG5                   | I/O         | $GV_DD$          | _    |

| MECC3     | Error Correcting Code | AH5                   | I/O         | GV <sub>DD</sub> | _    |

| MECC4     | Error Correcting Code | AG1                   | I/O         | $GV_DD$          | _    |

| MECC5     | Error Correcting Code | AG2                   | I/O         | $GV_DD$          | _    |

| MECC6     | Error Correcting Code | AH4                   | I/O         | GV <sub>DD</sub> | _    |

| MECC7     | Error Correcting Code | AF5                   | I/O         | GV <sub>DD</sub> | _    |

| MAPAR_ERR | Address Parity Error  | AH8                   | I           | GV <sub>DD</sub> | 4    |

| MAPAR_OUT | Address Parity Out    | AG15                  | 0           | GV <sub>DD</sub> | _    |

| MDM0      | Data Mask             | Y2                    | 0           | GV <sub>DD</sub> | _    |

| MDM1      | Data Mask             | AC7                   | 0           | GV <sub>DD</sub> | _    |

| MDM2      | Data Mask             | AD8                   | 0           | GV <sub>DD</sub> | _    |

| MDM3      | Data Mask             | AD5                   | 0           | GV <sub>DD</sub> | _    |

| MDM4      | Data Mask             | AE17                  | 0           | GV <sub>DD</sub> | _    |

| MDM5      | Data Mask             | AH25                  | 0           | GV <sub>DD</sub> | _    |

| MDM6      | Data Mask             | AF22                  | 0           | GV <sub>DD</sub> | _    |

| MDM7      | Data Mask             | AE26                  | 0           | GV <sub>DD</sub> | _    |

| MDM8      | Data Mask             | AF4                   | 0           | GV <sub>DD</sub> | _    |

| MDQS0     | Data Strobe           | AA2                   | I/O         | $GV_DD$          | _    |

| MDQS1     | Data Strobe           | AD3                   | I/O         | GV <sub>DD</sub> | _    |

| MDQS2     | Data Strobe           | AE9                   | I/O         | GV <sub>DD</sub> | _    |

| MDQS3     | Data Strobe           | AD1                   | I/O         | $GV_DD$          | _    |

| MDQS4     | Data Strobe           | AD18                  | I/O         | GV <sub>DD</sub> | _    |

| MDQS5     | Data Strobe           | AG24                  | I/O         | GV <sub>DD</sub> | _    |

| MDQS6     | Data Strobe           | AE23                  | I/O         | $GV_DD$          | _    |

| MDQS7     | Data Strobe           | AE28                  | I/O         | GV <sub>DD</sub> | _    |

| MDQS8     | Data Strobe           | AH3                   | I/O         | GV <sub>DD</sub> | _    |

| MDQS0     | Data Strobe           | AA1                   | I/O         | GV <sub>DD</sub> | _    |

| MDQS1     | Data Strobe           | AD4                   | I/O         | $GV_DD$          | _    |

| MDQS2     | Data Strobe           | AD9                   | I/O         | $GV_DD$          | _    |

| MDQS3     | Data Strobe           | AD2                   | I/O         | $GV_DD$          | _    |

| MDQS4     | Data Strobe           | AD17                  | I/O         | $GV_DD$          | _    |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal | Signal Description    | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note     |

|--------|-----------------------|-----------------------|-------------|------------------|----------|

| MDQS5  | Data Strobe           | AH24                  | I/O         | GV <sub>DD</sub> | _        |

| MDQS6  | Data Strobe           | AE22                  | I/O         | $GV_DD$          | _        |

| MDQS7  | Data Strobe           | AF28                  | I/O         | $GV_DD$          | _        |

| MDQS8  | Data Strobe           | AG3                   | I/O         | $GV_DD$          | _        |

| MBA0   | Bank Select           | AC16                  | 0           | $GV_DD$          | _        |

| MBA1   | Bank Select           | AC15                  | 0           | GV <sub>DD</sub> | _        |

| MBA2   | Bank Select           | AC8                   | 0           | GV <sub>DD</sub> | _        |

| MA00   | Address               | AG16                  | 0           | $GV_DD$          | _        |

| MA01   | Address               | AF12                  | 0           | GV <sub>DD</sub> | _        |

| MA02   | Address               | AC12                  | 0           | GV <sub>DD</sub> | _        |

| MA03   | Address               | AH11                  | 0           | GV <sub>DD</sub> | _        |

| MA04   | Address               | AG11                  | 0           | GV <sub>DD</sub> | _        |

| MA05   | Address               | AH10                  | 0           | GV <sub>DD</sub> | _        |

| MA06   | Address               | AC11                  | 0           | GV <sub>DD</sub> | _        |

| MA07   | Address               | AC10                  | 0           | GV <sub>DD</sub> | _        |

| MA08   | Address               | AF10                  | 0           | GV <sub>DD</sub> | _        |

| MA09   | Address               | AH9                   | 0           | GV <sub>DD</sub> | _        |

| MA10   | Address               | AH16                  | 0           | GV <sub>DD</sub> | _        |

| MA11   | Address               | AG9                   | 0           | GV <sub>DD</sub> | _        |

| MA12   | Address               | AC9                   | 0           | GV <sub>DD</sub> | _        |

| MA13   | Address               | AH20                  | 0           | GV <sub>DD</sub> | _        |

| MA14   | Address               | AG8                   | 0           | GV <sub>DD</sub> | _        |

| MA15   | Address               | AH7                   | 0           | GV <sub>DD</sub> | _        |

| MWE    | Write Enable          | AH18                  | 0           | GV <sub>DD</sub> | _        |

| MRAS   | Row Address Strobe    | AH17                  | 0           | GV <sub>DD</sub> | _        |

| MCAS   | Column Address Strobe | AH19                  | 0           | GV <sub>DD</sub> | _        |

| MCS0   | Chip Select           | AC18                  | 0           | GV <sub>DD</sub> | _        |

| MCS1   | Chip Select           | AC21                  | 0           | GV <sub>DD</sub> | _        |

| MCS2   | Chip Select           | AG17                  | 0           | GV <sub>DD</sub> | _        |

| MCS3   | Chip Select           | AG20                  | 0           | GV <sub>DD</sub> | <b>—</b> |

| MCKE0  | Clock Enable          | AB8                   | 0           | GV <sub>DD</sub> | <u> </u> |

| MCKE1  | Clock Enable          | AB7                   | 0           | GV <sub>DD</sub> | _        |

| MCKE2  | Clock Enable          | AH6                   | 0           | GV <sub>DD</sub> | _        |

| MCKE3  | Clock Enable          | AG6                   | 0           | GV <sub>DD</sub> | _        |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal | Signal Description             | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note |

|--------|--------------------------------|-----------------------|-------------|------------------|------|

| MCK0   | Clock                          | AD14                  | 0           | $GV_DD$          | _    |

| MCK1   | Clock                          | AE13                  | 0           | GV <sub>DD</sub> | _    |

| MCK2   | Clock                          | AG13                  | 0           | $GV_DD$          | _    |

| мск3   | Clock                          | AG14                  | 0           | $GV_DD$          | _    |

| MCK0   | Clock Complements              | AE14                  | 0           | GV <sub>DD</sub> | _    |

| MCK1   | Clock Complements              | AD13                  | 0           | $GV_DD$          | _    |

| MCK2   | Clock Complements              | AH13                  | 0           | $GV_DD$          | _    |

| MCK3   | Clock Complements              | AH14                  | 0           | GV <sub>DD</sub> | _    |

| MODT0  | On Die Termination             | AC19                  | 0           | $GV_DD$          | _    |

| MODT1  | On Die Termination             | AD22                  | 0           | $GV_DD$          | _    |

| MODT2  | On Die Termination             | AG18                  | 0           | $GV_DD$          | _    |

| MODT3  | On Die Termination             | AH21                  | 0           | $GV_DD$          | _    |

| MDIC0  | Driver Impedance Calibration   | AG12                  | I/O         | $GV_DD$          | 16   |

| MDIC1  | Driver Impedance Calibration   | AE12                  | I/O         | $GV_DD$          | 16   |

|        | Local Bus Controller Interface |                       |             |                  | -1   |

| LAD00  | Muxed Data/Address             | J6                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD01  | Muxed Data/Address             | J4                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD02  | Muxed Data/Address             | K2                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD03  | Muxed Data/Address             | K4                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD04  | Muxed Data/Address             | L1                    | I/O         | $BV_DD$          | 3    |

| LAD05  | Muxed Data/Address             | J5                    | I/O         | $BV_DD$          | 3    |

| LAD06  | Muxed Data/Address             | N5                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD07  | Muxed Data/Address             | N2                    | I/O         | $BV_DD$          | 3    |

| LAD08  | Muxed Data/Address             | N3                    | I/O         | $BV_DD$          | 3    |

| LAD09  | Muxed Data/Address             | N1                    | I/O         | $BV_DD$          | 3    |

| LAD10  | Muxed Data/Address             | P4                    | I/O         | $BV_DD$          | 3    |

| LAD11  | Muxed Data/Address             | R7                    | I/O         | $BV_DD$          | 3    |

| LAD12  | Muxed Data/Address             | T4                    | I/O         | $BV_DD$          | 3    |

| LAD13  | Muxed Data/Address             | U2                    | I/O         | $BV_DD$          | 3    |

| LAD14  | Muxed Data/Address             | T6                    | I/O         | BV <sub>DD</sub> | 3    |

| LAD15  | Muxed Data/Address             | T7                    | I/O         | BV <sub>DD</sub> | 3    |

| LA16   | Address                        | K6                    | I/O         | $BV_DD$          | 31   |

| LA17   | Address                        | К3                    | I/O         | BV <sub>DD</sub> | 31   |

| LA18   | Address                        | P6                    | I/O         | $BV_DD$          | 31   |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal                   | Signal Description                                 | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note       |

|--------------------------|----------------------------------------------------|-----------------------|-------------|------------------|------------|

| LA19                     | Address                                            | P3                    | I/O         | BV <sub>DD</sub> | 31         |

| LA20                     | Address                                            | P2                    | I/O         | BV <sub>DD</sub> | 31         |

| LA21                     | Address                                            | R3                    | I/O         | BV <sub>DD</sub> | 31         |

| LA22                     | Address                                            | T1                    | I/O         | BV <sub>DD</sub> | 31         |

| LA23                     | Address                                            | U1                    | I/O         | BV <sub>DD</sub> | 3          |

| LA24                     | Address                                            | R6                    | I/O         | BV <sub>DD</sub> | 3          |

| LA25                     | Address                                            | T5                    | I/O         | BV <sub>DD</sub> | 31         |

| LA26                     | Address                                            | T3                    | I/O         | BV <sub>DD</sub> | 3, 29      |

| LA27                     | Address                                            | T2                    | 0           | BV <sub>DD</sub> | T —        |

| LA28                     | Address                                            | U5                    | I/O         | BV <sub>DD</sub> | <u> </u>   |

| LA29                     | Address                                            | U3                    | I/O         | BV <sub>DD</sub> | <b>—</b>   |

| LA30                     | Address                                            | V1                    | I/O         | BV <sub>DD</sub> | T —        |

| LA31                     | Address                                            | V3                    | I/O         | BV <sub>DD</sub> | T —        |

| LDP0                     | Data Parity                                        | L3                    | I/O         | BV <sub>DD</sub> | <u> </u>   |

| LDP1                     | Data Parity                                        | M1                    | I/O         | BV <sub>DD</sub> | <b>T</b> — |

| LCS0                     | Chip Selects                                       | R5                    | 0           | BV <sub>DD</sub> | 5          |

| LCS1                     | Chip Selects                                       | P7                    | 0           | BV <sub>DD</sub> | 5          |

| LCS2                     | Chip Selects                                       | U4                    | 0           | BV <sub>DD</sub> | 5          |

| LCS3                     | Chip Selects                                       | R1                    | 0           | BV <sub>DD</sub> | 5          |

| <u>LWE0</u>              | Write Enable                                       | M6                    | 0           | BV <sub>DD</sub> | T —        |

| TWE1                     | Write Enable                                       | M3                    | 0           | BV <sub>DD</sub> | <b>†</b> – |

| LBCTL                    | Buffer Control                                     | P1                    | 0           | BV <sub>DD</sub> | T —        |

| LALE                     | Address Latch Enable                               | N6                    | I/O         | BV <sub>DD</sub> | T —        |

| LGPL0/LFCLE              | UPM General Purpose Line 0/<br>LFCLE—FCM           | L5                    | 0           | $BV_DD$          | 3, 4       |

| LGPL1/LFALE              | UPM General Purpose Line 1/<br>LFALE—FCM           | K1                    | 0           | $BV_DD$          | 3, 4       |

| LGPL2/LOE/LFRE           | UPM General Purpose Line 2/<br>LOE_B—Output Enable | L6                    | 0           | BV <sub>DD</sub> | 3, 4       |

| LGPL3/LFWP               | UPM General Purpose Line 3/<br>LFWP_B—FCM          | J3                    | 0           | BV <sub>DD</sub> | 3, 4       |

| LGPL4/LGTA/LUPWAIT/LPBSE | UPM General Purpose Line 4/<br>LGTA_B—FCM          | L2                    | I/O         | BV <sub>DD</sub> | 36         |

| LGPL5                    | UPM General Purpose Line 5 / Amux                  | J1                    | 0           | BV <sub>DD</sub> | 3, 4       |

| LCLK0                    | Local Bus Clock                                    | M4                    | 0           | BV <sub>DD</sub> | <u> </u>   |

| LCLK1                    | Local Bus Clock                                    | N7                    | 0           | BV <sub>DD</sub> | <b>†</b> – |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal                                                     | Signal Description                | Package<br>Pin Number | Pin<br>Type | Power<br>Supply         | Note  |

|------------------------------------------------------------|-----------------------------------|-----------------------|-------------|-------------------------|-------|

|                                                            | DMA                               |                       |             | I                       |       |

| DMA1_DREQ0/IIC4_SCL/EVT5/M1SRCID<br>1/LB_SRCID1/GPIO18     | DMA1 Channel 0 Request            | AC23                  | I           | $OV_DD$                 | 24    |

| DMA1_DACK0/IIC3_SCL/GPIO16/SDHC_<br>CD/<br>M1DVAL/LB_DVAL  | DMA1 Channel 0 Acknowledge        | AB23                  | 0           | OV <sub>DD</sub>        | 2, 14 |

| DMA1_DDONE0/IIC3_SDA/GPIO17/M1SR<br>CID0/LB_SRCID0/SDHC_WP | DMA1 Channel 0 Done               | AB26                  | 0           | $OV_DD$                 | 2, 14 |

| DMA2_DREQ0/IRQ03/GPIO21                                    | DMA2 Channel 0 Request            | AA26                  | I           | OV <sub>DD</sub>        | 24    |

| DMA2_DACK0/IRQ04/GPIO22                                    | DMA2 Channel 0 Acknowledge        | V25                   | 0           | OV <sub>DD</sub>        | 24    |

| DMA2_DDONE0/IRQ05/GPIO23                                   | DMA2 Channel 0 Done               | AA22                  | 0           | OV <sub>DD</sub>        | 24    |

|                                                            | USB Host Port 1                   |                       |             |                         |       |

| USB1_UDP                                                   | USB1 PHY Data Plus                | K28                   | I/O         | USB_V <sub>DD</sub> _3P | _     |

| USB1_UDM                                                   | USB1 PHY Data Minus               | L28                   | I/O         | USB_V <sub>DD</sub> _3P | _     |

| USB1_VBUS_CLMP                                             | USB1 PHY VBUS Divided Signals     | M25                   | I           | USB_V <sub>DD</sub> _3P | 34    |

| USB1_UID                                                   | USB1 PHY ID Detect                | M27                   | I           | USB_V <sub>DD</sub> _3P | _     |

| USB_CLKIN                                                  | USB PHY Clock Input               | P22                   | I           | OV <sub>DD</sub>        | _     |

| USB1_DRVVBUS/GPIO24/IRQ6                                   | USB1 5V Supply Enable             | Y26                   | 0           | OV <sub>DD</sub>        | _     |

| USB1_PWRFAULT/GPIO25/IRQ7                                  | USB Power Fault                   | AA23                  | I           | OV <sub>DD</sub>        | _     |

|                                                            | USB Host Port 2                   |                       |             | I                       |       |

| USB2_UDP                                                   | USB2 PHY Data Plus                | K26                   | I/O         | USB_V <sub>DD</sub> _3P | _     |

| USB2_UDM                                                   | USB2 PHY Data Minus               | L26                   | I/O         | USB_V <sub>DD</sub> _3P | _     |

| USB2_VBUS_CLMP                                             | USB2 PHY VBUS Divided Signals     | J25                   | I           | USB_V <sub>DD</sub> _3P | 34    |

| USB2_UID                                                   | USB2 PHY ID Detect                | J27                   | I           | USB_V <sub>DD</sub> _3P | _     |

| USB2_DRVVBUS/GPIO26/IRQ8                                   | USB2 5V Supply Enable             | AC22                  | I/O         | OV <sub>DD</sub>        | _     |

| USB2_PWRFAULT/GPIO27/IRQ9                                  | USB2 Power Fault                  | AC27                  | I/O         | OV <sub>DD</sub>        | _     |

|                                                            | Programmable Interrupt Controller |                       |             |                         |       |

| IRQ00                                                      | External Interrupts               | Y25                   | I           | $OV_{DD}$               | _     |

| IRQ01                                                      | External Interrupts               | AB27                  | I           | OV <sub>DD</sub>        | _     |

| IRQ02                                                      | External Interrupts               | AB25                  | I           | OV <sub>DD</sub>        | _     |

| IRQ03/GPIO21/DMA2_DREQ0                                    | External Interrupts               | AA26                  | I           | OV <sub>DD</sub>        | 24    |

| IRQ04/GPIO22/DMA2_DACK0                                    | External Interrupts               | V25                   | I           | $OV_{DD}$               | 24    |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal                                                    | Signal Description      | Package<br>Pin Number | Pin<br>Type | Power<br>Supply    | Note        |

|-----------------------------------------------------------|-------------------------|-----------------------|-------------|--------------------|-------------|

| IRQ05/GPIO23/DMA2_DDONE0                                  | External Interrupts     | AA22                  | I           | $OV_{DD}$          | 24          |

| IRQ06/GPIO24/USB1_DRVVBUS                                 | External Interrupts     | Y26                   | I           | $OV_{DD}$          | 24          |

| IRQ07/GPIO25/USB1_PWRFAULT                                | External Interrupts     | AA23                  | I           | OV <sub>DD</sub>   | 24          |

| IRQ08/GPIO26/USB2_DRVVBUS                                 | External Interrupts     | AC22                  | I           | OV <sub>DD</sub>   | 24          |

| IRQ09/GPIO27/USB2_PWRFAULT                                | External Interrupts     | AC27                  | ı           | OV <sub>DD</sub>   | 24          |

| IRQ10/GPIO28/EVT7                                         | External Interrupts     | AB24                  | I           | OV <sub>DD</sub>   | 24          |

| IRQ11/GPIO29/EVT8                                         | External Interrupts     | AC24                  | I           | OV <sub>DD</sub>   | 24          |

| IRQ_OUT/EVT9                                              | Interrupt Output        | Y24                   | 0           | OV <sub>DD</sub>   | 1, 2,<br>24 |

|                                                           | Trust                   |                       |             |                    |             |

| TMP_DETECT                                                | Tamper Detect           | T24                   | I           | OV <sub>DD</sub>   | 25          |

| LP_TMP_DETECT                                             | Low Power Tamper Detect | L21                   | I           | V <sub>DD_LP</sub> | 25          |

|                                                           | eSDHC                   |                       |             |                    |             |

| SDHC_CMD                                                  | Command/Response        | N22                   | I/O         | CV <sub>DD</sub>   | _           |

| SDHC_DAT0                                                 | Data                    | N23                   | I/O         | CV <sub>DD</sub>   | _           |

| SDHC_DAT1                                                 | Data                    | N26                   | I/O         | CV <sub>DD</sub>   |             |

| SDHC_DAT2                                                 | Data                    | N27                   | I/O         | CV <sub>DD</sub>   | _           |

| SDHC_DAT3                                                 | Data                    | N28                   | I/O         | CV <sub>DD</sub>   | _           |

| SDHC_DAT4/SPI_CS0/GPIO00                                  | Data                    | H26                   | I/O         | CV <sub>DD</sub>   | 24, 28      |

| SDHC_DAT5/SPI_CS1/GPIO01                                  | Data                    | H23                   | I/O         | CV <sub>DD</sub>   | 24, 28      |

| SDHC_DAT6/SPI_CS2/GPIO02                                  | Data                    | H27                   | I/O         | CV <sub>DD</sub>   | 24, 28      |

| SDHC_DAT7/SPI_CS3/GPIO03                                  | Data                    | H24                   | I/O         | CV <sub>DD</sub>   | 24, 28      |

| SDHC_CLK                                                  | Host to Card Clock      | N24                   | 0           | OV <sub>DD</sub>   | _           |

| SDHC_CD/IIC3_SCL/GPIO16/<br>M1DVAL/LB_DVAL/DMA1_DACK0     | Card Detection          | AB23                  | I/O         | OV <sub>DD</sub>   | 24, 28      |

| SDHC_WP/IIC3_SDA/GPIO17/<br>M1SRCID0/LB_SRCID0/DMA1_DDONE | Card Write Protection   | AB26                  | I           | $OV_{DD}$          | 24, 28      |

|                                                           | eSPI                    |                       | 1           |                    |             |

| SPI_MOSI                                                  | Master Out Slave In     | H28                   | I/O         | CV <sub>DD</sub>   | _           |

| SPI_MISO                                                  | Master In Slave Out     | G23                   | I           | CV <sub>DD</sub>   | _           |

| SPI_CLK                                                   | eSPI Clock              | H22                   | 0           | CV <sub>DD</sub>   | _           |

| SPI_CS0/SDHC_DAT4/GPIO00                                  | eSPI Chip Select        | H26                   | 0           | CV <sub>DD</sub>   | 24          |

| SPI_CS1/SDHC_DAT5/GPIO01                                  | eSPI Chip Select        | H23                   | 0           | CV <sub>DD</sub>   | 24          |

| SPI_CS2/SDHC_DAT6/GPIO02                                  | eSPI Chip Select        | H27                   | 0           | CV <sub>DD</sub>   | 24          |

| SPI_CS3/SDHC_DAT7/GPIO03                                  | eSPI Chip Select        | H24                   | 0           | CV <sub>DD</sub>   | 24          |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal                                   | Signal Description                | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note |

|------------------------------------------|-----------------------------------|-----------------------|-------------|------------------|------|

|                                          | IEEE 1588                         |                       |             |                  |      |

| TSEC_1588_CLK_IN/EC1_RXD2                | Clock In                          | B27                   | I           | LV <sub>DD</sub> | _    |

| TSEC_1588_TRIG_IN1/EC1_RXD0              | Trigger In 1                      | B28                   | ı           | LV <sub>DD</sub> | _    |

| TSEC_1588_TRIG_IN2/EC1_RXD1              | Trigger In 2                      | A27                   | I           | $LV_DD$          | _    |

| TSEC_1588_ALARM_OUT1/EC1_TXD0            | Alarm Out 1                       | B24                   | 0           | $LV_DD$          | _    |

| TSEC_1588_ALARM_OUT2/<br>EC1_TXD1/GPIO30 | Alarm Out 2                       | C25                   | 0           | LV <sub>DD</sub> | 23   |

| TSEC_1588_CLK_OUT/EC1_RXD3               | Clock Out                         | B26                   | 0           | $LV_DD$          | _    |

| TSEC_1588_PULSE_OUT1/EC1_TXD2            | Pulse Out1                        | C28                   | 0           | $LV_DD$          | _    |

| TSEC_1588_PULSE_OUT2/EC1_TXD3/G<br>PIO31 | Pulse Out2                        | A26                   | 0           | LV <sub>DD</sub> | 23   |

|                                          | Ethernet Management Interface 1   |                       |             |                  |      |

| EMI1_MDC                                 | Management Data Clock             | F23                   | 0           | LV <sub>DD</sub> | _    |

| EMI1_MDIO                                | Management Data In/Out            | G24                   | I/O         | LV <sub>DD</sub> | _    |

|                                          | Ethernet Reference Clock          | 1                     | 1           |                  | -    |

| EC1_GTX_CLK125/EC_XTRNL_TX_STMP 2        | Reference Clock (RGMII)           | A24                   | I           | LV <sub>DD</sub> | 25   |

| EC2_GTX_CLK125                           | Reference Clock (RGMII)           | D24                   | I           | LV <sub>DD</sub> | 25   |

|                                          | Ethernet External Timestamping    | l                     |             |                  |      |

| EC_XTRNL_TX_STMP1/EC1_TX_EN              | External Timestamp Transmit 1     | C27                   | I           | LV <sub>DD</sub> | T —  |

| EC_XTRNL_RX_STMP1/EC1_RX_DV              | External Timestamp Receive 1      | A25                   | ı           | LV <sub>DD</sub> | _    |

| EC_XTRNL_TX_STMP2/EC1_GTX_CLK12<br>5     | External Timestamp Transmit 2     | A24                   | I           | LV <sub>DD</sub> | _    |

| EC_XTRNL_RX_STMP2/EC1_RX_CLK             | External Timestamp Receive 2      | C24                   | ı           | LV <sub>DD</sub> | _    |

|                                          | Three-Speed Ethernet Controller 1 | l                     |             |                  |      |

| EC1_TXD3/TSEC_1588_PULSE_OUT2/G<br>PIO31 | Transmit Data                     | A26                   | 0           | LV <sub>DD</sub> | _    |

| EC1_TXD2/TSEC_1588_PULSE_OUT1            | Transmit Data                     | C28                   | 0           | LV <sub>DD</sub> | _    |

| EC1_TXD1/TSEC_1588_ALARM_OUT2/G<br>PIO30 | Transmit Data                     | C25                   | 0           | LV <sub>DD</sub> | _    |

| EC1_TXD0/TSEC_1588_ALARM_OUT1            | Transmit Data                     | B24                   | 0           | LV <sub>DD</sub> | _    |

| EC1_TX_EN/EC_XTRNL_TX_STMP1              | Transmit Enable                   | C27                   | 0           | LV <sub>DD</sub> | 15   |

| EC1_GTX_CLK                              | Transmit Clock Out (RGMII)        | D26                   | 0           | LV <sub>DD</sub> | 24   |

| EC1_RXD3/TSEC_1588_CLK_OUT               | Receive Data                      | B26                   | I           | LV <sub>DD</sub> | 25   |

| EC1_RXD2/TSEC_1588_CLK_IN                | Receive Data                      | B27                   | I           | $LV_DD$          | 25   |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal                                                | Signal Description                | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note       |

|-------------------------------------------------------|-----------------------------------|-----------------------|-------------|------------------|------------|

| EC1_RXD1/TSEC_1588_TRIG_IN2                           | Receive Data                      | A27                   | I           | $LV_DD$          | 25         |

| EC1_RXD0/TSEC_1588_TRIG_IN1                           | Receive Data                      | B28                   | I           | $LV_DD$          | 25         |

| EC1_RX_DV/EC_XTRNL_RX_STMP1                           | Receive Data Valid                | A25                   | I           | LV <sub>DD</sub> | 25         |

| EC1_RX_CLK/EC_XTRNL_RX_STMP2                          | Receive Clock                     | C24                   | I           | $LV_DD$          | 25         |

|                                                       | Three-Speed Ethernet Controller 2 | +                     |             |                  | -          |

| EC2_TXD3                                              | Transmit Data                     | G28                   | 0           | LV <sub>DD</sub> |            |

| EC2_TXD2                                              | Transmit Data                     | G26                   | 0           | LV <sub>DD</sub> |            |

| EC2_TXD1                                              | Transmit Data                     | G27                   | 0           | LV <sub>DD</sub> | <b>T</b> — |

| EC2_TXD0                                              | Transmit Data                     | G25                   | 0           | LV <sub>DD</sub> | T —        |

| EC2_TX_EN                                             | Transmit Enable                   | F28                   | 0           | LV <sub>DD</sub> | 15         |

| EC2_GTX_CLK                                           | Transmit Clock Out (RGMII)        | E28                   | 0           | $LV_DD$          | 24         |

| EC2_RXD3                                              | Receive Data                      | D28                   | I           | LV <sub>DD</sub> | 25         |

| EC2_RXD2                                              | Receive Data                      | E27                   | I           | LV <sub>DD</sub> | 25         |

| EC2_RXD1                                              | Receive Data                      | E25                   | I           | LV <sub>DD</sub> | 24, 25     |

| EC2_RXD0                                              | Receive Data                      | F26                   | I           | $LV_DD$          | 24, 25     |

| EC2_RX_DV                                             | Receive Data Valid                | D25                   | I           | $LV_DD$          | 25         |

| EC2_RX_CLK                                            | Receive Clock                     | F25                   | I           | $LV_DD$          | 25         |

|                                                       | UART                              |                       |             |                  | -          |

| UART1_SOUT/GPIO8                                      | Transmit Data                     | R23                   | 0           | OV <sub>DD</sub> | 24         |

| UART2_SOUT/GPIO9                                      | Transmit Data                     | P26                   | 0           | $OV_DD$          | 24         |

| UART1_SIN/GPIO10                                      | Receive Data                      | R26                   | I           | $OV_DD$          | 24         |

| UART2_SIN/GPIO11                                      | Receive Data                      | P27                   | I           | $OV_DD$          | 24         |

| UART1_RTS/UART3_SOUT/GPIO12                           | Ready to Send                     | P24                   | 0           | $OV_DD$          | 24         |

| UART2_RTS/UART4_SOUT/GPIO13                           | Ready to Send                     | P25                   | 0           | $OV_DD$          | 24         |

| UART1_CTS/UART3_SIN/GPIO14                            | Clear to Send                     | R25                   | I           | $OV_{DD}$        | 24         |

| UART2_CTS/UART4_SIN/GPIO15                            | Clear to Send                     | P23                   | I           | $OV_DD$          | 24         |

|                                                       | I <sup>2</sup> C Interface        |                       |             |                  |            |

| IIC1_SCL                                              | Serial Clock                      | AC25                  | I/O         | OV <sub>DD</sub> | 2, 14      |

| IIC1_SDA                                              | Serial Data                       | AC28                  | I/O         | OV <sub>DD</sub> | 2, 14      |

| IIC2_SCL                                              | Serial Clock                      | W25                   | I/O         | OV <sub>DD</sub> | 2, 14      |

| IIC2_SDA                                              | Serial Data                       | AA25                  | I/O         | OV <sub>DD</sub> | 2, 14      |

| IIC3_SCL/GPIO16/M1DVAL/LB_DVAL/<br>DMA1_DACK0/SDHC_CD | Serial Clock                      | AB23                  | I/O         | $OV_{DD}$        | 2, 14      |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal                                                 | Signal Description                        | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note  |

|--------------------------------------------------------|-------------------------------------------|-----------------------|-------------|------------------|-------|

| IIC3_SDA/GPIO17/M1SRCID0/LB_SRCID0                     | Serial Data                               | AB26                  | I/O         | $OV_{DD}$        | 2, 14 |

| DMA1_DDONE0/SDHC_WP                                    |                                           |                       |             |                  |       |

| IIC4_SCL/EVT5/M1SRCID1/LB_SRCID1/<br>GPIO18/DMA1_DREQ0 | Serial Clock                              | AC23                  | I/O         | OV <sub>DD</sub> | 2, 14 |

| IIC4_SDA/EVT6/M1SRCID2/<br>LB_SRCID2/GPIO19            | Serial Data                               | V24                   | I/O         | OV <sub>DD</sub> | 2, 14 |

| SerDes (x10                                            | ) PCI Express, Serial RapidIO, Aurora, 10 | OGE, 1GE              | 1           |                  | 1     |

| SD_TX13                                                | Transmit Data (positive)                  | C20                   | 0           | $XV_{DD}$        | _     |

| SD_TX12                                                | Transmit Data (positive)                  | C18                   | 0           | $XV_{DD}$        | _     |

| SD_TX11                                                | Transmit Data (positive)                  | D16                   | 0           | $XV_{DD}$        | _     |

| SD_TX10                                                | Transmit Data (positive)                  | C14                   | 0           | $XV_{DD}$        | _     |

| SD_TX07                                                | Transmit Data (positive)                  | C12                   | 0           | $XV_{DD}$        | _     |

| SD_TX06                                                | Transmit Data (positive)                  | C10                   | 0           | $XV_{DD}$        | _     |

| SD_TX05                                                | Transmit Data (positive)                  | C8                    | 0           | $XV_{DD}$        | _     |

| SD_TX04                                                | Transmit Data (positive)                  | B4                    | 0           | $XV_{DD}$        | _     |

| SD_TX03                                                | Transmit Data (positive)                  | F3                    | 0           | $XV_{DD}$        | _     |

| SD_TX02                                                | Transmit Data (positive)                  | G5                    | 0           | $XV_{DD}$        | _     |

| SD_TX13                                                | Transmit Data (negative)                  | D20                   | 0           | $XV_{DD}$        | _     |

| SD_TX12                                                | Transmit Data (negative)                  | D18                   | 0           | $XV_{DD}$        | _     |

| SD_TX11                                                | Transmit Data (negative)                  | C16                   | 0           | $XV_{DD}$        | _     |

| SD_TX10                                                | Transmit Data (negative)                  | D14                   | 0           | $XV_{DD}$        | _     |

| SD_TX07                                                | Transmit Data (negative)                  | D12                   | 0           | $XV_{DD}$        | _     |

| SD_TX06                                                | Transmit Data (negative)                  | D10                   | 0           | $XV_{DD}$        | _     |

| SD_TX05                                                | Transmit Data (negative)                  | D8                    | 0           | $XV_{DD}$        | _     |

| SD_TX04                                                | Transmit Data (negative)                  | B5                    | 0           | $XV_{DD}$        | _     |

| SD_TX03                                                | Transmit Data (negative)                  | F4                    | 0           | $XV_{DD}$        | _     |

| SD_TX02                                                | Transmit Data (negative)                  | G6                    | 0           | $XV_{DD}$        | _     |

| SD_RX13                                                | Receive Data (positive)                   | B21                   | ı           | $XV_{DD}$        | _     |

| SD_RX12                                                | Receive Data (positive)                   | B19                   | I           | $XV_{DD}$        | _     |

| SD_RX11                                                | Receive Data (positive)                   | B15                   | I           | $XV_{DD}$        | -     |

| SD_RX10                                                | Receive Data (positive)                   | A13                   | I           | $XV_{DD}$        | _     |

| SD_RX07                                                | Receive Data (positive)                   | B11                   | I           | $XV_{DD}$        | _     |

| SD_RX06                                                | Receive Data (positive)                   | В9                    | I           | $XV_{DD}$        | _     |

| SD_RX05                                                | Receive Data (positive)                   | B7                    | I           | $XV_{DD}$        | _     |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal                                                | Signal Description                              | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note     |

|-------------------------------------------------------|-------------------------------------------------|-----------------------|-------------|------------------|----------|

| SD_RX04                                               | Receive Data (positive)                         | A2                    | I           | $XV_{DD}$        | _        |

| SD_RX03                                               | Receive Data (positive)                         | E1                    | I           | $XV_{DD}$        | _        |

| SD_RX02                                               | Receive Data (positive)                         | G1                    | I           | $XV_{DD}$        | _        |

| SD_RX13                                               | Receive Data (negative)                         | A21                   | I           | $XV_{DD}$        | _        |

| SD_RX12                                               | Receive Data (negative)                         | A19                   | I           | $XV_{DD}$        | _        |

| SD_RX11                                               | Receive Data (negative)                         | A15                   | I           | $XV_{DD}$        | _        |

| SD_RX10                                               | Receive Data (negative)                         | B13                   | I           | $XV_{DD}$        | _        |

| SD_RX07                                               | Receive Data (negative)                         | A11                   | I           | $XV_{DD}$        | _        |

| SD_RX06                                               | Receive Data (negative)                         | A9                    | I           | $XV_{DD}$        | _        |

| SD_RX05                                               | Receive Data (negative)                         | A7                    | I           | $XV_{DD}$        | _        |

| SD_RX04                                               | Receive Data (negative)                         | A3                    | I           | $XV_{DD}$        | _        |

| SD_RX03                                               | Receive Data (negative)                         | E2                    | I           | $XV_{DD}$        | _        |

| SD_RX02                                               | Receive Data (negative)                         | G2                    | I           | $XV_{DD}$        | _        |

| SD_REF_CLK1                                           | SerDes Bank 1 PLL Reference Clock               | D3                    | I           | $XV_{DD}$        | _        |

| SD_REF_CLK1                                           | SerDes Bank 1 PLL Reference Clock<br>Complement | D4                    | I           | $XV_{DD}$        | _        |

| SD_REF_CLK2                                           | SerDes Bank 2 PLL Reference Clock               | E17                   | I           | $XV_{DD}$        | _        |

| SD_REF_CLK2                                           | SerDes Bank 2 PLL Reference Clock<br>Complement | F17                   | I           | $XV_{DD}$        | _        |

|                                                       | General-Purpose Input/Output                    |                       |             |                  | *        |

| GPIO00/SPI_CS0/SDHC_DATA4                             | General Purpose Input/Output                    | H26                   | I/O         | CV <sub>DD</sub> | _        |

| GPIO01/SPI_CS1/SDHC_DATA5                             | General Purpose Input/Output                    | H23                   | I/O         | CV <sub>DD</sub> | _        |

| GPIO02/SPI_CS2/SDHC_DATA6                             | General Purpose Input/Output                    | H27                   | I/O         | CV <sub>DD</sub> | _        |

| GPIO03SPI_CS3/SDHC_DATA7                              | General Purpose Input/Output                    | H24                   | I/O         | CV <sub>DD</sub> | _        |

| GPIO08/UART1_SOUT                                     | General Purpose Input/Output                    | R23                   | I/O         | OV <sub>DD</sub> | _        |

| GPIO09/UART2_SOUT                                     | General Purpose Input/Output                    | P26                   | I/O         | OV <sub>DD</sub> | _        |

| GPIO10/UART1_SIN                                      | General Purpose Input/Output                    | R26                   | I/O         | $OV_{DD}$        | _        |

| GPIO11/UART2_SIN                                      | General Purpose Input/Output                    | P27                   | I/O         | OV <sub>DD</sub> | _        |

| GPIO12/UART1_RTS/UART3_SOUT                           | General Purpose Input/Output                    | P24                   | I/O         | OV <sub>DD</sub> | _        |

| GPIO13/UART2_RTS/UART4_SOUT                           | General Purpose Input/Output                    | P25                   | I/O         | OV <sub>DD</sub> | <u> </u> |

| GPIO14/UART1_CTS/UART3_SIN                            | General Purpose Input/Output                    | R25                   | I/O         | OV <sub>DD</sub> | <u> </u> |

| GPIO15/UART2_CTS/UART4_SIN                            | General Purpose Input/Output                    | P23                   | I/O         | OV <sub>DD</sub> | <u> </u> |

| GPIO16/IIC3_SCL/M1DVAL/LB_DVAL/<br>DMA1_DACK0/SDHC_CD | General Purpose Input/Output                    | AB23                  | I/O         | $OV_{DD}$        | _        |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal                                                 | Signal Description           | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note |

|--------------------------------------------------------|------------------------------|-----------------------|-------------|------------------|------|

| GPIO17/IIC3_SDA/M1SRCID0/LB_SRCID0                     | General Purpose Input/Output | AB26                  | I/O         | $OV_{DD}$        | _    |

| DMA1_DDONE0/SDHC_WP                                    |                              |                       |             |                  |      |

| GPIO18/IIC4_SCL/EVT5/M1SRCID1/<br>LB_SRCID1/DMA1_DREQ0 | General Purpose Input/Output | AC23                  | I/O         | $OV_{DD}$        | _    |

| GPIO19/IIC4_SDA/EVT6/M1SRCID2/<br>LB_SRCID2            | General Purpose Input/Output | V24                   | I/O         | $OV_{DD}$        | _    |

| GPIO21/IRQ3/DMA2_DREQ0                                 | General Purpose Input/Output | AA26                  | I/O         | $OV_DD$          | _    |

| GPIO22/IRQ4/DMA2_DACK0                                 | General Purpose Input/Output | V25                   | I/O         | OV <sub>DD</sub> | _    |

| GPIO23/IRQ5/DMA2_DDONE0                                | General Purpose Input/Output | AA22                  | I/O         | $OV_DD$          | _    |

| GPIO24/IRQ6/USB1_DRVVBUS                               | General Purpose Input/Output | Y26                   | I/O         | $OV_DD$          | _    |

| GPIO25/IRQ7/USB1_PWRFAULT                              | General Purpose Input/Output | AA23                  | I/O         | $OV_DD$          | _    |

| GPIO26/IRQ8/USB2_DRVVBUS                               | General Purpose Input/Output | AC22                  | I/O         | $OV_DD$          | _    |

| GPIO27/IRQ9/USB2_PWRFAULT                              | General Purpose Input/Output | AC27                  | I/O         | $OV_DD$          | _    |

| GPIO28/IRQ10/EVT7                                      | General Purpose Input/Output | AB24                  | I/O         | $OV_DD$          | _    |

| GPIO29/IRQ11/EVT8                                      | General Purpose Input/Output | AC24                  | I/O         | $OV_DD$          | _    |

| GPIO30/EC1_TXD1/TSEC_1588_ALARM_<br>OUT2               | General Purpose Input/Output | C25                   | I/O         | $LV_DD$          | 23   |

| GPIO31/EC1_TXD3/TSEC_1588_PULSE_<br>OUT2               | General Purpose Input/Output | A26                   | I/O         | LV <sub>DD</sub> | 23   |

|                                                        | System Control               |                       | 1           |                  | 1    |

| PORESET                                                | Power On Reset               | T22                   | I           | OV <sub>DD</sub> | _    |

| HRESET                                                 | Hard Reset                   | T23                   | I/O         | OV <sub>DD</sub> | 1, 2 |

| RESET_REQ                                              | Reset Request                | U28                   | 0           | $OV_DD$          | 31   |

| CKSTP_OUT                                              | Checkstop Out                | T25                   | 0           | OV <sub>DD</sub> | 1, 2 |

|                                                        | Debug                        |                       |             |                  | П    |

| EVT0                                                   | Event 0                      | V26                   | I/O         | OV <sub>DD</sub> | 18   |

| EVT1                                                   | Event 1                      | U27                   | I/O         | OV <sub>DD</sub> | _    |

| EVT2                                                   | Event 2                      | U26                   | I/O         | OV <sub>DD</sub> | _    |

| EVT3                                                   | Event 3                      | W24                   | I/O         | OV <sub>DD</sub> | _    |

| EVT4                                                   | Event 4                      | U24                   | I/O         | OV <sub>DD</sub> | _    |

| EVT5/IIC4_SCL/M1SRCID1/LB_SRCID1/<br>GPIO18/DMA1_DREQ0 | Event 5                      | AC23                  | I/O         | $OV_{DD}$        | _    |

| EVT6/IIC4_SDA/M1SRCID2/<br>LB_SRCID2/GPIO19            | Event 6                      | V24                   | I/O         | $OV_{DD}$        | _    |

| EVT7GPIO28/IRQ10                                       | Event 7                      | AB24                  | I/O         | OV <sub>DD</sub> | _    |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal                                                           | Signal Description           | Package<br>Pin Number | Pin<br>Type | Power<br>Supply  | Note     |

|------------------------------------------------------------------|------------------------------|-----------------------|-------------|------------------|----------|

| EVT8/GPIO29/IRQ11                                                | Event 8                      | AC24                  | I/O         | $OV_DD$          | _        |

| EVT9/IRQ_OUT                                                     | Event 9                      | Y24                   | I/O         | $OV_DD$          | _        |

| M1DVAL/LB_DVAL/IIC3_SCL/GPIO16/<br>SDHC_CD/DMA1_DACK0            | Debug Data Valid             | AB23                  | 0           | $OV_{DD}$        | _        |

| MSRCID0/LB_SRCID0/IIC3_SDA/GPIO17/<br>DMA_DDONE0/SDHC_WP         | Debug Source ID 0            | AB26                  | 0           | $OV_{DD}$        | 4, 31    |

| MSRCID1/LB_MSRCID1/EVT5/IIC4_SCL/<br>LB_SRCID1/GPIO18/DMA1_DREQ0 | Debug Source ID 1            | AC23                  | 0           | $OV_{DD}$        | _        |

| MSRCID2/LB_SRCID2/EVT6/IIC4_SDA/<br>LB_SRCID2/GPIO19             | Debug Source ID 2            | V24                   | 0           | $OV_{DD}$        | _        |

| CLK_OUT                                                          | Clock Out                    | T27                   | 0           | $OV_{DD}$        | 6        |

|                                                                  | Clock                        | 1                     | I           |                  |          |

| RTC                                                              | Real Time Clock              | P28                   | I           | OV <sub>DD</sub> | _        |

| SYSCLK                                                           | System Clock                 | R28                   | ı           | OV <sub>DD</sub> | _        |

|                                                                  | JTAG                         |                       | <u> </u>    |                  | _        |

| ТСК                                                              | Test Clock                   | Y28                   | I           | OV <sub>DD</sub> | _        |

| TDI                                                              | Test Data In                 | W28                   | I           | OV <sub>DD</sub> | 7        |

| TDO                                                              | Test Data Out                | AA28                  | 0           | OV <sub>DD</sub> | 6        |

| TMS                                                              | Test Mode Select             | W27                   | I           | $OV_DD$          | 7        |

| TRST                                                             | Test Reset                   | Y27                   | I           | $OV_DD$          | 7        |

|                                                                  | DFT                          |                       |             |                  |          |

| SCAN_MODE                                                        | Scan Mode                    | V28                   | I           | OV <sub>DD</sub> | 35       |

| TEST_SEL                                                         | Test Mode Select             | T28                   | I           | $OV_DD$          | 12, 26   |

|                                                                  | Power Management             | 1                     | 1           |                  |          |

| ASLEEP                                                           | Asleep                       | R22                   | 0           | OV <sub>DD</sub> | 31       |

|                                                                  | Input /Output Voltage Select | 1                     |             |                  |          |

| IO_VSEL0                                                         | I/O Voltage Select           | AB28                  | I           | OV <sub>DD</sub> | 27       |

| IO_VSEL1                                                         | I/O Voltage Select           | U23                   | 1           | OV <sub>DD</sub> | 27       |

| IO_VSEL2                                                         | I/O Voltage Select           | AB21                  | I           | OV <sub>DD</sub> | 27       |

| IO_VSEL3                                                         | I/O Voltage Select           | Y23                   | I           | OV <sub>DD</sub> | 27       |

| IO_VSEL4                                                         | I/O Voltage Select           | Y21                   | I           | OV <sub>DD</sub> | 27       |

|                                                                  | Power and Ground Signals     | •                     | ,           |                  |          |

| GND168                                                           | Ground                       | A23                   | _           | _                | _        |

| GND167                                                           | Ground                       | B23                   | _           | _                | <b> </b> |

P2040 QorlQ Integrated Processor Hardware Specifications, Rev. 2

Table 1. Pin List by Bus (continued)

| Signal | Signal Description | Package<br>Pin Number | Pin<br>Type | Power<br>Supply | Note |

|--------|--------------------|-----------------------|-------------|-----------------|------|

| GND166 | Ground             | B25                   | _           | _               | _    |

| GND165 | Ground             | C23                   | _           | _               | _    |

| GND164 | Ground             | D23                   | _           | _               | _    |

| GND163 | Ground             | D27                   | _           | _               | _    |

| GND162 | Ground             | E24                   | _           | _               | _    |

| GND161 | Ground             | F22                   | _           | _               | _    |

| GND160 | Ground             | F27                   | _           | _               | _    |

| GND159 | Ground             | G10                   | _           | _               | _    |

| GND158 | Ground             | G12                   | _           | _               | _    |

| GND157 | Ground             | G14                   | _           | _               | _    |

| GND156 | Ground             | G16                   | _           | _               | _    |

| GND155 | Ground             | G18                   | _           | _               | _    |

| GND154 | Ground             | G21                   | _           | _               | _    |

| GND153 | Ground             | G22                   | _           | _               | _    |

| GND152 | Ground             | НЗ                    | _           | _               | _    |

| GND151 | Ground             | H4                    | _           | _               | _    |

| GND150 | Ground             | H10                   | _           | _               | _    |

| GND149 | Ground             | H12                   | _           | _               | _    |

| GND148 | Ground             | H14                   | _           | _               | _    |

| GND147 | Ground             | H16                   | _           | _               | _    |

| GND146 | Ground             | H18                   | _           | _               | _    |

| GND145 | Ground             | H21                   | _           | _               | _    |

| GND144 | Ground             | H25                   | _           | _               | _    |

| GND143 | Ground             | J2                    | _           | _               | _    |

| GND142 | Ground             | J8                    | _           | _               | _    |

| GND141 | Ground             | J10                   | _           | _               | _    |

| GND140 | Ground             | J12                   | _           | _               | _    |

| GND139 | Ground             | J14                   | _           | _               | _    |

| GND138 | Ground             | J16                   | _           | _               | _    |

| GND137 | Ground             | J18                   | _           | _               | _    |

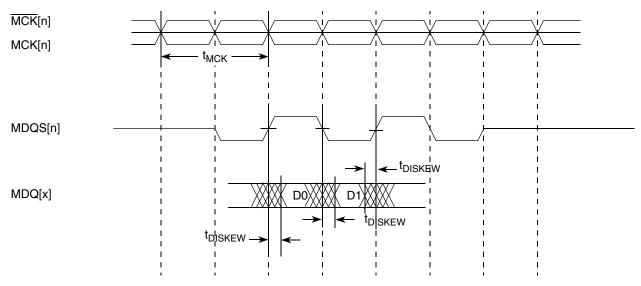

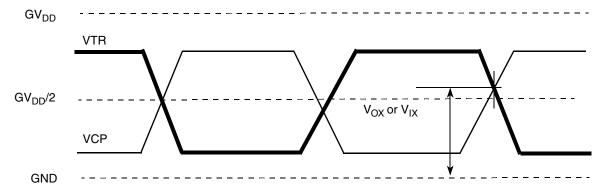

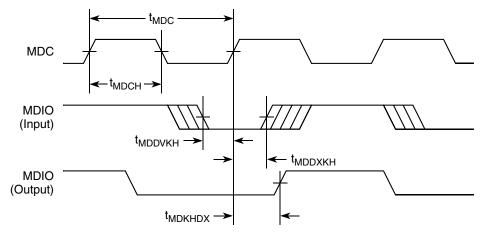

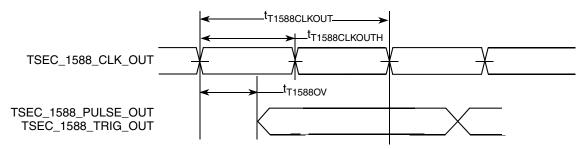

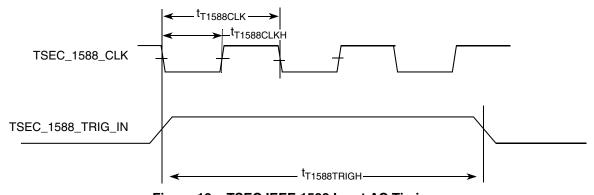

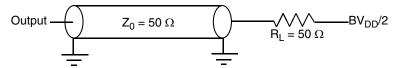

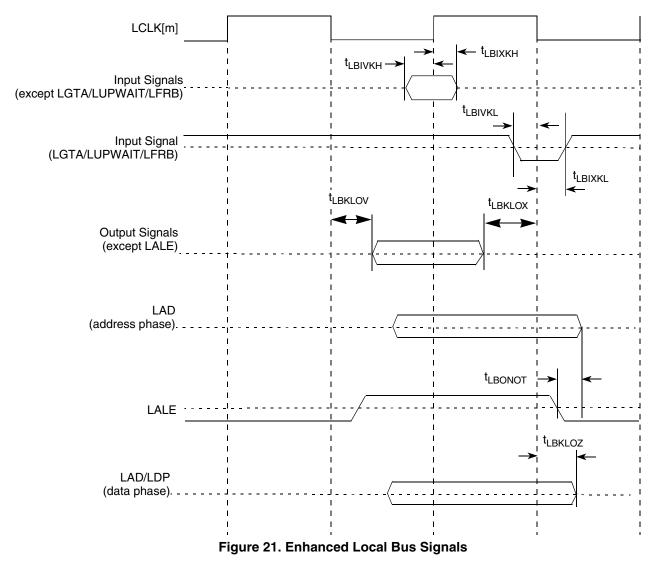

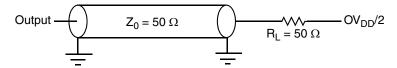

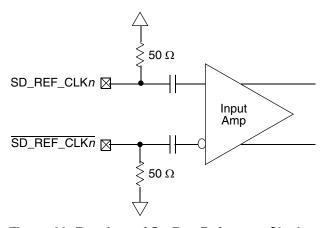

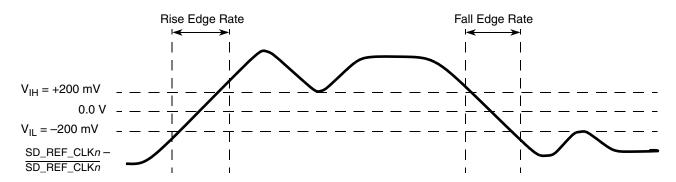

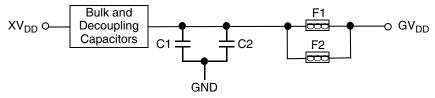

| GND136 | Ground             | J21                   | _           | _               | _    |