# **Quad IF Receiver**

Data Sheet AD6657A

#### **FEATURES**

11-bit, 200 MSPS output data rate per channel Integrated noise shaping requantizer Performance with NSR enabled

SNR: 76.0 dBFS in 40 MHz band to 70 MHz at 185 MSPS SNR: 73.6 dBFS in 60 MHz band to 70 MHz at 185 MSPS SNR: 72.8 dBFS in 65 MHz band to 70 MHz at 185 MSPS

Performance with NSR disabled

SNR: 66.5 dBFS to 70 MHz at 185 MSPS SFDR: 88 dBc to 70 MHz at 185 MSPS

Low power: 1.2 W at 185 MSPS

1.8 V analog supply operation

1.8 V LVDS (ANSI-644 levels) output

1-to-8 integer clock divider

Internal ADC voltage reference

1.75 V p-p analog input range (programmable to 2.0 V p-p)

Differential analog inputs with 800 MHz bandwidth

95 dB channel isolation/crosstalk

Serial port control

User-configurable built-in self test (BIST) capability

Energy saving power-down modes

# **APPLICATIONS**

Communications

Diversity radio and smart antenna (MIMO) systems

Multimode digital receivers (3G)

WCDMA, LTE, CDMA2000

WiMAX, TD-SCDMA

I/Q demodulation systems

General-purpose software radios

#### **GENERAL DESCRIPTION**

The AD6657A is an 11-bit, 200 MSPS, quad channel intermediate frequency (IF) receiver specifically designed to support multiple antenna systems in telecommunication applications where high dynamic range performance, low power, and small size are desired.

The device consists of four high performance ADCs and NSR digital blocks. Each ADC consists of a multistage, differential pipelined architecture with integrated output error correction logic. The ADC features a wide bandwidth switched capacitor sampling network within the first stage of the differential pipeline. An integrated voltage reference eases design considerations. A duty cycle stabilizer (DCS) compensates for variations in the ADC clock duty cycle, allowing the converters to maintain excellent performance.

Rev. A Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

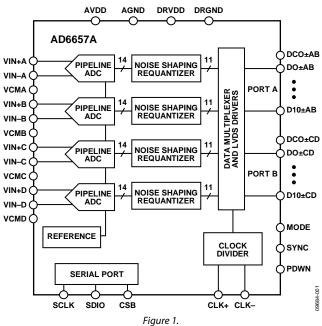

## **FUNCTIONAL BLOCK DIAGRAM**

Each ADC output is connected internally to an NSR block. The integrated NSR circuitry allows for improved SNR performance in a smaller frequency band within the Nyquist bandwidth. The device supports two different output modes selectable via the external MODE pin or the serial port interface (SPI).

With the NSR feature enabled, the outputs of the ADCs are processed such that the AD6657A supports enhanced SNR performance within a limited portion of the Nyquist bandwidth while maintaining an 11-bit output resolution. The NSR block can be programmed to provide a bandwidth of either 22%, 33%, or 36% of the sample clock. For example, with a sample clock rate of 185 MSPS, the AD6657A can achieve up to 76.0 dBFS SNR for a 40 MHz bandwidth in the 22% mode, up to 73.6 dBFS SNR for a 60 MHz bandwidth in the 33% mode, or up to 72.8 dBFS SNR for a 65 MHz bandwidth in the 36% mode.

(General Description continued on Page 3)

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2011–2014 Analog Devices, Inc. All rights reserved.

Technical Support www.analog.com

# **TABLE OF CONTENTS**

| Features                                      |

|-----------------------------------------------|

| Applications                                  |

| Functional Block Diagram                      |

| General Description                           |

| Revision History2                             |

| Product Highlights                            |

| Specifications4                               |

| DC Specifications                             |

| AC Specifications                             |

| Digital Specifications                        |

| Switching Specifications                      |

| Timing Specifications                         |

| Absolute Maximum Ratings1                     |

| Thermal Characteristics                       |

| ESD Caution                                   |

| Pin Configuration and Function Descriptions12 |

| Typical Performance Characteristics14         |

| Equivalent Circuits                           |

| Theory of Operation19                         |

| ADC Architecture                              |

| Analog Input Considerations19                 |

| Clock Input Considerations                    |

| Power Dissipation and Standby Mode23          |

|                                               |

| - •                                       |    |

|-------------------------------------------|----|

| Digital Outputs                           | 24 |

| Timing                                    | 24 |

| Noise Shaping Requantizer                 | 25 |

| 22% BW Mode (>40 MHz at 184.32 MSPS)      | 25 |

| 33% BW Mode (>60 MHz at 184.32 MSPS)      | 26 |

| 36% BW Mode (>65 MHz at 184.32 MSPS)      | 27 |

| MODE Pin                                  | 27 |

| Built-In Self Test (BIST) and Output Test | 28 |

| BIST                                      | 28 |

| Output Test Modes                         | 28 |

| Serial Port Interface (SPI)               | 29 |

| Configuration Using the SPI               | 29 |

| Hardware Interface                        | 29 |

| Memory Map                                | 30 |

| Reading the Memory Map Register Table     | 30 |

| Memory Map Register Table                 | 31 |

| Memory Map Register Descriptions          | 33 |

| Applications Information                  | 35 |

| Design Guidelines                         | 35 |

| Packaging and Ordering Information        | 36 |

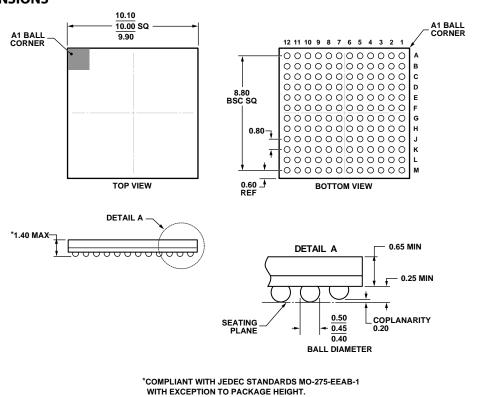

| Outline Dimensions                        | 36 |

| Ordering Guide                            | 36 |

# **REVISION HISTORY**

| 2/14—Rev. 0 to Rev. A                                      |   |

|------------------------------------------------------------|---|

| Changed DCO to Data Skew (tskew) Parameter Unit from ns to | , |

| ps, Table 4                                                | • |

10/11—Revision 0: Initial Version

With the NSR block disabled, the ADC data is provided directly to the output with a resolution of 11 bits. The AD6657A can achieve up to 66.5 dBFS SNR for the entire Nyquist bandwidth when operated in this mode. This allows the AD6657A to be used in telecommunication applications such as a digital predistortion observation path where wider bandwidths are used.

After digital signal processing, multiplexed output data is routed into two 11-bit output ports such that the maximum digital data rate (DDR) is 400 Mbps. These outputs are set at 1.8 V LVDS and support ANSI-644 levels.

The AD6657A receiver digitizes a wide spectrum of IF frequencies. Each receiver is designed for simultaneous reception of a separate antenna. This IF sampling architecture greatly reduces component cost and complexity compared with traditional analog techniques or less integrated digital methods.

Flexible power-down options allow significant power savings. Programming for device setup and control is accomplished using a 3-wire SPI-compatible serial interface with numerous modes to support board level system testing.

The AD6657A is available in a Pb-free, RoHS compliant, 144-ball,  $10~\text{mm} \times 10~\text{mm}$  chip scale package ball grid array

(CSP\_BGA) that is specified over the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

#### **PRODUCT HIGHLIGHTS**

- 1. Four analog-to-digital converters (ADCs) are contained in a small, space-saving,  $10 \text{ mm} \times 10 \text{ mm} \times 1.4 \text{ mm}$ , 144-ball CSP\_BGA package.

- 2. Pin selectable noise shaping requantizer (NSR) function that allows for improved SNR within a reduced bandwidth of up to 65 MHz at 185 MSPS.

- LVDS digital output interface configured for low cost FPGA families.

- 4. 230 mW per ADC core power consumption.

- 5. Operation from a single 1.8 V supply.

- Standard SPI that supports various product features and functions, such as data formatting (offset binary or twos complement), NSR, power-down, test modes, and voltage reference mode.

- 7. On-chip integer 1-to-8 input clock divider and multichip sync function to support a wide range of clocking schemes and multichannel subsystems.

# **SPECIFICATIONS** DC SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V,  $f_S = 185 \text{ MSPS}$ , 1.75 V p-p differential input, VIN = -1.0 dBFS differential input, and default SPI, unless otherwise noted.

Table 1.

| Parameter                                    | Temperature | Min   | Тур      | Max   | Unit   |

|----------------------------------------------|-------------|-------|----------|-------|--------|

| RESOLUTION                                   | Full        | 11    |          |       | Bits   |

| ACCURACY                                     |             |       |          |       |        |

| No Missing Codes                             | Full        |       | Guarante | ed    |        |

| Offset Error                                 | Full        | -0.9  | +0.1     | +0.9  | mV     |

| Gain Error                                   | Full        | +4    | +11      | +18   | % FSR  |

| Differential Nonlinearity (DNL) <sup>1</sup> | Full        | -0.4  | ±0.1     | +0.4  | LSB    |

| Integral Nonlinearity (INL)1                 | Full        | -0.55 | ±0.17    | +0.55 | LSB    |

| MATCHING CHARACTERISTIC                      |             |       |          |       |        |

| Offset Error                                 | Full        | -5    | +3       | +11   | mV     |

| Gain Error                                   | Full        | 0     | +2.1     | +8    | % FSR  |

| TEMPERATURE DRIFT                            |             |       |          |       |        |

| Offset Error                                 | Full        |       | 2        |       | ppm/°C |

| Gain Error                                   | Full        |       | 40       |       | ppm/°C |

| ANALOG INPUT                                 |             |       |          |       |        |

| Input Range                                  | Full        | 1.4   | 1.75     | 2.0   | V p-p  |

| Input Common-Mode Voltage                    | Full        |       | 0.95     |       | V      |

| Input Resistance (Differential)              | Full        |       | 20       |       | kΩ     |

| Input Capacitance <sup>2</sup>               | Full        |       | 5        |       | pF     |

| POWER SUPPLIES                               |             |       |          |       |        |

| Supply Voltage                               |             |       |          |       |        |

| AVDD                                         | Full        | 1.7   | 1.8      | 1.9   | V      |

| DRVDD                                        | Full        | 1.7   | 1.8      | 1.9   | V      |

| Supply Current                               |             |       |          |       |        |

| I <sub>AVDD</sub> <sup>1</sup>               | Full        |       | 466      | 510   | mA     |

| I <sub>DRVDD</sub> <sup>1</sup> (1.8 V LVDS) | Full        |       | 170      | 183   | mA     |

| POWER CONSUMPTION                            |             |       |          |       |        |

| Sine Wave Input <sup>1</sup>                 | Full        |       | 1145     | 1247  | mW     |

| Standby Power <sup>3</sup>                   | Full        |       | 129      |       | mW     |

| Power-Down Power                             | Full        |       | 3.8      | 10    | mW     |

$<sup>^{1}</sup>$  Measured with a 10 MHz, 0 dBFS sine wave, with 100  $\Omega$  termination on each LVDS output pair.

<sup>&</sup>lt;sup>2</sup> Input capacitance refers to the effective capacitance between one differential input pin and AGND.

<sup>&</sup>lt;sup>3</sup> Standby power is measured with a dc input and the CLKx pins inactive (set to AVDD or AGND).

# **AC SPECIFICATIONS**

AVDD = 1.8 V, DRVDD = 1.8 V,  $f_S = 185 \text{ MSPS}$ , 1.75 V p-p differential input, VIN = -1.0 dBFS differential input, and default SPI, unless otherwise noted.

Table 2.

| Parameter <sup>1</sup>                   | Temperature | Min  | Тур Мах | Unit |

|------------------------------------------|-------------|------|---------|------|

| SIGNAL-TO-NOISE-RATIO (SNR)—NSR DISABLED |             |      |         |      |

| $f_{IN} = 10 \text{ MHz}$                | 25°C        |      | 66.6    | dBFS |

| $f_{IN} = 50 \text{ MHz}$                | 25°C        |      | 66.5    | dBFS |

| $f_{IN} = 70 \text{ MHz}$                | 25°C        |      | 66.5    | dBFS |

| $f_{IN} = 170 \text{ MHz}$               | 25°C        |      | 66.3    | dBFS |

|                                          | Full        | 65.6 |         | dBFS |

| $f_{IN} = 250 \text{ MHz}$               | 25°C        |      | 65.9    | dBFS |

| SIGNAL-TO-NOISE-RATIO (SNR)—NSR ENABLED  |             |      |         |      |

| 22% BW Mode                              |             |      |         |      |

| $f_{IN} = 10 \text{ MHz}$                | 25°C        |      | 76.0    | dBFS |

| $f_{IN} = 50 \text{ MHz}$                | 25°C        |      | 75.7    | dBFS |

| $f_{IN} = 70 \text{ MHz}$                | 25°C        |      | 75.7    | dBFS |

| $f_{IN} = 170 \text{ MHz}$               | 25°C        |      | 74.3    | dBFS |

|                                          | Full        | 72.9 |         | dBFS |

| $f_{IN} = 250 \text{ MHz}$               | 25°C        |      | 72.8    | dBFS |

| 33% BW Mode                              |             |      |         |      |

| $f_{IN} = 10 \text{ MHz}$                | 25°C        |      | 73.6    | dBFS |

| f <sub>IN</sub> = 50 MHz                 | 25°C        |      | 73.6    | dBFS |

| f <sub>IN</sub> = 70 MHz                 | 25°C        |      | 73.3    | dBFS |

| f <sub>IN</sub> = 170 MHz                | 25°C        |      | 72.5    | dBFS |

|                                          | Full        | 71.3 |         | dBFS |

| $f_{IN} = 230 \text{ MHz}$               | 25°C        |      | 71.2    | dBFS |

| 36% BW Mode                              |             |      |         | 52.5 |

| f <sub>IN</sub> = 10 MHz                 | 25°C        |      | 72.8    | dBFS |

| f <sub>IN</sub> = 50 MHz                 | 25°C        |      | 72.6    | dBFS |

| $f_{IN} = 70 \text{ MHz}$                | 25°C        |      | 72.6    | dBFS |

| $f_{IN} = 170 \text{ MHz}$               | 25°C        |      | 71.8    | dBFS |

|                                          | Full        | 70.7 |         | dBFS |

| $f_{IN} = 250 \text{ MHz}$               | 25°C        |      | 70.8    | dBFS |

| SIGNAL-TO-NOISE-AND DISTORTION (SINAD)   |             |      |         |      |

| $f_{IN} = 10 \text{ MHz}$                | 25°C        |      | 65.5    | dBFS |

| f <sub>IN</sub> = 50 MHz                 | 25°C        |      | 65.5    | dBFS |

| $f_{IN} = 70 \text{ MHz}$                | 25°C        |      | 65.5    | dBFS |

| $f_{\text{IN}} = 170 \text{ MHz}$        | 25°C        |      | 65.3    | dBFS |

| 1110 170 111112                          | Full        | 64.6 | 03.3    | dBFS |

| $f_{IN} = 250 \text{ MHz}$               | 25°C        | 0 10 | 64.8    | dBFS |

| EFFECTIVE NUMBER OF BITS (ENOB)          | 23 0        |      | 3 1.0   | 4513 |

| $f_{\text{IN}} = 10 \text{ MHz}$         | 25°C        |      | 10.6    | Bits |

| $f_{IN} = 50 \text{ MHz}$                | 25°C        |      | 10.6    | Bits |

| $f_{\text{IN}} = 70 \text{ MHz}$         | 25°C        |      | 10.6    | Bits |

| $f_{\text{IN}} = 170 \text{ MHz}$        | 25°C        |      | 10.6    | Bits |

| $f_{\text{IN}} = 250 \text{MHz}$         | 25°C        |      | 10.5    | Bits |

| Parameter <sup>1</sup>                                 | Temperature | Min | Тур        | Max | Unit |

|--------------------------------------------------------|-------------|-----|------------|-----|------|

| WORST SECOND OR THIRD HARMONIC                         |             |     |            |     |      |

| $f_{IN} = 10 \text{ MHz}$                              | 25°C        |     | -94        |     | dBc  |

| $f_{IN} = 50 \text{ MHz}$                              | 25°C        |     | -91        |     | dBc  |

| $f_{IN} = 70 \text{ MHz}$                              | 25°C        |     | -88        |     | dBc  |

| $f_{IN} = 170 \text{ MHz}$                             | 25°C        |     | -90        |     | dBc  |

|                                                        | Full        |     |            | -80 | dBc  |

| $f_{IN} = 250 \text{ MHz}$                             | 25°C        |     | -83        |     | dBc  |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)                     |             |     |            |     |      |

| $f_{IN} = 10 \text{ MHz}$                              | 25°C        |     | 94         |     | dBc  |

| $f_{IN} = 50 \text{ MHz}$                              | 25°C        |     | 91         |     | dBc  |

| $f_{IN} = 70 \text{ MHz}$                              | 25°C        |     | 88         |     | dBc  |

| $f_{IN} = 170 \text{ MHz}$                             | 25°C        |     | 90         |     | dBc  |

|                                                        | Full        | 80  |            |     | dBc  |

| $f_{IN} = 250 \text{ MHz}$                             | 25°C        |     | 83         |     | dBc  |

| WORST OTHER HARMONIC (FOURTH THROUGH EIGHTH)           |             |     |            |     |      |

| $f_{IN} = 10 \text{ MHz}$                              | 25°C        |     | -94        |     | dBc  |

| $f_{IN} = 50 \text{ MHz}$                              | 25°C        |     | <b>-95</b> |     | dBc  |

| $f_{IN} = 70 \text{ MHz}$                              | 25°C        |     | -94        |     | dBc  |

| $f_{IN} = 170 \text{ MHz}$                             | 25°C        |     | -94        |     | dBc  |

|                                                        | Full        |     |            | -80 | dBc  |

| $f_{IN} = 250 \text{ MHz}$                             | 25°C        |     | -90        |     | dBc  |

| TWO TONE SFDR (–7 dBFS)                                |             |     |            |     |      |

| $f_{IN1} = 169 \text{ MHz}, f_{IN2} = 172 \text{ MHz}$ | 25°C        |     | 89         |     | dBc  |

| CROSSTALK <sup>2</sup>                                 | Full        |     | 95         |     | dB   |

| ANALOG INPUT BANDWIDTH                                 | 25°C        |     | 800        |     | MHz  |

<sup>&</sup>lt;sup>1</sup> See the AN-835 Application Note, *Understanding High Speed ADC Testing and Evaluation*, for a complete set of definitions. <sup>2</sup> Crosstalk is measured at 155 MHz with –1 dBFS on one channel and no input on the alternate channel.

# **DIGITAL SPECIFICATIONS**

AVDD = 1.8 V, DRVDD = 1.8 V,  $f_S = 185 \text{ MSPS}$ , 1.75 V p-p differential input, VIN = -1.0 dBFS differential input, and default SPI, unless otherwise noted.

Table 3.

| Parameter                              | Temperature | Min        | Тур         | Max        | Unit  |

|----------------------------------------|-------------|------------|-------------|------------|-------|

| DIFFERENTIAL CLOCK INPUTS (CLK+, CLK-) |             |            |             |            |       |

| Logic Compliance                       |             |            | CMOS/LVDS/L | VPECL      |       |

| Internal Common-Mode Bias              | Full        |            | 0.9         |            | V     |

| Differential Input Voltage             | Full        | 0.2        |             | 3.6        | V p-p |

| Input Voltage Range                    | Full        | AGND - 0.3 |             | AVDD + 0.2 | V     |

| High Level Input Voltage               | Full        | 1.2        |             | 2.0        | V     |

| Low Level Input Voltage                | Full        | 0          |             | 0.8        | V     |

| High Level Input Current               | Full        | -10        |             | +10        | μΑ    |

| Low Level Input Current                | Full        | -10        |             | +10        | μΑ    |

| Input Resistance                       | Full        | 8          | 10          | 12         | kΩ    |

| Input Capacitance                      | Full        |            | 4           |            | pF    |

| SYNC INPUT                             |             |            |             |            |       |

| Logic Compliance                       |             |            | CMOS        |            |       |

| Internal Bias                          | Full        |            | 0.9         |            | V     |

| Input Voltage Range                    | Full        | AGND       |             | AVDD       | V     |

| High Level Input Voltage               | Full        | 1.2        |             | AVDD       | V     |

| Low Level Input Voltage                | Full        | AGND       |             | 0.6        | V     |

| High Level Input Current               | Full        | -100       |             | +100       | μΑ    |

| Low Level Input Current                | Full        | -100       |             | +100       | μΑ    |

| Input Resistance                       | Full        | 12         | 16          | 20         | kΩ    |

| Input Capacitance                      | Full        |            | 1           |            | pF    |

| LOGIC INPUT (CSB) <sup>1</sup>         |             |            |             |            |       |

| High Level Input Voltage               | Full        | 1.22       |             | 2.1        | V     |

| Low Level Input Voltage                | Full        | 0          |             | 0.6        | V     |

| High Level Input Current               | Full        | -10        |             | +10        | μΑ    |

| Low Level Input Current                | Full        | 40         |             | 132        | μΑ    |

| Input Resistance                       | Full        |            | 26          |            | kΩ    |

| Input Capacitance                      | Full        |            | 2           |            | pF    |

| LOGIC INPUT (SCLK) <sup>2</sup>        |             |            |             |            |       |

| High Level Input Voltage               | Full        | 1.22       |             | 2.1        | V     |

| Low Level Input Voltage                | Full        | 0          |             | 0.6        | V     |

| High Level Input Current               | Full        | -92        |             | -135       | μΑ    |

| Low Level Input Current                | Full        | -10        |             | +10        | μΑ    |

| Input Resistance                       | Full        |            | 26          |            | kΩ    |

| Input Capacitance                      | Full        |            | 2           |            | pF    |

| LOGIC INPUT/OUTPUT (SDIO) <sup>2</sup> |             |            |             |            |       |

| High Level Input Voltage               | Full        | 1.22       |             | 2.1        | V     |

| Low Level Input Voltage                | Full        | 0          |             | 0.6        | V     |

| High Level Input Current               | Full        | -10        |             | +10        | μΑ    |

| Low Level Input Current                | Full        | 38         |             | 128        | μΑ    |

| Input Resistance                       | Full        |            | 26          |            | kΩ    |

| Input Capacitance                      | Full        |            | 5           |            | pF    |

| Parameter                         | Temperature | Min   | Тур | Max   | Unit |

|-----------------------------------|-------------|-------|-----|-------|------|

| LOGIC INPUT (MODE) <sup>1</sup>   |             |       |     |       |      |

| High Level Input Voltage          | Full        | 1.22  |     | 2.1   | V    |

| Low Level Input Voltage           | Full        | 0     |     | 0.6   | V    |

| High Level Input Current          | Full        | -10   |     | +10   | μΑ   |

| Low Level Input Current           | Full        | 40    |     | 132   | μΑ   |

| Input Resistance                  | Full        |       | 26  |       | kΩ   |

| Input Capacitance                 | Full        |       | 2   |       | pF   |

| LOGIC INPUT (PDWN) <sup>2</sup>   |             |       |     |       |      |

| High Level Input Voltage          | Full        | 1.22  |     | 2.1   | V    |

| Low Level Input Voltage           | Full        | 0     |     | 0.6   | V    |

| High Level Input Current          | Full        | -90   |     | -134  | μΑ   |

| Low Level Input Current           | Full        | -10   |     | +10   | μΑ   |

| Input Resistance                  | Full        |       | 26  |       | kΩ   |

| Input Capacitance                 | Full        |       | 5   |       | pF   |

| DIGITAL OUTPUTS (LVDS)            |             |       |     |       |      |

| Differential Output Voltage (Vod) | Full        | 247   |     | 454   | mV   |

| Output Offset Voltage (Vos)       | Full        | 1.125 |     | 1.375 | V    |

<sup>&</sup>lt;sup>1</sup> Pull up. <sup>2</sup> Pull down.

# **SWITCHING SPECIFICATIONS**

AVDD = 1.8 V, DRVDD = 1.8 V,  $f_S = 185 \text{ MSPS}$ , 1.75 V p-p differential input, VIN = -1.0 dBFS differential input, and default SPI, unless otherwise noted.

Table 4.

| Parameter                                              | Temperature | Min | Тур  | Max | Unit   |

|--------------------------------------------------------|-------------|-----|------|-----|--------|

| CLOCK INPUT PARAMETERS                                 |             |     |      |     |        |

| Input Clock Rate                                       | Full        |     |      | 625 | MHz    |

| Conversion Rate <sup>1</sup>                           | Full        | 40  | 185  | 200 | MSPS   |

| CLK Pulse Width High (tcH) <sup>2</sup>                | Full        |     | 2.7  |     | ns     |

| Aperture Delay (t <sub>A</sub> ) <sup>2</sup>          | Full        |     | 1.3  |     | ns     |

| Aperture Uncertainty (Jitter, t <sub>.</sub> )         | Full        |     | 0.13 |     | ps rms |

| DATA OUTPUT PARAMETERS                                 |             |     |      |     |        |

| Data Propagation Delay (tpD) <sup>2</sup>              | Full        | 3.0 | 4.0  | 4.9 | ns     |

| DCO Propagation Delay (t <sub>DCO</sub> ) <sup>2</sup> | Full        | 3.1 | 4.0  | 4.9 | ns     |

| DCO to Data Skew (t <sub>SKEW</sub> ) <sup>2</sup>     | Full        | -41 | +6.1 | +33 | ps     |

| Pipeline Delay (Latency)                               | Full        |     | 9    |     | Cycles |

| With NSR Enabled                                       | Full        |     | 12   |     | Cycles |

| Wake-Up Time (from Standby) <sup>3</sup>               | Full        |     | 0.5  |     | μs     |

| Wake-Up Time (from Power Down) <sup>3</sup>            | Full        |     | 310  |     | μs     |

| OUT-OF-RANGE RECOVERY TIME                             | Full        |     | 2    |     | Cycles |

<sup>&</sup>lt;sup>1</sup> Conversion rate is the clock rate after the divider.

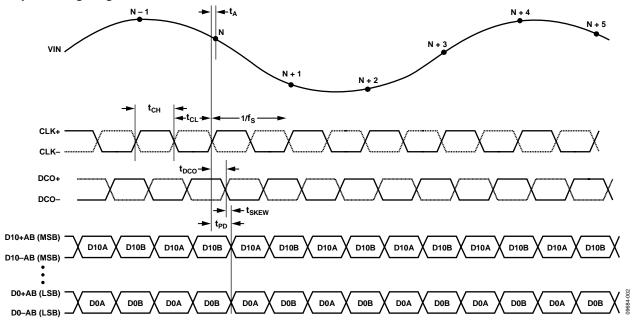

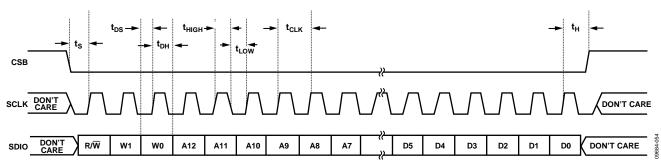

# **Data Output Timing Diagram**

Figure 2. Data Output Timing (Timing for Channel C and Channel D Is Identical to Timing for Channel A and Channel B)

<sup>&</sup>lt;sup>2</sup> See Figure 2 for details.

<sup>&</sup>lt;sup>3</sup> Wake-up time is dependent on the value of the decoupling capacitors.

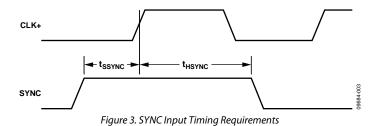

# **TIMING SPECIFICATIONS**

AVDD = 1.8 V, DRVDD = 1.8 V,  $f_S = 185 \text{ MSPS}$ , 1.75 V p-p differential input, VIN = -1.0 dBFS differential input, and default SPI, unless otherwise noted.

Table 5.

| Parameter                | Description                                                                                                                       | Min | Тур  | Max | Unit |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| SYNC TIMING REQUIREMENTS | See Figure 3 for details                                                                                                          |     |      |     |      |

| t <sub>ssync</sub>       | SYNC to rising edge of CLK setup time                                                                                             |     | 0.24 |     | ns   |

| thsync                   | SYNC to rising edge of CLK hold time                                                                                              |     | 0.40 |     | ns   |

| SPI TIMING REQUIREMENTS  | See Figure 60 for details, except where noted                                                                                     |     |      |     |      |

| t <sub>DS</sub>          | Setup time between the data and the rising edge of SCLK                                                                           | 2   |      |     | ns   |

| t <sub>DH</sub>          | Hold time between the data and the rising edge of SCLK                                                                            | 2   |      |     | ns   |

| t <sub>CLK</sub>         | Period of the SCLK                                                                                                                | 40  |      |     | ns   |

| <b>t</b> s               | Setup time between CSB and SCLK                                                                                                   | 2   |      |     | ns   |

| t <sub>H</sub>           | Hold time between CSB and SCLK                                                                                                    | 2   |      |     | ns   |

| tніgн                    | SCLK pulse width high                                                                                                             | 10  |      |     | ns   |

| t <sub>LOW</sub>         | SCLK pulse width low                                                                                                              | 10  |      |     | ns   |

| t <sub>en_sdio</sub>     | Time required for the SDIO pin to switch from an input to an output relative to the SCLK falling edge (not pictured in Figure 60) | 10  |      |     | ns   |

| t <sub>DIS_SDIO</sub>    | Time required for the SDIO pin to switch from an output to an input relative to the SCLK rising edge (not pictured in Figure 60)  | 10  |      |     | ns   |

# **Sync Input Timing Diagram**

# **ABSOLUTE MAXIMUM RATINGS**

Table 6.

| Tuble 0:                                   |                         |

|--------------------------------------------|-------------------------|

| Parameter                                  | Rating                  |

| AVDD to AGND                               | -0.3 V to +2.0 V        |

| DRVDD to AGND                              | -0.3 V to +2.0 V        |

| VIN+x, VIN-x to AGND                       | -0.3 V to AVDD + 0.2 V  |

| CLK+, CLK- to AGND                         | -0.3 V to AVDD + 0.2 V  |

| SYNC to AGND                               | -0.3 V to AVDD + 0.2 V  |

| VCMx to AGND                               | -0.3 V to AVDD + 0.2 V  |

| CSB to AGND                                | -0.3 V to DRVDD + 0.2 V |

| SCLK to AGND                               | -0.3 V to DRVDD + 0.2 V |

| SDIO to AGND                               | -0.3 V to DRVDD + 0.2 V |

| PDWN to AGND                               | -0.3 V to DRVDD + 0.2 V |

| MODE to AGND                               | -0.3 V to DRVDD + 0.2 V |

| Digital Outputs to AGND                    | -0.3 V to DRVDD + 0.2 V |

| DCO+AB, DCO-AB, DCO+CD,<br>DCO-CD to AGND  | -0.3 V to DRVDD + 0.2 V |

| Operating Temperature Range<br>(Ambient)   | −40°C to +85°C          |

| Maximum Junction Temperature<br>Under Bias | 150℃                    |

| Storage Temperature Range<br>(Ambient)     | −65°C to +150°C         |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS

The values in Table 7 are per JEDEC JESD51-7 and JEDEC JESD25-5 for a 2S2P test board. Typical  $\theta_{JA}$  is specified for a 4-layer printed circuit board (PCB) with a solid ground plane. As shown in Table 7, airflow improves heat dissipation, which reduces  $\theta_{JA}$ . In addition, metal in direct contact with the package leads from metal traces, through holes, ground, and power planes reduces  $\theta_{JA}$ .

Table 7.

| Package Type     | Airflow<br>Velocity | $\theta_{JA}^1$ | $\theta_{JC}^2$ | $\theta_{JB}^3$ | Unit |

|------------------|---------------------|-----------------|-----------------|-----------------|------|

| 144-Ball CSP_BGA | 0 m/s               | 26.9            | 8.9             | 6.6             | °C/W |

|                  | 1 m/s               | 24.2            |                 |                 | °C/W |

|                  | 2.5 m/s             | 23.0            |                 |                 | °C/W |

<sup>&</sup>lt;sup>1</sup>Per JEDEC JESD51-2 (still air) or JEDEC JESD51-6 (moving air).

The values in Table 8 are from simulations. The PCB is a JEDEC multilayer board. Thermal performance for actual applications requires careful inspection of the conditions in the application to determine whether they are similar to those assumed in these calculations.

Table 8.

| Package Type     | Airflow<br>Velocity | Ψјв  | Ψл   | Unit |

|------------------|---------------------|------|------|------|

| 144-Ball CSP_BGA | 0 m/s               | 14.4 | 0.23 | °C/W |

|                  | 1 m/s               | 14.0 | 0.50 | °C/W |

|                  | 2.5 m/s             | 13.9 | 0.53 | °C/W |

# **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup>Per MIL-STD 883, Method 1012.1.

<sup>&</sup>lt;sup>3</sup>Per JEDEC JESD51-8 (still air).

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

|   | 1     | 2     | 3     | 4     | 5     | 6      | 7     | 8     | 9     | 10    | 11    | 12     |           |

|---|-------|-------|-------|-------|-------|--------|-------|-------|-------|-------|-------|--------|-----------|

| A | AGND  | VIN+C | VIN-C | AGND  | AVDD  | CLK-   | CLK+  | AVDD  | AGND  | VIN-B | VIN+B | AGND   |           |

| В | AGND  | AGND  | VCMC  | AGND  | AVDD  | AVDD   | AVDD  | AVDD  | AGND  | VCMB  | AGND  | AGND   |           |

| С | VIN+D | AGND  | AGND  | CSB   | SDIO  | SCLK   | PDWN  | SYNC  | MODE  | AGND  | AGND  | VIN+A  |           |

| D | VIN-D | VCMD  | AGND  | AVDD  | AVDD  | AVDD   | AVDD  | AVDD  | AVDD  | AGND  | VCMA  | VIN-A  |           |

| E | AGND  | AVDD  | AVDD  | AVDD  | AVDD  | AVDD   | AVDD  | AVDD  | AVDD  | AVDD  | AVDD  | AGND   |           |

| F | AGND  | AGND  | AGND  | AGND  | AGND  | AGND   | AGND  | AGND  | AGND  | AGND  | AGND  | AGND   |           |

| G | DRGND | DRGND | DRGND | DRGND | DRGND | DRGND  | DRGND | DRGND | DRGND | DRGND | DRGND | DRGND  |           |

| Н | DRVDD | DRVDD | DRVDD | DRVDD | DRVDD | DRVDD  | DRVDD | DRVDD | DRVDD | DRVDD | DRVDD | DRVDD  |           |

| J | D0-CD | D2-CD | D4-CD | D6-CD | D8-CD | D10-CD | D0-AB | D2-AB | D4-AB | D6-AB | D8-AB | D10-AB |           |

| K | D0+CD | D2+CD | D4+CD | D6+CD | D8+CD | D10+CD | D0+AB | D2+AB | D4+AB | D6+AB | D8+AB | D10+AB |           |

| L | D1-CD | D3-CD | D5-CD | D7-CD | D9-CD | DCO-CD | D1-AB | D3-AB | D5-AB | D7-AB | D9-AB | DCO-AB | _         |

| М | D1+CD | D3+CD | D5+CD | D7+CD | D9+CD | DCO+CD | D1+AB | D3+AB | D5+AB | D7+AB | D9+AB | DCO+AB | 09684-004 |

Figure 4. Pin Configuration (Top View)

**Table 9. Pin Function Descriptions**

| Pin No.                                                                                           | Mnemonic | Туре   | Description                                               |

|---------------------------------------------------------------------------------------------------|----------|--------|-----------------------------------------------------------|

| A5, A8, B5 to B8, D4 to<br>D9, E2 to E11                                                          | AVDD     | Supply | Analog Power Supply. 1.8 V nominal.                       |

| A1, A4, A9, A12, B1, B2,<br>B4, B9, B11, B12, C2, C3,<br>C10, C11, D3, D10, E1,<br>E12, F1 to F12 | AGND     | Ground | Analog Ground.                                            |

| H1 to H12                                                                                         | DRVDD    | Supply | Digital Output Driver Supply. 1.8 V nominal.              |

| G1 to G12                                                                                         | DRGND    | Ground | Digital Output Driver Ground.                             |

| A7                                                                                                | CLK+     | Input  | ADC Clock Input—True.                                     |

| A6                                                                                                | CLK-     | Input  | ADC Clock Input—Complement.                               |

| C12                                                                                               | VIN+A    | Input  | Differential Analog Input Pin (+) for Channel A.          |

| D12                                                                                               | VIN-A    | Input  | Differential Analog Input Pin (–) for Channel A.          |

| D11                                                                                               | VCMA     | Output | Common-Mode Level Bias Output for Analog Input Channel A. |

| A11                                                                                               | VIN+B    | Input  | Differential Analog Input Pin (+) for Channel B.          |

| A10                                                                                               | VIN-B    | Input  | Differential Analog Input Pin (–) for Channel B.          |

| B10                                                                                               | VCMB     | Output | Common-Mode Level Bias Output for Analog Input Channel B. |

| A2                                                                                                | VIN+C    | Input  | Differential Analog Input Pin (+) for Channel C.          |

| A3                                                                                                | VIN-C    | Input  | Differential Analog Input Pin (–) for Channel C.          |

| B3                                                                                                | VCMC     | Output | Common-Mode Level Bias Output for Analog Input Channel C. |

| C1                                                                                                | VIN+D    | Input  | Differential Analog Input Pin (+) for Channel D.          |

| D1                                                                                                | VIN-D    | Input  | Differential Analog Input Pin (–) for Channel D.          |

| D2                                                                                                | VCMD     | Output | Common-Mode Level Bias Output for Analog Input Channel D. |

| K7                                                                                                | D0+AB    | Output | Channel A and Channel B LVDS Output Data 0—True.          |

| J7                                                                                                | D0-AB    | Output | Channel A and Channel B LVDS Output Data 0—Complement.    |

| M7                                                                                                | D1+AB    | Output | Channel A and Channel B LVDS Output Data 1—True.          |

| L7                                                                                                | D1-AB    | Output | Channel A and Channel B LVDS Output Data 1—Complement.    |

| K8                                                                                                | D2+AB    | Output | Channel A and Channel B LVDS Output Data 2—True.          |

| J8                                                                                                | D2-AB    | Output | Channel A and Channel B LVDS Output Data 2—Complement.    |

| M8                                                                                                | D3+AB    | Output | Channel A and Channel B LVDS Output Data 3—True.          |

| L8                                                                                                | D3-AB    | Output | Channel A and Channel B LVDS Output Data 3—Complement.    |

| K9                                                                                                | D4+AB    | Output | Channel A and Channel B LVDS Output Data 4—True.          |

| J9                                                                                                | D4-AB    | Output | Channel A and Channel B LVDS Output Data 4—Complement.    |

Rev. A | Page 12 of 36

| Pin No. | Mnemonic | Туре         | Description                                                      |

|---------|----------|--------------|------------------------------------------------------------------|

| M9      | D5+AB    | Output       | Channel A and Channel B LVDS Output Data 5—True.                 |

| L9      | D5-AB    | Output       | Channel A and Channel B LVDS Output Data 5—Complement.           |

| K10     | D6+AB    | Output       | Channel A and Channel B LVDS Output Data 6—True.                 |

| J10     | D6-AB    | Output       | Channel A and Channel B LVDS Output Data 6—Complement.           |

| M10     | D7+AB    | Output       | Channel A and Channel B LVDS Output Data 7—True.                 |

| L10     | D7–AB    | Output       | Channel A and Channel B LVDS Output Data 7—Complement.           |

| K11     | D8+AB    | Output       | Channel A and Channel B LVDS Output Data 8—True.                 |

| J11     | D8-AB    | Output       | Channel A and Channel B LVDS Output Data 8—Complement.           |

| M11     | D9+AB    | Output       | Channel A and Channel B LVDS Output Data 9—True.                 |

| L11     | D9–AB    | Output       | Channel A and Channel B LVDS Output Data 9—Complement.           |

| K12     | D10+AB   | Output       | Channel A and Channel B LVDS Output Data 10—True.                |

| J12     | D10-AB   | Output       | Channel A and Channel B LVDS Output Data 10—Complement.          |

| M12     | DCO+AB   | Output       | Data Clock LVDS Output for Channel A and Channel B—True.         |

| L12     | DCO-AB   | Output       | Data Clock LVDS Output for Channel A and Channel B—Complement.   |

| K1      | D0+CD    | Output       | Channel C and Channel D LVDS Output Data 0—True.                 |

| J1      | D0-CD    | Output       | Channel C and Channel D LVDS Output Data 0—Complement.           |

| M1      | D1+CD    | Output       | Channel C and Channel D LVDS Output Data 1—True.                 |

| L1      | D1–CD    | Output       | Channel C and Channel D LVDS Output Data 1—Complement.           |

| K2      | D2+CD    | Output       | Channel C and Channel D LVDS Output Data 2—True.                 |

| J2      | D2–CD    | Output       | Channel C and Channel D LVDS Output Data 2—Complement.           |

| M2      | D3+CD    | Output       | Channel C and Channel D LVDS Output Data 3—True.                 |

| L2      | D3–CD    | Output       | Channel C and Channel D LVDS Output Data 3—Complement.           |

| K3      | D4+CD    | Output       | Channel C and Channel D LVDS Output Data 4—True.                 |

| J3      | D4–CD    | Output       | Channel C and Channel D LVDS Output Data 4—Complement.           |

| M3      | D5+CD    | Output       | Channel C and Channel D LVDS Output Data 5—True.                 |

| L3      | D5–CD    | Output       | Channel C and Channel D LVDS Output Data 5—Complement.           |

| K4      | D6+CD    | Output       | Channel C and Channel D LVDS Output Data 6—True.                 |

| J4      | D6–CD    | Output       | Channel C and Channel D LVDS Output Data 6—Complement.           |

| M4      | D7+CD    | Output       | Channel C and Channel D LVDS Output Data 7—True.                 |

| L4      | D7–CD    | Output       | Channel C and Channel D LVDS Output Data 7—Complement.           |

| K5      | D8+CD    | Output       | Channel C and Channel D LVDS Output Data 8—True.                 |

| J5      | D8–CD    | Output       | Channel C and Channel D LVDS Output Data 8—Complement.           |

| M5      | D9+CD    | Output       | Channel C and Channel D LVDS Output Data 9—True.                 |

| L5      | D9–CD    | Output       | Channel C and Channel D LVDS Output Data 9—Complement.           |

| K6      | D10+CD   | Output       | Channel C and Channel D LVDS Output Data 10—True.                |

| J6      | D10-CD   | Output       | Channel C and Channel D LVDS Output Data 10—Complement.          |

| M6      | DCO+CD   | Output       | Data Clock LVDS Output for Channel C and Channel D—True.         |

| L6      | DCO-CD   | Output       | Data Clock LVDS Output for Channel C and Channel D—Complement.   |

| C9      | MODE     | Input        | Mode Select Pin. Logic low enables NSR; logic high disables NSR. |

| C8      | SYNC     | Input        | Digital Synchronization Pin.                                     |

| C7      | PDWN     | Input        | Power-Down Input (Active High).                                  |

| C6      | SCLK     | Input        | SPI Clock.                                                       |

| C5      | SDIO     | Input/Output | SPI Data.                                                        |

| C4      | CSB      | Input        | SPI Chip Select (Active Low).                                    |

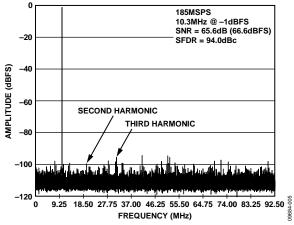

# TYPICAL PERFORMANCE CHARACTERISTICS

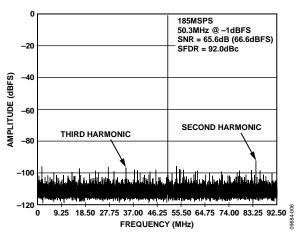

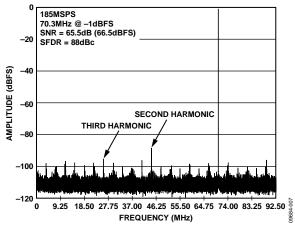

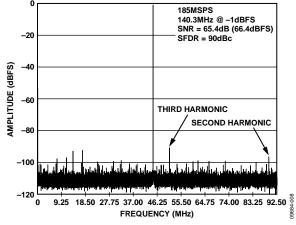

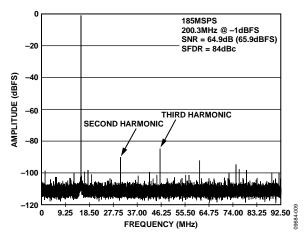

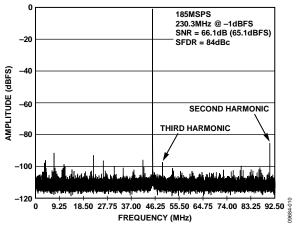

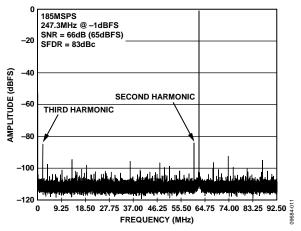

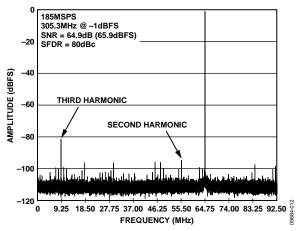

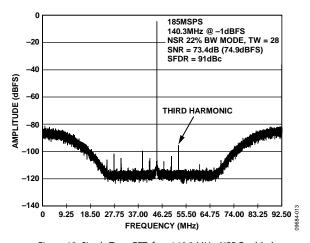

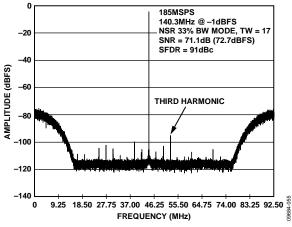

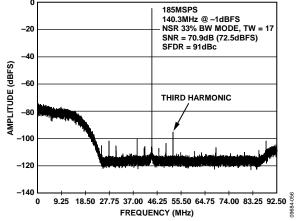

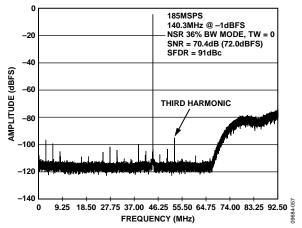

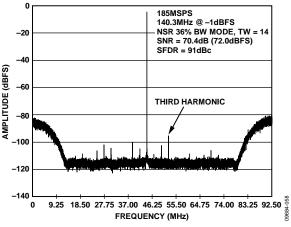

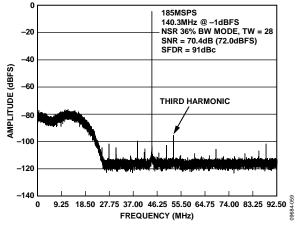

AVDD = 1.8 V, DRVDD = 1.8 V, sample rate = 185 MSPS, 1.75 V p-p differential input, VIN = -1.0 dBFS, 32,000 sample,  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.

Figure 5. Single Tone FFT,  $f_{IN} = 10.3 \text{ MHz}$

Figure 6. Single Tone FFT,  $f_{IN} = 50.3 \text{ MHz}$

Figure 7. Single Tone FFT,  $f_{IN} = 70.3 \text{ MHz}$

Figure 8. Single Tone FFT,  $f_{IN} = 140.3 \text{ MHz}$

Figure 9. Single Tone FFT,  $f_{IN} = 200.3 \text{ MHz}$

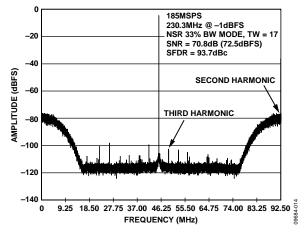

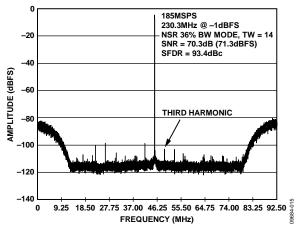

Figure 10. Single Tone FFT,  $f_{IN} = 230.3 MHz$

Figure 11. Single Tone FFT,  $f_{IN} = 247.3 \text{ MHz}$

Figure 12. Single Tone FFT,  $f_{IN} = 305.3 \text{ MHz}$

Figure 13. Single Tone FFT,  $f_{\rm IN}$  = 140.3 MHz, NSR Enabled in 22% BW Mode, Tuning Word = 28

Figure 14. Single Tone FFT,  $f_N = 230.3$  MHz, NSR Enabled in 33% BW Mode, Tuning Word = 17

Figure 15. Single Tone FFT, f<sub>IN</sub> = 230.3 MHz, NSR Enabled in 36% BW Mode, Tuning Word = 14

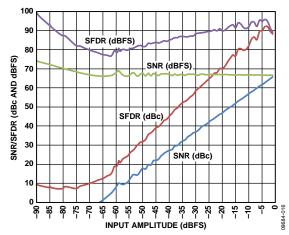

Figure 16. Single Tone SNR/SFDR vs. Input Amplitude ( $A_{IN}$ ),  $f_{IN} = 70.3 \text{ MHz}$

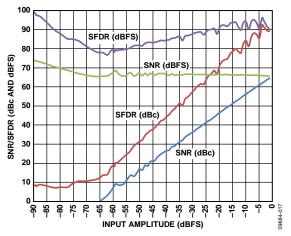

Figure 17. Single Tone SNR/SFDR vs. Input Amplitude ( $A_{IN}$ ),  $f_{IN} = 140.3 \text{ MHz}$

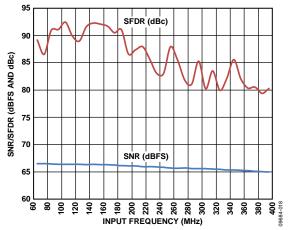

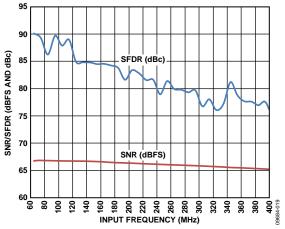

Figure 18. Single Tone SNR/SFDR vs. Input Frequency  $(f_{IN})$ , 1.75 V p-p Full Scale

Figure 19. Single Tone SNR/SFDR vs. Input Frequency  $(f_{IN})$ , 2.0 V p-p Full Scale

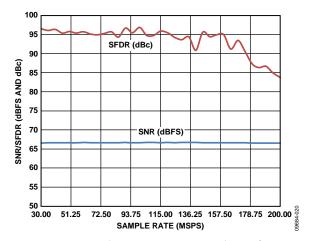

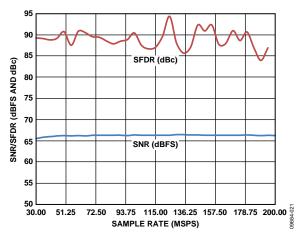

Figure 20. Single Tone SNR/SFDR vs. Sample Rate ( $f_s$ ),  $f_{lN} = 70.3 \text{ MHz}$

Figure 21. Single Tone SNR/SFDR vs. Sample Rate ( $f_s$ ),  $f_{IN} = 140.3 \text{ MHz}$

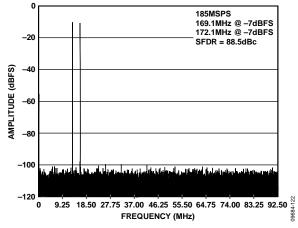

Figure 22. Two Tone FFT,  $f_{\text{IN1}} = 169.1 \text{ MHz}$  and  $f_{\text{IN2}} = 172.1 \text{ MHz}$

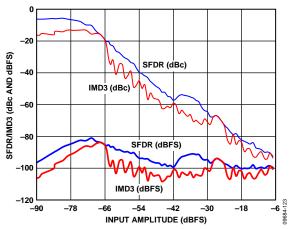

Figure 23. Two Tone SFDR/IMD3 vs. Input Amplitude (A<sub>IN</sub>),  $f_{\rm IN1}=169.1$  MHz and  $f_{\rm IN2}=172.1$  MHz

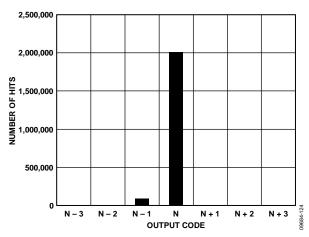

Figure 24. Grounded Input Histogram

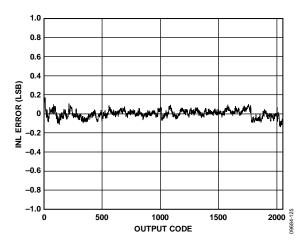

Figure 25. INL,  $f_{IN} = 30.3 MHz$

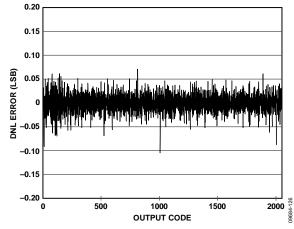

Figure 26. DNL,  $f_{IN} = 30.3 MHz$

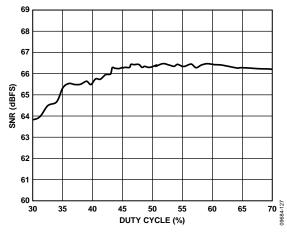

Figure 27. SNR vs. Duty Cycle,  $f_{IN} = 10.3 \text{ MHz}$

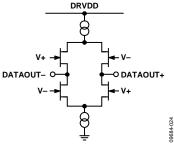

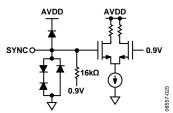

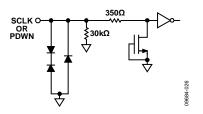

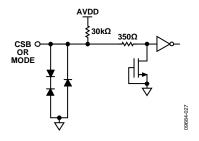

# **EQUIVALENT CIRCUITS**

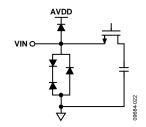

Figure 28. Equivalent Analog Input Circuit

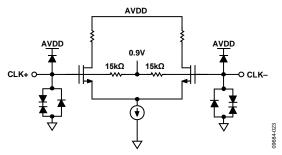

Figure 29. Equivalent Clock Input Circuit

Figure 30. Equivalent LVDS Output Circuit

Figure 31. Equivalent SYNC Input Circuit

Figure 32. Equivalent SCLK and PDWN Input Circuit

Figure 33. Equivalent CSB and MODE Input Circuit

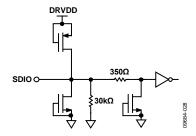

Figure 34. Equivalent SDIO Circuit

# THEORY OF OPERATION

# **ADC ARCHITECTURE**

The AD6657A architecture consists of a quad front-end sampleand-hold circuit, followed by a pipelined, switched capacitor ADC. The quantized outputs from each stage are combined into a final 14-bit result in the digital correction logic. Alternately, the 14-bit result can be processed through the NSR block before it is sent to the digital correction logic.

The pipelined architecture permits the first stage to operate on a new input sample and the remaining stages to operate on the preceding samples. Sampling occurs on the rising edge of the clock.

Each stage of the pipeline, excluding the last, consists of a low resolution flash ADC connected to a switched-capacitor digital-to-analog converter (DAC) and an interstage residue amplifier (MDAC). The residue amplifier magnifies the difference between the reconstructed DAC output and the flash input for the next stage in the pipeline. One bit of redundancy is used in each stage to facilitate digital correction of flash errors. The last stage simply consists of a flash ADC.

The input stage of each channel contains a differential sampling circuit that can be ac- or dc-coupled in differential or single-ended modes. The output staging block aligns the data, corrects errors, and passes the data to the output buffers. The output buffers are powered from a separate supply, allowing adjustment of the output drive current. During power-down, the output buffers go into a high impedance state.

The AD6657A quad IF receiver can simultaneously digitize four channels, making it ideal for diversity reception and digital predistortion (DPD) observation paths in telecommunication systems.

Synchronization capability is provided to allow synchronized timing between multiple channels or multiple devices.

Programming and control of the AD6657A are accomplished using a 3-wire SPI-compatible serial interface.

# **ANALOG INPUT CONSIDERATIONS**

The analog input to the AD6657A is a differential switched capacitor circuit that has been designed for optimum performance while processing a differential input signal.

The clock signal alternatively switches the input between sample mode and hold mode (see Figure 35). When the input is switched to sample mode, the signal source must be capable of charging the sample capacitors and settling within 1/2 of a clock cycle.

A small resistor in series with each input can help reduce the peak transient current required from the output stage of the driving source. A shunt capacitor can be placed across the inputs to provide dynamic charging currents. This passive network creates a low-pass filter at the ADC input; therefore, the precise values are dependent on the application.

In intermediate frequency (IF) undersampling applications, any shunt capacitors should be reduced. In combination with the driving source impedance, the shunt capacitors limit the input bandwidth. For more information on this subject, see the AN-742 Application Note, Frequency Domain Response of Switched-Capacitor ADCs; AN-827 Application Note, A Resonant Approach to Interfacing Amplifiers to Switched-Capacitor ADCs; and the Analog Dialogue article, "Transformer-Coupled Front-End for Wideband A/D Converters" (see www.analog.com).

Figure 35. Switched Capacitor Input

For best dynamic performance, match the source impedances driving the VIN+ and VIN- pins.

An internal differential reference buffer creates positive and negative reference voltages that define the input span of the ADC core. The span of the ADC core is set by this buffer to  $2 \times V_{\text{REF}}$ .

# **Input Common Mode**

The analog inputs of the AD6657A are not internally dc biased. In ac-coupled applications, the user must provide this bias externally. An on-board common-mode voltage reference is included in the design and is available from the VCMx pins. Optimum performance is achieved when the common-mode voltage of the analog input is set by the VCMx pin voltage (typically  $0.5\times AVDD$ ). The VCMx pins must be decoupled to ground by a  $0.1~\mu F$  capacitor.

# **Differential Input Configurations**

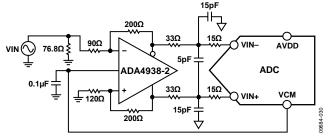

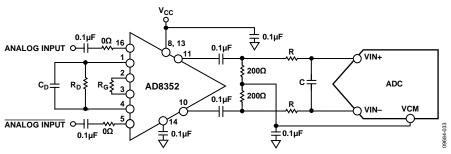

Optimum performance is achieved when driving the AD6657A in a differential input configuration. For baseband applications, the AD8138, ADA4937-2, and ADA4938-2 differential drivers provide excellent performance and a flexible interface to the ADC.

The output common-mode voltage of the ADA4938-2 is easily set with the VCMx pin of the AD6657A (see Figure 36), and the driver can be configured in a Sallen-Key filter topology to provide band limiting of the input signal.

Figure 36. Differential Input Configuration Using the ADA4938-2

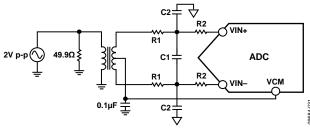

For baseband applications where SNR is a key parameter, differential transformer coupling is the recommended input configuration. An example is shown in Figure 37. To bias the analog input, the VCM voltage can be connected to the center tap of the secondary winding of the transformer.

Figure 37. Differential Transformer-Coupled Configuration

The signal characteristics must be considered when selecting a transformer. Most RF transformers saturate at frequencies below a few megahertz (MHz). Excessive signal power can also cause core saturation, which leads to distortion.

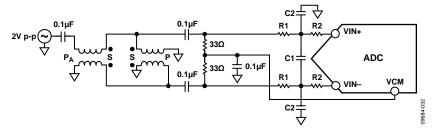

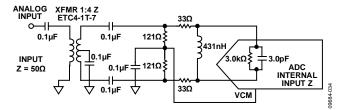

At input frequencies in the second Nyquist zone and above, the noise performance of most amplifiers is not adequate to achieve the true SNR performance of the AD6657A. For applications in which SNR is a key parameter, differential double balun coupling is the recommended input configuration (see Figure 38). In this configuration, the input is ac-coupled and the CML is provided to each input through a 33  $\Omega$  resistor. These resistors compensate for losses in the input baluns to provide a 50  $\Omega$  impedance to the driver.

In the double balun and transformer configurations, the value of the input capacitors and resistors is dependent on the input frequency and source impedance and may need to be reduced or removed. Table 10 lists recommended values to set the RC network. At higher input frequencies, good performance can be achieved by using a ferrite bead in series with a resistor and removing the capacitors. However, these values are dependent on the input signal and should be used as a starting guide only.

**Table 10. Example RC Network**

| Frequency<br>Range<br>(MHz) | R1 Series<br>(Each) | C1 Differential | R2 Series<br>(Each) | C2 Shunt<br>(Each) |

|-----------------------------|---------------------|-----------------|---------------------|--------------------|

| 0 to 100                    | 33 Ω                | 5 pF            | 15 Ω                | 15 pF              |

| 100 to 200                  | 10 Ω                | 5 pF            | 10 Ω                | 10 pF              |

| 100 to 300                  | 10 Ω¹               | Remove          | 66 Ω                | Remove             |

$<sup>^{\</sup>text{1}}$  In this configuration, R1 is a ferrite bead with a value of 10  $\Omega$  @ 100 MHz.

An alternative to using a transformer-coupled input at frequencies in the second Nyquist zone is to use the AD8352 differential driver (see Figure 39). For more information, see the AD8352 data sheet.

Figure 38. Differential Double Balun Input Configuration

Figure 39. Differential Input Configuration Using the AD8352

Figure 40. 1:4 Transformer Passive Configuration

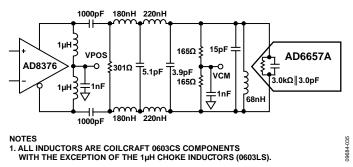

Figure 41. Active Front-End Configuration Using the AD8376

For the popular IF band of 140 MHz, Figure 40 shows an example of a 1:4 transformer passive configuration where a differential inductor is used to resonate with the internal input capacitance of the AD6657A. This configuration realizes excellent noise and distortion performance. Figure 41 shows an example of an active front-end configuration using the AD8376 dual variable gain amplifier (VGA). This configuration is recommended when signal gain is required.

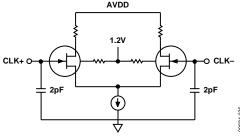

# **CLOCK INPUT CONSIDERATIONS**

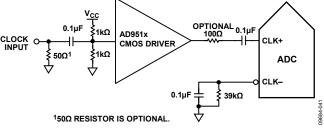

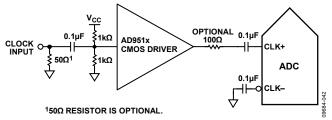

For optimum performance, clock the AD6657A sample clock inputs, CLK+ and CLK-, with a differential signal. The signal is typically ac-coupled into the CLK+ and CLK- pins via a transformer or capacitors. These pins are biased internally and require no external bias (see Figure 42).

Figure 42. Equivalent Clock Input Circuit

# **Clock Input Options**

The AD6657A has a very flexible clock input structure. The clock input can be a CMOS, LVDS, LVPECL, or sine wave signal. Regardless of the type of signal being used, clock source jitter is of the most concern (see the Jitter Considerations section).

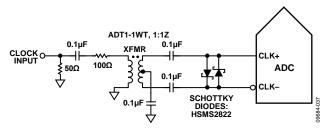

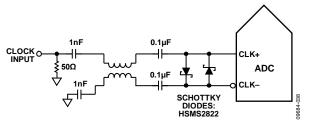

Figure 43 and Figure 44 show two preferred methods for clocking the AD6657A (at clock rates of up to 625 MHz). A low jitter clock source is converted from a single-ended signal to a differential signal using either an RF balun or an RF transformer.

The RF balun configuration is recommended for clock frequencies between 125 MHz and 625 MHz, and the RF transformer configuration is recommended for clock frequencies from 10 MHz to 200 MHz. The back-to-back Schottky diodes across the transformer/balun secondary limit clock excursions into the AD6657A to approximately 0.8 V p-p differential. This limit helps to prevent the large voltage swings of the clock from feeding through to other portions of the AD6657A, yet preserves the fast rise and fall times of the signal that are critical to a low jitter performance.

Figure 43. Transformer-Coupled Differential Clock (Up to 200 MHz)

Figure 44. Balun-Coupled Differential Clock (Up to 625 MHz)

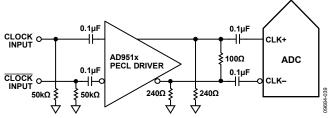

If a low jitter clock source is not available, another option is to ac couple a differential PECL signal to the sample clock input pins, as shown in Figure 45. The AD9510/AD9511/AD9512/AD9513/AD9514/AD9515/AD9516 clock drivers offer excellent jitter performance.

Figure 45. Differential PECL Sample Clock (Up to 625 MHz)

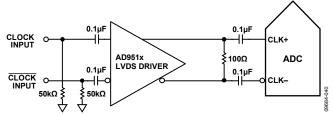

A third option is to ac couple a differential LVDS signal to the sample clock input pins, as shown in Figure 46. The AD9510/AD9511/AD9512/AD9513/AD9514/AD9515/AD9516 clock drivers offer excellent jitter performance.

Figure 46. Differential LVDS Sample Clock (Up to 625 MHz)

In some applications, it may be acceptable to drive the sample clock inputs with a single-ended CMOS signal. In such applications, drive the CLK+ pin directly from a CMOS gate, and bypass the CLK– pin to ground with a 0.1  $\mu F$  capacitor in parallel with a 39  $k\Omega$  resistor (see Figure 47).

Figure 47. Single-Ended 1.8 V CMOS Input Clock (Up to 200 MHz)

CLK+ can be driven directly from a CMOS gate. Although the CLK+ input circuit supply is AVDD (1.8 V), this input is designed to withstand input voltages of up to 3.6 V, making the selection of the drive logic voltage very flexible (see Figure 48).

Figure 48. Single-Ended 3.3 V CMOS Input Clock (Up to 200 MHz)

# **Input Clock Divider**

The AD6657A contains an input clock divider with the ability to divide the input clock by integer values from 1 to 8.

The AD6657A clock divider can be synchronized using the external SYNC input. Bit 1 of Register 0x3A enables the clock divider to be resynchronized on every SYNC signal. A valid SYNC causes the clock divider to reset to its initial state. This synchronization feature allows multiple parts to have their clock dividers aligned to guarantee simultaneous input sampling.

# **Clock Duty Cycle**

Typical high speed ADCs use both clock edges to generate a variety of internal timing signals and, as a result, may be sensitive to clock duty cycle. Commonly, a  $\pm 5\%$  tolerance is required on the clock duty cycle to maintain dynamic performance characteristics.

The AD6657A contains a DCS that retimes the nonsampling (falling) edge, providing an internal clock signal with a nominal 50% duty cycle. This allows the user to provide a wide range of clock input duty cycles without affecting the performance of the AD6657A. Noise and distortion performance are nearly flat for a wide range of duty cycles with the DCS enabled.

Jitter in the rising edge of the input is of paramount concern and is not easily reduced by the internal stabilization circuit. The duty cycle control loop does not function for clock rates at less than 40 MHz nominally. The loop has a time constant associated with it that must be considered in applications in which the clock rate can change dynamically. A wait time of 1.5  $\mu s$  to 5  $\mu s$  is required after a dynamic clock frequency increase or decrease before the DCS loop is relocked to the input signal. During the time period that the loop is not locked, the DCS loop is bypassed, and internal device timing is dependent on the duty cycle of the input clock signal.

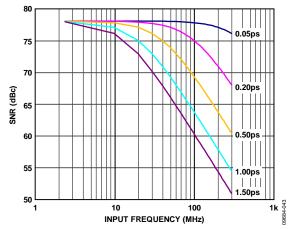

#### **Jitter Considerations**

High speed, high resolution ADCs are sensitive to the quality of the clock input. The degradation in SNR from the low frequency SNR (SNR<sub>LF</sub>) at a given input frequency ( $f_{\rm IN}$ ) due to jitter ( $t_{\rm JRMS}$ ) can be calculated by

$$SNR_{HF} = -10\log[(2\pi \times f_{IN} \times t_{JRMS})^2 + 10^{(-SNR_{LF}/10)}]$$

In the equation, the rms aperture jitter represents the clock input jitter specification. IF undersampling applications are particularly sensitive to jitter, as shown in Figure 49.

Figure 49. SNR vs. Input Frequency and Jitter

In cases where aperture jitter may affect the dynamic range of the AD6657A, treat the clock input as an analog signal. Separate power supplies for clock drivers should be separated from the ADC output driver supplies to avoid modulating the clock signal with digital noise. Low jitter, crystal controlled oscillators make the best clock sources. If the clock is generated from another type of source (by gating, dividing, or another method), it should be retimed by the original clock at the last step. Refer to the AN-501 Application Note and AN-756 Application Note for more information about jitter performance as it relates to ADCs (available at www.analog.com).

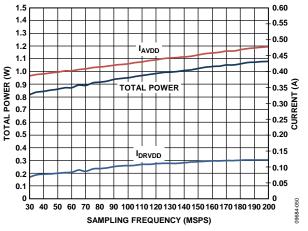

#### POWER DISSIPATION AND STANDBY MODE

The power dissipated by the AD6657A is proportional to its clock rate (see Figure 50). The digital power dissipation does not vary significantly because it is determined primarily by the DRVDD supply and the bias current of the LVDS drivers.

Reducing the capacitive load presented to the output drivers can minimize digital power consumption. The data in Figure 50 was obtained using the same operating conditions as those used in the Typical Performance Characteristics section, with a 5 pF load on each output driver.

Figure 50. Power and Current vs. Sampling Frequency

By asserting PDWN (either through the SPI port or by asserting the PDWN pin high), the AD6657A is placed in power-down mode. In this state, the ADC typically dissipates 4.5 mW. During power-down, the output drivers are placed in a high impedance state. Asserting the PDWN pin low returns the AD6657A to its normal operating mode. Note that PDWN is referenced to the digital output driver supply (DRVDD) and should not exceed that supply voltage.

Low power dissipation in power-down mode is achieved by shutting down the reference, reference buffer, biasing networks, and clock. Internal capacitors are discharged when entering power-down mode and must be recharged when returning to normal operation. As a result, wake-up time is related to the time spent in power-down mode; shorter power-down cycles result in proportionally shorter wake-up times.

When using the SPI port interface, the user can place the ADC in power-down mode or standby mode. Standby mode allows the user to keep the internal reference circuitry powered when faster wake-up times are required. See the Memory Map Register Descriptions section for more details.

# **CHANNEL/CHIP SYNCHRONIZATION**

The AD6657A has a SYNC input that offers the user flexible synchronization options for synchronizing the clock divider. The clock divider sync feature is useful for guaranteeing synchronized sample clocks across multiple ADCs.

The SYNC input is internally synchronized to the sample clock; however, to ensure that there is no timing uncertainty between multiple parts, externally synchronize the SYNC input signal to the input clock signal, meeting the setup and hold times shown in Table 5. Drive the SYNC input using a single-ended CMOS type signal.

#### **DIGITAL OUTPUTS**

The AD6657A output drivers are configured to interface with LVDS outputs using a DRVDD supply voltage of 1.8 V. The output bits are DDR LVDS as shown in Figure 2. Applications that require the ADC to drive large capacitive loads or large fanouts may require external buffers or latches.

As described in the AN-877 Application Note, *Interfacing to High Speed ADCs via SPI*, the data format can be selected for offset binary or twos complement when using the SPI control.

# **TIMING**

The AD6657A provides latched data with a latency of nine clock cycles. Data outputs are available one propagation delay (tpd) after the rising edge of the clock signal.

Minimize the length of the output data lines and minimize the loads placed on them to reduce transients within the AD6657A because these transients can degrade converter dynamic performance.

The lowest typical conversion rate of the AD6657A is 40 MSPS. At clock rates below 40 MSPS, dynamic performance can degrade.

# Data Clock Output (DCO)

The AD6657A provides a data clock output (DCO) signal intended for capturing the data in an external register. The output data for Channel A and Channel C is valid when DCO is high; the output data for Channel B and Channel D is valid when DCO is low (see Figure 2).

**Table 11. Output Data Format**

| Input (V)   | Condition (V)                 | Offset Binary Output Mode | Twos Complement Mode |

|-------------|-------------------------------|---------------------------|----------------------|

| VIN+ – VIN– | < -V <sub>REF</sub> - 0.5 LSB | 000 0000 0000             | 100 0000 0000        |

| VIN+ - VIN- | $=-V_{REF}$                   | 000 0000 0000             | 100 0000 0000        |

| VIN+ - VIN- | = 0                           | 100 0000 0000             | 000 0000 0000        |

| VIN+ - VIN- | $= +V_{REF} - 1.0 LSB$        | 111 1111 1111             | 011 1111 1111        |

| VIN+-VIN-   | > +V <sub>REF</sub> - 0.5 LSB | 111 1111 1111             | 011 1111 1111        |

# **NOISE SHAPING REQUANTIZER**

The AD6657A features a noise shaping requantizer (NSR) to allow higher than an 11-bit SNR to be maintained in a subset of the Nyquist band. The harmonic performance of the receiver is unaffected by the NSR feature.

When enabled, the NSR contributes an additional 0.6 dB of loss to the input signal, such that a 0 dBFS input is reduced to -0.6 dBFS at the output pins.

The NSR feature can be independently controlled per channel via the SPI or via the MODE pin.

Two different bandwidth modes are provided; the mode can be selected from the SPI port. In each of the two modes, the center frequency of the band can be tuned such that IFs can be placed anywhere in the Nyquist band.

# 22% BW MODE (>40 MHz at 184.32 MSPS)

The first bandwidth mode offers excellent noise performance over 22% of the ADC sample rate (44% of the Nyquist band) and can be centered by setting the NSR mode bits in the NSR control register (Address 0x3C) to 000. In this mode, the useful frequency range can be set using the 6-bit tuning word in the NSR tuning word register (Address 0x3E).

There are 57 possible tuning words (TW); each step is 0.5% of the ADC sample rate. The following three equations describe the left band edge ( $f_0$ ), the channel center ( $f_{CENTER}$ ), and the right band edge ( $f_1$ ), respectively.

$$f_0 = f_{ADC} \times .005 \times TW$$

$$f_{CENTER} = f_0 + 0.11 \times f_{ADC}$$

$$f_1 = f_0 + 0.22 \times f_{ADC}$$

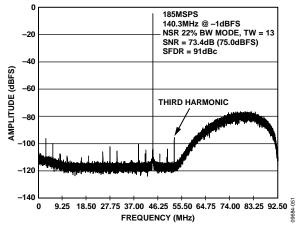

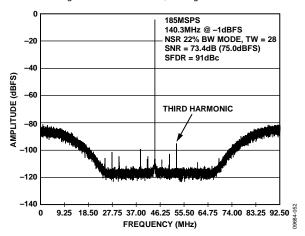

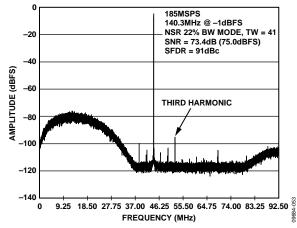

Figure 51 to Figure 53 show the typical spectrum that can be expected from the AD6657A in the 22% BW mode for three different tuning words.

Figure 51. 22% BW Mode, Tuning Word = 13

Figure 52. 22% BW Mode, Tuning Word = 28 (f<sub>s</sub>/4 Tuning)

Figure 53. 22% BW Mode, Tuning Word = 41

# 33% BW MODE (>60 MHz AT 184.32 MSPS)

The second bandwidth mode offers excellent noise performance over 33% of the ADC sample rate (66% of the Nyquist band) and can be centered by setting the NSR mode bits in the NSR control register (Address 0x3C) to 001. In this mode, the useful frequency range can be set using the 6-bit tuning word in the NSR tuning word register (Address 0x3E).

There are 34 possible tuning words (TW); each step is 0.5% of the ADC sample rate. The following three equations describe the left band edge ( $f_0$ ), the channel center ( $f_{\text{CENTER}}$ ), and the right band edge ( $f_1$ ), respectively.

$$f_0 = f_{ADC} \times .005 \times TW$$

$$f_{CENTER} = f_0 + 0.165 \times f_{ADC}$$

$$f_1 = f_0 + 0.33 \times f_{ADC}$$

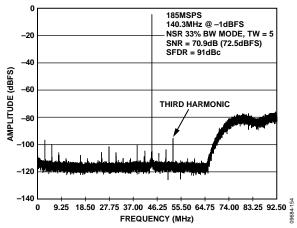

Figure 54 to Figure 56 show the typical spectrum that can be expected from the AD6657A in the 33% BW mode for three different tuning words.

Figure 54. 33% BW Mode, Tuning Word = 5

Figure 55. 33% BW Mode, Tuning Word = 17 ( $f_s$ /4 Tuning)

Figure 56. 33% BW Mode, Tuning Word = 17

# 36% BW MODE (>65 MHz AT 184.32 MSPS)

The third bandwidth mode offers excellent noise performance over 36% of the ADC sample rate (72% of the Nyquist band) and can be centered by setting the NSR mode bits in the NSR control register (Address 0x3C) to 010. In this mode, the useful frequency range can be set using the 6-bit tuning word in the NSR tuning register (Address 0x3E).

There are 28 possible tuning words (TW); each step is 0.5% of the ADC sample rate. The following three equations describe the left band edge ( $f_0$ ), the channel center ( $f_{\text{CENTER}}$ ), and the right band edge ( $f_1$ ), respectively.

$$f_0 = f_{ADC} \times .005 \times TW$$

$$f_{CENTER} = f_0 + 0.18 \times f_{ADC}$$

$$f_1 = f_0 + 0.36 \times f_{ADC}$$

Figure 57 to Figure 59 show the typical spectrum that can be expected from the AD6657A in the 36% BW mode for three different tuning words.

Figure 57. 36% BW Mode, Tuning Word = 0

Figure 58. 36% BW Mode, Tuning Word = 14 ( $f_s$ /4 Tuning)

Figure 59. 36% BW Mode, Tuning Word = 28

#### **MODE PIN**

The MODE pin input allows convenient control of the NSR feature. A logic low enables NSR mode and a logic high sets the receiver to a straight 11-bit mode with NSR disabled. By default, the MODE pin is pulled high internally to disable the NSR.

Each channel can be individually configured to ignore the MODE pin state by writing to Bit 4 of the NSR control register at Address 0x3C. Use of the NSR control register in conjunction with the MODE pin allows for very flexible control of the NSR feature on a per channel basis.

# BUILT-IN SELF TEST (BIST) AND OUTPUT TEST

The AD6657A includes built-in test features designed to verify the integrity of each channel and to facilitate board-level debugging. A built-in self test (BIST) feature is included that verifies the integrity of the digital datapath of the AD6657A. Various output test options are also provided to place predictable values on the outputs of the AD6657A.

# **BIST**

The BIST is a thorough test of the digital portion of the selected AD6657A signal path. When enabled, the test runs from an internal pseudorandom noise (PN) source through the digital datapath starting at the ADC block output. The BIST sequence runs for 512 cycles and stops. The BIST signature value for the selected channel is written to Register 0x24 and Register 0x25.

If more than one channel is BIST enabled, the channel that is first according to alphabetical order is written to the BIST signature registers. For example, if Channel B and Channel C are BIST enabled, the results from Channel B are written to the BIST signature registers.

The outputs are not disconnected during this test, so the PN sequence can be observed as it runs. The PN sequence can be continued from its last value or reset from the beginning, based on the value programmed in Register 0x0E, Bit 2. The BIST signature result varies based on the channel configuration.

# **OUTPUT TEST MODES**

The output test options are shown in Table 13. When an output test mode is enabled, the analog section of the receiver is disconnected from the digital back-end blocks, and the test pattern is run through the output formatting block. Some of the test patterns are subject to output formatting. The seed value for the PN sequence tests can be forced if the PN reset bits are used to hold the generator in reset mode by setting Bit 4 or Bit 5 of Register 0x0D. These tests can be performed with or without an analog signal (if present, the analog signal is ignored), but they require an encode clock. For more information, see the AN-877 Application Note, *Interfacing to High Speed ADCs via SPI*.

# **SERIAL PORT INTERFACE (SPI)**

The AD6657A serial port interface (SPI) allows the user to configure the receiver for specific functions or operations through a structured internal register space. The SPI provides added flexibility and customization, depending on the application. Addresses are accessed via the serial port and can be written to or read from via the port. Memory is organized into bytes that can be further divided into fields, which are documented in the Memory Map section. For detailed operational information, see the AN-877 Application Note, *Interfacing to High Speed ADCs via SPI*.

# **CONFIGURATION USING THE SPI**

Three pins define the SPI of the AD6657A: SCLK, SDIO, and CSB (see Table 12). SCLK (a serial clock) is used to synchronize the read and write data presented from and to the AD6657A. SDIO (serial data input/output) is a bidirectional pin that allows data to be sent to and read from the internal memory map registers. CSB (chip select bar) is an active low control that enables or disables the read and write cycles.

**Table 12. Serial Port Interface Pins**

| Pin  | Function                                                                                                                                                                 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK | Serial clock. Serial shift clock input. SCLK is used to synchronize serial interface reads and writes.                                                                   |

| SDIO | Serial data input/output. Bidirectional pin that serves as an input or an output, depending on the instruction being sent and the relative position in the timing frame. |

| CSB  | Chip select bar (active low). This control gates the read and write cycles.                                                                                              |

The falling edge of the CSB pin, in conjunction with the rising edge of the SCLK pin, determines the start of the framing. An example of the serial timing can be found in Figure 60 (for symbol definitions, see Table 5).

CSB can be held low indefinitely, which permanently enables the device; this is called streaming. CSB can stall high between bytes to allow for additional external timing. When CSB is tied high, SPI functions are placed in high impedance mode.