### **Bridge Driver IC**

### **Features**

- High Power 3 Phase Bridge Driver for low RDSON N-channel FETs

- 0...100% duty cycle, adjustable without restrictions

- Specified supply voltage range of 5.5 V to 60 V

- Logic operation down to 3 V supply voltage

- High robustness of motor connection pins of -15 V to 90 V

- Extended protection and supervision functionality

- Serial Peripheral Interface (SPI), control of supervision

- Supervision read out by SPI

- Reverse diode measurement of external FET for temperature detection

- Limp-home functionality of diagnostic and failure behavior with SPI configurable content

- 3 current sense amplifiers for shunt signal conditioning

- 2 switch off paths by pins ENA and SOFF

- Low quiescent current mode by pin INH

- Compatible to 3.3 V μCs and TTL logic

- Phase voltage feedback with SPI programmable voltage thresholds

- Output for phase cut off circuit activation

- Green Product (RoHS compliant)

- AEC Qualified

### PRO-SIL<sup>™</sup> features

- Safety Manual and Safety Analysis Summary Report up to  $V_{VS} \le 28 \text{ V}$  and  $V_{VDHP}$ ,  $V_{VDHX} \le 28 \text{ V}$  available

- Safety Barrier to  $\mu$ C interface up to  $V_{VS} \le 28$  V and  $V_{VDHP}$ ,  $V_{VDHx} \le 28$  V

- · High voltage rated digital input and output pins

- Fast and functional independent disable functionality via pin SOFF

- Functional redundant disable paths via pin SOFF and ENA

- Monitoring of system relevant voltages and dedicated self-test functionality

- Secure SPI interface with CRC check over data and address

- Integrated window watchdog for μC supervision

- · Functional independent current sense amplifier

- Functional independent phase feedback with SPI programmable threshold

- Passive clamping of external FETs

### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

### **Description**

## **Description**

The TLE9180D-31QK is an advanced gate driver IC dedicated to control 6 external N-channel MOSFETs forming an inverter for high current 3 phase motor drives application in the automotive sector.

A sophisticated high voltage technology allows the TLE9180D-31QK to support applications for single and mixed battery systems with battery voltages of 12 V, 24 V and 48 V even within tough automotive environments in combination with high motor currents. Therefore bridge, motor and supply related pins can withstand voltages of up to 90 V. Motor related pins can even withstand negative voltage transients down to - 15 V without damage.

All low- and high-side output stages are based on a floating concept and its driver strength allows to drive lowest RDSON MOSFETs common on the market.

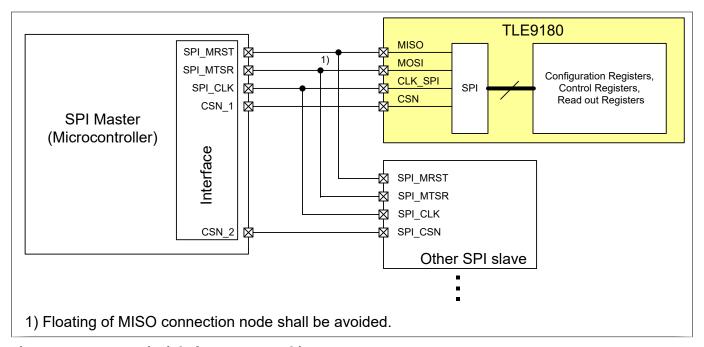

An integrated SPI interface is used to configure the TLE9180D-31QK for the application after power-up. After successful power-up parameters can be adjusted by SPI, monitoring data, configuration and error registers can be read. Cyclic redundancy check over data and address bits ensures safe communication and data integrity.

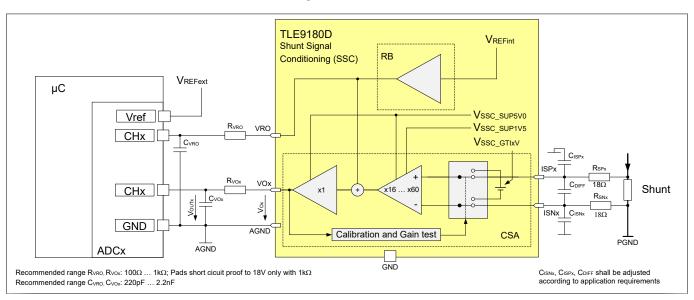

GND related bridge currents can be measured with 3 integrated current sense amplifiers. The outputs of the current sense amplifiers support 5 V ADCs and the robust inputs can withstand negative transients down to -10 V without damage. Gain and zero current voltage offset can be adjusted by SPI. The offset can be calibrated.

Diagnostic coverage and redundancy have increased steadily in recent years in automotive drive applications. Therefore the TLE9180D-31QK offers a wide range of diagnostic features, like monitoring of power supply voltages as well as system parameters. A testability of safety relevant supervision functions has been integrated. Failure behavior, threshold voltages and filter times of the supervisions of the device are adjustable via SPI.

The TLE9180D-31QK is integrated in a LQFP64 package with an exposed pad. Due to its exposed pad the gate driver IC provides an excellent thermal characteristic.

Table 1 Device Marking

| Product Type  | Package | Marking       |  |

|---------------|---------|---------------|--|

| TLE9180D-31QK | LQFP-64 | TLE9180D-31QK |  |

## **Bridge Driver IC**

### **Table of contents**

|     | Features                                               | 1  |

|-----|--------------------------------------------------------|----|

|     | Product validation                                     | 1  |

|     | Description                                            | 2  |

|     | Table of contents                                      | 3  |

| 1   | Block Diagram                                          | 10 |

| 2   | Pin Configuration                                      | 11 |

| 2.1 | Pin Assignment                                         | 11 |

| 2.2 | Pin Definitions and Functions                          | 11 |

| 3   | General Product Characteristics                        | 18 |

| 3.1 | Absolute Maximum Ratings                               | 18 |

| 3.2 | Thermal Resistance                                     | 22 |

| 3.3 | Functional Range                                       | 23 |

| 3.4 | Typical Behavior Figures                               | 25 |

| 4   | Input and Output Characteristics                       | 26 |

| 4.1 | Digital Inputs                                         | 26 |

| 4.2 | General Inputs                                         | 27 |

| 4.3 | VCC - I/O Supply and μC Supply Monitoring              | 27 |

| 4.4 | Digital Outputs                                        | 27 |

| 4.5 | General Output                                         | 28 |

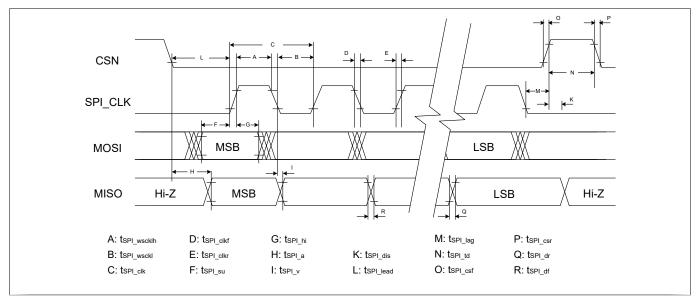

| 4.6 | SPI Interface                                          |    |

| 4.7 | Electrical Characteristics IOs                         | 28 |

| 5   | Serial Peripheral Interface - SPI                      | 33 |

| 5.1 | IO-Buffer                                              | 33 |

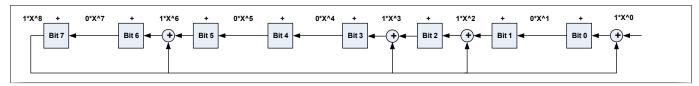

| 5.2 | Shift Registers                                        | 33 |

| 5.3 | Address and Command Decoder                            | 33 |

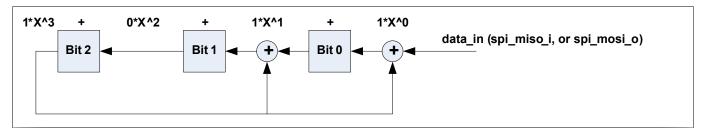

| 5.4 | Cyclic Redundancy Check - CRC Generation and Detection |    |

| 5.5 | Electrical Characteristics SPI                         | 34 |

| 6   | Clock                                                  | 36 |

| 6.1 | Clock Programming                                      |    |

| 6.2 | Electrical Characteristics Clock                       | 36 |

| 7   | Power Supply                                           | 37 |

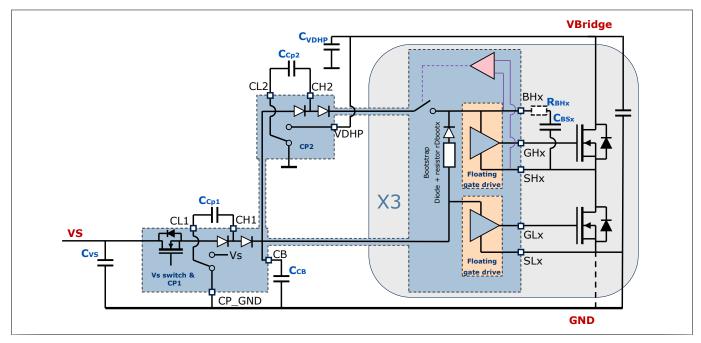

| 7.1 | Output Stage Supply Concept                            |    |

| 7.2 | Internal Supply Voltages                               |    |

| 7.3 | Electrical Characteristics Power Supply                |    |

| 7.4 | Typical Behavior Figures                               | 44 |

| Q   | Floating MOSEFT Driver                                 | 46 |

## Bridge Driver IC

| 8.1      | Driver Output Stage                                                                 | 46 |

|----------|-------------------------------------------------------------------------------------|----|

| 8.2      | Input to Output Information                                                         | 46 |

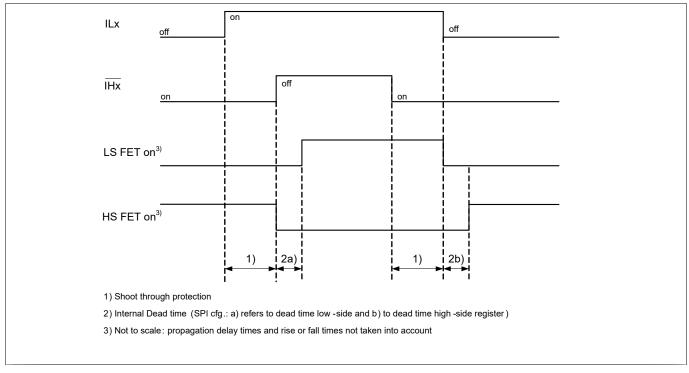

| 8.3      | Shoot Through Protection and Dead Time Generation                                   | 46 |

| 8.4      | Electrical Characteristics Floating MOSFET Driver                                   | 47 |

| 8.5      | Typical Timings and Behavior Figures                                                | 50 |

| 9        | Shunt Signal Conditioning                                                           | 51 |

| 9.1      | Gain Programming                                                                    | 51 |

| 9.2      | Setting VRO Voltage and VOx Voltage for Zero SSC Differential Input Voltage         | 52 |

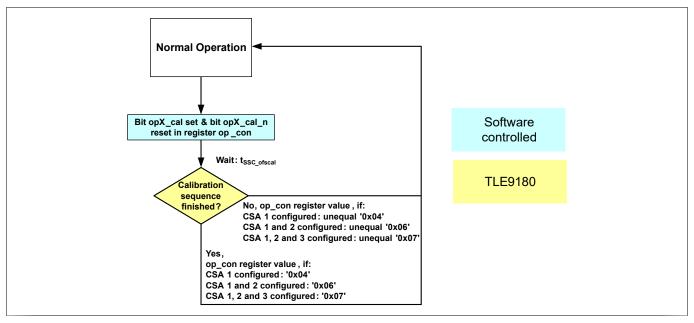

| 9.3      | Auto Calibration                                                                    | 52 |

| 9.4      | Overcurrent Detection                                                               | 53 |

| 9.5      | Self-tests of Shunt Signal Conditioning                                             | 53 |

| 9.5.1    | Gain Test                                                                           | 54 |

| 9.5.2    | Power Supply Monitoring of SSC                                                      | 54 |

| 9.6      | Electrical Parameter Shunt Signal Conditioning (SSC)                                | 54 |

| 10       | Protection and Diagnostics                                                          | 60 |

| 10.1     | Supervision Overview                                                                | 60 |

| 10.1.1   | Diagnosis in Configuration Mode                                                     | 63 |

| 10.1.2   | Disabled Functions in Reduced Operation Mode                                        | 63 |

| 10.1.3   | Disabled Functions in Safe Off Mode                                                 | 63 |

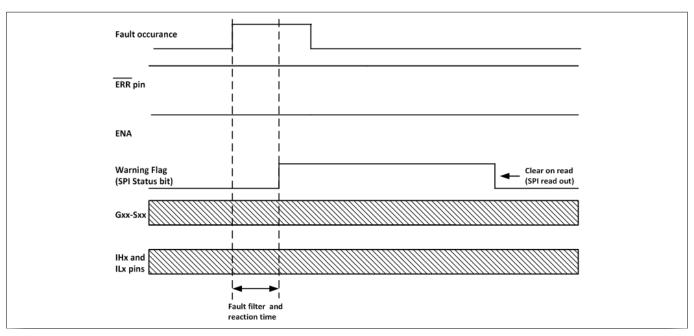

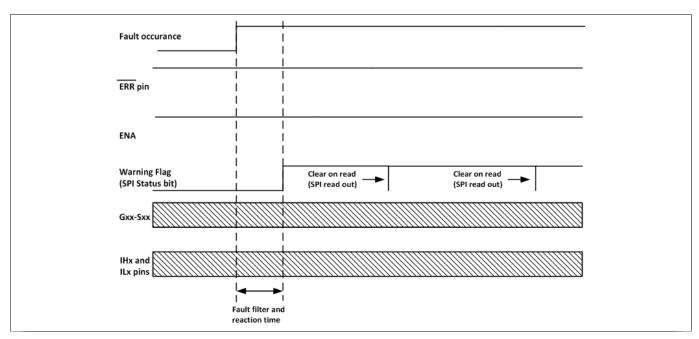

| 10.2     | Failure Detection Handling                                                          | 63 |

| 10.2.1   | Failure Flags                                                                       | 63 |

| 10.2.2   | Failure Behavior Configuration                                                      | 64 |

| 10.2.3   | Parallel Failure Occurrence                                                         | 66 |

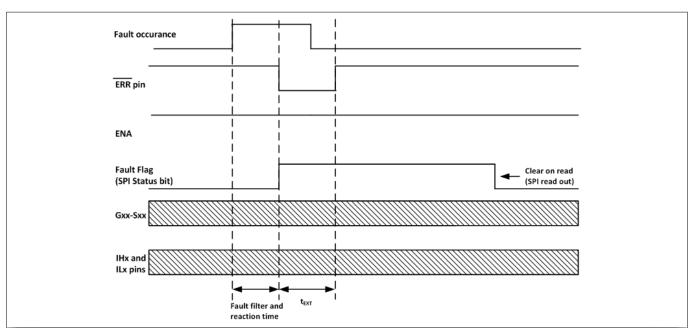

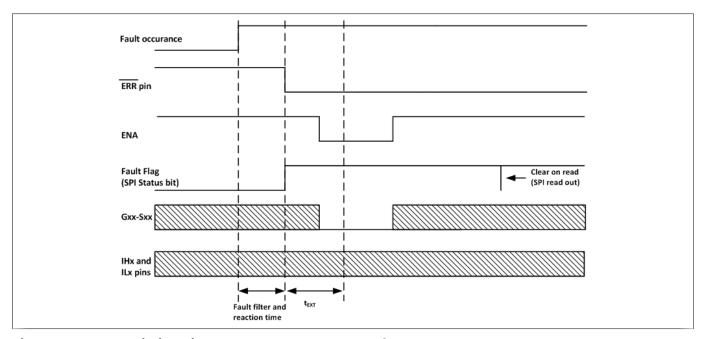

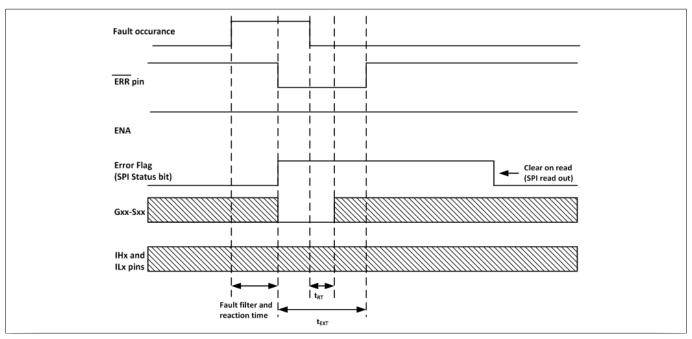

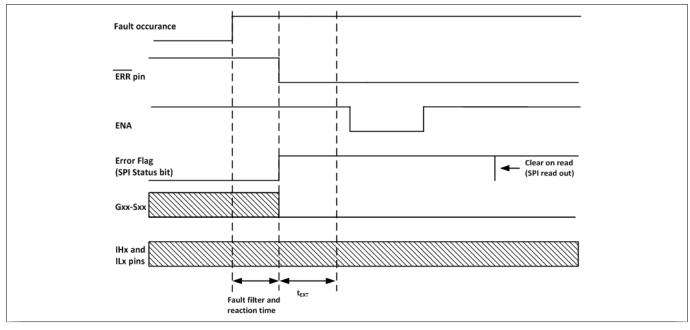

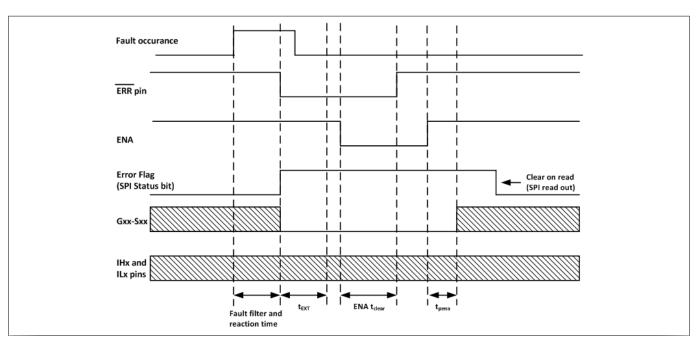

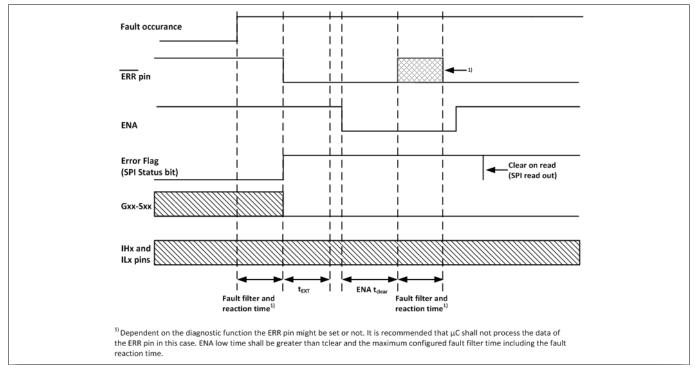

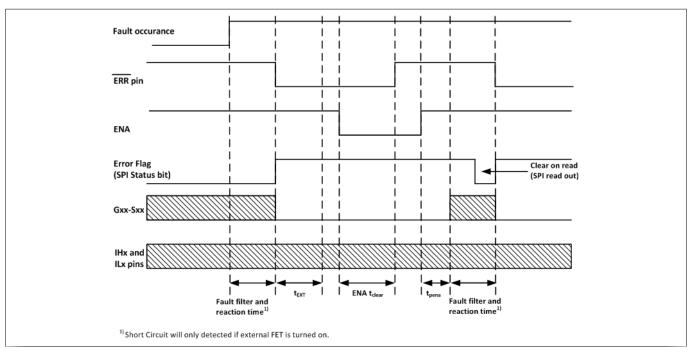

| 10.2.4   | General Failure Behavior Timing Diagrams                                            | 66 |

| 10.3     | Diagnostic Test Functions                                                           | 71 |

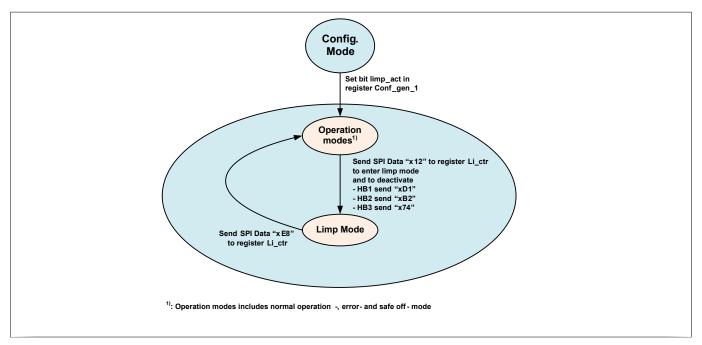

| 10.4     | LIMP Functionality                                                                  | 72 |

| 10.5     | Detailed Supervision Description                                                    | 73 |

| 10.5.1   | Vs Voltage Monitoring                                                               | 73 |

| 10.5.1.1 | SPI Register Reference for VS Supervision                                           | 73 |

| 10.5.2   | VDHP Voltage Monitoring                                                             | 74 |

| 10.5.2.1 | SPI Register Reference for VDHP Supervision                                         | 74 |

| 10.5.2.2 | VDHP Overvoltage Detection LD                                                       | 75 |

| 10.5.3   | Charge Pump Monitoring                                                              | 75 |

| 10.5.3.1 | SPI Register Reference for CB Undervoltage Supervision                              | 76 |

| 10.5.3.2 | Overload and Overvoltage of Charge Pumps                                            | 76 |

| 10.5.4   | High-side Buffer Capacitor Voltage Monitoring                                       | 77 |

| 10.5.4.1 | Overvoltage Detection of High-side Buffer Capacitor at High Negative Voltage at the |    |

|          | Pins SHx                                                                            | 77 |

| 10.5.4.2 | SPI Register Reference for High-side Buffer Capacitor UV Monitoring                 | 77 |

| 10.5.5   | VCC Monitoring                                                                      |    |

| 10.5.5.1 | SPI Register Reference for VCC Supervision                                          | 78 |

## Bridge Driver IC

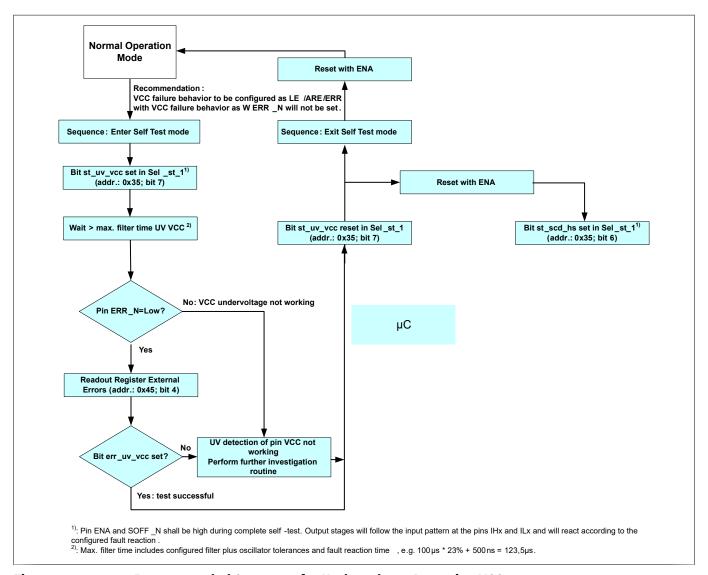

| 10.5.5.2    | Self-test Function for VCC                                     | 78  |

|-------------|----------------------------------------------------------------|-----|

| 10.5.6      | Internal Power Supply Monitoring                               | 79  |

| 10.5.7      | Internal CLK Supervision                                       | 79  |

| 10.5.8      | Temperature Detection and Shutdown                             | 80  |

| 10.5.8.1    | SPI Register Reference for Overtemperature Detection           | 80  |

| 10.5.8.2    | Temperature Read Out                                           | 80  |

| 10.5.9      | Output Stage Status Feedback                                   | 80  |

| 10.5.10     | Digital Driving Path Monitoring                                | 80  |

| 10.5.11     | Short Circuit Detection - SCD                                  | 81  |

| 10.5.11.1   | SPI Register Reference for SCD Voltage Threshold               | 81  |

| 10.5.11.2   | Self-test Function for SCD                                     | 82  |

| 10.5.12     | FET Drain Source Voltage Read Out                              | 85  |

| 10.5.13     | FET Reverse Diode Forward Voltage Read Out                     | 85  |

| 10.5.14     | Drain Source Voltage Measurement of External FETs              | 86  |

| 10.5.15     | Input Pattern Violation Monitoring                             | 86  |

| 10.5.16     | Overload Digital Output Pins                                   | 86  |

| 10.5.17     | Configuration Errors                                           | 86  |

| 10.5.17.1   | Configuration Signature Invalid                                | 86  |

| 10.5.17.2   | Configuration Time-out                                         | 87  |

| 10.5.18     | Control Register Error Monitoring                              | 87  |

| 10.5.19     | State Machine Error Monitoring                                 | 87  |

| 10.5.20     | SPI Communication Errors                                       | 87  |

| 10.5.20.1   | SPI Frame Error                                                | 88  |

| 10.5.20.2   | SPI Frame Time-out                                             | 88  |

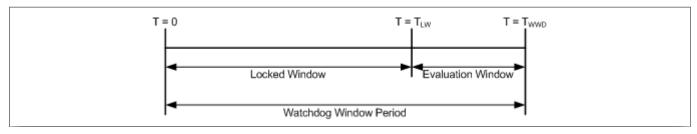

| 10.5.20.3   | SPI Window Watchdog                                            | 88  |

| 10.5.20.3.1 | SPI Register Reference for Window Watchdog                     | 89  |

| 10.5.20.4   | CRC Error                                                      | 90  |

| 10.5.20.5   | Invalid Address Access Monitoring                              | 90  |

| 10.6        | Electrical Characteristics Protection and Diagnostic Functions | 90  |

| 11          | Digital Phase Voltage Feedback                                 | 100 |

| 11.1        | Phase Voltage Feedback Programming                             | 100 |

| 11.2        | Electrical Parameter Phase Feedback                            | 100 |

| 12          | Phase Cut Off Activation                                       | 102 |

| 12.1        | Phase Cut Off Programming                                      | 102 |

| 12.2        | Electrical Parameter Activation Phase Cut Off                  | 103 |

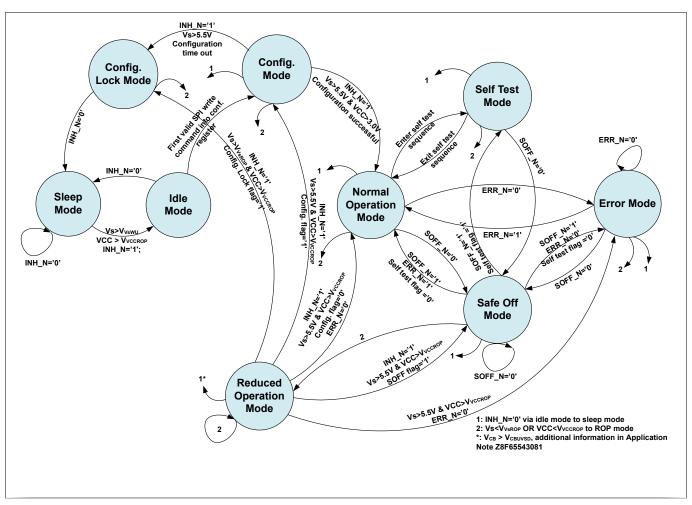

| 13          | Operation Modes                                                | 104 |

| 13.1        | Normal Operation Mode                                          | 104 |

| 13.1.1      | Driving Mode                                                   | 104 |

| 13.1.2      | Limp Mode                                                      | 104 |

| 13.2        | Reduced Operation Mode                                         | 105 |

| 13.3        | Sleep Mode                                                     | 105 |

## Bridge Driver IC

| 13.4      | Idle Mode                                                       | 105 |

|-----------|-----------------------------------------------------------------|-----|

| 13.5      | Configuration Mode                                              | 106 |

| 13.6      | Configuration Lock Mode                                         | 106 |

| 13.7      | Safe-Off Mode                                                   | 106 |

| 13.8      | Error Mode                                                      | 106 |

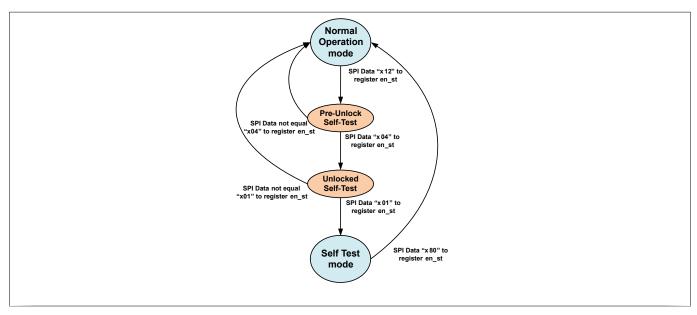

| 13.9      | Self-test Mode                                                  | 106 |

| 13.10     | Overview of Operation Modes and Transition States               | 107 |

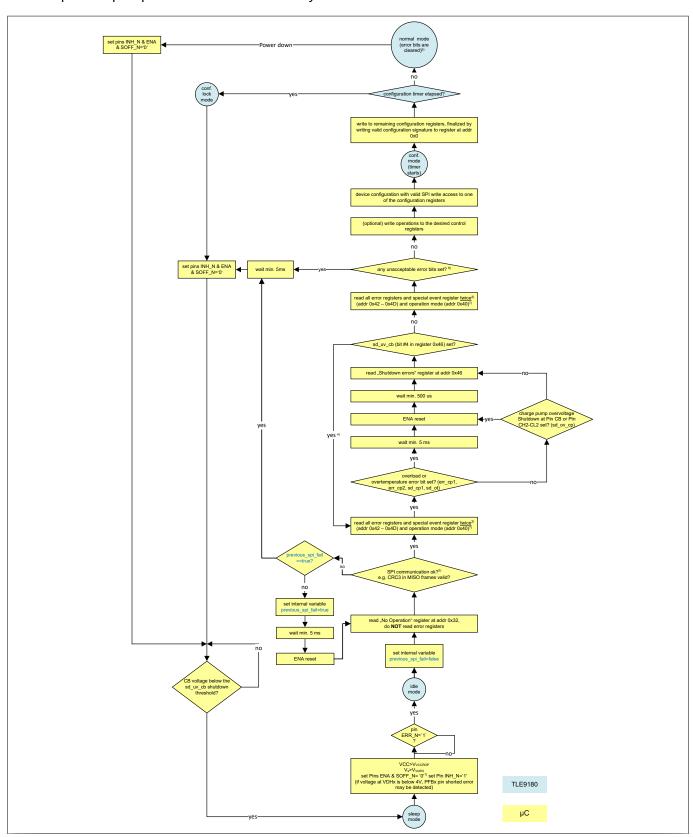

| 13.11     | Power-up Diagram                                                | 109 |

| 14        | Register Description                                            | 111 |

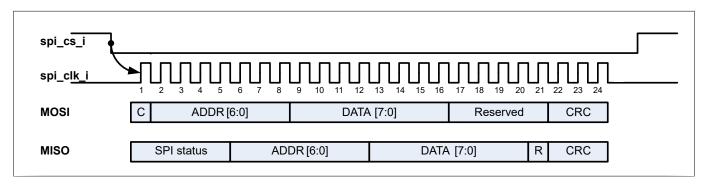

| 14.1      | SPI Data Flow                                                   | 111 |

| 14.2      | SPI Frame Format                                                | 111 |

| 14.2.1    | SPI Status Flags                                                | 111 |

| 14.3      | SPI Supervision Overview                                        | 112 |

| 14.3.1    | Overview of SPI Communication and Configuration Errors          | 112 |

| 14.3.2    | Overview of Special Event Register                              | 112 |

| 14.3.3    | Reserved Registers, Bits and Values                             | 113 |

| 14.3.4    | Overview of Register Types                                      | 113 |

| 15        | Register Specification                                          | 115 |

| 15.1      | Registers Chapter                                               | 115 |

| 15.1.1    | Configuration registers                                         | 118 |

| 15.1.1.1  | Configuration Signature                                         | 118 |

| 15.1.1.2  | General Configuration 1                                         | 119 |

| 15.1.1.3  | General Configuration 2                                         | 120 |

| 15.1.1.4  | General Configuration 3                                         | 121 |

| 15.1.1.5  | Window Watchdog                                                 | 122 |

| 15.1.1.6  | Vs Over- and Undervoltage Thresholds                            | 123 |

| 15.1.1.7  | VDHP Over- and Undervoltage Thresholds                          | 124 |

| 15.1.1.8  | CB Under- and VCC Under- and Overvoltage Thresholds             | 125 |

| 15.1.1.9  | Charge Pump/High-side Buffer Failure Modes                      | 126 |

| 15.1.1.10 | Miscellaneous Failure Modes                                     | 127 |

| 15.1.1.11 | Vs & VDHP & VCC Undervoltage Failure Modes                      | 128 |

| 15.1.1.12 | Vs & VDHP & VCC Overvoltage Failure Modes                       | 129 |

| 15.1.1.13 | Short Circuit Detection & Signal Path Supervision Failure Modes | 130 |

| 15.1.1.14 | Dead Time High-side                                             | 131 |

| 15.1.1.15 | Dead Time Low-side                                              | 132 |

| 15.1.1.16 | Undervoltage Filter Times                                       | 133 |

| 15.1.1.17 | Overvoltage and VCC Filter Times                                | 134 |

| 15.1.1.18 | Overtemperature & Short Circuit Detection Filter Times          | 135 |

| 15.1.1.19 | Overcurrent Filter Time                                         | 136 |

| 15.1.1.20 | Overcurrent Failure Modes                                       | 137 |

| 15.1.2    | Control registers                                               | 138 |

## Bridge Driver IC

| 15.1.2.1  | Current Sense Amplifier 1&2 - Gain 1              | 138 |

|-----------|---------------------------------------------------|-----|

| 15.1.2.2  | Current Sense Amplifier 1&2 - Gain 2              | 139 |

| 15.1.2.3  | Current Sense Amplifier 3 - Gain 1&2              | 140 |

| 15.1.2.4  | Current Sense Amplifier Zero Current Offset       | 141 |

| 15.1.2.5  | Current Sense Amplifier Configuration             |     |

| 15.1.2.6  | Short Circuit Detection Threshold Low-side 1      |     |

| 15.1.2.7  | Short Circuit Detection Threshold Low-side 2      | 144 |

| 15.1.2.8  | Short Circuit Detection Threshold Low-side 3      |     |

| 15.1.2.9  | Short Circuit Detection Threshold High-side 1     | 146 |

| 15.1.2.10 | Short Circuit Detection Threshold High-side 2     | 147 |

| 15.1.2.11 | Short Circuit Detection Threshold High-side 3     | 148 |

| 15.1.2.12 | Limp Home Activation and Half Bridge Deactivation | 149 |

| 15.1.2.13 | Shift Phase Voltage Feedback and CSA Gain         | 150 |

| 15.1.2.14 | Passive Rectification Threshold                   | 151 |

| 15.1.2.15 | Active Rectification Threshold                    | 152 |

| 15.1.2.16 | Rectification Filter Time                         | 153 |

| 15.1.2.17 | Rectification Accuracy                            | 154 |

| 15.1.2.18 | Rectification Mode entry                          | 155 |

| 15.1.2.19 | No Operation                                      | 156 |

| 15.1.2.20 | Reverse Diode Measurement                         |     |

| 15.1.2.21 | Drain Source Measurement                          | 158 |

| 15.1.3    | Self_test registers                               |     |

| 15.1.3.1  | Self Test Selection 1                             | 159 |

| 15.1.3.2  | Self Test Selection 2                             | 160 |

| 15.1.3.3  | Self Test Mode Entry                              | 161 |

| 15.1.4    | Read registers                                    | 162 |

| 15.1.4.1  | Operation Mode Overview                           |     |

| 15.1.4.2  | Error Overview                                    | 163 |

| 15.1.4.3  | Special Event Register                            | 164 |

| 15.1.4.4  | Internal Errors 1                                 | 165 |

| 15.1.4.5  | Internal Errors 2                                 | 166 |

| 15.1.4.6  | External Errors                                   | 167 |

| 15.1.4.7  | Shutdown Errors                                   | 168 |

| 15.1.4.8  | Short Circuit Errors                              | 169 |

| 15.1.4.9  | Input Pattern Violations                          | 170 |

| 15.1.4.10 | Output Stage Feedback Errors                      | 171 |

| 15.1.4.11 | SPI Communication and Configuration Errors        | 172 |

| 15.1.4.12 | Current Sense Amplifiers 1 & 2 Errors             | 173 |

| 15.1.4.13 | Current Sense Amplifier 3                         | 174 |

| 15.1.4.14 | Digital Output Pin Errors                         | 175 |

| 15.1.4.15 | Low-side 1 Drain Source Measurement               |     |

| 15.1.4.16 | Low-side 2 Drain Source Measurement               | 177 |

|           |                                                   |     |

## Bridge Driver IC

|           | Revision History                                                           | 209 |

|-----------|----------------------------------------------------------------------------|-----|

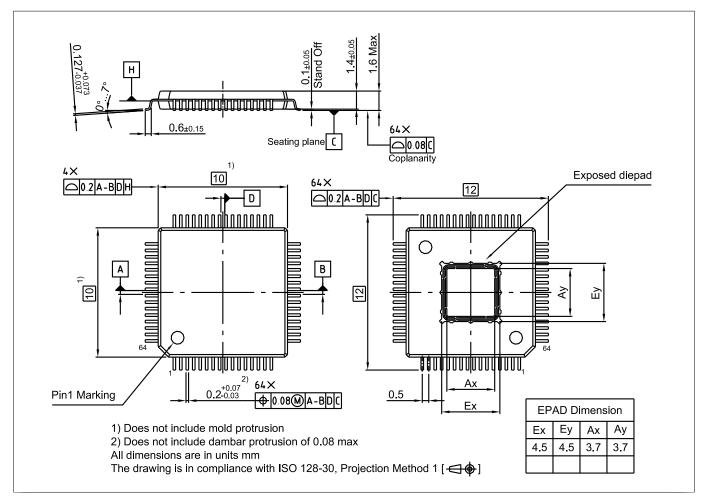

| 17        | Package Outlines                                                           | 207 |

| 16.3.10   | Reduced Operation Mode INH set to low                                      |     |

| 16.3.9    | Minimum INH Pulse Length at Power Up Sequence                              |     |

| 16.3.8    | FET Reverse Diode Forward Voltage Read Out - No Dead time Generation in μC |     |

| 16.3.7    | FET Reverse Diode Forward Voltage Read Out - Short Dead Time               |     |

| 16.3.6    | Digital Output Pin Overload Detection                                      |     |

| 16.3.5    | Overload CP1                                                               |     |

| 16.3.4    | CSA Cross Talk                                                             |     |

| 16.3.3    | Minimum Input Pulses at Pins IHx and ILx                                   |     |

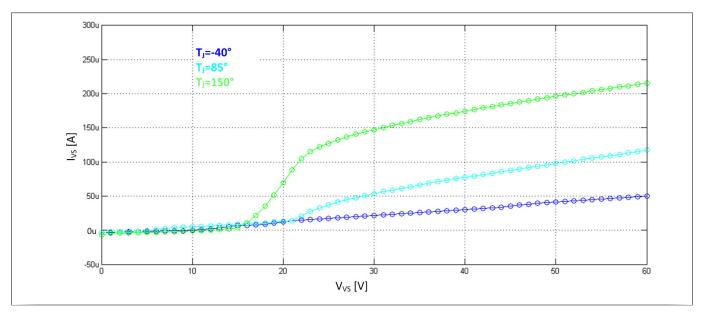

| 16.3.2    | Quiescent Current Consumption at Pin Vs                                    |     |

| 16.3.1    | High Level Output Voltage of Digital Output Pins                           |     |

| 16.3      | Additional Application Hints                                               |     |

| 16.2.1    | Additional Components                                                      |     |

| 16.2      | Additional Components Recommendation                                       |     |

| 16.1      | Layout Guide Lines                                                         |     |

| 16        | Application Information                                                    |     |

|           |                                                                            |     |

| 15.1.4.40 | VDHP Measurement Result                                                    |     |

| 15.1.4.39 | Vs Measurement Result                                                      |     |

| 15.1.4.38 | CB Measurement Result                                                      |     |

| 15.1.4.37 | VCC Measurement Result                                                     |     |

| 15.1.4.36 | Watchdog Clock Counter 3                                                   |     |

| 15.1.4.35 | Watchdog Clock Counter 2                                                   |     |

| 15.1.4.34 | Watchdog Clock Counter 1                                                   |     |

| 15.1.4.33 | Window Watchdog Loop Counter                                               |     |

| 15.1.4.32 | High-side 3 Output Stage Temperature                                       |     |

| 15.1.4.31 | High-side 2 Output Stage Temperature                                       |     |

| 15.1.4.30 | High-side 1 Output Stage Temperature                                       |     |

| 15.1.4.29 | Low-side 3 Output Stage Temperature                                        |     |

| 15.1.4.28 | Low-side 2 Output Stage Temperature                                        |     |

| 15.1.4.27 | Low-side 1 Output Stage Temperature                                        |     |

| 15.1.4.26 | High-side 3 Reverse Diode Measurement                                      |     |

| 15.1.4.25 | High-side 2 Reverse Diode Measurement                                      |     |

| 15.1.4.24 | High-side 1 Reverse Diode Measurement                                      |     |

| 15.1.4.23 | Low-side 3 Reverse Diode Measurement                                       |     |

| 15.1.4.22 | Low-side 2 Reverse Diode Measurement                                       |     |

| 15.1.4.21 | Low-side 1 Reverse Diode Measurement                                       |     |

| 15.1.4.20 | High-side 3 Drain Source Measurement                                       |     |

| 15.1.4.19 | High-side 2 Drain Source Measurement                                       |     |

| 15.1.4.18 | High-side 1 Drain Source Measurement                                       |     |

| 15.1.4.17 | Low-side 3 Drain Source Measurement                                        |     |

## Bridge Driver IC

|              |      | 242  |

|--------------|------|------|

| Dicciaimar   |      | 212  |

| DISCLAIIIIEI | <br> | <br> |

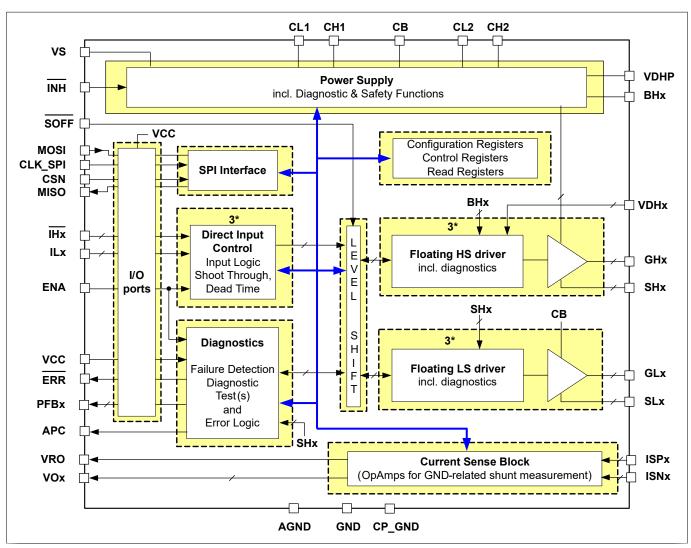

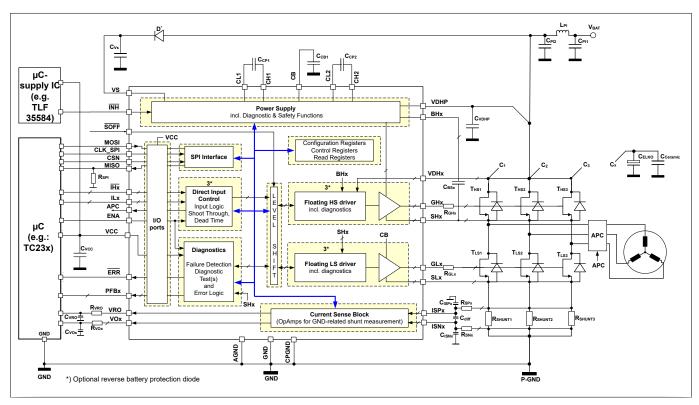

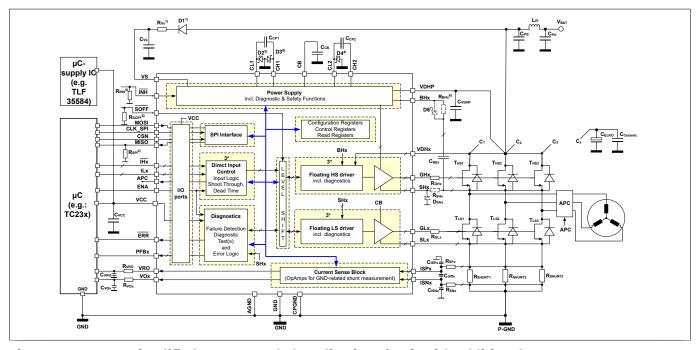

### 1 Block Diagram

### **Block Diagram** 1

Figure 1 **Block Diagram**

### bridge briver ic

## 2 Pin Configuration

## **2** Pin Configuration

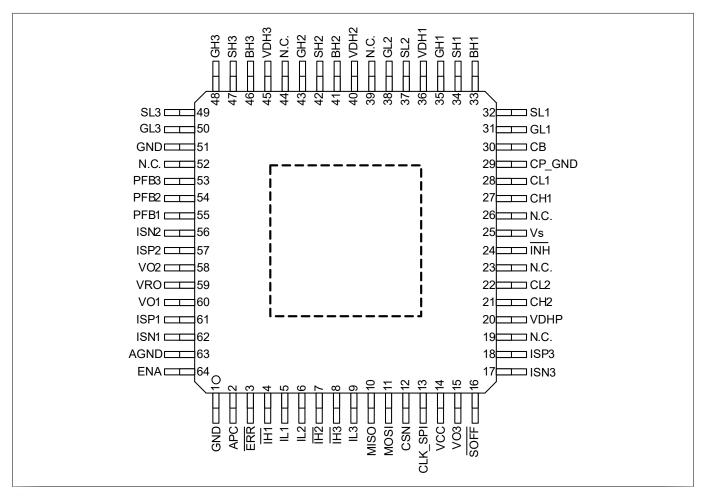

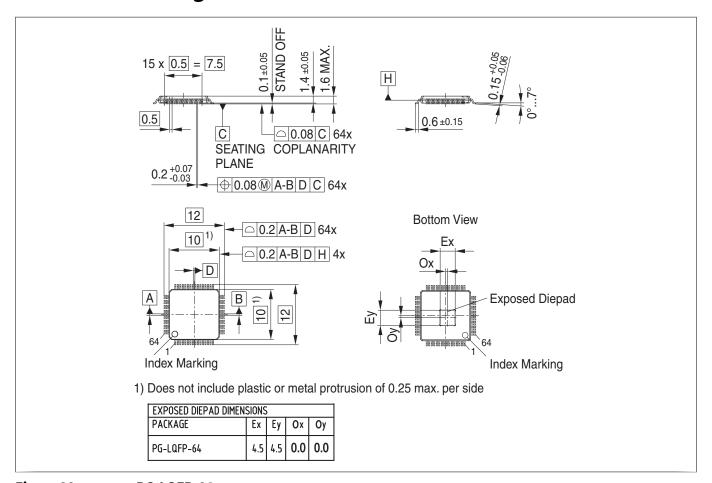

### 2.1 Pin Assignment

Figure 2 Pin Configuration

### 2.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                                                                                                                                                          |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND    | Ground                                                                                                                                                                                            |

|     |        | Connect this pin to ground.                                                                                                                                                                       |

| 2   | APC    | Activation Phase Cut off Circuit                                                                                                                                                                  |

|     |        | Digital output referred to 5 V. Connect this safe state output pin to the driving circuit for the phase separation FETs. Can be used for any other safe state circuit. If not used keep pin open. |

| 3   | ERR    | Error Not                                                                                                                                                                                         |

|     |        | Digital active-low error output pin referred to VCC supply voltage. Indication for ready for configuration when high after power-up. If not used keep pin open.                                   |

| 4   | ĪH1    | Input High-side 1 Not                                                                                                                                                                             |

|     |        | Digital active-low input pin to turn on/off high-side FET 1 referred to VCC supply voltage.                                                                                                       |

## infineon

| Pin | Symbol  | Function                                                                                                                                                                                                                                    |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | IL1     | Input Low-side 1                                                                                                                                                                                                                            |

|     |         | Digital active-high input pin to turn on/off low-side FET 1 referred to VCC supply voltage.                                                                                                                                                 |

| 6   | IL2     | Input Low-side 2                                                                                                                                                                                                                            |

|     |         | Digital active-high input pin to turn on/off low-side FET 2 referred to VCC supply voltage.                                                                                                                                                 |

| 7   | ĪH2     | Input High-side 2 Not                                                                                                                                                                                                                       |

|     |         | Digital active-low input pin to turn on/off high-side FET 2 referred to VCC supply voltage.                                                                                                                                                 |

| 8   | ĪH3     | Input High-side 3 Not                                                                                                                                                                                                                       |

|     |         | Digital active-low input pin to turn on/off high-side FET 3 referred to VCC supply voltage.                                                                                                                                                 |

| 9   | IL3     | Input Low-side 3                                                                                                                                                                                                                            |

|     |         | Digital active-high input pin to turn on/off low-side FET 3 referred to VCC supply voltage.                                                                                                                                                 |

| 10  | MISO    | Master In Slave Out                                                                                                                                                                                                                         |

|     |         | Digital SPI signalling output port referred to VCC supply voltage. Connect to SPI port "data input" of $\mu$ C to send status information during SPI communication.                                                                         |

| 11  | MOSI    | Master Out Slave In                                                                                                                                                                                                                         |

|     |         | Digital SPI signalling input port referred to VCC supply voltage. Connect to SPI port "data output" of $\mu C$ to receive commands during SPI communication.                                                                                |

| 12  | CSN     | Chip Select Not                                                                                                                                                                                                                             |

|     |         | Digital active-low SPI signalling input port referred to VCC supply voltage. Connect to SPI port "chip select" of $\mu$ C to address the device for SPI communication.                                                                      |

| 13  | CLK_SPI | Clock Serial Peripheral Interface                                                                                                                                                                                                           |

|     |         | Digital SPI signalling input port referred to VCC supply voltage. Connect to SPI port "clock" of $\mu C$ to clock the device for SPI communication.                                                                                         |

| 14  | VCC     | VCC Supply Voltage                                                                                                                                                                                                                          |

|     |         | Power supply for digital I/O pins and input for VCC monitoring. Connect to I/O supply of $\mu C$ .                                                                                                                                          |

| 15  | VO3     | Voltage Output of CSA 3                                                                                                                                                                                                                     |

|     |         | Analog output of current sense amplifier 3 for shunt signal amplification referred to 5 V. Connect to analog-to-digital converter.                                                                                                          |

| 16  | SOFF    | Safe Off Not                                                                                                                                                                                                                                |

|     |         | Analog active-low input pin to turn all FETs off and to enter safe off mode. Functional independent to ENA pin.                                                                                                                             |

| 17  | ISN3    | Input Shunt Negative of CSA 3                                                                                                                                                                                                               |

|     |         | Negative input of current sense amplifier 3 for shunt signal amplification. An external input filter is recommended. If current sense amplifier 3 is not used the pin shall be connected to GND and deactivate CSA 3 at configuration mode. |

## infineon

| Pin | Symbol | Function                                                                                                                                                                                                                                    |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | ISP3   | Input Shunt Positive of CSA 3                                                                                                                                                                                                               |

|     |        | Positive input of current sense amplifier 3 for shunt signal amplification. An external input filter is recommended. If current sense amplifier 3 is not used the pin shall be connected to GND and deactivate CSA 3 at configuration mode. |

| 19  | N.C.   | Not Connected                                                                                                                                                                                                                               |

|     |        | Keep pin open and do not connect to GND                                                                                                                                                                                                     |

| 20  | VDHP   | Voltage Drain High-side Power                                                                                                                                                                                                               |

|     |        | Low reference for charge pump 2.                                                                                                                                                                                                            |

|     |        | Sense input for VDHP under- and overvoltage detections, shutdown and readout. Sense input for phase voltage feedback PFBx threshold.                                                                                                        |

|     |        | Sense input for short circuit detection (SCD) of all high-side FETs. (Note: Depends on configuration, bit en_vdh3. If pins VDHx are used for short circuit detection (activated via SPI) then VDHP pin is not the sense input for SCD.)     |

|     |        | Connect this pin directly (low ohmic and low inductive) to recommended common star point of the drains of the high-side FETs and buffer capacitor(s).                                                                                       |

| 21  | CH2    | Charge Pump 2 High                                                                                                                                                                                                                          |

|     |        | Positive terminal for pump capacitor of charge pump 2. Connect the pump capacitor as close as possible to pin.                                                                                                                              |

| 22  | CL2    | Charge Pump 2 Low                                                                                                                                                                                                                           |

|     |        | Negative terminal for pump capacitor of charge pump 2. Connect the pump capacitor as close as possible to pin.                                                                                                                              |

| 23  | N.C.   | Not Connected                                                                                                                                                                                                                               |

|     |        | Keep pin open and do not connect to GND                                                                                                                                                                                                     |

| 24  | ĪNH    | Inhibit Not                                                                                                                                                                                                                                 |

|     |        | Analog active-low inhibit pin. Sets device into sleep mode for low quiescent current consumption. External FETs are turned off actively before the charge pumps are turned off. Reset via inhibit requires a new configuration via SPI.     |

| 25  | Vs     | Voltage Supply                                                                                                                                                                                                                              |

|     |        | Supply voltage for device. Connect to supply (battery) voltage with reverse polarity protection circuit and capacitor between pin and GND. An EMC filter is recommended.                                                                    |

| 26  | N.C.   | Not Connected                                                                                                                                                                                                                               |

|     |        | Keep pin open and do not connect to GND                                                                                                                                                                                                     |

| 27  | CH1    | Charge Pump 1 High                                                                                                                                                                                                                          |

|     |        | Positive terminal for pump capacitor of charge pump 1. Connect the pump capacitor as close as possible to pin.                                                                                                                              |

| 28  | CL1    | Charge Pump 1 Low                                                                                                                                                                                                                           |

|     |        | Negative terminal for pump capacitor of charge pump 1. Connect the pump capacitor as close as possible to pin.                                                                                                                              |

| 29  | CP_GND | Charge Pump Ground                                                                                                                                                                                                                          |

|     |        | GND pin for the charge pumps. Connect this pin directly (low ohmic and low inductive) to GND.                                                                                                                                               |

| Pin | Symbol | Function                                                                                                                                                                                                                                                                                                                                                               |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30  | СВ     | Charge Pump Buffer                                                                                                                                                                                                                                                                                                                                                     |

|     |        | Buffer capacitor connection for charge pump 1. Connect the capacitor as close as possible to pin.                                                                                                                                                                                                                                                                      |

| 31  | GL1    | Gate Low-side 1                                                                                                                                                                                                                                                                                                                                                        |

|     |        | Analog I/O pin to turn on/off low-side FET 1. Connect to the gate of low-side FET 1. A gate resistor is recommended.                                                                                                                                                                                                                                                   |

| 32  | SL1    | Source Low-side 1                                                                                                                                                                                                                                                                                                                                                      |

|     |        | Analog I/O pin to turn on/off low-side FET 1. Connect to the source of low-side FET 1. If transients violate maximum rating or functional range external protection circuit is required.                                                                                                                                                                               |

| 33  | BH1    | Bootstrap High-side 1                                                                                                                                                                                                                                                                                                                                                  |

|     |        | Analog I/O pin. Positive terminal to high-side buffer capacitor 1. Connect the capacitor as close as possible to pin.                                                                                                                                                                                                                                                  |

| 34  | SH1    | Source High-side 1                                                                                                                                                                                                                                                                                                                                                     |

|     |        | Analog I/O pin to turn on/off high-side FET 1 and negative terminal to high-side buffer capacitor. Connect the capacitor as close as possible to pin and connect to the source of high-side FET 1. Connection to motor and input for phase voltage feedback circuit. If transients violate maximum rating or functional range external protection circuit is required. |

| 35  | GH1    | Gate High-side 1                                                                                                                                                                                                                                                                                                                                                       |

|     |        | Analog I/O pin to turn on/off high-side FET 1. Connect to the gate of high-side FET 1. A gate resistor is recommended.                                                                                                                                                                                                                                                 |

| 36  | VDH1   | Voltage Drain High-side 1                                                                                                                                                                                                                                                                                                                                              |

|     |        | Sense input for short circuit detection (SCD) of high-side FET 1. (Note: Depends on configuration, bit en_vdh3. If pins VDHx are used for short circuit detection (activated via SPI) then VDHP pin is not the sense input for SCD.)                                                                                                                                   |

|     |        | Connect directly to the drain of high-side FET 1, or not connected if not configured.                                                                                                                                                                                                                                                                                  |

| 37  | SL2    | Source Low-side 2                                                                                                                                                                                                                                                                                                                                                      |

|     |        | Analog I/O pin to turn on/off low-side FET 2. Connect to the source of low-side FET 2. If transients violate maximum rating or functional range external protection circuit is required.                                                                                                                                                                               |

| 38  | GL2    | Gate Low-side 2                                                                                                                                                                                                                                                                                                                                                        |

|     |        | Analog I/O pin to turn on/off low-side FET 2. Connect to the gate of low-side FET 2. A gate resistor is recommended.                                                                                                                                                                                                                                                   |

| 39  | N.C.   | Not Connected                                                                                                                                                                                                                                                                                                                                                          |

|     |        | Keep pin open and do not connect to GND                                                                                                                                                                                                                                                                                                                                |

| 40  | VDH2   | Voltage Drain High-side 2                                                                                                                                                                                                                                                                                                                                              |

|     |        | Sense input for short circuit detection (SCD) of high-side FET 2. (Note: Depends on configuration, bit en_vdh3. If pins VDHx are used for short circuit detection (activated via SPI) then VDHP pin is not the sense input for SCD.)                                                                                                                                   |

|     |        | Connect directly to the drain of high-side FET 2, or not connected if not configured.                                                                                                                                                                                                                                                                                  |

# infineon

| Pin | Symbol | Function                                                                                                                                                                                                                                                                                                                                                               |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 41  | BH2    | Bootstrap High-side 2                                                                                                                                                                                                                                                                                                                                                  |

|     |        | Analog I/O pin. Positive terminal to high-side buffer capacitor 2. Connect the capacitor as close as possible to pin.                                                                                                                                                                                                                                                  |

| 42  | SH2    | Source High-side 2                                                                                                                                                                                                                                                                                                                                                     |

|     |        | Analog I/O pin to turn on/off high-side FET 2 and negative terminal to high-side buffer capacitor. Connect the capacitor as close as possible to pin and connect to the source of high-side FET 2. Connection to motor and input for phase voltage feedback circuit. If transients violate maximum rating or functional range external protection circuit is required. |

| 43  | GH2    | Gate High-side 2                                                                                                                                                                                                                                                                                                                                                       |

|     |        | Analog I/O pin to turn on/off high-side FET 2. Connect to the gate of high-side FET 2. A gate resistor is recommended.                                                                                                                                                                                                                                                 |

| 44  | N.C.   | Not Connected                                                                                                                                                                                                                                                                                                                                                          |

|     |        | Keep pin open and do not connect to GND                                                                                                                                                                                                                                                                                                                                |

| 45  | VDH3   | Voltage Drain High-side 3                                                                                                                                                                                                                                                                                                                                              |

|     |        | Sense input for short circuit detection (SCD) of high-side FET 3. (Note: Depends on configuration, bit en_vdh3. If pins VDHx are used for short circuit detection (activated via SPI) then VDHP pin is not the sense input for SCD.)                                                                                                                                   |

|     |        | Connect directly to the drain of high-side FET 3, or not connected if not configured.                                                                                                                                                                                                                                                                                  |

| 46  | ВН3    | Bootstrap High-side 3                                                                                                                                                                                                                                                                                                                                                  |

|     |        | Analog I/O pin. Positive terminal to high-side buffer capacitor 3. Connect the capacitor as close as possible to pin.                                                                                                                                                                                                                                                  |

| 47  | SH3    | Source High-side 3                                                                                                                                                                                                                                                                                                                                                     |

|     |        | Analog I/O pin to turn on/off high-side FET 3 and negative terminal to high-side buffer capacitor. Connect the capacitor as close as possible to pin and connect to the source of high-side FET 3. Connection to motor and input for phase voltage feedback circuit. If transients violate maximum rating or functional range external protection circuit is required. |

| 48  | GH3    | Gate High-side 3                                                                                                                                                                                                                                                                                                                                                       |

|     |        | Analog I/O pin to turn on/off high-side FET 3. Connect to the gate of high-side FET 3. A gate resistor is recommended.                                                                                                                                                                                                                                                 |

| 49  | SL3    | Source Low-side 3                                                                                                                                                                                                                                                                                                                                                      |

|     |        | Analog I/O pin to turn on/off low-side FET 3. Connect to the source of low-side FET 3. If transients violate maximum rating or functional range external protection circuit is required.                                                                                                                                                                               |

| 50  | GL3    | Gate Low-side 3                                                                                                                                                                                                                                                                                                                                                        |

|     |        | Analog I/O pin to turn on/off low-side FET 3. Connect to the gate of low-side FET 3. A gate resistor is recommended.                                                                                                                                                                                                                                                   |

| 51  | GND    | Ground                                                                                                                                                                                                                                                                                                                                                                 |

|     |        | Connect this pin to ground.                                                                                                                                                                                                                                                                                                                                            |

| 52  | N.C.   | Not Connected                                                                                                                                                                                                                                                                                                                                                          |

|     |        | Keep pin open and do not connect to GND                                                                                                                                                                                                                                                                                                                                |

# infineon

| Pin | Symbol | Function                                                                                                                                                                                                                                    |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53  | PFB3   | Phase Voltage Feedback 3                                                                                                                                                                                                                    |

|     |        | Digital output pin referred to VCC supply voltage. Feedback for $\mu$ C of the state of the motor connection of pin SH3 referred to voltage at VDHP. Connect to PFB 3 port to $\mu$ C. If not used keep pin open.                           |

| 54  | PFB2   | Phase Voltage Feedback 2                                                                                                                                                                                                                    |

|     |        | Digital output pin referred to VCC supply voltage. Feedback for $\mu$ C of the state of the motor connection of pin SH2 referred to voltage at VDHP. Connect to PFB 2 port to $\mu$ C. If not used keep pin open.                           |

| 55  | PFB1   | Phase Voltage Feedback 1                                                                                                                                                                                                                    |

|     |        | Digital output pin referred to VCC supply voltage. Feedback for $\mu$ C of the state of the motor connection of pin SH1 referred to voltage at VDHP. Connect to PFB 1 port to $\mu$ C. If not used keep pin open.                           |

| 56  | ISN2   | Input Shunt Negative of CSA 2                                                                                                                                                                                                               |

|     |        | Negative input of current sense amplifier 2 for shunt signal amplification. An external input filter is recommended. If current sense amplifier 2 is not used the pin shall be connected to GND and deactivate CSA 2 at configuration mode. |

| 57  | ISP2   | Input Shunt Positive of CSA 2                                                                                                                                                                                                               |

|     |        | Positive input of current sense amplifier 2 for shunt signal amplification. An external input filter is recommended. If current sense amplifier 2 is not used the pin shall be connected to GND and deactivate CSA 2 at configuration mode. |

| 58  | VO2    | Voltage Output of CSA 2                                                                                                                                                                                                                     |

|     |        | Analog output of current sense amplifier 2 for shunt signal amplification referred to 5 V. Connect to analog-to-digital converter.                                                                                                          |

| 59  | VRO    | Voltage Reference Output                                                                                                                                                                                                                    |

|     |        | Output pin of reference voltage of current sense amplifier. The reference voltage indicates the zero motor current output voltage. Connect to analog-to-digital converter.                                                                  |

| 60  | VO1    | Voltage Output of CSA 1                                                                                                                                                                                                                     |

|     |        | Analog output of current sense amplifier 1 for shunt signal amplification referred to 5 V. Connect to analog-to-digital converter.                                                                                                          |

| 61  | ISP1   | Input Shunt Positive of CSA 1                                                                                                                                                                                                               |

|     |        | Positive input of current sense amplifier 1 for shunt signal amplification. An external input filter is recommended. If current sense amplifier 1 is not used the pin shall be connected to GND and deactivate CSA 1 at configuration mode. |

| 62  | ISN1   | Input Shunt Negative of CSA 1                                                                                                                                                                                                               |

|     |        | Negative input of current sense amplifier 1 for shunt signal amplification. An external input filter is recommended. If current sense amplifier 1 is not used the pin shall be connected to GND and deactivate CSA 1 at configuration mode. |

| 63  | AGND   | Analog Ground                                                                                                                                                                                                                               |

|     |        | GND pin of current sense amplifier. Connect directly (low ohmic and low inductive) to GND.                                                                                                                                                  |

## Bridge Driver IC

| Pin     | Symbol | Function                                                                                                                                      |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 64      | ENA    | Enable                                                                                                                                        |

|         |        | Digital input pin to turn all FETs off referred to VCC supply voltage. Functional independent to SOFF pin. Reset of latched error conditions. |

| Cooling | GND    | Cooling Tab                                                                                                                                   |

| Tab     |        | To be connected to GND                                                                                                                        |

Rev. 1.31 2023-04-30

### **3 General Product Characteristics**

### **General Product Characteristics** 3

### **Absolute Maximum Ratings** 3.1

### Table 2 **Absolute Maximum Ratings**

$T_i = -40$ °C to +150°C; all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                          | Symbol               |      | Values | i    | Unit | Note or Test                                | Number   |

|----------------------------------------------------|----------------------|------|--------|------|------|---------------------------------------------|----------|

|                                                    |                      | Min. | Тур.   | Max. |      | Condition                                   |          |

| Power Supply                                       |                      |      | 1      | 1    |      | 1                                           |          |

| Supply Voltage                                     | V <sub>Vs1</sub>     | -0.3 | _      | 60   | V    | _                                           | P_4.1.1  |

| Supply Voltage for Power-up <sup>1)</sup>          | V <sub>Vs6</sub>     | _    | _      | 40   | V    | -                                           | P_4.1.7  |

| Supply Voltage <sup>1)</sup>                       | V <sub>Vs2</sub>     | -5   | -      | -    | V    | Reverse polarity $R_{VS} \ge 10 \Omega^{2}$ | P_4.1.2  |

| Voltage Range VDHP                                 | V <sub>VDHP1</sub>   | -5   | _      | 85   | V    | 3)                                          | P_4.1.3  |

| Voltage Difference Vs-VDHP                         | $V_{\rm dVsVDHP}$    | -85  | _      | 60   | V    | _                                           | P_4.1.5  |

| Voltage Range VDH1, VDH2, VDH3                     | V <sub>VDHx1</sub>   | -5   | _      | 90   | V    | -                                           | P_4.1.6  |

| Voltage Difference Vs-VDH1, VDH2, VDH3             | $V_{\rm dVsVDHx}$    | -90  | -      | 60   | V    | -                                           | P_4.1.8  |

| Voltage Range CL1                                  | V <sub>CL1</sub>     | -0.3 | _      | 60   | V    | _                                           | P_4.1.9  |

| Voltage Range CH1                                  | V <sub>CH1</sub>     | -0.3 | _      | 28   | V    | -                                           | P_4.1.10 |

| Voltage Range CB                                   | V <sub>CB</sub>      | -0.3 | _      | 28   | V    | -                                           | P_4.1.11 |

| Voltage Range CL2, CH2                             | V <sub>CHL2</sub>    | -0.3 | _      | 90   | V    | _                                           | P_4.1.12 |

| Voltage Difference CH2-CL2                         | V <sub>dCH2CL2</sub> | -0.3 | _      | 28   | V    | _                                           | P_4.1.62 |

| Maximum Peak Pulse Current CB to CH2               | I <sub>CBCH2</sub>   | _    | -      | 1    | A    | $t = 5 \mu s^{1/3}$                         | P_4.1.61 |

| Maximum Peak Pulse Current CB to BHx <sup>1)</sup> | I <sub>CBBHx</sub>   | _    | _      | 1    | A    | $t = 0.8 \ \mu s^{4)}$                      | P_4.1.66 |

| Floating Driver Stages                             |                      |      |        | 1    |      | ,                                           | ,        |

| Voltage Range SLx                                  | V <sub>SLx1</sub>    | -7   | _      | 10   | V    | _                                           | P_4.1.13 |

| Voltage Range SLx <sup>1)</sup>                    | V <sub>SLx2</sub>    | -10  | _      | _    | V    | 10)                                         | P_4.1.14 |

| Voltage Range SLx <sup>1)</sup>                    | V <sub>SLx3</sub>    | -15  | _      | _    | V    | 5)                                          | P_4.1.15 |

| Voltage Range GLx                                  | $V_{GLx1}$           | -7   | _      | 28   | V    | -                                           | P_4.1.16 |

| Voltage Range GLx <sup>1)</sup>                    | V <sub>GLx2</sub>    | -10  | _      | _    | V    | 10)                                         | P_4.1.17 |

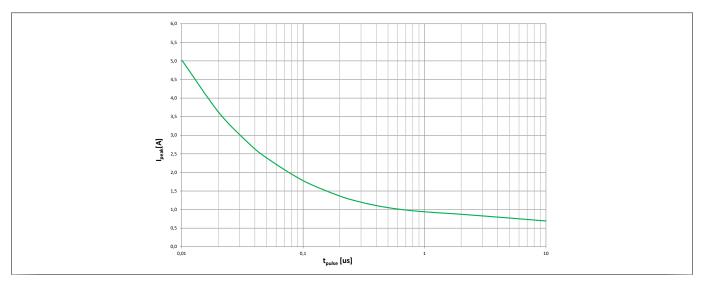

<sup>1</sup> Not subject to production test, specified by design

<sup>2</sup> Voltage drop via resistor has be to taken into account for applications operating at low battery voltage

<sup>3</sup> Minimum limit of -5 V valid only for a limited time frame

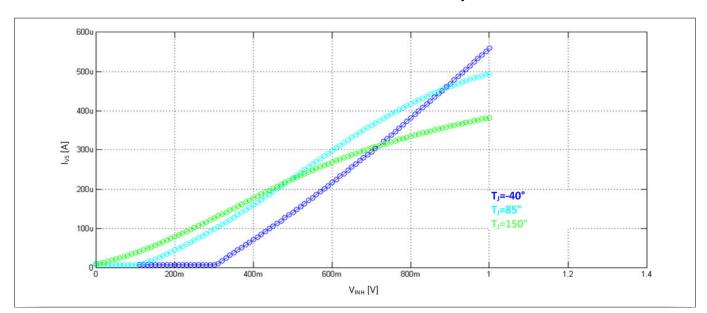

For details please refer to Figure 3

<sup>10</sup> For a duration of t\_on = 500 ns; t\_on/t\_off = 1% per 20 kHz PWM frequency

For a duration of t\_on = 250ns; t\_on/t\_off = 0.5% per 20 kHz PWM frequency

### **3 General Product Characteristics**

### Table 2 (continued) Absolute Maximum Ratings

$T_i = -40$ °C to +150°C; all voltages with respect to GND, positive current flowing into pin (unless otherwise specified)

| Parameter                                | Symbol                 |      | Values |      | Unit |                                    | Number   |

|------------------------------------------|------------------------|------|--------|------|------|------------------------------------|----------|

|                                          |                        | Min. | Тур.   | Max. |      | Condition                          |          |

| Voltage Range GLx <sup>1)</sup>          | V <sub>GLx3</sub>      | -15  | _      | _    | V    | 5)                                 | P_4.1.18 |

| Voltage Range SHx                        | V <sub>SHx1</sub>      | -7   | _      | 90   | V    | _                                  | P_4.1.19 |

| Voltage Range SHx <sup>1)</sup>          | V <sub>SHx2</sub>      | -10  | _      | _    | V    | 10)6)                              | P_4.1.20 |

| Voltage Range SHx <sup>1)</sup>          | V <sub>SHx3</sub>      | -15  | _      | _    | V    | 5)6)                               | P_4.1.21 |

| Max. Voltage Transients at SHx           | V <sub>fSH_tr1</sub>   | _    | -      | 55   | V    | Slew rate ≤ 1 V/ns <sup>7)1)</sup> | P_4.3.31 |

| Voltage Range GHx                        | V <sub>GHx1</sub>      | -7   | _      | 90   | V    | -                                  | P_4.1.22 |

| Voltage Range GHx <sup>1)</sup>          | V <sub>GHx2</sub>      | -10  | _      | _    | V    | 10)                                | P_4.1.23 |

| Voltage Range GHx <sup>1)</sup>          | V <sub>GHx3</sub>      | -15  | _      | _    | V    | 5)                                 | P_4.1.24 |

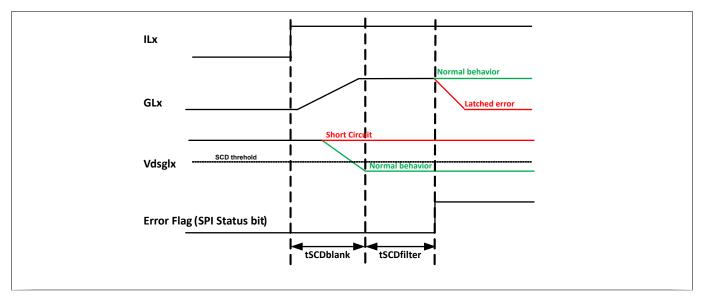

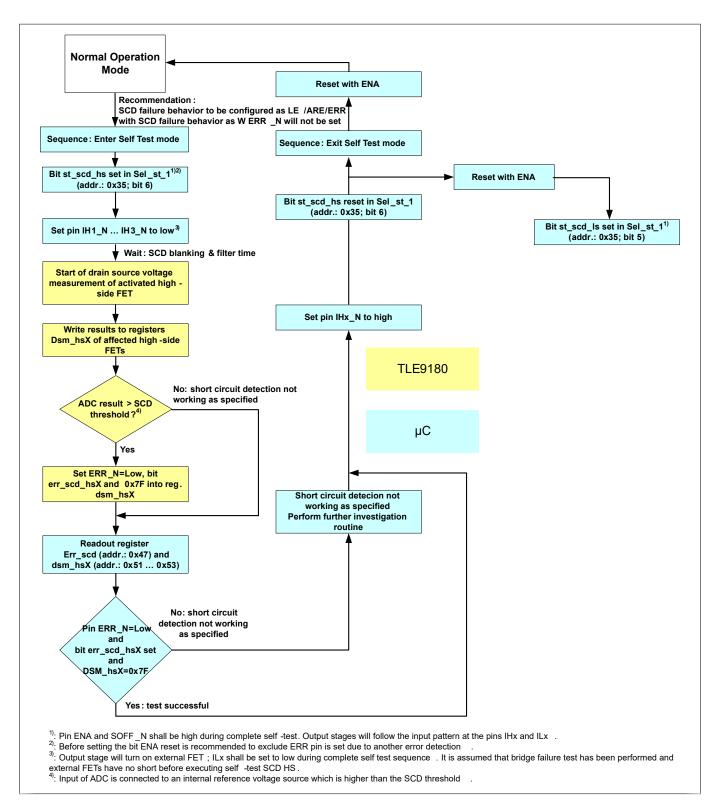

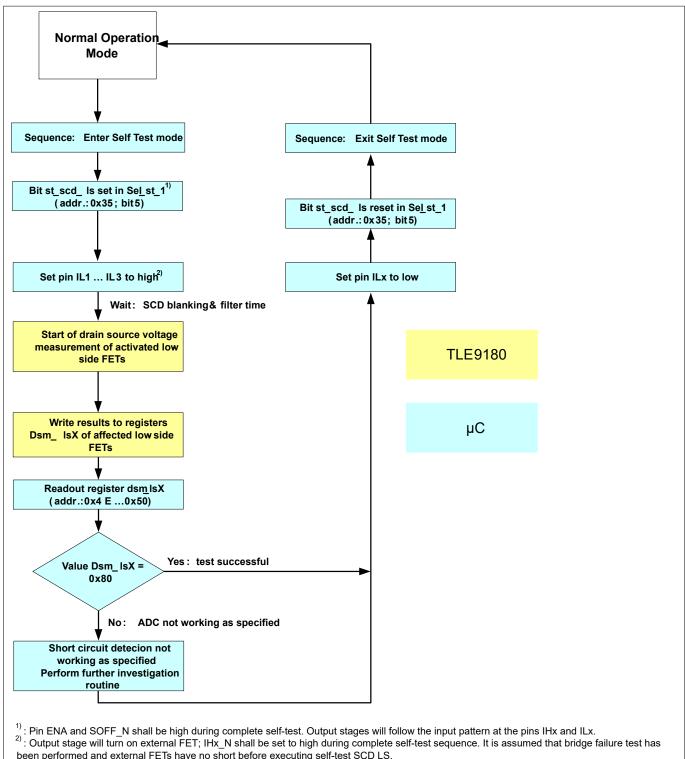

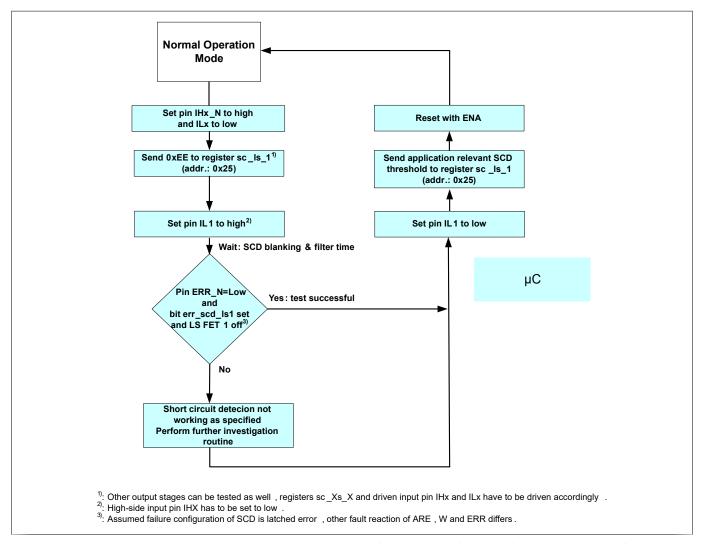

| Voltage Range BHx                        | V <sub>BH</sub>        | -0.3 | _      | 90   | V    | -                                  | P_4.1.25 |