## Remote 16-bit I/O expander for Fm+ I<sup>2</sup>C-bus with interrupt and reset

### **Features**

- → Operation power supply voltage from 2.3V to 5.5V

- → 16-bit remote I/O pins that default to inputs at power-up

- → 1 MHz I<sup>2</sup>C-bus interface

- $\rightarrow$  Compliant with the I<sup>2</sup>C-bus Fast and Standard modes

- → 5.5V tolerant I/Os

- → SDA with 30 mA sink capability for 4000 pF buses

- → Latched outputs with 25 mA sink capability for directly driving LEDs

- → Total package sink capability of 400 mA

- → Active LOW open-drain interrupt output

- → Low standby current

- → 16 programmable slave addresses using 2 address pins

- → ESD protection (4KV HBM and 1KV CDM)

- → Latch-up tested (exceeds 100mA)

- → Offered in three different packages: TSSOP-24 and TOFN 4x4-24

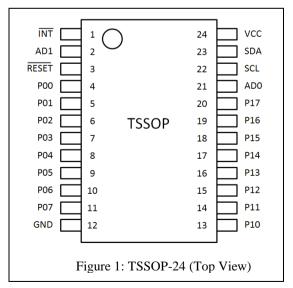

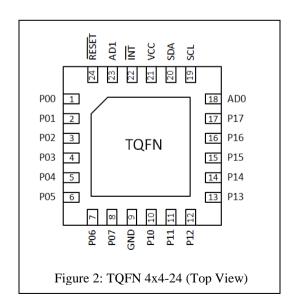

# Pin Configuration

## **Description**

The PI4IOE5V9673 provides general purpose remote I/O expansion for most microcontroller families via the two-line bidirectional bus (I<sup>2</sup>C-bus) and is a part of the Fast-mode Plus family.

The PI4IOE5V9673 provides higher Fast-mode Plus (Fm+) I<sup>2</sup>C-bus speeds (1 MHz versus 400 kHz) so that the output can support PWM dimming of LEDs, higheI2C-bus drive (30 mA) so that many more devices can be on the bus without the need for bus buffers, high total package sink capacity (400 mA) that supports having all 25 mA LEDs on at the same time and more device addresses (16) are available to allow many more devices on the bus without address conflicts.

The device consists of a 16-bit quasi-bidirectional port and an I<sup>2</sup>C-bus interface. The PI4IOE5V9673 has a low current consumption and includes latched outputs with high current drive capability for directly driving LEDs.

It also possesses an interrupt line (INT) which can be connected to the interrupt logic of the microcontroller. By sending an interrupt signal on this line, the remote I/O can inform the microcontroller if there is incoming data on its ports without having to communicate via the I2C-bus. The internal Power-On Reset (POR) or software reset sequence initializes the I/Os as inputs.

# **Pin Description**

Table 1: Pin Description

| Pin     |        | Name  | Туре | Type Description             |  |  |

|---------|--------|-------|------|------------------------------|--|--|

| TSSOP24 | TQFN24 | Name  | Туре | Description                  |  |  |

| 1       | 22     | INT   | О    | Interrupt input (open-drain) |  |  |

| 2       | 23     | AD1   | I    | Address input 1              |  |  |

| 3       | 24     | RESET | I    | Reset input                  |  |  |

| 4       | 1      | P00   | I/O  | Port 0 input/output 0        |  |  |

| 5       | 2      | P01   | I/O  | Port 0 input/output 1        |  |  |

| 6       | 3      | P02   | I/O  | Port 0 input/output 2        |  |  |

| 7       | 4      | P03   | I/O  | Port 0 input/output 3        |  |  |

| 8       | 5      | P04   | I/O  | Port 0 input/output 4        |  |  |

| 9       | 6      | P05   | I/O  | Port 0 input/output 5        |  |  |

| 10      | 7      | P06   | I/O  | Port 0 input/output 6        |  |  |

| 11      | 8      | P07   | I/O  | Port 0 input/output 7        |  |  |

| 12      | 9      | GND   | G    | Ground                       |  |  |

| 13      | 10     | P10   | I/O  | Port 1 input/output 0        |  |  |

| 14      | 11     | P11   | I/O  | Port 1 input/output 1        |  |  |

| 15      | 12     | P12   | I/O  | Port 1 input/output 2        |  |  |

| 16      | 13     | P13   | I/O  | Port 1 input/output 3        |  |  |

| 17      | 14     | P14   | I/O  | Port 1 input/output 4        |  |  |

| 18      | 15     | P15   | I/O  | Port 1 input/output 5        |  |  |

| 19      | 16     | P16   | I/O  | Port 1 input/output 6        |  |  |

| 20      | 17     | P17   | I/O  | Port 1 input/output 7        |  |  |

| 21      | 18     | AD0   | I    | Address input 0              |  |  |

| 22      | 19     | SCL   | I    | Serial clock line input      |  |  |

| 23      | 20     | SDA   | I    | Serial data line open-drain  |  |  |

| 24      | 21     | VCC   | P    | Supply voltage               |  |  |

<sup>\*</sup> I = Input; O = Output; P = Power; G = Ground

## **Maximum Ratings**

| Power supply                           | -0.5V to +6.0V    |

|----------------------------------------|-------------------|

| Voltage on an I/O pin                  | GND-0.5V to +6.0V |

| Input current                          | ±20mA             |

| Output current on an I/O pin           | ±50mA             |

| Supply current                         | ±160mA            |

| Ground supply current                  | 600mA             |

| Total power dissipation                | 600mW             |

| Operation temperature                  | 40~85°C           |

| Storage temperature                    | -65~150°C         |

| Maximum Junction temperature ,T j(max) | 125°C             |

|                                        |                   |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Static characteristics**

VCC = 2.3 V to 5.5 V; GND = 0 V; Tamb= -40  $^{\circ}$ C to +85  $^{\circ}$ C; unless otherwise specified.

Table 2: Static characteristics

| Symbol         | Parameter                             | Conditions                                                                 | Min.   | Тур. | Max.    | Unit |

|----------------|---------------------------------------|----------------------------------------------------------------------------|--------|------|---------|------|

| Power sup      | ply                                   | •                                                                          |        |      |         |      |

| VCC            | Supply voltage                        |                                                                            | 2.3    | -    | 5.5     | V    |

| $I_{CC}$       | Supply current                        | Operating mode; VCC = 5.5 V; no load; fSCL= 1MHz                           | -      | 200  | 500     | μΑ   |

| $I_{stb}$      | Standby current                       | Standby mode; VCC = 5.5 V; no load;<br>VI = VCC; fscL= 0 kHz; I/O = inputs | -      | 2.5  | 10      | uA   |

| $V_{POR}$      | Power-on reset voltage <sup>[1]</sup> |                                                                            | -      | 1.16 | 1.41    | V    |

| Input SCL      | , input/output SDA                    |                                                                            |        |      |         |      |

| $V_{\rm I\!L}$ | Low level input voltage               |                                                                            | -0.5   | -    | +0.3VCC | V    |

| $V_{ m I\!H}$  | High level input voltage              |                                                                            | 0.7VCC | -    | 5.5     | V    |

|                |                                       | V <sub>OL</sub> =0.4V; VCC=2.3V                                            | 16     | -    | -       | mA   |

| $I_{OL}$       | Low level output current              | V <sub>OL</sub> =0.4V; VCC=3V                                              | 18     | -    | -       | mA   |

|                |                                       | V <sub>OL</sub> =0.4V; VCC=4.5V                                            | 20     | -    | -       | mA   |

| $I_{L}$        | Leakage current                       | V <sub>I</sub> =VCC=GND                                                    | -1     | -    | 1       | μΑ   |

| $C_{i}$        | Input capacitance                     | V <sub>I</sub> =GND                                                        | -      | 4    | 10      | pF   |

| Symbol                | Parameter                            | Conditions                                          | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------------------------|-----------------------------------------------------|------|------|------|------|

| I/Os                  |                                      |                                                     |      |      |      |      |

|                       |                                      | $VCC = 2.3 \text{ V}; V_{OL} = 0.5 \text{ V}^{[2]}$ | 12   | 27   |      | mA   |

| $I_{OL}$              | Low level output current             | $VCC = 3.0V; V_{OL} = 0.5V^{[2]}$                   | 17   | 35   |      | mA   |

|                       |                                      | $VCC = 4.5V; V_{OL} = 0.5 V^{[2]}$                  | 25   | 42   |      | mA   |

| I <sub>OL</sub> (tot) | total LOW-level output current       | V <sub>OL</sub> =0.5V;VCC=4.5V                      |      |      | 400  | mA   |

| $I_{OH}$              | HIGH-level output current            | $V_{OH} = GND$                                      | -30  | -359 | -480 | uA   |

| Itrt(pu)              | transient boosted pull-up<br>current | V <sub>OH</sub> = GND                               | -0.5 | -1.0 |      | mA   |

| $C_{i}$               | Off-state Input capacitance          | [3]                                                 | -    | 4    | 10   | pF   |

| Co                    | Off-state Output capacitance         | [3]                                                 | -    | 4    | 10   | pF   |

| Interrupt             | INT                                  |                                                     | ·    |      |      |      |

| $I_{OL}$              | Low level output current             | V <sub>OL</sub> =0.4V                               | 6    | -    | -    | mA   |

| Co                    | Output capacitance                   |                                                     |      | 3    | 10   | pF   |

| Interrupt             | RESET                                |                                                     |      |      |      |      |

| $V_{\rm IL}$          | Low level input voltage              |                                                     | -0.5 | -    | 0.8  | V    |

| $V_{IH}$              | High level input voltage             |                                                     | 2    | -    | 5.5  | V    |

| $I_L$                 | Input leakage current                |                                                     | -1   |      | 1    | μΑ   |

| Ci                    | input capacitance                    |                                                     |      | 3    | 10   | pF   |

| Select inpu           | ts AD0,AD1                           |                                                     |      |      |      |      |

| $V_{\rm IL}$          | Low level input voltage              |                                                     | -0.5 | -    | 0.8  | V    |

| $V_{\mathrm{IH}}$     | High level input voltage             |                                                     | 2    | -    | 5.5  | V    |

| $I_{L}$               | Input leakage current                |                                                     | -1   |      | 1    | μΑ   |

| Ci                    | input capacitance                    |                                                     |      | 3    | 5    | pF   |

Note:

[1]: VCC must be lowered to 0.2 V for at least 20 us in order to reset part.

[2]: Each I/O must be externally limited to a maximum of 25 mA and the total package limited to 400 mA due to internal busing limits.

[3]: The value is not tested, but verified on sampling basis.

# **Dynamic Characteristics**

Table 3: Dynamic characteristics

| Symbol                      | Parameter                                                         | Standa | ard mode I <sup>2</sup> C | Fast mod | e I <sup>2</sup> C | Fast mode<br>Plus I <sup>2</sup> C |      | Unit |

|-----------------------------|-------------------------------------------------------------------|--------|---------------------------|----------|--------------------|------------------------------------|------|------|

|                             | Taraneer                                                          | Min    | Max                       | Min      | Max                | Min                                | Max  |      |

| $f_{SCL}$                   | SCL clock frequency                                               | 0      | 100                       | 0        | 400                | 0                                  | 1000 | kHz  |

| $t_{ m BUF}$                | bus free time between a STOP and START condition                  | 4.7    | -                         | 1.3      | -                  | 0.5                                |      | μs   |

| $t_{\text{HD;STA}}$         | hold time (repeated) START condition                              | 4.0    | -                         | 0.6      | -                  | 0.26                               |      | μs   |

| $t_{SU;STA}$                | set-up time for a repeated START condition                        | 4.7    | -                         | 0.6      | -                  | 0.26                               |      | μs   |

| $t_{\rm SU;STO}$            | set-up time for STOP condition                                    | 4.0    | -                         | 0.6      | -                  | 0.26                               |      | μs   |

| $t_{\mathrm{VD;ACK}}^{[1]}$ | data valid acknowledge time                                       | -      | 3.45                      | =        | 0.9                | -                                  | 0.45 | μs   |

| $t_{\rm HD;DAT}^{[2]}$      | data hold time                                                    | 0      | -                         | 0        | -                  | 0                                  |      | ns   |

| $t_{\mathrm{VD;DAT}}$       | data valid time                                                   | -      | 3.45                      | -        | 0.9                | -                                  | 0.45 | ns   |

| $t_{SU;DAT}$                | data set-up time                                                  | 250    | -                         | 100      | -                  | 50                                 |      | ns   |

| $t_{LOW}$                   | LOW period of the SCL clock                                       | 4.7    | -                         | 1.3      | -                  | 0.5                                |      | μs   |

| t <sub>HIGH</sub>           | HIGH period of the SCL clock                                      | 4.0    | -                         | 0.6      | -                  | 0.26                               |      | μs   |

| $t_{\mathrm{f}}$            | fall time of both SDA and SCL signals                             | -      | 300                       | -        | 300                | -                                  | 120  | ns   |

| t <sub>r</sub>              | rise time of both SDA and SCL signals                             | -      | 1000                      | -        | 300                | -                                  | 120  | ns   |

| $t_{SP}$                    | pulse width of spikes that must be suppressed by the input filter | -      | 50                        | -        | 50                 |                                    | 50   | ns   |

| Port timing                 | g C <sub>L</sub> ≤100pF                                           |        |                           |          |                    |                                    |      |      |

| $t_{v(Q)}$                  | Data output valid time <sup>[3]</sup>                             |        | 4                         |          | 4                  |                                    | 4    | ns   |

| t <sub>su(D)</sub>          | Data input set-up time                                            | 0      |                           | 0        |                    | 0                                  |      | ns   |

| $T_{h(D)}$                  | Data input hold time                                              | 4      |                           | 4        |                    | 4                                  |      | μs   |

| Interrupt t                 | iming C <sub>L</sub> ≤100pF                                       |        |                           |          |                    |                                    |      |      |

| t <sub>v(INT)</sub>         | Valid time on pin INT                                             | -      | 4                         | -        | 4                  |                                    | 4    | μs   |

| t <sub>rst(INT)</sub>       | Reset time on pin INT                                             | -      | 4                         | -        | 4                  |                                    | 4    | μs   |

| Reset timir                 | ng                                                                |        |                           |          | •                  | •                                  | •    |      |

| $t_{w(rst)}$                | Reset pulse width                                                 |        | 25                        | -        | 25                 | -                                  | 25   | ns   |

| $t_{rec(rst)}$              | Reset recovery time                                               |        | 0                         | -        | 0                  | =                                  | 0    | ns   |

| $t_{rst}$                   | Reset time                                                        |        | 1                         | -        | 1                  | -                                  | 1    | us   |

| td(rst)                     | Reset time on pin INT                                             | -      | 4                         | -        | 4                  |                                    | 4    | μs   |

<sup>[1]:</sup>  $t_{VD;ACK}$  = time for acknowledgement signal from SCL LOW to SDA (out) LOW.

<sup>[2]:</sup>  $t_{VD;DAT}$  = minimum time for SDA data out to be valid following SCL LOW. [3]:  $t_{VQ}$  measured from 0.7VCC on SCL to 50% I/O output.

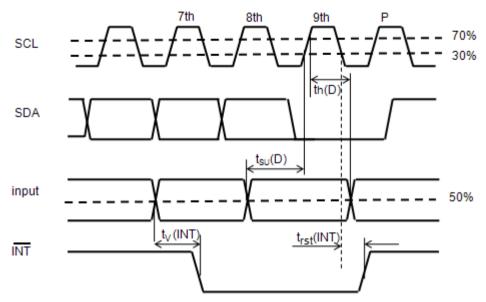

Figure 3: timing parameters for INT signal

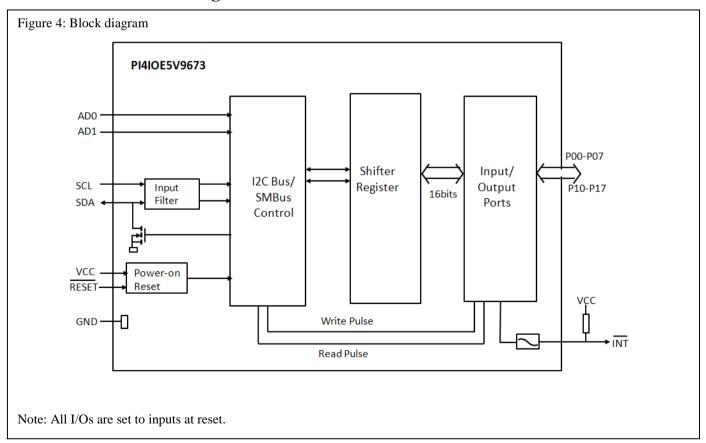

# PI4IOE5V9673 Block Diagram

# **Details Description**

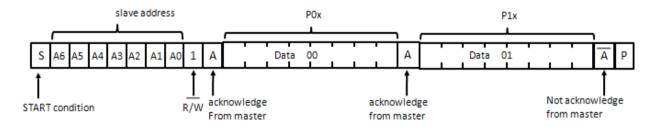

#### a. Device address

Following a START condition, the bus master must send the address of the slave it is accessing and the operation it wants to perform (read or write). The address of the PI4IOE5V9673 is shown in bellow. Slave address pins AD1, and AD0 choose 1 of 16 slave addresses. To conserve power, no internal pull-up resistors are incorporated on AD2, AD1, and AD0. Address values depending on AD1, and AD0 can be found in Table "PI4IOE5V9673 address map".

Remark: The General Call address (0000 0000b) and the Device ID address (1111 100Xb) are reserved and cannot be used as device address. Failure to follow this requirement will cause the PI4IOE5V9673 not to acknowledge.

Remark: Reserved I2C-bus addresses must be used with caution since they can interfere with:

- "reserved for future use" I2C-bus addresses (0000 011, 1111 101, 1111 110, 1111 111)

- slave devices that use the 10-bit addressing scheme (1111 0xx)

- High speed mode (Hs-mode) master code (0000 1xx)

#### PI4IOE5V9673 address

|              | b7(MSB) | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

|--------------|---------|----|----|----|----|----|----|-----|

| Address Byte | A6      | A5 | A4 | A3 | A2 | A1 | A0 | R/W |

The last bit of the first byte defines the operation to be performed. When set to logic 1 a read is selected, while a logic 0 selects a write operation.

### PI4IOE5V9673 Address maps

| AD1 | AD0 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Address<br>(Write) | Address<br>(Read) |

|-----|-----|----|----|----|----|----|----|----|--------------------|-------------------|

| SCL | GND | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 28h                | 29h               |

| SCL | VCC | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 2Ah                | 2Bh               |

| SDA | GND | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 2Ch                | 2Dh               |

| SDA | VCC | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 2Eh                | 2Fh               |

| SCL | SCL | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 38h                | 39h               |

| SCL | SDA | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 3Ah                | 3Bh               |

| SDA | SCL | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 3Ch                | 3Dh               |

| SDA | SDA | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 3Eh                | 3Fh               |

| GND | GND | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 48h                | 49h               |

| GND | VCC | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 4Ah                | 4Bh               |

| VCC | GND | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 4Ch                | 4Dh               |

| VCC | VCC | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 4Eh                | 4Fh               |

| GND | SCL | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 58h                | 59h               |

| GND | SDA | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 5Ah                | 5Bh               |

| VCC | SCL | 0  | 1  | 0  | 1  | 1  | 1  | 0  | 5Ch                | 5Dh               |

| VCC | SDA | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 5Eh                | 5Fh               |

#### **Software Reset call**

• General Call address: allows to reset the PI4IOE5V9673 through the I<sup>2</sup>C-bus upon reception of the right C-bus sequence.

|              | b7(MSB) | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

|--------------|---------|----|----|----|----|----|----|-----|

| General Call | 0       | 1  | 0  | 0  | 1  | 0  | 0  | R/W |

| Address      |         |    |    |    |    |    |    |     |

#### **Software Reset**

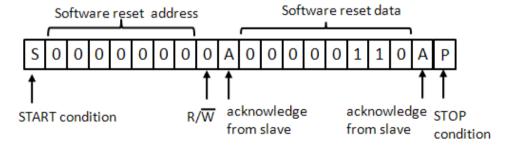

The Software Reset Call allows all the devices in the  $I^2C$ -bus to be reset to the power-up state value through a specific formatted  $I^2C$ -bus command. To be performed correctly, it implies that the  $I^2C$ -bus is functional and that there is no device hanging the bus.

The Software Reset sequence is defined as following:

- 1. A START command is sent by the I<sup>2</sup>C-bus master.

- 2. The reserved General Call I<sup>2</sup>C-bus address '0000 000' with the R/W bit set to 0 (write) is sent by the I<sup>2</sup>C-bus master.

- 3. The device acknowledges after seeing the General Call address '0000 0000' (00h) only. If the R/W bit is set to 1 (read), no acknowledge is returned to the  $I^2$ C-bus master.

- 4. Once the General Call address has been sent and acknowledged, the master sends 1 byte. The value of the byte must be equal to 06h.

- a. The device acknowledges this value only. If the byte is not equal to 06h, the device does not acknowledge it.

- b. If more than 1 byte of data is sent, the device does not acknowledge any more.

- 5. Once the right byte has been sent and correctly acknowledged, the master sends a STOP command to end the Software Reset sequence: the device then resets to the default value (power-up value) and is ready to be addressed again within the specified bus free time. If the master sends a Repeated START instead, no reset is performed.

The I2C-bus master must interpret a non-acknowledge from the device (at any time) as a 'Software Reset Abort'. The device does not initiate a reset of its registers.

The unique sequence that initiates a Software Reset is described in Figure 5.

Figure 5: Software Reset sequence

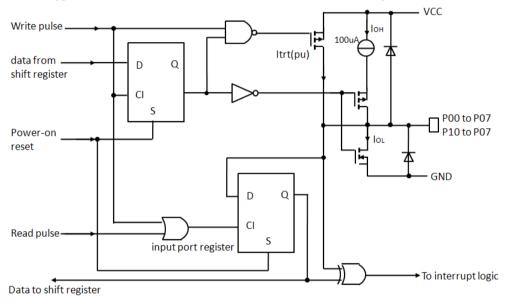

## Quasi-bidirectional I/O architecture

The PI4IOE5V9673's 16 ports (see Figure 6) are entirely independent and can be used either as input or output ports. Input data is transferred from the ports to the microcontroller in the Read mode. Output data is transmitted to the ports in the Write mode.

Every data transmission from the PI4IOE5V9673 must consist of an even number of bytes, the first byte will be referred to as P07 to P00, and the second byte as P17 to P10. The third will be referred to as P07 to P00, and so on.

This quasi-bidirectional I/O can be used as an input or output without the use of a control signal for data directions. At power-on the I/Os are HIGH. In this mode only a current source ( $I_{OH}$ ) to VCC is active. An additional strong pull-up to VCC (Itrt(pu)) allows fast rising edges into heavily loaded outputs. These devices turn on when an output is written HIGH, and are switched off by the negative edge of SCL. The I/Os should be HIGH before being used as inputs. After power-on, as all the I/Os are set HIGH, all of them can be used as inputs. Any change in setting of the I/Os as either inputs or outputs can be done with the write mode.

Remark: If a HIGH is applied to an I/O which has been written earlier to LOW, a large current (I<sub>OL</sub>) will flow to GND.

Figure 6.Simplified schematic diagram of P00 to P17

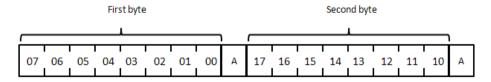

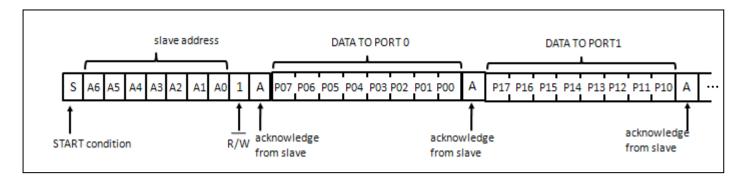

# Writing to the port (Output mode)

To write, the master (microcontroller) first addresses the slave device. By setting the last bit of the byte containing the slave address to logic 0 the Write mode is entered. The PI4IOE5V9673 acknowledges and the master sends the first data byte for P07 to P00. After the first data byte is acknowledged by the PI4IOE5V9673, the second data byte P17 to P10 is sent by the master. Once again, the PI4IOE5V9673 acknowledges the receipt of the data. Each 8-bit data is presented on the port lines after it has been acknowledged by the PI4IOE5V9673.

The number of data bytes that can be sent successively is not limited. After every two bytes, the previous data is overwritten. The first data byte in every pair refers to Port 0 (P07 to P00), whereas the second data byte in every pair refers to Port 1 (P17 to P10).

Figure 7. Correlation between bits and ports

Figure 8. Write Mode

## Reading from a port (Input mode)

All ports programmed as input should be set to logic 1. To read, the master (microcontroller) first addresses the slave device after it receives the interrupt. By setting the last bit of the byte containing the slave address to logic 1 the Read mode is entered. The data bytes that follow on the SDA are the values on the ports.

If the data on the input port changes faster than the master can read, this data may be lost. Transfer of data can be stopped at any moment by a STOP condition. When this occurs, data present at the latest acknowledge phase is valid.

Figure 9.Read input port register

#### Power-on reset

When power is applied to VCC, an internal Power-On Reset (POR) holds the PI4IOE5V9673 in a reset condition until VCC has reached VPOR. At that point, the reset condition is released and the PI4IOE5V9673 registers and I2C-bus/SMBus state machine will initialize to their default states. Thereafter VCC must be lowered below 0.2 V to reset the device.

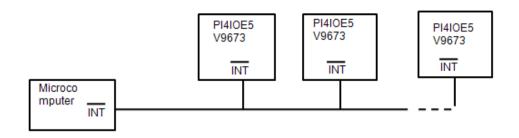

## **Interrupt output (INT)**

The PI4IOE5V9673 provides an open-drain interrupt (INT) which can be fed to a corresponding input of the microcontroller. This gives these chips a kind of master function which can initiate an action elsewhere in the system.

An interrupt is generated by any rising or falling edge of the port inputs. After time  $t_{(V)D}$  the signal INT is valid.

The interrupt disappears when data on the port is changed to the original setting or data is read from or written to the device which has generated the interrupt.

In the write mode, the interrupt may become deactivated (HIGH) on the rising edge of the write to port pulse. On the falling edge of the write to port pulse the interrupt is definitely deactivated (HIGH).

The interrupt is reset in the read mode on the rising edge of the read from port pulse.

During the resetting of the interrupt itself, any changes on the I/Os may not generate an interrupt. After the interrupt is reset any change in I/Os will be detected and transmitted as an INT.

Figure 10. Application of multiple P4IOE5V9673s with interrupt

## **RESET** input

A reset can be accomplished by holding the RESET pin LOW for a minimum of tw(rst). The PI4IOE5V9673 registers and I2C-bus state machine will be held in their default state until the RESET input is once again HIGH. The I2C-bus is for 2-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

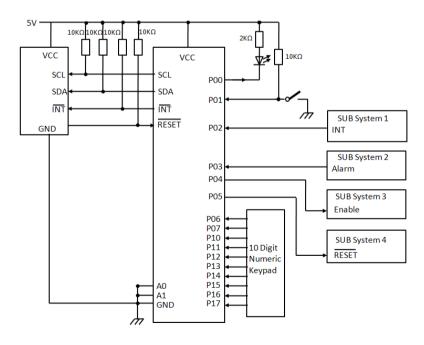

# Bidirectional I/O expander applications

In the 8-bit I/O expander application shown in Figure 11, P00 and P01 are inputs, and P02 to P07 are outputs. When used in this configuration, during a write, the input (P00 and P01) must be written as HIGH so the external devices fully control the input ports. The desired HIGH or LOW logic levels may be written to the I/Os used as outputs (P02 to P07). During a read, the logic levels of the external devices driving the input ports (P00 and P01) and the previous written logic level to the output ports (P02 to P07) will be read. The GPIO also has an interrupt line (INT) that can be connected to the interrupt logic of the microprocessor. By sending an interrupt signal on this line, the remote I/O informs the microprocessor that there is incoming data or a change of data on its ports without having to communicate via the I2C-bus.

Figure 11. Bidirectional I/O expander application

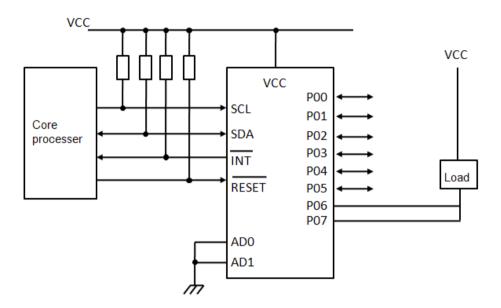

# High current-drive load applications

The GPIO has a maximum sinking current of 25 mA per bit. In applications requiring additional drive, two port pins in the same octal may be connected together to sink up to 50 mA current. Both bits must then always be turned on or off together. Up to 8 pins (one octal) can be connected together to drive 200 mA.

Figure 12. High current-drive load application

## **Mechanical Information**

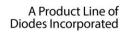

TSSOP-24(L)

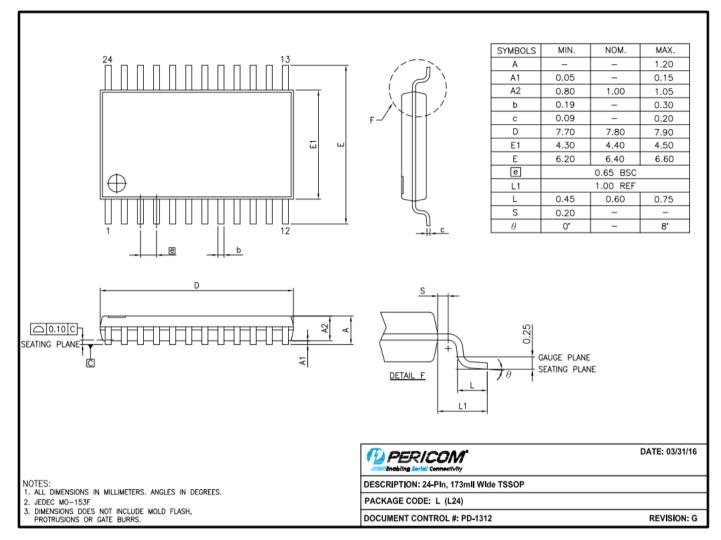

#### **TQFN 4x4-24(ZD)**

Note: For latest package info, please check: http://www.pericom.com/support/packaging/packaging-mechanicals-and-thermal-characteristics/

# **Ordering Information**

| Part Number      | er Package Code Package |                                                             |  |  |  |

|------------------|-------------------------|-------------------------------------------------------------|--|--|--|

| PI4IOE5V9673LE   | L                       | 24-pin, 173mil wide (TSSOP)                                 |  |  |  |

| PI4IOE5V9673LEX  | L                       | 24-pin, 173mil wide (TSSOP), Tape & Reel                    |  |  |  |

| PI4IOE5V9673ZDE  | ZD                      | 24-Contact, Very Thin Quad Flat No-Lead (TQFN)              |  |  |  |

| PI4IOE5V9673ZDEX | ZD                      | 24-Contact, Very Thin Quad Flat No-Lead (TQFN), Tape & Reel |  |  |  |

#### Note:

- Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- E = Pb-free and Green

- Adding X Suffix= Tape/Reel