#### **Features**

- Floating channel designed for bootstrap operation

- Fully operational to +600 V

- Tolerant to negative transient voltage, dV/dt immune

- Gate drive supply range from 10 V to 20 V

- Undervoltage lockout for both channels

- 3.3 V and 5 V input logic compatible

- Matched propagation delay for both channels

- Logic and power ground +/- 5 V offset

- · Lower di/dt gate driver for better noise immunity

- Output source/sink current capability (typical) 1.9 A /2.3 A

- Leadfree, RoHS compliant

- Automotive qualified\*

#### **Typical Applications**

- Piezo/ common rail Injection

- Starter/Alternator

- Electric Power Steering

- Fan and compressor

### **Product Summary**

| Topology                                     | High and Low Side Driver |

|----------------------------------------------|--------------------------|

| V <sub>OFFSET</sub>                          | ≤ 600 V                  |

| V <sub>OUT</sub>                             | 10 V – 20 V              |

| I <sub>o+</sub> & I <sub>o-</sub> (typical)  | 1.9 A &2.3 A             |

| t <sub>ON</sub> & t <sub>OFF</sub> (typical) | 160 ns & 200 ns          |

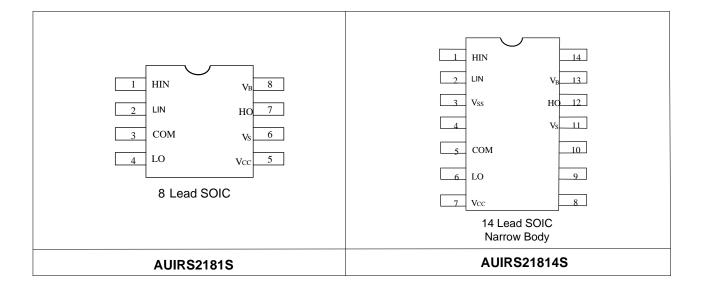

Package Options

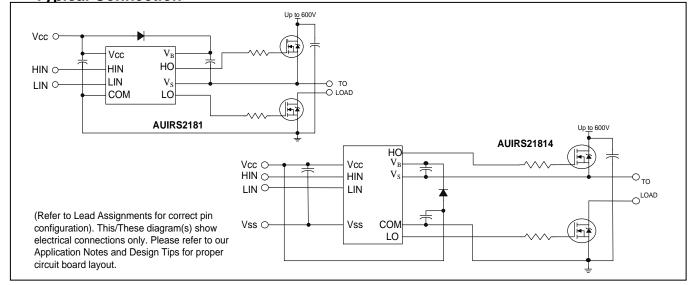

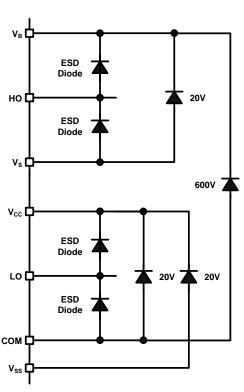

**Typical Connection**

# **Ordering Information**

| Danie Bard Namelan | David and Tarre   | Standard Pack |          | Occupated Boat Noveles |

|--------------------|-------------------|---------------|----------|------------------------|

| Base Part Number   | Package Type Form |               | Quantity | Complete Part Number   |

| ALUD 004040        | SOIC8             | Tube/Bulk     | 95       | AUIRS2181S             |

| AUIRS2181S         | 30108             | Tape and Reel | 2500     | AUIRS2181STR           |

|                    | SOIC14N           | Tube/Bulk     | 55       | AUIRS21814S            |

| AUIRS21814S        | SOIC14N           | Tape and Reel | 2500     | AUIRS21814STR          |

### **Description**

The AUIRS2181(4)(S) are high voltage, high speed power MOSFET and IGBT drivers with independent high and low-side referenced output channels. Proprietary HVIC and latch immune CMOS technologies enable ruggedized monolithic construction. The logic input is compatible with standard CMOS or LSTTL output, down to 3.3 V logic. The output drivers feature a high pulse current buffer stage designed for minimum driver cross-conduction. The floating channel can be used to drive an N-channel power MOSFET or IGBT in the high-side configuration which operates up to 600 V.

### Feature Comparison: AUIRS2181/AUIRS2183/AUIRS2184

| Part  | Input<br>Logic | Cross-<br>Conduction<br>Prevention<br>logic | Dead-Time               | Ground<br>Pins       | Ton/Toff    |

|-------|----------------|---------------------------------------------|-------------------------|----------------------|-------------|

| 2181  |                |                                             |                         | COM                  | 160/200 no  |

| 21814 | HIN/LIN        | no                                          | none                    | V <sub>SS</sub> /COM | 160/200 ns  |

| 2183  |                |                                             | Internal 500ns          | COM                  | 160/200 ns  |

| 21834 | HIN/LIN        | yes                                         | Programmable 0.4 – 5 us | V <sub>SS</sub> /COM | 100/200 115 |

| 2184  |                |                                             | Internal 500ns          | COM                  | 600/220 na  |

| 21844 | IN/SD          | yes                                         | Programmable 0.4 – 5 us | V <sub>SS</sub> /COM | 600/230 ns  |

www.irf.com

© 2014 International Rectifier

### Absolute Maximum Ratings

Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM lead. Stresses beyond those listed under " Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only; and functional operation of the device at these or any other condition beyond those indicated in the "Recommended Operating Conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions. Ambient temperature (T<sub>A</sub>) is 25°C, unless otherwise specified.

| Symbol              | Definition                                             |                      | Min                 | Max                  | Units |

|---------------------|--------------------------------------------------------|----------------------|---------------------|----------------------|-------|

| $V_B$               | High-side floating absolute voltage                    |                      | -0.3                | 625                  |       |

| Vs                  | High-side floating supply offset voltage               |                      | V <sub>B</sub> - 25 | V <sub>B</sub> + 0.3 |       |

| $V_{HO}$            | High-side floating output voltage                      | V <sub>S</sub> - 0.3 | $V_B + 0.3$         |                      |       |

| $V_{CC}$            | Low-side and logic fixed supply voltage                | -0.3                 | 20 <sup>(†)</sup>   | V                    |       |

| $V_{LO}$            | Low-side output voltage                                | -0.3                 | $V_{CC} + 0.3$      |                      |       |

| $V_{IN}$            | Logic input voltage (HIN &LIN)                         | V <sub>SS</sub> -0.3 | $V_{CC} + 0.3$      |                      |       |

| $V_{SS}$            | Logic ground (AUIRS21814(S) only)                      | V <sub>CC</sub> - 20 | $V_{CC} + 0.3$      |                      |       |

| dV <sub>S</sub> /dt | Allowable offset supply voltage transient              |                      |                     | 50                   | V/ns  |

| P <sub>D</sub>      | Package power dissipation @ TA ≤ 25°C                  | (8 lead SOIC)        |                     | 0.625                | W     |

| ГD                  | Fackage power dissipation & TA = 25 C                  | (14 lead SOIC)       |                     | 1.0                  | VV    |

| Dth                 | Thermal registance innetion to embient                 | (8 lead SOIC)        |                     | 200                  | °C/M  |

| Rth <sub>JA</sub>   | Thermal resistance, junction to ambient (14 lead SOIC) |                      | _                   | 120                  | °C/W  |

| TJ                  | Junction temperature                                   |                      |                     | 150                  |       |

| Ts                  | Storage temperature                                    | -50                  | 150                 | °C                   |       |

| $T_L$               | Lead temperature (soldering, 10 seconds)               |                      | _                   | 300                  |       |

<sup>†</sup> All supplies are fully tested at 25 V and an internal 20 V clamp exists for each supply.

### **Recommended Operating Conditions**

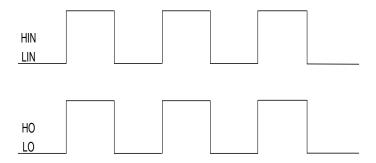

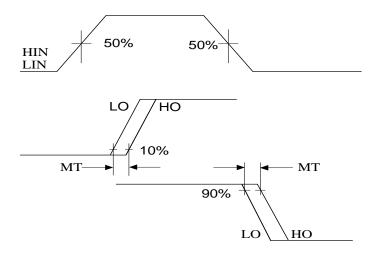

The input/output logic timing diagram is shown in figure 1. For proper operation the device should be used within the recommended conditions. The  $V_S$  and  $V_{SS}$  offset rating are tested with all supplies biased at 15 V differential.

| Symbol   | Definition                                 | Min                | Max                | Units |

|----------|--------------------------------------------|--------------------|--------------------|-------|

| $V_{B}$  | High-side floating supply absolute voltage | V <sub>S</sub> +10 | V <sub>S</sub> +20 |       |

| Vs       | High-side floating supply offset voltage   | (††)               | 600                |       |

| $V_{HO}$ | High-side floating output voltage          | Vs                 | $V_B$              |       |

| $V_{CC}$ | Low-side and logic fixed supply voltage    | 10                 | 20                 | V     |

| $V_{LO}$ | Low-side output voltage                    | 0                  | $V_{CC}$           | V     |

| $V_{IN}$ | Logic input voltage                        | $V_{SS}$           | V <sub>CC</sub>    |       |

| DT       | Programmable deadtime pin voltage          | $V_{SS}$           | V <sub>CC</sub>    |       |

| $V_{SS}$ | Logic ground                               | -5                 | 5                  |       |

| $T_A$    | Ambient temperature                        | -40                | 125                | °C    |

<sup>11</sup> Logic operational for  $V_S$  of -5 V to +600 V. Logic state held for  $V_S$  of -5 V to  $-V_{BS}$ . (Please refer to the Design Tip DT97-3 for more details).

### **Dynamic Electrical Characteristics**

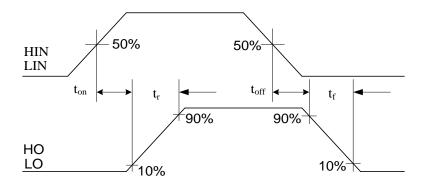

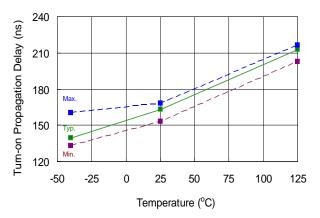

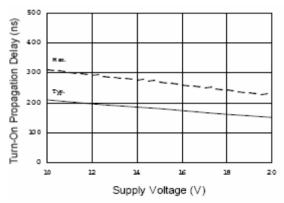

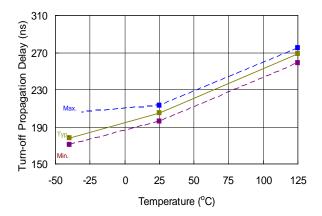

Unless otherwise noted, these specifications apply for an operating junction temperature range of -40°C  $\leq$  Tj  $\leq$  125°C with bias conditions of V<sub>BIAS</sub> (V<sub>CC</sub>, V<sub>BS</sub>) = 15 V, V<sub>SS</sub> = COM, C<sub>L</sub> = 1000 pF.

| Symbol           | Definition                          | Min | Тур | Max | Units | <b>Test Conditions</b>                |

|------------------|-------------------------------------|-----|-----|-----|-------|---------------------------------------|

| t <sub>on</sub>  | Turn-on propagation delay           | _   | 160 | 270 |       | $V_S = 0 V$                           |

| t <sub>off</sub> | Turn-off propagation delay          | _   | 200 | 330 |       | $V_S = 0 \text{ V or } 600 \text{ V}$ |

| MT               | Delay matching, HS & LS turn-on/off |     |     | 35  | ns    |                                       |

| t <sub>r</sub>   | Turn-on rise time                   | _   | 15  | 60  |       | \/ 0\/                                |

| t <sub>f</sub>   | Turn-off fall time                  | _   | 15  | 35  |       | $V_S = 0 V$                           |

#### **Static Electrical Characteristics**

Unless otherwise noted, these specifications apply for an operating junction temperature range of -40°C  $\leq$  Tj  $\leq$  125°C with bias conditions of  $V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 15 V,  $V_{SS}$  = COM. The  $V_{IL}$ ,  $V_{IH}$  and  $I_{IN}$  parameters are referenced to  $V_{SS}$ /COM and are applicable to the respective input leads: HIN and LIN. The  $V_{O_i}$  I<sub>O</sub> and Ron parameters are referenced to COM and are applicable to the respective output leads: HO and LO.

| Symbol                                | Definition                                                                       | Min | Тур | Max | Units | Test Conditions                                   |

|---------------------------------------|----------------------------------------------------------------------------------|-----|-----|-----|-------|---------------------------------------------------|

| $V_{IH}$                              | Logic "1" input voltage                                                          | 2.5 | _   | _   |       | $V_{CC} = 10 \text{ V to } 20 \text{ V}$          |

| $V_{IL}$                              | Logic "0" input voltage                                                          | _   | _   | 0.8 | V     | $V_{CC} = 10 \text{ V to } 20 \text{ V}$          |

| $V_{OH}$                              | High level output voltage, $V_{BIAS}$ - $V_{O}$ — -                              |     | _   | 1.4 | V     | $I_O = 0 \text{ mA}$                              |

| $V_{OL}$                              | Low level output voltage, Vo                                                     | _   | _   | 0.2 |       | $I_O = 20 \text{ mA}$                             |

| $I_{LK}$                              | Offset supply leakage current                                                    | _   | _   | 50  |       | $V_B = V_S = 600 \text{ V}$                       |

| $I_{QBS}$                             | Quiescent V <sub>BS</sub> supply current                                         | 15  | 60  | 150 |       | V = 0 V or 5 V                                    |

| I <sub>QCC</sub>                      | Quiescent V <sub>CC</sub> supply current                                         | 15  | 120 | 240 | μΑ    | $V_{IN} = 0 \text{ V or 5 V}$                     |

| I <sub>IN+</sub>                      | Logic "1" input bias current                                                     | _   | 25  | 60  |       | $V_{IN} = 5 V$                                    |

| I <sub>IN-</sub>                      | Logic "0" input bias current                                                     | _   | _   | 5.0 |       | $V_{IN} = 0 V$                                    |

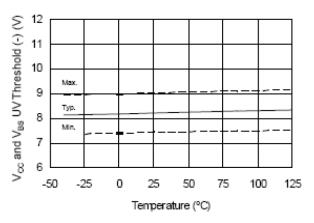

| $V_{CCUV+} \ V_{BSUV+}$               | V <sub>CC</sub> and V <sub>BS</sub> supply undervoltage positive going threshold | 8.0 | 8.9 | 9.8 |       |                                                   |

| $V_{CCUV-} \ V_{BSUV-}$               | $V_{\text{CC}}$ and $V_{\text{BS}}$ supply undervoltage negative going threshold | 7.4 | 8.2 | 9.0 | V     |                                                   |

| $V_{\text{CCUVH}}$ $V_{\text{BSUVH}}$ | $V_{\text{CC}}$ and $V_{\text{BS}}$ supply undervoltage Hysteresis               | 0.3 | 0.7 |     |       |                                                   |

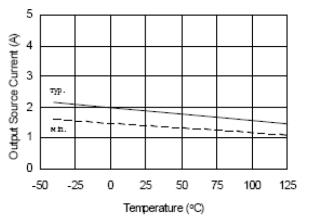

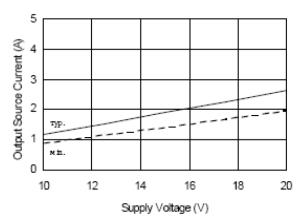

| I <sub>O25+</sub> <sup>(†)</sup>      | Output high short circuit pulsed current                                         | 1.4 | 1.9 | _   |       | $V_O = 0V$ ,<br>$PW \le 10us$ ,<br>$T_J = 25$ °C  |

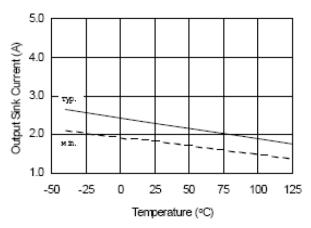

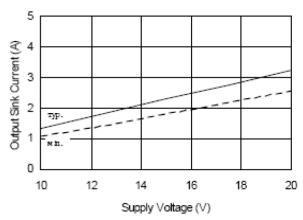

| I <sub>O25-</sub> <sup>(†)</sup>      | Output low short circuit pulsed current                                          | 1.8 | 2.3 | _   | А     | $V_O = 15V$ ,<br>$PW \le 10us$ ,<br>$T_J = 25$ °C |

| $I_{O+}^{(\dagger)(\dagger\dagger)}$  | Output high short circuit pulsed current                                         | 1.2 | _   | _   |       | $V_O = 0 V$ ,<br>PW $\leq 10 \text{ us}$          |

| I <sub>O-</sub> (†)(††)               | Output low short circuit pulsed current                                          | 1.5 | _   |     |       | $V_O = 15 V$ ,<br>PW $\leq 10 \text{ us}$         |

<sup>(†)</sup> Guaranteed by design

<sup>(††)</sup> I<sub>O+</sub> and I<sub>O-</sub> decrease with rising temperature

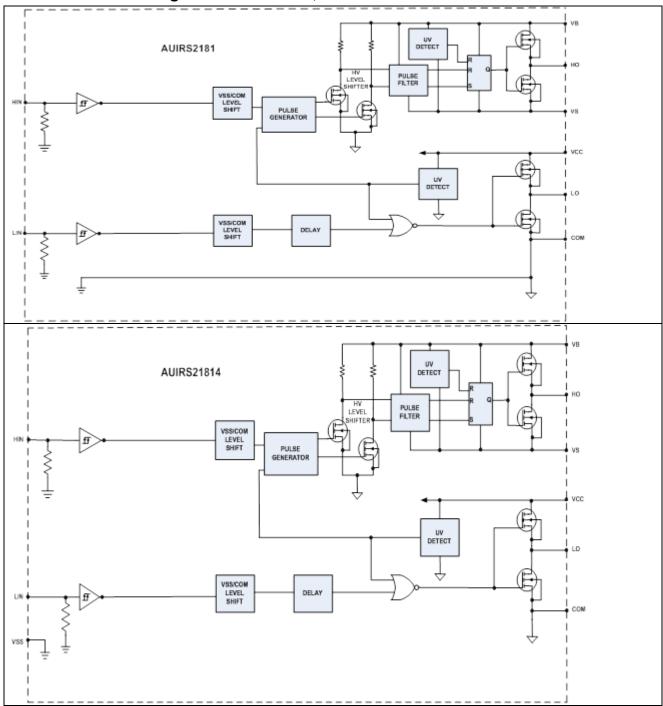

# Functional Block Diagrams: AUIRS2181, AUIRS21814

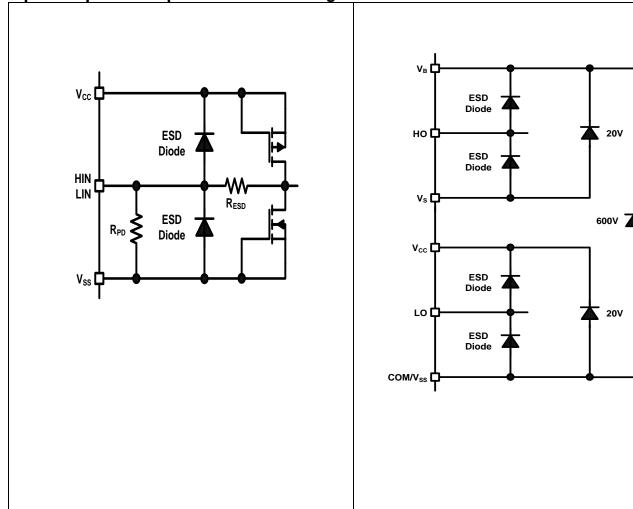

Input/Output Pin Equivalent Circuit Diagrams: AUIRS2181S

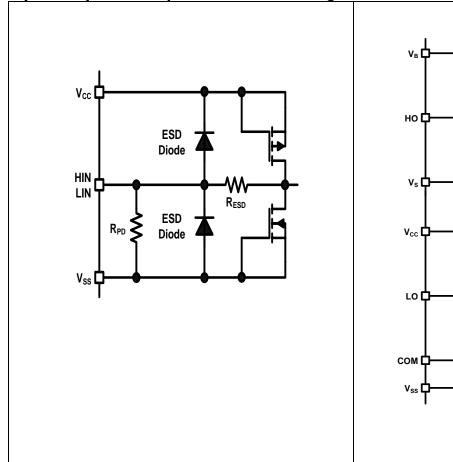

Input/Output Pin Equivalent Circuit Diagrams: AUIRS21814S

# Lead Definitions: AUIRS2181(4)S

| Symbol   | Description                                                 |

|----------|-------------------------------------------------------------|

| HIN      | Logic input for high-side gate driver output (HO), in phase |

| LIN      | Logic input for low-side driver output (LO), in phase       |

| $V_{SS}$ | Logic ground (AUIRS21814 only)                              |

| $V_B$    | High-side floating supply                                   |

| НО       | High-side gate drive output                                 |

| $V_S$    | High-side floating supply return                            |

| $V_{CC}$ | Low-side and logic fixed supply                             |

| LO       | Low-side gate drive output                                  |

| COM      | Low-side return                                             |

# Lead Assignments: AUIRS2181(4)S

## **Application Information and Additional Details**

Figure 1. Input/Output Timing Diagram

Figure 2. Switching Time Waveform Definitions

Figure 3. Delay Matching Waveform Definitions

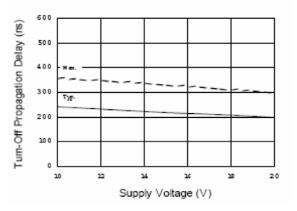

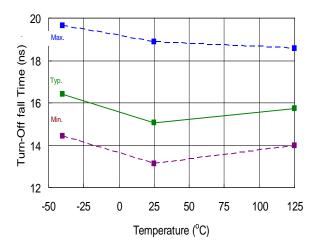

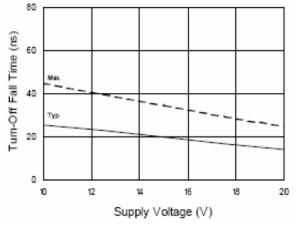

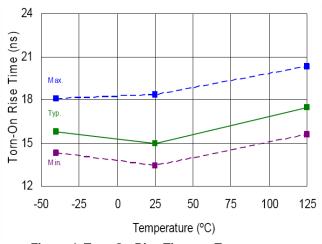

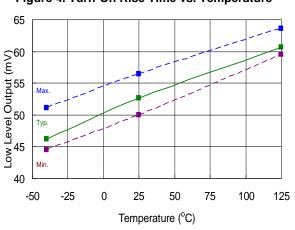

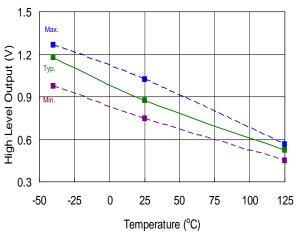

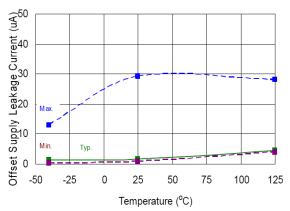

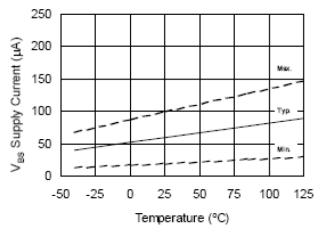

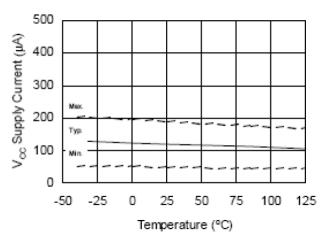

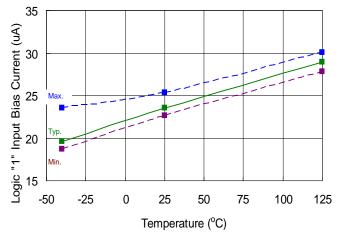

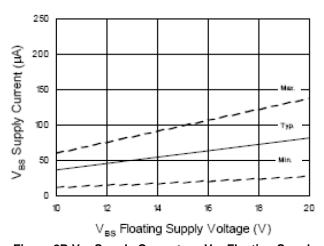

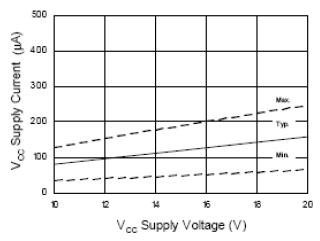

### Parameter Trends vs. Temperature and vs. Supply Voltage

Figures of this chapter provide information on the experimental performance of the AUIRS2181(4)S HVIC. The line plotted in each figure is generated from actual lab data.

A large number of individual samples were tested at three temperatures (-40  $^{\circ}$ C, 25  $^{\circ}$ C, and 125  $^{\circ}$ C) in order to generate the experimental curve. The line consists of three data points (one data point at each of the tested temperatures) that have been connected together to illustrate the understood trend. The individual data points on the Typ. curve were determined by calculating the averaged experimental value of the parameter (for a given temperature).

A different set of individual samples was used to generate curves of parameter trends vs. supply voltage.

Figure 1A. Turn-On Propagation Delay vs. Temperature

Figure 1B. Turn-On Propagation Delay vs. Supply Voltage

Figure 2A. Turn-Off Propagation Delay vs. Temperature

Figure 2B. Turn-Off Propagation Delay vs. Supply Voltage

Figure 3A. Turn-Off Fall Time vs. Temperature

Figure 3B. Turn-Off Fall Time vs. Supply Voltage

Figure 4. Turn-On Rise Time vs. Temperature

Figure 6. Low Level Output vs. Temperature

Figure 5. High Level Output Voltage vs. Temperature (Io = 0mA)

Figure 7. Offset Supply Leakage Current vs. Temperature

Figure 8A V<sub>BS</sub> Supply Current vs. Temperature

Figure 9A V<sub>CC</sub> Supply Current vs Temperature

Figure 10. Logic "1" Input Bias vs Temperature

Figure 8B  $V_{BS}$  Supply Current vs.  $V_{BS}$  Floating Supply Voltage

Figure 9B V<sub>CC</sub> Supply Current vs. V<sub>CC</sub> Supply Voltage

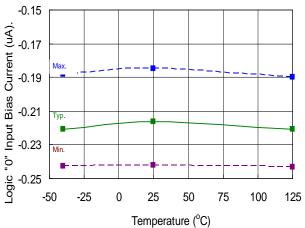

Figure 11. Logic "0" Input Bias vs Temperature

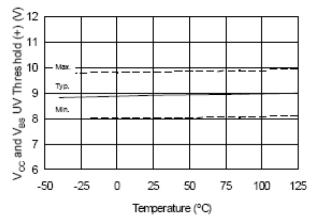

Figure 12. V<sub>CC</sub> and V<sub>BS</sub> Undervoltage Threshold(+) vs Temperature

Figure 14A. Output Source Current vs Temperature

Figure 15A. Output Sink Current vs Temperature

Figure 13.  $V_{CC}$  and  $V_{BS}$  Undervoltage Threshold(-) vs Temperature

Figure 14B. Output Source Current vs Supply Voltage

Figure 15B. Output Sink Current vs Supply Voltage

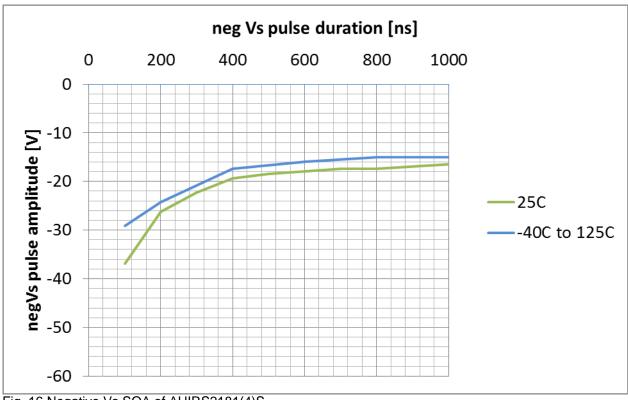

#### **Negative Vs Safety Operating Area (negVs SOA)**

There could be conditions in which Vs node falls below (i.e. negative) VSS/COM nodes (e.g. because of wrong system layout). This condition should be avoided because it could bring to uncontrolled behavior of the driver.

The negVs SOA identifies the energy of negative Vs pulses at which the driver can withstand; pulse energy is identified as the product of pulse duration by its amplitude. Fig. 16 shows the negVs SOA of AUIRS2181(4)S at both ambient and over temperature conditions. Test conditions were VCC=VBS=15V referenced to VSS=COM.

Even though the AUIRS2181(4)S has been designed and tested to handle these negative VS transient conditions, it is highly recommended that the circuit designer always limit the negative VS transients as much as possible by careful PCB layout and component use.

Fig. 16 Negative Vs SOA of AUIRS2181(4)S.

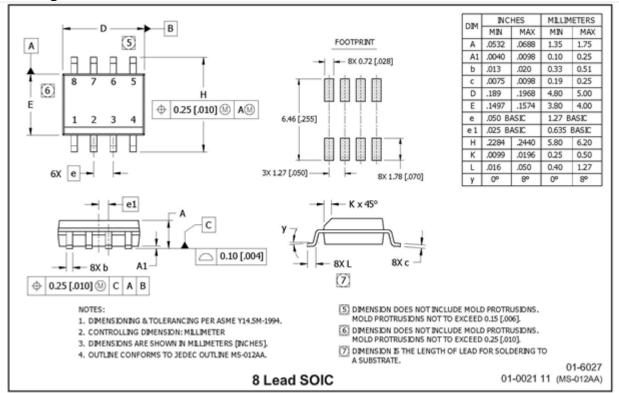

Package Details: SOIC8

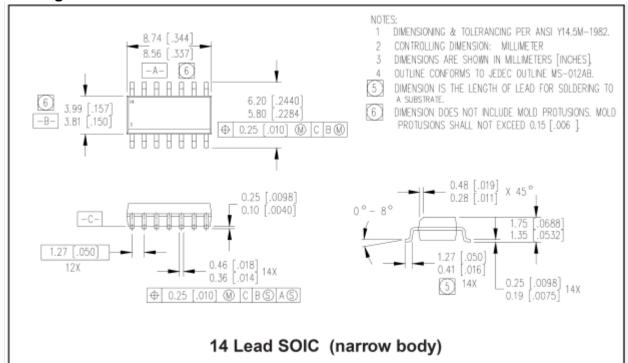

### Package Details: SOIC14N

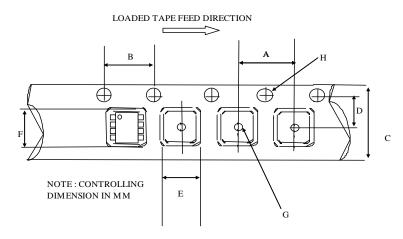

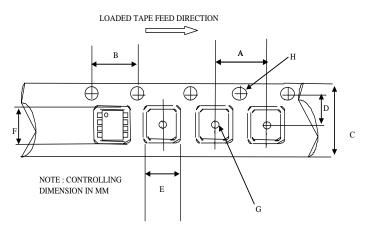

## **Tape and Reel Details: SOIC8**

#### CARRIER TAPE DIMENSION FOR 8SOICN

|      | Metric Im |       | Imp   | erial |

|------|-----------|-------|-------|-------|

| Code | Min       | Max   | Min   | Max   |

| Α    | 7.90      | 8.10  | 0.311 | 0.318 |

| В    | 3.90      | 4.10  | 0.153 | 0.161 |

| С    | 11.70     | 12.30 | 0.46  | 0.484 |

| D    | 5.45      | 5.55  | 0.214 | 0.218 |

| E    | 6.30      | 6.50  | 0.248 | 0.255 |

| F    | 5.10      | 5.30  | 0.200 | 0.208 |

| G    | 1.50      | n/a   | 0.059 | n/a   |

| Н    | 1.50      | 1.60  | 0.059 | 0.062 |

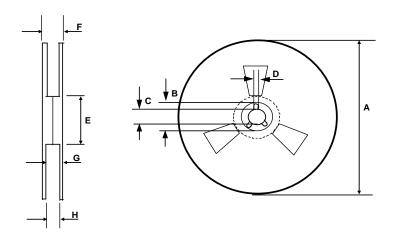

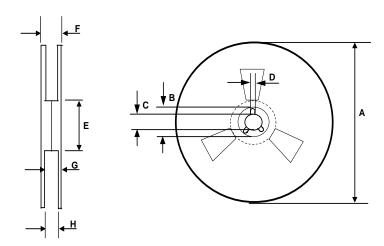

#### **REEL DIMENSIONS FOR 8SOICN**

|      | Me     | etric  | Imp    | erial  |

|------|--------|--------|--------|--------|

| Code | Min    | Max    | Min    | Max    |

| Α    | 329.60 | 330.25 | 12.976 | 13.001 |

| В    | 20.95  | 21.45  | 0.824  | 0.844  |

| С    | 12.80  | 13.20  | 0.503  | 0.519  |

| D    | 1.95   | 2.45   | 0.767  | 0.096  |

| E    | 98.00  | 102.00 | 3.858  | 4.015  |

| F    | n/a    | 18.40  | n/a    | 0.724  |

| G    | 14.50  | 17.10  | 0.570  | 0.673  |

| Н    | 12.40  | 14.40  | 0.488  | 0.566  |

## **Tape and Reel Details: SOIC14N**

#### CARRIER TAPE DIMENSION FOR 14SOICN

|      | Me    | etric | Imp   | erial |

|------|-------|-------|-------|-------|

| Code | Min   | Max   | Min   | Max   |

| Α    | 7.90  | 8.10  | 0.311 | 0.318 |

| В    | 3.90  | 4.10  | 0.153 | 0.161 |

| С    | 15.70 | 16.30 | 0.618 | 0.641 |

| D    | 7.40  | 7.60  | 0.291 | 0.299 |

| E    | 6.40  | 6.60  | 0.252 | 0.260 |

| F    | 9.40  | 9.60  | 0.370 | 0.378 |

| G    | 1.50  | n/a   | 0.059 | n/a   |

| Н    | 1.50  | 1.60  | 0.059 | 0.062 |

REEL DIMENSIONS FOR 14SOICN

|        | Me     | etric  | Imp    | erial  |  |

|--------|--------|--------|--------|--------|--|

| Code   | Min    | Max    | Min    | Max    |  |

| Α      | 329.60 | 330.25 | 12.976 | 13.001 |  |

| В      | 20.95  | 21.45  | 0.824  | 0.844  |  |

| С      | 12.80  | 13.20  | 0.503  | 0.519  |  |

| D      | 1.95   | 2.45   | 0.767  | 0.096  |  |

| E<br>F | 98.00  | 102.00 | 3.858  | 4.015  |  |

|        | n/a    | 22.40  | n/a    | 0.881  |  |

| G      | 18.50  | 21.10  | 0.728  | 0.830  |  |

| Н      | 16.40  | 18.40  | 0.645  | 0.724  |  |

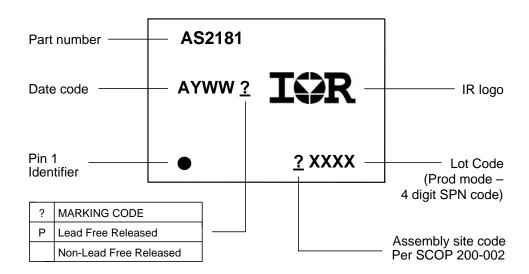

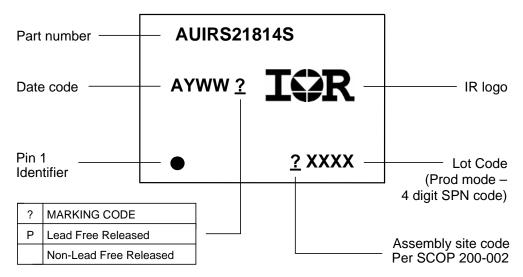

### **Part Marking Information**

#### SOIC8:

#### SOIC14N:

# **Qualification Information**<sup>†</sup>

| Qualification Level        |                      | Automotive (per AEC-Q100††)  Comments: This family of ICs has passed an Automotive qualification. IR's Industrial and Consumer qualification level is granted by extension of the higher Automotive level. |                                                        |

|----------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Moisture Sensitivity Level |                      | SOIC8                                                                                                                                                                                                      | MSL3 <sup>†††</sup> 260°C<br>(per IPC/JEDEC J-STD-020) |

|                            |                      | SOIC14N                                                                                                                                                                                                    | MSL3 <sup>†††</sup> 260°C<br>(per IPC/JEDEC J-STD-020) |

| ESD                        | Machine Model        | Class M2 (Pass +/-150V)<br>(per AEC-Q100-003)                                                                                                                                                              |                                                        |

|                            | Human Body Model     | Class H1B (Pass +/-1000V)<br>(per AEC-Q100-002)                                                                                                                                                            |                                                        |

|                            | Charged Device Model | Class C4 (Pass +/-1000V)<br>(per AEC-Q100-011)                                                                                                                                                             |                                                        |

| IC Latch-Up Test           |                      | Class II, Level A <sup>††††</sup><br>(per AEC-Q100-004)                                                                                                                                                    |                                                        |

| RoHS Compliant             |                      | Yes                                                                                                                                                                                                        |                                                        |

- † Qualification standards can be found at International Rectifier's web site <a href="http://www.irf.com/">http://www.irf.com/</a>

- †† Exceptions to AEC-Q100 requirements are noted in the qualification report.

- ††† Higher MSL ratings may be available for the specific package types listed here. Please contact your International Rectifier sales representative for further information.

- †††† HIN, LIN Class II Level B at 80mA per JESD78.

### **IMPORTANT NOTICE**

Unless specifically designated for the automotive market, International Rectifier Corporation and its subsidiaries (IR) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or services without notice. Part numbers designated with the "AU" prefix follow automotive industry and / or customer specific requirements with regards to product discontinuance and process change notification. All products are sold subject to IR's terms and conditions of sale supplied at the time of order acknowledgment.

IR warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with IR's standard warranty. Testing and other quality control techniques are used to the extent IR deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

IR assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using IR components. To minimize the risks with customer products and applications, customers should provide adequate design and operating safeguards.

Reproduction of IR information in IR data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alterations is an unfair and deceptive business practice. IR is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of IR products or serviced with statements different from or beyond the parameters stated by IR for that product or service voids all express and any implied warranties for the associated IR product or service and is an unfair and deceptive business practice. IR is not responsible or liable for any such statements.

IR products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of the IR product could create a situation where personal injury or death may occur. Should Buyer purchase or use IR products for any such unintended or unauthorized application, Buyer shall indemnify and hold International Rectifier and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that IR was negligent regarding the design or manufacture of the product.

IR products are neither designed nor intended for use in military/aerospace applications or environments unless the IR products are specifically designated by IR as military-grade or "enhanced plastic." Only products designated by IR as military-grade meet military specifications. Buyers acknowledge and agree that any such use of IR products which IR has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

IR products are neither designed nor intended for use in automotive applications or environments unless the specific IR products are designated by IR as compliant with ISO/TS 16949 requirements and bear a part number including the designation "AU". Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, IR will not be responsible for any failure to meet such requirements.

For technical support, please contact IR's Technical Assistance Center http://www.irf.com/technical-info/

#### **WORLD HEADQUARTERS:**

233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105

**Revision History**

| Date                          | Comment                                                                                                                                                                                               |  |  |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 04/29/08                      | Draft                                                                                                                                                                                                 |  |  |

| 5/6/08                        | Converted to new automotive format                                                                                                                                                                    |  |  |

| 9/30/08                       | Reviewed and updated various missing information                                                                                                                                                      |  |  |

| 10/01/08                      | Inserted Input/Output Pin Equivalent Circuit Diagram                                                                                                                                                  |  |  |

| Feb, 10 <sup>th</sup> , 2009  | Typ application list and other minor changes                                                                                                                                                          |  |  |

| Feb. 11, 2009                 | Removed PDIP package versions from datasheet                                                                                                                                                          |  |  |

| Aug. 4, 2009                  | Updated qualification information, characterization curves                                                                                                                                            |  |  |

| Aug. 11, 2009                 | Updated plot, removed characterization graphs, changes package type info                                                                                                                              |  |  |

| Aug. 13, 2009                 | Updated VIH/VIL graphs                                                                                                                                                                                |  |  |

| Sep 23 <sup>rd</sup> , 2009   | Typ appl. Section update; Rearranged graphs with temperature and supply characteristic, updated marking detail with p/n; added ESD passing voltage; update LU test passing current from 40mA to 80mA. |  |  |

| Dec. 16, 09                   | Changed Iqcc/Iqbs min to 15uA; added Important Notice page; changed ton typ=160ns; toff typ=200ns; tr typ=15ns; tf typ=15ns                                                                           |  |  |

| Feb. 24, 2010                 | Page 6: Added I <sub>O25+</sub> and I <sub>O25-</sub> specification and the notes                                                                                                                     |  |  |

| Jul. 27, 2010                 | clamp diode values changed from 25V into 20V (in-out pin eq. circ. diagrams)                                                                                                                          |  |  |

| Mar 07, 2012                  | Input zener clamp note deleted in recommended op cond                                                                                                                                                 |  |  |

| Sept. 30 <sup>th</sup> , 2013 | Added negVs SOA                                                                                                                                                                                       |  |  |

| Oct. 04 <sup>th</sup> , 2013  | Adapted to new format                                                                                                                                                                                 |  |  |

| Jan. 10, 2014                 | Updated datasheet to display respective page number on bottom left corner of every page                                                                                                               |  |  |