DLPC8445 DLPS253 – SEPTEMBER 2024

# **DLPC8445 High-Resolution Controller**

### **1** Features

- DLPC8445 controller using the DLP472TP digital micromirror device (DMD) supports

- Up to 4K UHD at 60Hz

- Up to 1080p at 240Hz (2D) and 120Hz (3D)

- Provides single V-by-One<sup>®</sup> HS video input port with one, two, four, or eight lanes

- Up to 600MHz Pixel clock support

- Up to 3.0Gbps per input transmission rate

- Input formats supported

- RGB and YCbCr

- 4:4:4, 4:2:2

- Internal Arm<sup>®</sup> processor

- 52 configurable GPIOs

- PWM generator

- Capture and delay timers

- USB 2.0 high-speed controller

- SPI controllers

- I<sup>2</sup>C controllers

- UART and interrupt controllers

- Warping engine

- 1D and 2D keystone correction

- Embedded partial frame memory for video processing

- Additional image processing

- Variable refresh rate (VRR) support

- DynamicBlack

- HDR10 (PQ and HLG) support

- Frame rate multiplication

- Color coordinate adjustment

- White color temperature adjustment

- Programmable degamma

- Read-side spatial-temporal multiplexing

- Integrated support for 3-D display

- Rolling buffer for reduced frame latency

- Splash screen display

- Serial flash for µP and PWM sequences

- System control

- DMD power and reset driver control

- DMD horizontal and vertical image flip

- JTAG boundary scan test support

- Supports LED-based projector systems

### **2** Applications

- Mobile smart TV

- Mobile projector

- Digital signage

- Laser TV

### **3 Description**

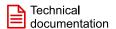

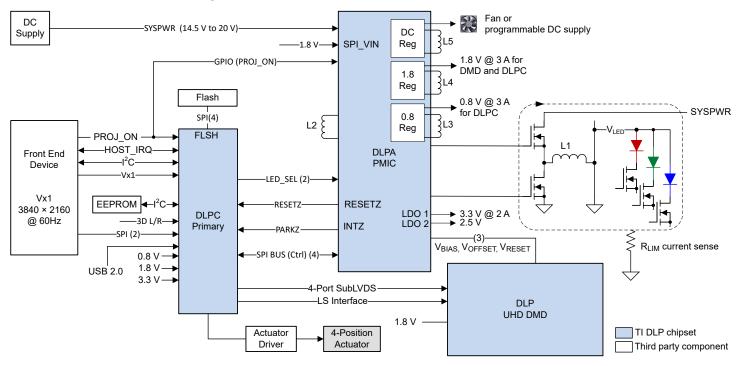

The DLPC8445 is a digital display controller for the TI DLP<sup>®</sup> Products 4K UHD display chipset. The display controller, together with the DLP472TP DMD and the DLPA3085 power management integrated circuit, comprise the chipset. This solution fits display systems that require high resolution and high brightness in a small form factor. For reliable operation, the DLPC8445 display controller must always be used with the DLP472TP DMD and the DLPA3085 PMIC per application.

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE<br>SIZE |

|-------------|------------------------|-----------------|

| DLPC8445AMD | FCCSP (484)            | 9.00mm × 9.00mm |

(1) For more information, see the *Mechanical, Packaging, and Orderable* sections.

#### 4K UHD Display Chipset

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# **Table of Contents**

| 1 | Features1                                                 |

|---|-----------------------------------------------------------|

| 2 | Applications1                                             |

|   | Description1                                              |

| 4 | Pin Configuration and Functions                           |

|   | 4.1 Initialization, Board Level Test, and Debug3          |

|   | 4.2 V-by-One Interface Input Data and Control5            |

|   | 4.3 FPD Link Port(s) Input Data and Control (Not          |

|   | Supported in DLPC8445)6                                   |

|   | 4.4 DSI Input Data and Clock (Not Supported in            |

|   | DLPC8445)7                                                |

|   | 4.5 DMD SubLVDS Interface                                 |

|   | 4.6 DMD Reset and Low Speed Interfaces10                  |

|   | 4.7 Flash Interface10                                     |

|   | 4.8 Peripheral Interfaces11                               |

|   | 4.9 GPIO Peripheral Interface12                           |

|   | 4.10 Clock and PLL Support16                              |

|   | 4.11 Power and Ground17                                   |

|   | 4.12 I/O Type Subscript Definition                        |

| _ | 4.13 Internal Pullup and Pulldown Characteristics19       |

| 5 | Specifications                                            |

|   | 5.1 Absolute Maximum Ratings                              |

|   | 5.2 ESD Ratings                                           |

|   | 5.3 Recommended Operating Conditions                      |

|   | 5.4 Thermal Information                                   |

|   |                                                           |

|   | 5.6 Pin Electrical Characteristics                        |

|   |                                                           |

|   | 5.8 DMD Low Speed Interface Electrical<br>Characteristics |

|   | 5.9 V-by-One Interface Electrical Characteristics         |

|   | 5.10 USB Electrical Characteristics                       |

|   | 5.11 System Oscillator Timing Requirements                |

|   | 5.12 Power Supply and Reset Timing Requirements           |

|   | 5.13 V-by-One Interface General Timing                    |

|   | Requirements                                              |

|   | 5.14 Flash Interface Timing Requirements                  |

|   | 5.15 Source Frame Timing Requirements                     |

|   | ······································                    |

| 5.16 Synchronous Serial Port Interface Timing       |      |

|-----------------------------------------------------|------|

| Requirements                                        |      |

| 5.17 I2C Interface Timing Requirements              | . 37 |

| 5.18 Programmable Output Clock Timing               |      |

| Requirements                                        | . 38 |

| 5.19 JTAG Boundary Scan Interface Timing            |      |

| Requirements (Debug Only)                           | .39  |

| 5.20 DMD Low Speed Interface Timing Requirements    | .40  |

| 5.21 DMD SubLVDS Interface Timing Requirements      | . 40 |

| 6 Detailed Description                              | .41  |

| 6.1 Overview                                        |      |

| 6.2 Functional Block Diagram                        | .41  |

| 6.3 Feature Description                             |      |

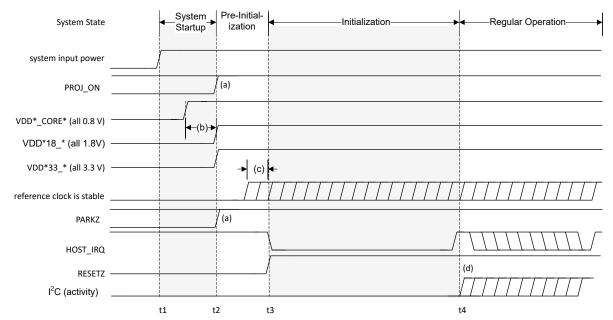

| 7 Power Supply Recommendations                      |      |

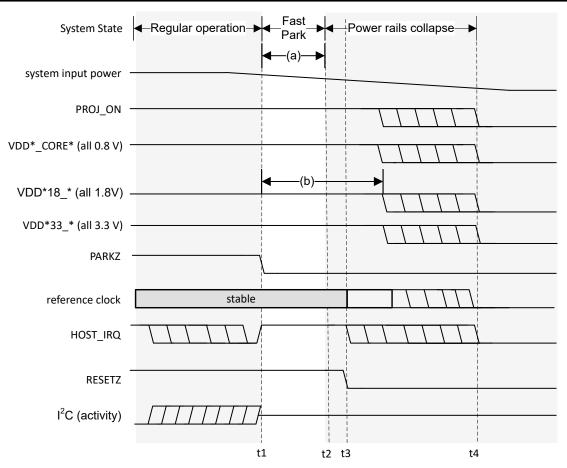

| 7.1 System Power-Up and Power-Down Sequence         |      |

| 7.2 DMD Fast Park Control (PARKZ)                   | .55  |

| 7.3 Power Supply Management                         |      |

| 7.4 Hot Plug Usage                                  | .56  |

| 7.5 Power Supplies for Unused Input Source          |      |

| Interfaces                                          |      |

| 7.6 Power Supplies                                  |      |

| 8 Layout                                            |      |

| 8.1 Layout Guidelines                               |      |

| 8.2 Thermal Considerations                          |      |

| 9 Device and Documentation Support                  |      |

| 9.1 Third-Party Products Disclaimer                 |      |

| 9.2 Documentation Support                           |      |

| 9.3 Receiving Notification of Documentation Updates |      |

| 9.4 Support Resources                               |      |

| 9.5 Device Nomenclature                             |      |

| 9.6 Trademarks                                      |      |

| 9.7 Electrostatic Discharge Caution                 |      |

| 9.8 Glossary                                        |      |

| 10 Revision History                                 | . 66 |

| 11 Mechanical, Packaging, and Orderable             | 00   |

| Information                                         | 00   |

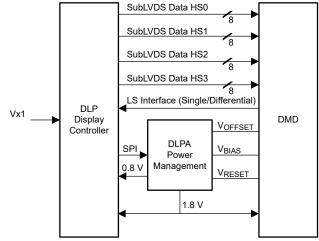

# **4** Pin Configuration and Functions

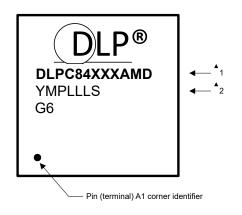

Figure 4-1. AMD Package 484-Pin FCCSP Top View

### 4.1 Initialization, Board Level Test, and Debug

| PIN      |     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. |                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PROJ_ON  | AP2 | 11                 | Normal mirror parking request (active low): To be driven by the PROJ_ON output of the host. A logic low on this signal causes the Controller to PARK the DMD, but it does not power down the DMD (the DLPA does that instead). The minimum high time is 200ms. The minimum low time is 200ms.                                                                                                                                                |

| RESETZ   | P2  | 11                 | Power-on reset (active low input with a hysteresis buffer). Self-configuration starts when a low-to-high transition is detected on RESETZ. All controller power and clocks must be stable before this reset is de-asserted. No signals are in their active state while RESETZ is asserted. This pin is typically connected to the RESETZ pin of the DLPA PMIC.                                                                               |

| PARKZ    | AR1 | 11                 | DMD fast park control (active low Input with a hysteresis buffer). This signal<br>is used to quickly park the DMD when loss of power is imminent. The longest<br>lifetime of the DMD may not be achieved with the fast park operation; therefore,<br>this signal is intended to only be asserted when a normal park operation is unable<br>to be completed. The PARKZ signal is typically provided from the DLPA interrupt<br>output signal. |

| JTAGTCK  | V24 | 12                 | JTAG and ARM-ICE Serial Data Clock. This signal is shared between JTAG and ARM-ICE (TI test only), operation. Includes a weak internal pulldown                                                                                                                                                                                                                                                                                              |

| JTAGTMS1 | U23 | 12                 | JTAG Test Mode Select. Includes a weak internal pullup                                                                                                                                                                                                                                                                                                                                                                                       |

| JTAGTMS2 | W25 | 12                 | ARM-ICE Test Mode Select<br>For normal operation, this pin must be left open or unconnected. Includes a weak<br>internal pullup                                                                                                                                                                                                                                                                                                              |

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

DLPC8445 DLPS253 – SEPTEMBER 2024

| PIN           |      | 10 (1)               | DECODIDION                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME          | NO.  | – I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                          |

| JTAGTRSTZ     | AA25 | 12                   | JTAG, ARM-ICE Reset.<br>For normal operation, this pin must be pulled to ground through an external resistor with value $8k\Omega$ or less. Failure to pull this pin low during normal operation causes start-up and initialization problems.<br>For JTAG Boundary Scan and ARM-ICE Debug operation, this pin must be pulled up or left disconnected. Includes a weak internal pullup and hysteresis |

| JTAGTDI       | Y24  | 12                   | JTAG, ARM-ICE, and CPU MBIST: Serial Data In. Includes weak internal pullups                                                                                                                                                                                                                                                                                                                         |

| JTAGTDO1      | V22  | B14                  | JTAG Serial Data Out                                                                                                                                                                                                                                                                                                                                                                                 |

| JTAGTDO2      | W23  | B14                  | ARM-ICE Serial Data Out. For normal operation, this pin requires an external pullup resistor with a value of $\leq 9.15$ k $\Omega$ .                                                                                                                                                                                                                                                                |

| ETM_TRACECLK  | U25  | O14                  | Reserved Pin, must be left unconnected.                                                                                                                                                                                                                                                                                                                                                              |

| ETM_TRACECTL  | T24  | O14                  | Reserved Pin, must be left unconnected.                                                                                                                                                                                                                                                                                                                                                              |

| TSTPT_0       | T22  | B14                  | Test pin 0<br>This pin has an internal pulldown and may require an external pullup resistor (no pullup: Normal Boot, pullup: Wait for Host commands) with a value of $\leq 9.15 k\Omega$ .                                                                                                                                                                                                           |

| TSTPT_1       | R25  | B14                  | Test pin 1<br>This pin has an internal pulldown for Normal Boot operation.                                                                                                                                                                                                                                                                                                                           |

| TSTPT_2       | R23  | B14                  | Test pin 2<br>This pin has an internal pulldown and may require an external pullup resistor (no pullup: I <sup>2</sup> C address = 0x36, pullup: I <sup>2</sup> C address = 0x34) with a value of $\leq$ 9.15k $\Omega$ .                                                                                                                                                                            |

| TSTPT_3       | P24  | B14                  | Test pin 3<br>This pin has an internal pulldown and may require an external pullup resistor (no<br>pullup: Host interface is USB or I <sup>2</sup> C, pullup: Host interface is I <sup>2</sup> C only) with a value<br>of $\leq 9.15$ k $\Omega$ .                                                                                                                                                   |

| TSTPT_4       | N25  | B14                  | Test pin 4<br>This pin has an internal pulldown resistor.                                                                                                                                                                                                                                                                                                                                            |

| TSTPT_5       | P22  | B14                  | Test pin 5<br>This pin has an internal pulldown resistor.                                                                                                                                                                                                                                                                                                                                            |

| TSTPT_6       | N23  | B14                  | Test pin 6<br>This pin has an internal pulldown resistor.                                                                                                                                                                                                                                                                                                                                            |

| TSTPT_7       | M24  | B14                  | Test pin 7<br>This pin has an internal pulldown resistor.                                                                                                                                                                                                                                                                                                                                            |

| GPTP0         | AA23 | B13                  | General Purpose Test pin 0<br>This pin has an internal pulldown and may require an external pullup resistor (no pullup: external crystal, pullup: external clock) with a value of $\leq 9.15 k\Omega$ .                                                                                                                                                                                              |

| GPTP1         | AB22 | B13                  | General Purpose Test pin 1<br>This pin has an internal pulldown resistor.                                                                                                                                                                                                                                                                                                                            |

| GPTP2         | AC25 | B13                  | General Purpose Test pin 2<br>This pin has an internal pulldown resistor.                                                                                                                                                                                                                                                                                                                            |

| ATB_0_H       | AH4  | PWR                  | Reserved Pin, must be left unconnected.                                                                                                                                                                                                                                                                                                                                                              |

| ATB_1_H       | AJ5  | PWR                  | Reserved Pin, must be left unconnected.                                                                                                                                                                                                                                                                                                                                                              |

| ATEST         | G13  | PWR                  | Reserved Pin, must be left unconnected.                                                                                                                                                                                                                                                                                                                                                              |

| CAP_VDDS_FLSH | AD22 | PWR                  | External bias capacitance                                                                                                                                                                                                                                                                                                                                                                            |

| CAP_VDDS_INTF | AJ21 | PWR                  | External bias capacitance                                                                                                                                                                                                                                                                                                                                                                            |

| IFORCE        | L3   | PWR                  | Manufacturing use only. Must be tied to ground.                                                                                                                                                                                                                                                                                                                                                      |

| VSENSE        | K2   | PWR                  | Reserved Pin, must be left unconnected.                                                                                                                                                                                                                                                                                                                                                              |

| HWTEST_EN     | Y22  | 12                   | Reserved Pin.<br>This signal must be connected directly to ground on the PCB for normal operation<br>Includes a weak internal pulldown and hysteresis                                                                                                                                                                                                                                                |

(1) See Section 4.12 for more information on I/O definitions.

#### 4.2 V-by-One Interface Input Data and Control

| PIN         |      | I/O <sup>(1)</sup> | DESCRIPTION (2) (3) (4)                                                                                                                                                                                                                            |

|-------------|------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.  |                    | DESCRIPTION                                                                                                                                                                                                                                        |

| P1_VX1_D0_P | AV8  |                    |                                                                                                                                                                                                                                                    |

| P1_VX1_D0_N | AU9  |                    |                                                                                                                                                                                                                                                    |

| P1_VX1_D1_P | BB8  |                    |                                                                                                                                                                                                                                                    |

| P1_VX1_D1_N | AY8  |                    |                                                                                                                                                                                                                                                    |

| P1_VX1_D2_P | BA9  |                    |                                                                                                                                                                                                                                                    |

| P1_VX1_D2_N | AW9  |                    |                                                                                                                                                                                                                                                    |

| P1_VX1_D3_P | BB10 |                    |                                                                                                                                                                                                                                                    |

| P1_VX1_D3_N | AY10 | 15                 | V by One interface data lance                                                                                                                                                                                                                      |

| P1_VX1_D4_P | BA11 | 15                 | V-by-One interface data lanes                                                                                                                                                                                                                      |

| P1_VX1_D4_N | AW11 |                    |                                                                                                                                                                                                                                                    |

| P1_VX1_D5_P | AV12 |                    |                                                                                                                                                                                                                                                    |

| P1_VX1_D5_N | AU13 |                    |                                                                                                                                                                                                                                                    |

| P1_VX1_D6_P | BB12 |                    |                                                                                                                                                                                                                                                    |

| P1_VX1_D6_N | AY12 |                    |                                                                                                                                                                                                                                                    |

| P1_VX1_D7_P | BA13 |                    |                                                                                                                                                                                                                                                    |

| P1_VX1_D7_N | AW13 |                    |                                                                                                                                                                                                                                                    |

| P1_HTPDN    | AN3  | O10                | V-by-One interface hot plug detects (controller receiver pulls this signal low to indicate its presence to the transmitter). This signal is an open drain at the controller output. A pullup resistor is required at the transmitter.              |

| P1_LOCKN    | AM4  | O10                | A V-by-One interface clock detects lock (controller receiver pulls this signal low to indicate clock extraction lock to the transmitter). This signal is an open drain at the controller output. A pullup resistor is required at the transmitter. |

| P1_RREF     | AU11 | PWR                | V-by-One bias resistor input                                                                                                                                                                                                                       |

(1) See I/O Type Subscript Definition for more information on I/O definitions.

(2) The system supports 1-lane, 2-lane, 4-lane, or 8-lane operation, based on the bandwidth requirement of the input source. The inputs for any unused data lanes must be left open.

(3) The V-by-One port supports limited lane remapping to help optimize board layout. The details are described in V-by-One Interface.

(4) In this document, the terms V-by-One and Vx1 are used interchangeably.

### 4.3 FPD Link Port(s) Input Data and Control (Not Supported in DLPC8445)

| PIN           |      | I/O <sup>(1)</sup> | DESCRIPTION <sup>(2)</sup> (3) (4) |

|---------------|------|--------------------|------------------------------------|

| NAME          | NO.  |                    | DESCRIPTION                        |

| P2A_LVDS_C_P  | BA17 | 14                 | Reserved                           |

| P2A_LVDS_C_N  | AW17 | 14                 |                                    |

| P2A_LVDS_D0_P | BA15 | 14                 |                                    |

| P2A_LVDS_D0_N | AW15 | 14                 |                                    |

| P2A_LVDS_D1_P | BB16 | 14                 |                                    |

| P2A_LVDS_D1_N | AY16 | 14                 |                                    |

| P2A_LVDS_D2_P | AV16 | 14                 | Reserved                           |

| P2A_LVDS_D2_N | AU15 | 14                 | - Kesel veu                        |

| P2A_LVDS_D3_P | BB18 | 14                 |                                    |

| P2A_LVDS_D3_N | AY18 | 14                 |                                    |

| P2A_LVDS_D4_P | AV18 | 14                 |                                    |

| P2A_LVDS_D4_N | AU17 | 14                 |                                    |

| P2A_LVDS_RPI  | AT16 | PWR                | Reserved                           |

| P2B_LVDS_C_P  | BA21 | 14                 | Reserved                           |

| P2B_LVDS_C_N  | AW21 | 14                 | - Kesel veu                        |

| P2B_LVDS_D0_P | BB20 | 14                 |                                    |

| P2B_LVDS_D0_N | AY20 | 14                 |                                    |

| P2B_LVDS_D1_P | AV20 | 14                 |                                    |

| P2B_LVDS_D1_N | AU19 | 14                 |                                    |

| P2B_LVDS_D2_P | AV22 | 14                 | Reserved                           |

| P2B_LVDS_D2_N | AU21 | 14                 | - Kesel veu                        |

| P2B_LVDS_D3_P | BB22 | 14                 |                                    |

| P2B_LVDS_D3_N | AY22 | 14                 |                                    |

| P2B_LVDS_D4_P | BA23 | 14                 |                                    |

| P2B_LVDS_D4_N | AW23 | 14                 |                                    |

| P2B_LVDS_RPI  | AT20 | PWR                | Reserved                           |

(1) See Section 4.12 for more information on I/O definitions.

(2) Throughout this document, the terms FPD and FPD Link refer to FPD Link I.

(3) Tie the inputs for any unused port(s) to ground, or pull to ground through an external resistor.

(4) If only one of these two ports is needed, either port can be used, with the other port to be treated as an unused port.

### 4.4 DSI Input Data and Clock (Not Supported in DLPC8445)

| PIN           |     | I/O <sup>(1)</sup> | DESCRIPTION <sup>(2)</sup> |

|---------------|-----|--------------------|----------------------------|

| NAME          | NO. |                    |                            |

| P3_DSI_C_P    | BB6 | 16                 | Reserved                   |

| P3_DSI_C_N    | AY6 | 16                 |                            |

| P3_DSI_D0_P   | BA5 | 16                 |                            |

| P3_DSI_D0_N   | AW5 | 16                 |                            |

| P3_DSI_D1_P   | BB4 | 16                 |                            |

| P3_DSI_D1_N   | AY4 | 16                 | Reserved                   |

| P3_DSI_D2_P   | AV4 | 16                 |                            |

| P3_DSI_D2_N   | AU5 | 16                 |                            |

| P3_DSI_D3_P   | BA3 | 16                 |                            |

| P3_DSI_D3_N   | AW3 | 16                 |                            |

| P3_DSI_RCALIB | AV6 | PWR                | Reserved                   |

(1) See Section 4.12 for more information on I/O definitions.

(2) Tie the inputs for any unused port(s) to ground, or pull to ground through an external resistor.

### 4.5 DMD SubLVDS Interface

| PIN              |     | I/O <sup>(1)</sup> | DESCRIPTION                       |

|------------------|-----|--------------------|-----------------------------------|

| NAME             | NO. |                    | DESCRIPTION                       |

| DMD_HS0_CLK_P    | B6  | O15                | Channel 0 DMD SubLVDS clock lane  |

| DMD_HS0_CLK_N    | D6  | O15                |                                   |

| DMD_HS0_WDATA0_P | A3  | O15                |                                   |

| DMD_HS0_WDATA0_N | C3  | O15                |                                   |

| DMD_HS0_WDATA1_P | F4  | O15                |                                   |

| DMD_HS0_WDATA1_N | E5  | O15                |                                   |

| DMD_HS0_WDATA2_P | B4  | O15                |                                   |

| DMD_HS0_WDATA2_N | D4  | O15                |                                   |

| DMD_HS0_WDATA3_P | A5  | O15                |                                   |

| DMD_HS0_WDATA3_N | C5  | O15                |                                   |

| DMD_HS0_WDATA4_P | F6  | O15                | - Channel 0 DMD SubLVDS data lane |

| DMD_HS0_WDATA4_N | E7  | O15                |                                   |

| DMD_HS0_WDATA5_P | A7  | O15                |                                   |

| DMD_HS0_WDATA5_N | C7  | O15                |                                   |

| DMD_HS0_WDATA6_P | F8  | O15                |                                   |

| DMD_HS0_WDATA6_N | E9  | O15                |                                   |

| DMD_HS0_WDATA7_P | B8  | O15                |                                   |

| DMD_HS0_WDATA7_N | D8  | O15                |                                   |

| DMD_HS1_CLK_P    | A13 | O15                |                                   |

| DMD_HS1_CLK_N    | C13 | O15                | Channel 1 DMD SubLVDS clock lane  |

| DMD_HS1_WDATA0_P | B10 | O15                |                                   |

| DMD_HS1_WDATA0_N | D10 | O15                |                                   |

| DMD_HS1_WDATA1_P | A11 | O15                |                                   |

| DMD_HS1_WDATA1_N | C11 | O15                |                                   |

| DMD_HS1_WDATA2_P | F10 | O15                |                                   |

| DMD_HS1_WDATA2_N | E11 | O15                |                                   |

| DMD_HS1_WDATA3_P | B12 | O15                |                                   |

| DMD_HS1_WDATA3_N | D12 | O15                |                                   |

| DMD_HS1_WDATA4_P | B14 | O15                | - Channel 1 DMD SubLVDS data lane |

| DMD_HS1_WDATA4_N | D14 | O15                |                                   |

| DMD_HS1_WDATA5_P | F12 | O15                | 1                                 |

| DMD_HS1_WDATA5_N | E13 | O15                | 1                                 |

| DMD_HS1_WDATA6_P | A15 | O15                | 1                                 |

| DMD_HS1_WDATA6_N | C15 | O15                | 1                                 |

| DMD_HS1_WDATA7_P | F14 | O15                | 1                                 |

| DMD_HS1_WDATA7_N | E15 | O15                | -                                 |

| DMD_HS2_CLK_P    | A19 | O15                |                                   |

| DMD_HS2_CLK_N    | C19 | O15                | Channel 2 DMD SubLVDS clock lane  |

| PIN              |     | u( <b>0</b> (1)      | DECODIDEION                       |

|------------------|-----|----------------------|-----------------------------------|

| NAME             | NO. | - I/O <sup>(1)</sup> | DESCRIPTION                       |

| DMD_HS2_WDATA0_P | A17 | O15                  |                                   |

| DMD_HS2_WDATA0_N | C17 | O15                  |                                   |

| DMD_HS2_WDATA1_P | F16 | O15                  |                                   |

| DMD_HS2_WDATA1_N | E17 | O15                  |                                   |

| DMD_HS2_WDATA2_P | B18 | O15                  |                                   |

| DMD_HS2_WDATA2_N | D18 | O15                  |                                   |

| DMD_HS2_WDATA3_P | F18 | O15                  |                                   |

| DMD_HS2_WDATA3_N | E19 | O15                  | Channel 2 DMD Subl V/DS data lana |

| DMD_HS2_WDATA4_P | B20 | O15                  | Channel 2 DMD SubLVDS data lane   |

| DMD_HS2_WDATA4_N | D20 | O15                  |                                   |

| DMD_HS2_WDATA5_P | A21 | O15                  |                                   |

| DMD_HS2_WDATA5_N | C21 | O15                  |                                   |

| DMD_HS2_WDATA6_P | F20 | O15                  |                                   |

| DMD_HS2_WDATA6_N | E21 | O15                  |                                   |

| DMD_HS2_WDATA7_P | B22 | O15                  |                                   |

| DMD_HS2_WDATA7_N | D22 | O15                  |                                   |

| DMD_HS3_CLK_P    | H24 | O15                  | Channel 3 DMD SubLVDS clock lane  |

| DMD_HS3_CLK_N    | J25 | O15                  |                                   |

| DMD_HS3_WDATA0_P | B24 | O15                  |                                   |

| DMD_HS3_WDATA0_N | C25 | O15                  |                                   |

| DMD_HS3_WDATA1_P | D24 | O15                  |                                   |

| DMD_HS3_WDATA1_N | E25 | O15                  |                                   |

| DMD_HS3_WDATA2_P | F22 | O15                  |                                   |

| DMD_HS3_WDATA2_N | E23 | O15                  |                                   |

| DMD_HS3_WDATA3_P | F24 | O15                  |                                   |

| DMD_HS3_WDATA3_N | G25 | O15                  | Channel 3 DMD SubLVDS data lane   |

| DMD_HS3_WDATA4_P | H22 | O15                  |                                   |

| DMD_HS3_WDATA4_N | G23 | O15                  |                                   |

| DMD_HS3_WDATA5_P | K24 | O15                  |                                   |

| DMD_HS3_WDATA5_N | L25 | O15                  |                                   |

| DMD_HS3_WDATA6_P | K22 | O15                  |                                   |

| DMD_HS3_WDATA6_N | J23 | O15                  |                                   |

| DMD_HS3_WDATA7_P | M22 | O15                  |                                   |

| DMD_HS3_WDATA7_N | L23 | O15                  |                                   |

(1) See Section 4.12 for more information on I/O definitions.

9

### 4.6 DMD Reset and Low Speed Interfaces

| PIN             |     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO. |                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DMD_LS0_CLK_P   | F2  | O15                | DMD law aroad differential interface. Dart 0 Clask                                                                                                                                                                                                                                                                                                                                                                                    |

| DMD_LS0_CLK_N   | E1  | O15                | DMD low-speed differential interface, Port 0 Clock                                                                                                                                                                                                                                                                                                                                                                                    |

| DMD_LS0_WDATA_P | B2  | O15                | DMD low-speed differential interface, Port 0 Write Data                                                                                                                                                                                                                                                                                                                                                                               |

| DMD_LS0_WDATA_N | C1  | O15                | DMD low-speed differential interface, For 0 write Data                                                                                                                                                                                                                                                                                                                                                                                |

| DMD_LS1_CLK     | G1  | 012                | DMD low-speed single-ended interface, Port 1 Clock                                                                                                                                                                                                                                                                                                                                                                                    |

| DMD_LS1_WDATA   | E3  | 012                | DMD low-speed single-ended interface, Port 1 Write Data                                                                                                                                                                                                                                                                                                                                                                               |

| DMD_LS2_CLK     | H2  | 012                | DMD low-speed single-ended interface, Port 2 Clock                                                                                                                                                                                                                                                                                                                                                                                    |

| DMD_LS2_WDATA   | G3  | 012                | DMD low-speed single-ended interface, Port 2 Write Data                                                                                                                                                                                                                                                                                                                                                                               |

| DMD_LS0_RDATA   | H4  | 11                 | DMD, low speed single ended serial interface, Port 0 Read Data <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                         |

| DMD_LS1_RDATA   | J3  | 11                 | DMD, low-speed single-ended serial interface, Port 1 Read Data <sup>(2)</sup> . If this port is not used, this signal requires an external pullup or pulldown to keep this input from floating.                                                                                                                                                                                                                                       |

| DMD_LS2_RDATA   | M4  | 11                 | DMD, low-speed single-ended serial interface, Port 2 Read Data <sup>(2)</sup> . If this port is not used, this signal requires an external pullup or pulldown to keep this input from floating.                                                                                                                                                                                                                                       |

| DMD_LS3_RDATA   | K4  | 11                 | DMD, low-speed single-ended serial interface, Port 3 Read Data <sup>(2)</sup> . If this port is not used, this signal requires an external pullup or pulldown to keep this input from floating.                                                                                                                                                                                                                                       |

| DMD_DEN_ARSTZ   | J1  | O10                | DMD driver enable signal / Active Low Asynchronous Reset ('1' = Enabled, '0'<br>= Reset)<br>This signal is driven low after the DMD is parked and before power is<br>removed from the DMD.<br>If the 1.8V power to the controller is independent of the 1.8V power to the<br>DMD, then an external pulldown resistor must be used to hold the signal low<br>in the event the controller power is inactive while DMD power is applied. |

(1) See Section 4.12 for more information on I/O definitions.

(2) All control interface reads make use of the single-ended low speed signals. The read data is clocked by the low speed differential write clock.

### 4.7 Flash Interface

| PIN        |      | I/O <sup>(1)</sup> | DESCRIPTION                                                         |

|------------|------|--------------------|---------------------------------------------------------------------|

| NAME       | NO.  |                    | DESCRIPTION                                                         |

| FLSH_CSZ   | AG23 | B16                | Chip select: Boot FLASH Only (Boot FLASH must use this chip select) |

| FLSH_CLK   | AG25 | B16                | Flash Clock                                                         |

| FLSH_DATA0 | AH22 | B16                | Address bit 0 (LSB)                                                 |

| FLSH_DATA1 | AH24 | B16                | Address bit 1                                                       |

| FLSH_DATA2 | AJ25 | B16                | Address bit 2                                                       |

| FLSH_DATA3 | AJ23 | B16                | Address bit 3                                                       |

(1) See Section 4.12 for more information on I/O definitions.

# 4.8 Peripheral Interfaces

| PIN         |      | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                               |  |

|-------------|------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO.  |                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                               |  |

| IIC0_SCL    | AL25 | B18                | I2C Port 0 (Primary-Secondary), Typically Secondary for Host Command and                                                                                                                                                                                                                                                                  |  |

| IIC0_SDA    | AK24 | B18                | Control to Controller, SCL (bidirectional, open-drain): An external pullup is required. The minimum acceptable value for this pullup is 470Ω.                                                                                                                                                                                             |  |

| SSP0_DO     | AP24 | 017                | SSP/SPI Port 0 Data Out (Primary): Transmit data pin.                                                                                                                                                                                                                                                                                     |  |

| SSP0_DI     | AN23 | 13                 | SSP/SPI Port 0 Data In (Primary): Receive data pin.                                                                                                                                                                                                                                                                                       |  |

| SSP0_CLK    | AN25 | 017                | SSP/SPI Port 0 Clock (Primary): Clock pin.                                                                                                                                                                                                                                                                                                |  |

| SSP0_CSZ_0  | AM22 | 017                | SPI Port 0 chip select 0 (Primary): Chip select (Active Low).<br>An external pullup resistor ( $\leq 10 k\Omega$ ) is suggested to avoid a floating chip select input to the external device.                                                                                                                                             |  |

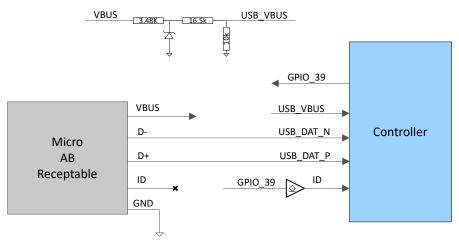

| USB_DAT_P   | AU1  | B7                 | USB OTG Data Lane                                                                                                                                                                                                                                                                                                                         |  |

| USB_DAT_N   | AW1  | B7                 |                                                                                                                                                                                                                                                                                                                                           |  |

| USB_VBUS    | AP4  | B7                 | USB OTG 5V Power Supply Detection                                                                                                                                                                                                                                                                                                         |  |

| USB_ID      | AT2  | 17                 | USB OTG Mini Receptacle Identification.                                                                                                                                                                                                                                                                                                   |  |

| USB_TXRTUNE | AR3  | PWR                | RTTRIM USB OTG Reference Resistor:<br>An external reference resistor, for calibrating the on-chip resistors, must be<br>connected with a value of $499\Omega$ .                                                                                                                                                                           |  |

| HOST_IRQ    | AK22 | 017                | Host interrupt (output):<br>HOST_IRQ indicates when the DLPC auto-initialization is in progress and most<br>importantly when it completes. The HOST_IRQ also toggles during command<br>handling to indicate when the execution is in progress. This pin is tristated during<br>reset. An external pullup must be included on this signal. |  |

(1) See Section 4.12 for more information on I/O definitions.

# 4.9 GPIO Peripheral Interface

| PIN     |      | u(1)                 |                                                                                                                         |  |

|---------|------|----------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| NAME    | NO.  | — I/O <sup>(1)</sup> | DESCRIPTION <sup>(2) (3) (4)</sup>                                                                                      |  |

| GPIO_00 | AR25 | B17                  | General purpose I/O 00:<br>Options:<br>1. Alt 0: SSP1_SCLK (O-P/I-S)<br>2. Alt 1: XY_IF_SCLK (I)<br>3. SW GPIO (B)      |  |

| GPIO_01 | AU25 | B17                  | General purpose I/O 01:<br>Dptions:<br>I. Alt 0: SSP1_DI (I)<br>2. Alt 1: XY_IF_DI(I)<br>3. SW GPIO (B)                 |  |

| GPIO_02 | AW25 | B17                  | General purpose I/O 02:<br>Options:<br>1. Alt 0: SSP1_DO (O)<br>2. Alt 1: XY_IF_DO (O)<br>3. SW GPIO (B)                |  |

| GPIO_03 | AT24 | B17                  | General purpose I/O 03:<br>Options:<br>1. Alt 0: SSP1_CSZ_0 (O-P/I-S)<br>2. Alt 1: XY_IF_CSZ (I)<br>3. SW GPIO (B)      |  |

| GPIO_04 | AV24 | B17                  | General purpose I/O 04:<br>Options: 1. Alt<br>0: SSP1_CSZ_1 (O-P/I-S)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                |  |

| GPIO_05 | AR23 | B17                  | General purpose I/O 05:<br>Options:<br>1. Alt 0: SSP1_CSZ_2 (O-P/I-S)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                |  |

| GPIO_06 | AP22 | B17                  | General purpose I/O 06:<br>Options:<br>1. Alt 0: SSP0_BCSZ (O-P/I-S)<br>2. Alt 1: SSP1_BCSZ (O-P/I-S)<br>3. SW GPIO (B) |  |

| GPIO_07 | AL23 | B17                  | General purpose I/O 07:<br>Options:<br>1. Alt 0: IIC1_SCL (B)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                        |  |

| GPIO_08 | AM24 | B17                  | General purpose I/O 08:<br>Options:<br>1. Alt 0: IIC1_SDA (B)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                        |  |

| GPIO_09 | N3   | B10                  | General purpose I/O 09:<br>Options:<br>1. Alt 0: WPC_COLOR_SENSOR_VSYNC(O)<br>2. Alt 1: MEMAUX_1(O)<br>3. SW GPIO (B)   |  |

| GPIO_10 | Ρ4   | В9                   | General purpose I/O 10:<br>Options:<br>1. Alt 0: UART1_RSTZ (O)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                      |  |

Submit Document Feedback

13

| Р       | IN   | I/O <sup>(1)</sup> | DESCRIPTION <sup>(2)</sup> (3) (4)                                                                           |

|---------|------|--------------------|--------------------------------------------------------------------------------------------------------------|

| NAME    | NO.  |                    |                                                                                                              |

| GPIO_11 | Τ4   | B10                | General purpose I/O 11:<br>Options:<br>1. Alt 0: UART1_CTSZ(I)<br>2. Alt 1: N/A<br>3. SW GPIO (B)            |

| GPIO_12 | ∨4   | B10                | General purpose I/O 12:<br>Options:<br>1. Alt 0: DMD_PWR_EN (O)<br>2. Alt 1: RC_CHARGE (O)<br>3. SW GPIO (B) |

| GPIO_13 | AD24 | B14                | General purpose I/O 13:<br>Options:<br>1. Alt 0: PAUX0 (O)<br>2. Alt 1: LED_SEL0 (O)<br>3. SW GPIO (B)       |

| GPIO_14 | AC23 | B14                | General purpose I/O 14:<br>Options:<br>1. Alt 0: PAUX1 (O)<br>2. Alt 1: LED_SEL1 (O)<br>3. SW GPIO (B)       |

| GPIO_15 | AE25 | B14                | General purpose I/O 15:<br>Options:<br>1. Alt 0: PAUX2 (O)<br>2. Alt 1: LED_SEL2 (O)<br>3. SW GPIO (B)       |

| GPIO_16 | AE23 | B14                | General purpose I/O 16:<br>Options:<br>1. Alt 0: PAUX3 (O)<br>2. Alt 1: LED_SEL3 (O)<br>3. SW GPIO (B)       |

| GPIO_17 | AF24 | B13                | General purpose I/O 17:<br>Options:<br>1. Alt 0: PAUX4 (O)<br>2. Alt 1: LED_SEL4 (O)<br>3. SW GPIO (B)       |

| GPIO_18 | AF22 | B13                | General purpose I/O 18:<br>Options:<br>1. Alt 0: PAUX5 (O)<br>2. Alt 1: LED_SEL5 (O)<br>3. SW GPIO (B)       |

| GPIO_19 | R1   | B10                | General purpose I/O 19:<br>Options:<br>1. Alt 0: PAUX6 (O)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                |

| GPIO_20 | R3   | B10                | General purpose I/O 20:<br>Options:<br>1. Alt 0: PAUX7 (O)<br>2. Alt 1: SL_Trigger (I)<br>3. SW GPIO (B)     |

| GPIO_21 | U1   | B10                | General purpose I/O 21:<br>Options:<br>1. Alt 0: PAUX8 (O)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                |

| GPIO_22 | T2   | В9                 | General purpose I/O 22:<br>Options:<br>1. Alt 0: PAUX9 (O)<br>2. Alt 1: CW_INDEX0 (I)<br>3. SW GPIO (B)      |

Copyright © 2024 Texas Instruments Incorporated

DLPC8445 DLPS253 – SEPTEMBER 2024

| PIN //O <sup>(1)</sup> |     |     | DESCRIPTION <sup>(2)</sup> (3) (4)                                                                              |

|------------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------|

| NAME                   | NO. |     | DESCRIPTION                                                                                                     |

| GPIO_23                | U3  | B10 | General purpose I/O 23:<br>Options:<br>1. Alt 0: PAUX10 (O)<br>2. Alt 1: PWM_OUT_CW0 (O)<br>3. SW GPIO (B)      |

| GPIO_24                | W1  | B10 | General purpose I/O 24:<br>Options:<br>1. Alt 0: PAUX11 (O)<br>2. Alt 1: PWM_OUT_CW1 (O)<br>3. SW GPIO (B)      |

| GPIO_25                | V2  | B10 | General purpose I/O 25:<br>Options:<br>1. Alt 0: PWM_OUT_RLED (O)<br>2. Alt 1: CMP_MSEL_0 (O)<br>3. SW GPIO (B) |

| GPIO_26                | W3  | B10 | General purpose I/O 26:<br>Options:<br>1. Alt 0: PWM_OUT_GLED (O)<br>2. Alt 1: CMP_PWM (O)<br>3. SW GPIO (B)    |

| GPIO_27                | AA1 | B10 | General purpose I/O 27:<br>Options:<br>1. Alt 0: PWM_OUT_BLED (O)<br>2. Alt 1: CMP_OUT (I)<br>3. SW GPIO (B)    |

| GPIO_28                | Y4  | B10 | General purpose I/O 28:<br>Options:<br>1. Alt 0: PWM_OUT_IRLED (O)<br>2. Alt 1: LS_PWR (O)<br>3. SW GPIO (B)    |

| GPIO_29                | Y2  | B10 | General purpose I/O 29:<br>Options: 1. Alt 0: PWM_OUT_UVLED (O)<br>2. Alt 1: CW_INDEX_1 (I)<br>3. SW GPIO (B)   |

| GPIO_30                | AA3 | B11 | General purpose I/O 30:<br>Options:<br>1. Alt 0: HBT_CLKOUT (O)<br>2. Alt 1: N/A<br>3. SW GPIO (B)              |

| GPIO_31                | AB4 | B10 | General purpose I/O 31:<br>Options:<br>1. Alt 0: HBT_DO (O)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                  |

| GPIO_32                | AC1 | B10 | General purpose I/O 32:<br>Options:<br>1. Alt 0: HBT_CLKIN_0 (I)<br>2. Alt 1: N/A<br>3. SW GPIO (B)             |

| GPIO_33                | AB2 | B10 | General purpose I/O 33:<br>Options:<br>1. Alt 0: HBT_DI_0 (I)<br>2. Alt 1:N/A<br>3. SW GPIO (B)                 |

| GPIO_34                | AC3 | В9  | General purpose I/O 34:<br>Options:<br>1. Alt 0: HBT_CLKIN_1 (I)<br>2. Alt 1: GP_CLK2 (O)<br>3. SW GPIO (B)     |

Submit Document Feedback

15

| PIN //O <sup>(1)</sup> |     |     |                                                                                                                         |  |  |  |

|------------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                   | NO. |     | DESCRIPTION <sup>(2)</sup> (3) (4)                                                                                      |  |  |  |

| GPIO_35                | AD4 | B10 | General purpose I/O 35:<br>Options:<br>1. Alt 0: HBT_DI_1 (I)<br>2. Alt 1: CAL_PWR(O)<br>3. SW GPIO (B)                 |  |  |  |

| GPIO_36                | AE1 | B10 | General purpose I/O 36:<br>Options:<br>1. Alt 0: HBT_CLKIN_2 (I)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                     |  |  |  |

| GPIO_37                | AD2 | B10 | General purpose I/O 37:<br>Options:<br>1. Alt 0: HBT_DI_2 (I)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                        |  |  |  |

| GPIO_38                | AE3 | B10 | General purpose I/O 38:<br>Options:<br>1. Alt 0: EFSYNC (O)/DASYNC(I)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                |  |  |  |

| GPIO_39                | AG1 | B10 | General purpose I/O 39:<br>Options:<br>1. Alt 0: SEQ_SYNC (B - Open Drain)<br>2. Alt 1: N/A<br>3. SW GPIO (B)           |  |  |  |

| GPIO_40                | AF4 | B10 | General purpose I/O 40:<br>Options:<br>1. Alt 0: AWC0_DACCLK_0_1 (O)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                 |  |  |  |

| GPIO_41                | AF2 | B11 | General purpose I/O 41:<br>Options:<br>1. Alt 0: AWC0_DACCLK_0_1 (O)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                 |  |  |  |

| GPIO_42                | AJ1 | B10 | General purpose I/O 42:<br>Options:<br>1. Alt 0: AWC0_DACS_PWMA_0 (O)<br>2. Alt 1: N/A<br>3. SW GPIO (B)                |  |  |  |

| GPIO_43                | AG3 | B10 | General purpose I/O 43:<br>Options:<br>1. Alt 0: AWC0_DACD_PWMB_0 (O)<br>2. Alt 1: PWM_OUT_BLED_2 (O)<br>3. SW GPIO (B) |  |  |  |

| GPIO_44                | AH2 | B10 | General purpose I/O 44:<br>Options:<br>1. Alt 0: AWC0_DACS_PWMA_1 (O)<br>2. Alt 1: PAUX_INT0 (O)<br>3. SW GPIO (B)      |  |  |  |

| GPIO_45                | AJ3 | B10 | General purpose I/O 45:<br>Options:<br>1. Alt 0: AWC0_DACD_PWMB_1 (O)<br>2. Alt 1: PAUX_INT1 (O)<br>3. SW GPIO (B)      |  |  |  |

| GPIO_46                | AL1 | B10 | General purpose I/O 46:<br>Options:<br>1. Alt 0: N/A<br>2. Alt 1: PAUX_INT2 (O)<br>3. SW GPIO (B)                       |  |  |  |

Copyright © 2024 Texas Instruments Incorporated

**DLPC8445** DLPS253 - SEPTEMBER 2024

| PIN     |     | I/O <sup>(1)</sup> | DESCRIPTION <sup>(2)</sup> (3) (4)                                                                                |

|---------|-----|--------------------|-------------------------------------------------------------------------------------------------------------------|

| NAME    | NO. | 1/0()              |                                                                                                                   |

| GPIO_47 | AK4 | B11                | General purpose I/O 47:<br>Options:<br>1. Alt 0: AWC1_DACCLK_0_1 (O)<br>2. Alt 1: PAUX_INT3 (O)<br>3. SW GPIO (B) |

| GPIO_48 | AK2 | B10                | General purpose I/O 48:<br>Options:<br>1. Alt 0: AWC1_DACS_PWMA_0 (O)<br>2. Alt 1: SF_SEL_0 (O)<br>3. SW GPIO (B) |

| GPIO_49 | AN1 | B10                | General purpose I/O 49:<br>Options:<br>1. Alt 0: AWC1_DACD_PWMB_0 (O)<br>2. Alt 1: SF_SEL_1 (O)<br>3. SW GPIO (B) |

| GPIO_50 | AL3 | B10                | General purpose I/O 50:<br>Options:<br>1. Alt 0: AWC1_DACS_PWMA_1 (O)<br>2. Alt 1: SF_SEL_2 (O)<br>3. SW GPIO (B) |

| GPIO_51 | AM2 | B10                | General purpose I/O 51:<br>Options:<br>1. Alt 0: AWC1_DACD_PWMB_1 (O)<br>2. Alt 1: SF_SEL_3 (O)<br>3. SW GPIO (B) |

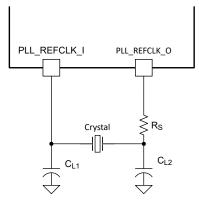

#### 4.10 Clock and PLL Support

| PIN      |          | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                        |  |  |

|----------|----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NAME NO. |                    |                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| REFCLK_I | N1       | 18                 | Crystal Input: Reference clock crystal input <sup>(2) (3)</sup>                                                                                                                                                                                                                                                                                                    |  |  |

| REFCLK_O | L1       | O8                 | Crystal Output: Reference clock crystal output <sup>(2) (5)</sup>                                                                                                                                                                                                                                                                                                  |  |  |

| OCLKA    | AB24     | O14                | General Purpose Output Clock A <sup>(4)</sup><br>Targeted for driving Color Wheel motor controller. Frequency is software<br>programmable, with a power-up default frequency of 0.99MHz.<br>Note: The output frequency is not affected by non-power-up reset operations (that<br>is, the system holds the last programmed value until the system is power cycled). |  |  |

(1) (2)

See I/O Table for more information on I/O definitions. For more information on this signal see System Oscillator Timing.

(3) For applications where an external oscillator is used in place of a crystal, use an oscillator to drive this pin.

(4) For more information on this signal see Programmable Output Clock Timing.

(5) For applications where an external oscillator is used in place of a crystal, this pin should be grounded.

### 4.11 Power and Ground

| PIN            |                                                                                                                                                                                                                                     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                        |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME           | NO.                                                                                                                                                                                                                                 |                    | DESCRIPTION                                                                                                                                                        |  |

| VDDA18_PLLM    | AL11                                                                                                                                                                                                                                | PWR                | 1.8V (Nominal) for the Main I/F PLL                                                                                                                                |  |

| VDDA18_PLLD    | J13                                                                                                                                                                                                                                 | PWR                | 1.8V (Nominal) for the DMD I/F PLL                                                                                                                                 |  |

| VDD_CORE       | AA13, AA15, AA21,<br>AB16, AC13, AD6,<br>AD8, AD18, AD20,<br>AE9, AE11, AF14,<br>AF16, AF20, AG7,<br>AH6, AJ11, AL9,<br>AL13, AL17, AL19,<br>K8, K18, L9, L13, M6,<br>M20, N15, N17, T6,<br>T12, T14, T20, U19,<br>V8, V10, Y6, Y20 | PWR                |                                                                                                                                                                    |  |

| VDDAR_CORE     | AB10, AB12, AJ9,<br>AJ13, AJ15, AJ17,<br>AJ19, AK8, N11, N13,<br>P8, P18, R9, R19,<br>W15, W17                                                                                                                                      | PWR                |                                                                                                                                                                    |  |

| VDDA_CORE_DSI  | AR7                                                                                                                                                                                                                                 | PWR                |                                                                                                                                                                    |  |

| VDDA_CORE_FPD  | AM16, AM18, AM20                                                                                                                                                                                                                    | PWR                | 0.8V (Nominal) Fixed Power for FPD core                                                                                                                            |  |

| VDDA_CORE_USB  | AM6                                                                                                                                                                                                                                 | PWR                | 0.8V (Nominal) for USB Controller                                                                                                                                  |  |

| VDDA_CORE_Vx1  | AM10, AM14                                                                                                                                                                                                                          | PWR                | 0.8V (Nominal) Fixed Power for Vx1 core                                                                                                                            |  |

| VDDA18_DDI     | J7, J9, J11, J15, J17,<br>J19                                                                                                                                                                                                       | PWR                | 1.8V (Nominal) Fixed IO Power for SubLVDS DMD Interface                                                                                                            |  |

| VDDA18_DSI     | AP8                                                                                                                                                                                                                                 | PWR                | 1.8V (Nominal) for DSI                                                                                                                                             |  |

| VDDA18_FPD     | AN15, AP16, AP18,<br>AR19                                                                                                                                                                                                           | PWR                | 1.8V (Nominal) Fixed Power for FPD I/O                                                                                                                             |  |

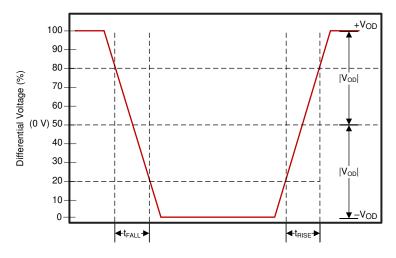

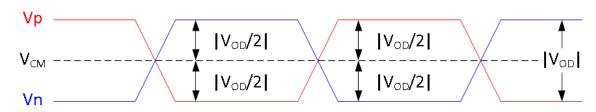

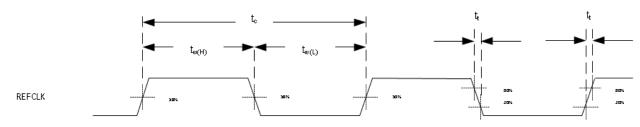

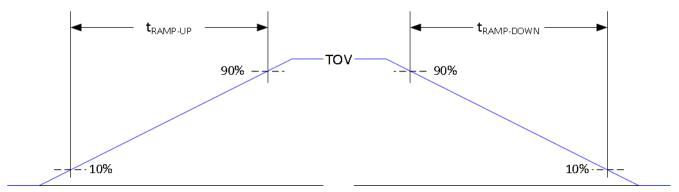

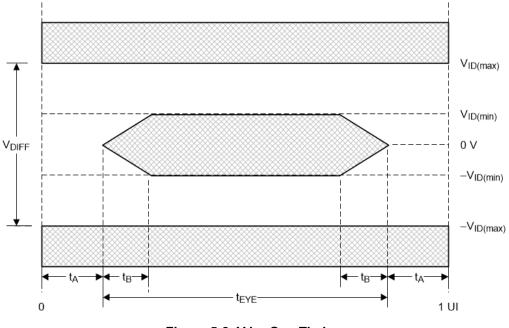

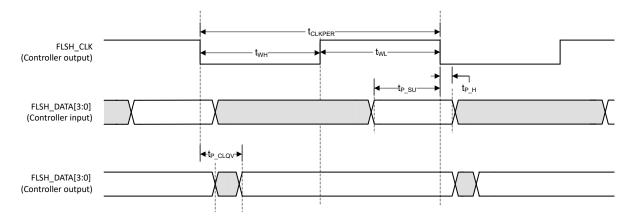

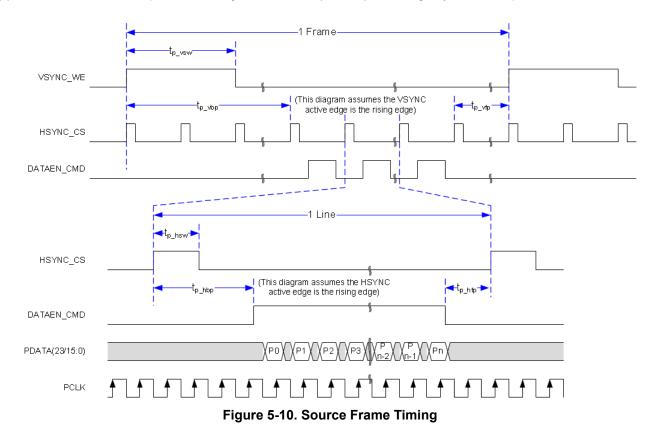

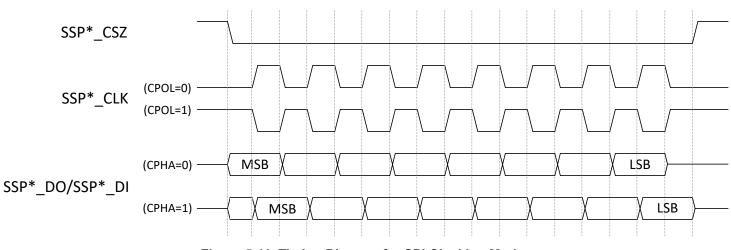

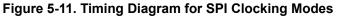

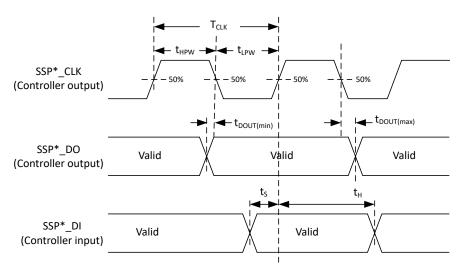

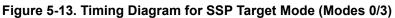

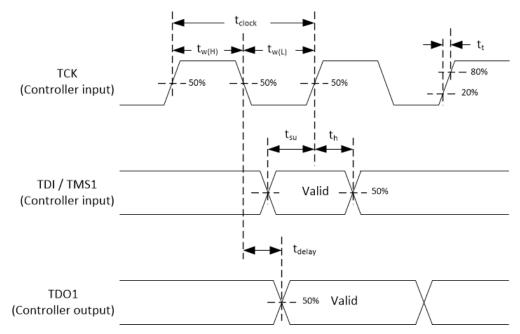

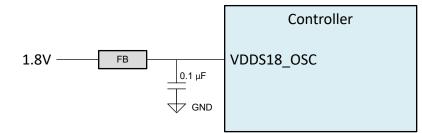

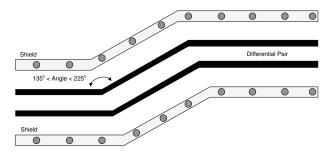

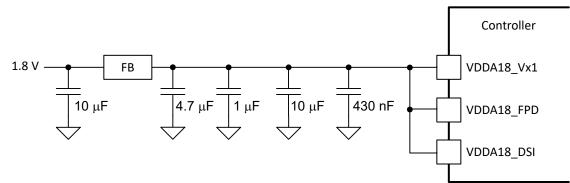

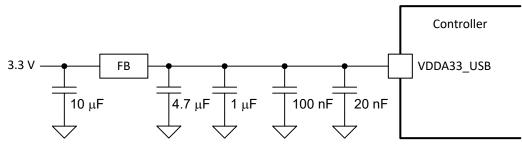

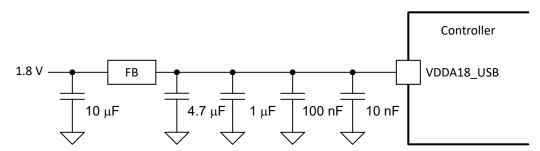

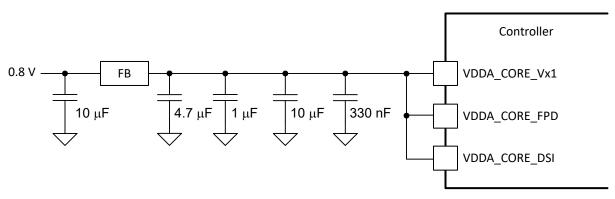

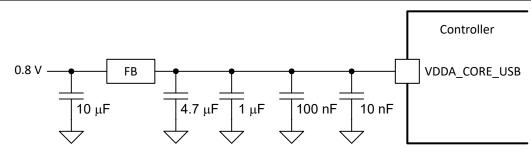

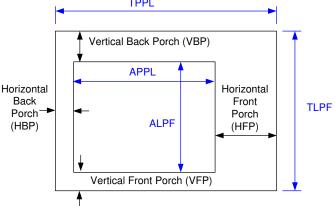

| VDDA18_USB     | AN7                                                                                                                                                                                                                                 | PWR                | 1.8V (Nominal) for USB Phy                                                                                                                                         |  |