### QP7025 High-Speed 8K x 16 Dual-Port Static RAM

## **General Description**

The QP7025 is a CMOS Fast 8K x 16 Dual-Port Static RAM (SRAM). QP Semiconductor designed the QP7025 to be a direct replacement for the IDT7025. It is designed to be used as a stand-alone 128K-bit Dual-Port RAM or as a combination MASTER/SLAVE Dual-Port RAM for 32-bit or larger (wider) word systems. Applications requiring a 32-bit or wider memory system can use the MASTER/SLAVE Dual-Port RAM approach to achieve full-speed, error free operation without additional discrete logic.

The QP7025 supports asynchronous access for reads or writes to any location in memory via two independent ports with separate control, address, and I/O pins that function identically to the IDT7025 that it replaces. The QP7025 has an automatic power down feature controlled by the appropriate Chip Enable (CE) pin that puts each port in a very low standby power mode.

The QP7025 utilizes CMOS high-performance technology which allows the devices to typically operate on only 750mW of power. Low-power (L) versions offer battery backup data retention capability with typical power consumption of  $10\mu$ W from a 2V source.

The QP7025 is available in a hermetic ceramic 84-pin PGA and a ceramic 84-pin Flatpack. Military grade product is manufactured in compliance with the latest revision of MIL-PRF-38535 QML, making it ideally suited to military temperature applications demanding the highest level of performance and reliability.

#### **Features**

- True Dual-Ported memory cells which allow simultaneous reads of the same memory location

- High-speed access

- Military: 35/45/55/70nsIndustrial: 20/25ns

- Low-power operation

- QP7025S

- Active: 750mW (typ.)Standby: 0.2mW (typ.)

- o QP7025L

- Active: 750mW (typ.)Standby: 0.2mW (typ.)

- Separate upper-byte and lower-byte control for multiplexed bus compatibility

- Expands data bus width to 32 bits or more using the Master/Slave select when cascading more than one device

- M/S = H for BUSY output flag on Master

- o M/S = L for BUSY input on Slave

- o Interrupt Flag

- o On-chip port arbitration logic

- Full on-chip hardware support of semaphore signaling between ports

- Fully asynchronous operation from either port

- Battery backup operation—2V data retention

- TTL-compatible, single 5V (±10%) power supply

- Packages: 84-pin PGA & 84-pin Flatpack

- Industrial temperature range (-40°C to +85°C) is available

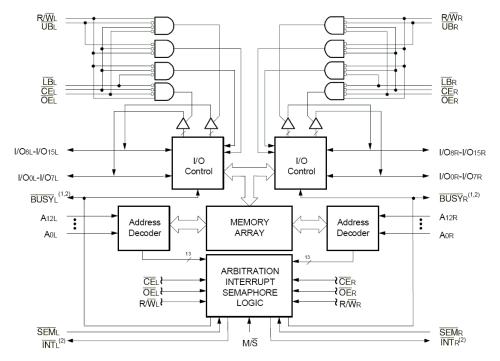

# **Block Diagram**

Notes:

(Master): BUSY is output; (Slave): BUSY is input.

Outputs and INT outputs are non-tri-stated push-pull.

# **Functional Description**

|                                        | Description                            |                                                                     |

|----------------------------------------|----------------------------------------|---------------------------------------------------------------------|

| Left Port                              | Right Port                             | Functional Description                                              |

| CE L                                   | CE <sub>R</sub>                        | Chip Enable                                                         |

| R/W <sub>L</sub>                       | R/W <sub>R</sub>                       | Read/Write Enable                                                   |

| OE L                                   | OE R                                   | Output Enable                                                       |

| $A_{0L} - A_{12L}$                     | A <sub>0R</sub> – A <sub>12R</sub>     | Address                                                             |

| I/O <sub>0L</sub> – I/O <sub>15L</sub> | I/O <sub>0R</sub> – I/O <sub>15R</sub> | Data Input/Output                                                   |

| SEML                                   | SEM <sub>R</sub>                       | Semaphore Enable                                                    |

| UB L                                   | UB <sub>R</sub>                        | Upper Byte Select                                                   |

| LB L                                   | LB <sub>R</sub>                        | Lower Byte Select                                                   |

| ĪNT L                                  | INT <sub>R</sub>                       | Interrupt Flag                                                      |

| BUSY                                   | BUSY R                                 | Busy Flag                                                           |

| M/S                                    |                                        | Master Slave Select                                                 |

| V                                      | / <sub>cc</sub>                        | Power- All V <sub>CC</sub> pins must be connected to a power supply |

|                                        | ND                                     | Ground- All GND pins must be connected to a good ground             |

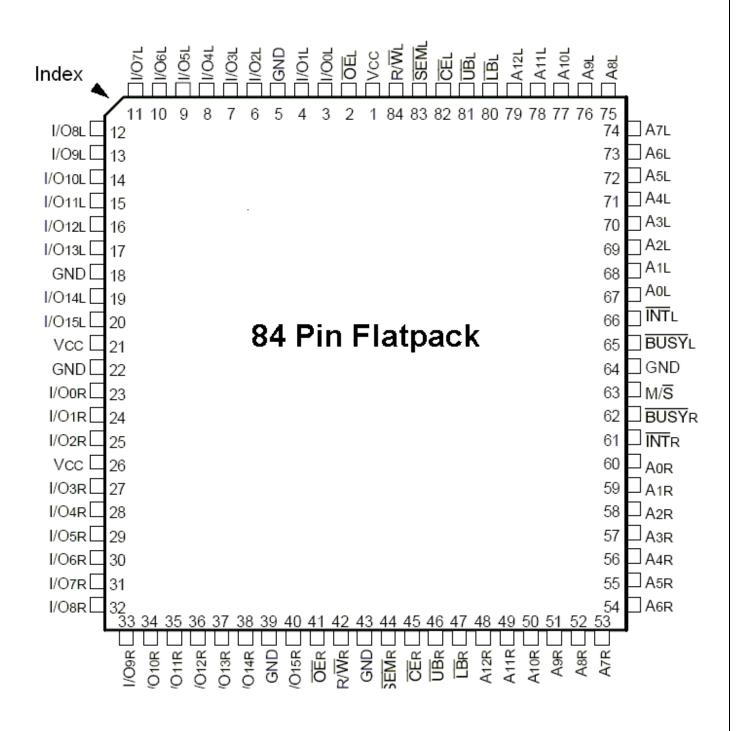

# **Connection Diagrams**

# **Connection Diagrams**

|                   | 63                 | 61     | 60     | 58                 | 55                 | 54                | 51              | 48           | 46           | 45               | 42          |

|-------------------|--------------------|--------|--------|--------------------|--------------------|-------------------|-----------------|--------------|--------------|------------------|-------------|

| 11                | I/O7L              | I/O5L  | I/O4L  | I/O <sub>2</sub> L | I/O <sub>0</sub> L | ŌĒL               | SEML            | ŪB∟          | A11L         | <b>A</b> 10L     | <b>A</b> 7L |

|                   | 66                 | 64     | 62     | 59                 | 56                 | 49                | 50              | 47           | 44           | 43               | 40          |

| 10                | I/O10L             | I/O8L  | I/O6L  | I/O3L              | I/O1L              | ŪB∟               | CEL             | <b>A</b> 12L | <b>A</b> 9L  | <b>A</b> 8L      | <b>A</b> 5L |

|                   | 67                 | 65     |        | 57 53 52 41        |                    |                   |                 |              |              |                  | 39          |

| 09                | I/O11L             | I/O9L  |        |                    | GND                | Vcc               | R/WL            |              |              | <b>A</b> 6L      | A4L         |

|                   | 69                 | 68     |        |                    |                    | 38                | 37              |              |              |                  |             |

| 80                | I/O13L             | I/O12L |        |                    |                    |                   |                 |              |              | <b>A</b> 3L      | <b>A</b> 2L |

|                   | 72                 | 71     | 73     |                    |                    |                   |                 |              | 33           | 35               | 34          |

| 07                | I/O15L             | I/O14L | Vcc    |                    |                    |                   |                 |              | BUSYL        | A <sub>0</sub> L | ĪNTL        |

|                   | 75                 | 70     | 74     |                    | 84 1               | Pin Po            | <b>3</b> Δ      |              | 32           | 31               | 36          |

| 06                | I/O <sub>0</sub> R | GND    | GND    |                    |                    | p View            |                 |              | GND          | M/S              | A1L         |

|                   | 76                 | 77     | 78     |                    |                    |                   |                 |              | 28           | 29               | 30          |

| 05                | I/O1R              | I/O2R  | Vcc    |                    |                    | ĪN₹               | BUSYR           |              |              |                  |             |

|                   | 79                 | 80     |        |                    |                    |                   |                 |              |              | 26               | 27          |

| 04                | I/O3R              | I/O4R  |        |                    |                    |                   |                 |              |              | <b>A</b> 2R      | <b>A</b> 1R |

|                   | 81                 | 83     |        |                    | 7                  | 11                | 12              |              |              | 23               | 25          |

| 03                | I/O5R              | I/O7R  |        |                    | GND                | GND               | SEMR            |              |              | <b>A</b> 5R      | <b>A</b> 3R |

|                   | 82                 | 1      | 2      | 5                  | 8                  | 10                | 14              | 17           | 20           | 22               | 24          |

| 02                | I/O6R              | I/O9R  | I/O10R | I/O13R             | I/O15R             | $R/\overline{W}R$ | <del>UB</del> R | <b>A</b> 11R | <b>A</b> 8R  | <b>A</b> 6R      | <b>A</b> 4R |

|                   | 84                 | 3      | 4      | 6                  | 9                  | 15                | 13              | 16           | 18           | 19               | 21          |

| 01                | I/O8R              | I/O11R | I/O12R | I/O14R             | ŌĒR                | <del>LB</del> R   | CER             | <b>A</b> 12R | <b>A</b> 10R | <b>A</b> 9R      | <b>A</b> 7R |

| <b>▼</b><br>Index | А                  | В      | С      | D                  | E                  | F                 | G               | Н            | J            | К                | L           |

**Absolute Maximum Ratings /1**

| Condition                                   | Rating                  | Units    |

|---------------------------------------------|-------------------------|----------|

| Power Supply and Input Voltage              | -0.5 to +7.0            | Volts DC |

| Storage Temperature Range                   | -65 to +150             | °C       |

| Output Current                              | 50                      | mA       |

| Maximum Power Dissipation (P <sub>D</sub> ) | 2.2                     | W        |

| Lead Temperature (soldering, 10 seconds)    | +260                    | °C       |

| Junction Temperature (T <sub>J</sub> )      | +150                    | °C       |

| DC Input and Output Voltage Range           | $-0.5$ to $V_{CC}$ +0.5 | Volts DC |

| Output Voltage Applied in High Z State      | -0.5 to $V_{CC}$ +0.5   | Volts DC |

/1Stresses above the AMR may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.All voltages referenced to GND, unless otherwise specified.

**Recommended Operating Conditions /1**

| Condition                                   | Rating       | Units    | Notes |

|---------------------------------------------|--------------|----------|-------|

| Supply Voltage Range (V <sub>CC</sub> )     | 4.5 to 5.5   | Volts DC |       |

| High-Level Input Voltage (V <sub>IH</sub> ) | 2.2 to 6.0   | Volts DC |       |

| Low-Level Input Voltage (V <sub>IL</sub> )  | -0.5 to +0.8 | Volts DC |       |

| Case Operating Range (T <sub>c</sub> )      | -55C to +125 | °C       |       |

/1Maximum junction temperature shall not be exceeded except for allowable short duration burn-in screening conditions in accordance with method 5004 of MIL-STD-883.

| ELECTRICAL PERFORMANCE CHARACTERISTICS-DC            |                  |                                                                                                                                                                                                                                                                                                                              |     |      |     |      |  |  |  |

|------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|--|--|--|

| Test                                                 | Symbol           | Conditions $ -55^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq +125^{\circ}\text{C} $ $ 4.5 \text{ V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{ V} $ Unless Otherwise Specified                                                                                                                                              | Min | Тур  | Max | Unit |  |  |  |

| Output Low Voltage                                   | V <sub>OL</sub>  | $V_{CC} = 4.5V, I_{OL} = 4mA,$<br>$V_{IH} = 2.2V, V_{IL} = 0.8V$                                                                                                                                                                                                                                                             |     |      | 0.4 | V    |  |  |  |

| Output High Voltage                                  | V <sub>OH</sub>  | V <sub>CC</sub> = 4.5V, I <sub>OH</sub> = -4mA,<br>V <sub>IH</sub> = 2.2V, V <sub>IL</sub> =0.8V                                                                                                                                                                                                                             | 2.4 |      |     | V    |  |  |  |

| Input Leakage Current                                | ILI              | $V_{CC}$ = 5.5V<br>$V_{IN}$ = GND to $V_{CC}$                                                                                                                                                                                                                                                                                |     |      | 5   | μA   |  |  |  |

| Output Leakage Current                               | I <sub>LO</sub>  | $V_{CC}$ = 5.5V, $\overline{CE} = V_{IH}$ , $V_{IN}$ = GND to $V_{CC}$                                                                                                                                                                                                                                                       |     |      | 5   | μA   |  |  |  |

| Dynamic Operating Current (both ports active)        | I <sub>CC1</sub> | Outputs Open,<br>$V_{CC} = 5.5V$ , $f = f_{max}$ /1,<br>$\overline{SEM} \ge VIH$ , $\overline{CE} \le V_{IL}$                                                                                                                                                                                                                |     | 150  | 250 | mA   |  |  |  |

| Standby Supply Current (both ports) TTL Inputs       | I <sub>CC2</sub> | $\overline{SEM}_{R} = \overline{SEM}_{L} \ge V_{IH},$ $\overline{CE}_{R} = \overline{CE}_{L} \ge V_{IH},$ $V_{CC} = 5.5V, f = f_{max} / 1$                                                                                                                                                                                   |     | 8    | 25  | mA   |  |  |  |

| Standby Supply Current<br>(one port) TTL Inputs      | Іссз             | Active ports outputs open $ \overline{SEM}_{R} = \overline{SEM}_{L} \ge V_{IH}, $ $ \overline{CE}_{R} = \overline{CE}_{L} \ge V_{IH}, \text{ Opposite Port} = V_{IL}, $ $ V_{CC} = 5.5V, f = f_{max} \setminus 1 $                                                                                                           |     | 85   | 160 | mA   |  |  |  |

| Full Standby Supply Current (both ports) CMOS Inputs | I <sub>CC4</sub> | $\overline{SEM}_{R} = \overline{SEM}_{L} \ge V_{cc} - 0.2V,$ both ports $\overline{CE}_{R} = \overline{CE}_{L} \ge V_{cc} - 0.2V,$ $V_{IN} \le 0.2V \text{ or } V_{IN} \ge V_{cc} - 0.2V,$ $V_{cc} = 5.5V, f = 0 \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$                                                                        |     | 0.04 | 5   | mA   |  |  |  |

| Full Standby Supply Current (one port) CMOS Inputs   | I <sub>CC5</sub> | Active ports outputs open $\overline{SEM}_{R} = \overline{SEM}_{L} \ge V_{CC} - 0.2 \text{ V},$ one port $\overline{CE}_{R} = \overline{CE}_{L} \ge V_{CC} - 0.2 \text{ V},$ opposite port < 0.2 V $V_{IN} \le 0.2 \text{V or } V_{IN} \ge V_{cc} - 0.2 \text{ V},$ $V_{CC} = 5.5 \text{V}, \text{ f= } f_{max} \setminus 1$ |     | 80   | 150 | mA   |  |  |  |

| Input Capacitance                                    | C <sub>IN</sub>  | $V_{IN} = 0 \text{ V}, V_{CC} = 5.0 \text{V},$<br>$f = 1 \text{MHz}, T_A = 25^{\circ} \text{C} /3$                                                                                                                                                                                                                           |     |      | 11  | pF   |  |  |  |

| Output Capacitance                                   | Соит             | $V_{OUT} = 0 \text{ V}, V_{CC} = 5.0 \text{ V},$<br>$f = 1 \text{MHz}, T_A = 25^{\circ} \text{C} /3$                                                                                                                                                                                                                         |     |      | 11  | pF   |  |  |  |

<sup>1/</sup> At  $f_{MAX}$ , address and data inputs (excluding OE) are cycling at the maximum frequency of read cycle of  $1/t_{AVAV}$ , and using AC test conditions of input levels of GND to 3.0 V.

<sup>2/</sup> f = 0 Hz means no address or control lines change

<sup>3/</sup> Measured at initial qualification only

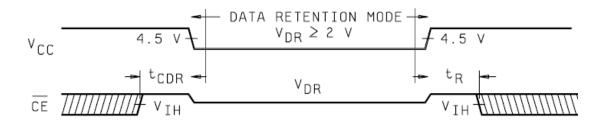

| ELECTRICAL PERFORMANCE CHARACTERISTICS-Data Retention                   |                   |                                                                                                                                                                                                 |                   |     |      |      |  |  |  |  |

|-------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|------|------|--|--|--|--|

| Test                                                                    | Symbol            | Conditions Conditions -55°C ≤T <sub>A</sub> ≤+125°C 4.5 V ≤ Vcc ≤ 5.5 V Unless Otherwise Specified                                                                                              | Min               | Тур | Мах  | Unit |  |  |  |  |

| Data Retention Voltage<br>("L" Series Devices Only)                     | $V_{DR}$          | $\overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.2\text{V}, \text{V}_{\text{CC}} = 2.0 \text{ V}$ $\text{V}_{\text{IN}} \ge \text{V}_{\text{CC}} - 0.2\text{V} \text{ or } \le 0.2 \text{ V}$ | 2.0               |     |      | V    |  |  |  |  |

| Data Retention Current<br>("L" Series Devices Only)                     | I <sub>CCDR</sub> | $\overline{CE} \ge V_{CC} - 0.2V, V_{CC} = 2.0 V$ $V_{IN} \ge V_{CC} - 0.2V \text{ or } \le 0.2 V$                                                                                              |                   | 5   | 1000 | μΑ   |  |  |  |  |

| Chip Deselect to Data<br>Retention Time /4<br>("L" Series Devices Only) | t <sub>CDR</sub>  | $\overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.2\text{V}, \text{Vcc} = 2.0\text{V}$ $\text{V}_{\text{IN}} \ge \text{Vcc} - 0.2\text{V or} \le 0.2\text{V }/5$ See output test load figures  | 0                 |     |      | ns   |  |  |  |  |

| Operation Recovery Time /4 ("L" Series Devices Only)                    | t <sub>R</sub>    | $\overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.2\text{V}, \text{Vcc} = 2.0\text{V}$ $\text{V}_{\text{IN}} \ge \text{Vcc} - 0.2\text{V or} \le 0.2\text{V }/5$ See output test load figures  | t <sub>AVAV</sub> |     |      | ns   |  |  |  |  |

<sup>/4</sup> Parameter tested at initial characterization and after design change. Parameter guaranteed per limits in table.

## **Data Retention Mode Timing**

<sup>/5</sup> Measurement assumption: transition times ≤ 5 ns, input levels from GND to 3.0 V, timing ref levels of 1.5 V and output load per AC Output Test Load Type I shown herein.

| ELECTRICAL PERFORMANCE CHARACTERISTICS- Read Cycle |                   |                                                                                                  |     |     |      |  |  |  |  |

|----------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------|-----|-----|------|--|--|--|--|

| Description                                        | Symbol            | Conditions<br>-55°C ≤T <sub>A</sub> ≤+125°C<br>4.5 V ≤ Vcc ≤ 5.5 V<br>Unless Otherwise Specified | Min | Max | Unit |  |  |  |  |

| Read Cycle Time /6                                 | t <sub>AVAV</sub> | S or L 70                                                                                        |     | 70  |      |  |  |  |  |

| •                                                  | AVAV              | S or L 55                                                                                        |     | 55  | ns   |  |  |  |  |

|                                                    |                   | S or L 45                                                                                        |     | 45  | 113  |  |  |  |  |

|                                                    |                   | S or L 35                                                                                        |     | 35  |      |  |  |  |  |

| Address Access Time /6                             | t <sub>AVQV</sub> | S or L 70                                                                                        |     | 70  |      |  |  |  |  |

|                                                    |                   | S or L 55                                                                                        |     | 55  | ns   |  |  |  |  |

|                                                    |                   | S or L 45                                                                                        |     | 45  | 1.0  |  |  |  |  |

|                                                    |                   | S or L 35                                                                                        |     | 35  |      |  |  |  |  |

| Semaphore Flag Update Pulse SEM or OE              | t <sub>SOP</sub>  | ALL                                                                                              |     | 15  | ns   |  |  |  |  |

| Chip Enable Access time /7                         | t <sub>ELQV</sub> | S or L 70                                                                                        |     | 70  |      |  |  |  |  |

|                                                    |                   | S or L 55                                                                                        |     | 55  | ns   |  |  |  |  |

|                                                    |                   | S or L 45                                                                                        |     | 45  |      |  |  |  |  |

|                                                    |                   | S or L 35                                                                                        |     | 35  |      |  |  |  |  |

| Byte Enable Access time /7                         | t <sub>ABE</sub>  | S or L 70                                                                                        |     | 70  |      |  |  |  |  |

|                                                    |                   | S or L 55                                                                                        |     | 55  | ns   |  |  |  |  |

|                                                    |                   | S or L 45                                                                                        |     | 45  |      |  |  |  |  |

|                                                    |                   | S or L 35                                                                                        |     | 35  |      |  |  |  |  |

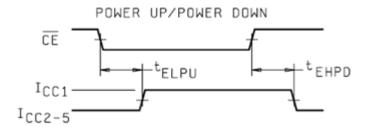

| Chip Enable to Pwr Up /6, /8                       | t <sub>ELPU</sub> | ALL                                                                                              | 0   |     | ns   |  |  |  |  |

| Chip Disable to Pwr Down /6, /8                    | t <sub>EHPD</sub> | ALL                                                                                              |     | 50  | ns   |  |  |  |  |

| Output Enable Access Time /7                       | t <sub>OLQV</sub> | ALL                                                                                              |     | 20  | ns   |  |  |  |  |

| Output Hold from Addr Change                       | t <sub>AVQX</sub> | ALL                                                                                              | 3   |     | ns   |  |  |  |  |

| Output- Low Z                                      | t <sub>OLQX</sub> | ALL                                                                                              | 3   |     | ns   |  |  |  |  |

| Output- High Z                                     | t <sub>OLQZ</sub> | S or L 70                                                                                        |     | 30  |      |  |  |  |  |

|                                                    |                   | S or L 55                                                                                        |     | 25  |      |  |  |  |  |

|                                                    |                   | S or L 45                                                                                        |     | 20  | ns   |  |  |  |  |

|                                                    |                   | S or L 35                                                                                        |     | 15  |      |  |  |  |  |

<sup>/6</sup> Measurement assumption: transition times ≤ 5 ns, input levels from GND to 3.0 V, timing ref levels of 1.5 V and output load per AC Output Test Load Type I shown herein.

<sup>/7</sup> To access RAM: CE = L, SEM = H, UB or LB = L

<sup>/8</sup> Parameter tested at initial characterization and after design change. Parameter guaranteed per limits in table.

| ELECTRICAL PERFORMANCE CHARACTERISTICS- Write Cycle |                   |                                                                                                  |     |     |      |  |  |

|-----------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------|-----|-----|------|--|--|

| Description                                         | Symbol            | Conditions<br>-55°C ≤T <sub>A</sub> ≤+125°C<br>4.5 V ≤ Vcc ≤ 5.5 V<br>Unless Otherwise Specified | Min | Max | Unit |  |  |

| Write Cycle                                         | t <sub>AVAV</sub> | S or L 70                                                                                        | 70  |     | T T  |  |  |

|                                                     |                   | S or L 55                                                                                        | 55  |     |      |  |  |

|                                                     |                   | S or L 45                                                                                        | 45  |     | ns   |  |  |

|                                                     |                   | S or L 35                                                                                        | 35  |     |      |  |  |

| Chip Enable to End-of-Write /9 /12                  | t <sub>ELWH</sub> | S or L 70                                                                                        | 50  |     |      |  |  |

|                                                     |                   | S or L 55                                                                                        | 45  |     | ns   |  |  |

|                                                     |                   | S or L 45                                                                                        | 40  |     | "    |  |  |

|                                                     |                   | S or L 35                                                                                        | 30  |     |      |  |  |

| Address valid to End of Write /12                   | t <sub>AVWH</sub> | S or L 70                                                                                        | 50  |     |      |  |  |

|                                                     |                   | S or L 55                                                                                        | 45  |     | ns   |  |  |

|                                                     |                   | S or L 45                                                                                        | 40  |     | "    |  |  |

|                                                     |                   | S or L 35                                                                                        | 30  |     |      |  |  |

| Address Set-up /9, /12                              | t <sub>AVWL</sub> | ALL                                                                                              | 0   |     | ns   |  |  |

| Write Pulse /12                                     | t <sub>WLWH</sub> | S or L 70                                                                                        | 50  |     |      |  |  |

|                                                     |                   | S or L 55                                                                                        | 40  |     | ns   |  |  |

|                                                     |                   | S or L 45                                                                                        | 35  |     | 110  |  |  |

|                                                     |                   | S or L 35                                                                                        | 30  |     |      |  |  |

| Write Recovery /12                                  | twhax             | ALL                                                                                              | 0   |     | ns   |  |  |

| Data Valid to End of Write /12                      | t <sub>DVWH</sub> | S or L 70                                                                                        | 40  |     |      |  |  |

|                                                     |                   | S or L 55                                                                                        | 30  |     | ns   |  |  |

|                                                     |                   | S or L 45                                                                                        | 25  |     |      |  |  |

|                                                     |                   | S or L 35                                                                                        | 25  |     |      |  |  |

| Output High Z                                       | t <sub>WLQZ</sub> | S or L 70                                                                                        |     | 30  |      |  |  |

|                                                     |                   | S or L 55                                                                                        |     | 25  | ns   |  |  |

|                                                     |                   | S or L 45                                                                                        |     | 20  |      |  |  |

|                                                     |                   | S or L 35                                                                                        |     | 15  |      |  |  |

| Data Hold Time /10, /12                             | t <sub>WHDX</sub> | ALL                                                                                              | 0   |     | ns   |  |  |

| Write Enable to Output (in High Z) /11              | t <sub>WLQZ</sub> | S or L 70                                                                                        |     | 30  |      |  |  |

|                                                     |                   | S or L 55                                                                                        |     | 25  | ns   |  |  |

|                                                     |                   | S or L 45                                                                                        |     | 20  |      |  |  |

|                                                     |                   | S or L 35                                                                                        |     | 15  |      |  |  |

| Output Active from End of Write /10                 | t <sub>WHQX</sub> | ALL                                                                                              | 0   |     | ns   |  |  |

| SEM Flag- Write to Read Time /12                    | tswrd             | ALL                                                                                              | 10  |     | ns   |  |  |

| SEM Flag Contention Window /12                      | t <sub>SPS</sub>  | ALL                                                                                              | 10  |     | ns   |  |  |

<sup>/9</sup> To access RAM: CE = H, SEM = H, UB or LB = L To access Semaphore: CE = h, SEM = H, UB or LB = L. Either condition must be valid for the entire  $t_{\text{EL:WH}}$  time.

$<sup>/10</sup> t_{WHDX} < t_{WHQX}$

<sup>/11</sup> Transition measured at steady-state high level -500mV or steady-state low level +500mV on the output from the 1.5 V level on the input; CL = 5 pF (ref AC Output Test Load Type II shown herein).

<sup>/12</sup> Measurement assumption: transition times ≤ 5 ns, input levels from GND to 3.0 V, timing ref levels of 1.5 V and output load per AC Output Test Load Type I shown herein.

| ELECTRICAL PERFORMANCE CHARACTERISTICS- BUSY Timing |                  |                                                                                                                    |     |          |          |  |  |  |

|-----------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------|-----|----------|----------|--|--|--|

| Description                                         | Symbol           | Conditions -55°C ≤T <sub>A</sub> ≤+125°C 4.5 V ≤ Vcc ≤ 5.5 V Unless Otherwise Specified M/ S = V <sub>IH</sub> /12 | Min | Max      | Unit     |  |  |  |

| THOY A Time for Alline                              | t <sub>BAA</sub> | S or L 70                                                                                                          |     | 45       | ns       |  |  |  |

| BUSY Access Time from Address                       | *BAA             | S or L 55                                                                                                          |     | 45       | ns       |  |  |  |

| Match                                               |                  | S or L 45                                                                                                          |     | 35       | ns       |  |  |  |

|                                                     |                  | S or L 35                                                                                                          |     | 35       | ns       |  |  |  |

| BUSY Disable Time from Address Not                  | t <sub>BDA</sub> | S or L 70                                                                                                          |     | 40       | ns       |  |  |  |

|                                                     |                  | S or L 55                                                                                                          |     | 40       | ns       |  |  |  |

| Matched                                             |                  | S or L 45                                                                                                          |     | 30       | ns       |  |  |  |

|                                                     |                  | S or L 35                                                                                                          |     | 30       | ns       |  |  |  |

| BUSY Access Time from Chip Enable                   | $T_{BAC}$        | S or L 70                                                                                                          |     | 40       | ns       |  |  |  |

| Low                                                 |                  | S or L 55                                                                                                          |     | 40       | ns       |  |  |  |

| LOW                                                 |                  | S or L 45                                                                                                          |     | 30       | ns       |  |  |  |

|                                                     | <del>-</del>     | S or L 35                                                                                                          |     | 30       | ns       |  |  |  |

| BUSY Disable Time from Chip Enable                  | $T_BDC$          | S or L 70                                                                                                          |     | 35       | ns       |  |  |  |

| High                                                |                  | S or L 55  <br>S or L 45                                                                                           |     | 35<br>25 | ns<br>ns |  |  |  |

| 1.19.1                                              |                  | S or L 35                                                                                                          |     | 25       | ns       |  |  |  |

| Arbitration priority Set-up Time                    | T <sub>APS</sub> | ALL                                                                                                                | 5   | 20       | ns       |  |  |  |

| BUSY Disable to Chip Enable High                    | $T_{BDD}$        | ALL                                                                                                                |     | 35       | ns       |  |  |  |

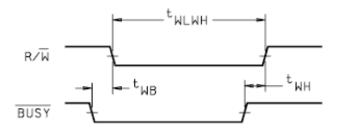

| Write Hold after BUSY                               | t <sub>WH</sub>  | ALL                                                                                                                | 25  |          | ns       |  |  |  |

<sup>/12</sup> Measurement assumption: transition times ≤ 5 ns, input levels from GND to 3.0 V, timing ref levels of 1.5 V and output load per AC Output Test Load Type I shown herein.

| ELECTRICAL PERFORMANCE CHARACTERISTICS- BUSY Timing |                 |                                                                                                                                              |     |     |      |  |  |  |  |

|-----------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|--|--|--|--|

| Description                                         | Symbol          | Conditions $-55^{\circ}C \le T_{A} \le +125^{\circ}C$ $4.5 \ V \le Vcc \le 5.5 \ V$ Unless Otherwise Specified $M/\overline{S} = V_{IL} /12$ | Min | Max | Unit |  |  |  |  |

| BUSY Input to Write                                 | t <sub>WB</sub> | ALL                                                                                                                                          | 0   |     | ns   |  |  |  |  |

| Write Hold After BUSY                               | $t_WH$          | ALL                                                                                                                                          | 25  |     | ns   |  |  |  |  |

<sup>/12</sup> Measurement assumption: transition times  $\leq$  5 ns, input levels from GND to 3.0 V, timing ref levels of 1.5 V and output load per AC Output Test Load Type I shown herein.

| ELECTRICAL PERFORMANCE CHARACTERISTICS- Port-to-Port Delay Timing |                  |                                                                                                  |     |     |      |  |  |  |  |

|-------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------|-----|-----|------|--|--|--|--|

| Description                                                       | Symbol           | Conditions<br>-55°C ≤T <sub>A</sub> ≤+125°C<br>4.5 V ≤ Vcc ≤ 5.5 V<br>Unless Otherwise Specified | Min | Max | Unit |  |  |  |  |

| Write Pulse to Data Delay                                         | t <sub>WDD</sub> | S or L 70                                                                                        |     | 95  |      |  |  |  |  |

|                                                                   |                  | S or L 55                                                                                        |     | 80  |      |  |  |  |  |

|                                                                   |                  | S or L 45                                                                                        |     | 70  | ns   |  |  |  |  |

|                                                                   |                  | S or L 35                                                                                        |     | 60  |      |  |  |  |  |

| Write Data Valid to Read Data Delay                               | t <sub>DDD</sub> | S or L 70                                                                                        |     | 80  |      |  |  |  |  |

|                                                                   |                  | S or L 55                                                                                        |     | 65  |      |  |  |  |  |

|                                                                   |                  | S or L 45                                                                                        |     | 55  | ns   |  |  |  |  |

|                                                                   |                  | S or L 35                                                                                        |     | 45  |      |  |  |  |  |

| ELECTRICAL PERFORMANCE CHARACTERISTICS- Interrupt Timing |                  |                                                                                                  |     |     |      |  |  |  |  |

|----------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------|-----|-----|------|--|--|--|--|

| Description                                              | Symbol           | Conditions<br>-55°C ≤T <sub>A</sub> ≤+125°C<br>4.5 V ≤ Vcc ≤ 5.5 V<br>Unless Otherwise Specified | Min | Max | Unit |  |  |  |  |

| Address Set-up Time                                      | t <sub>AS</sub>  | ALL                                                                                              | 0   |     | ns   |  |  |  |  |

| Write Recovery Time                                      | t <sub>WR</sub>  | ALL                                                                                              | 0   |     | ns   |  |  |  |  |

| Interrupt Set Time                                       | t <sub>NS</sub>  | S or L 70                                                                                        |     | 50  |      |  |  |  |  |

|                                                          |                  | S or L 55                                                                                        |     | 40  | ns   |  |  |  |  |

|                                                          |                  | S or L 45                                                                                        |     | 35  |      |  |  |  |  |

|                                                          |                  | S or L 35                                                                                        |     | 30  |      |  |  |  |  |

| Interrupt Reset Time                                     | t <sub>inr</sub> | S or L 70                                                                                        |     | 50  |      |  |  |  |  |

|                                                          |                  | S or L 55                                                                                        |     | 40  | ]    |  |  |  |  |

|                                                          |                  | S or L 45                                                                                        |     | 35  | ns   |  |  |  |  |

|                                                          |                  | S or L 35                                                                                        |     | 30  |      |  |  |  |  |

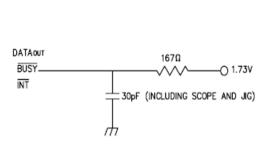

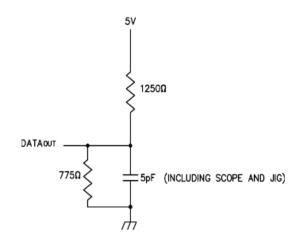

# **AC Output Test Load**

Type I

Type II (tolax twlaz twhax)

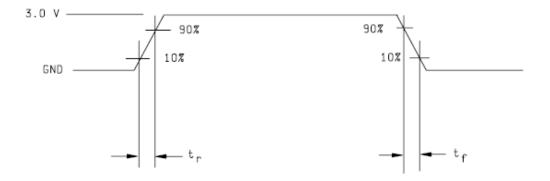

| AC TEST CONDITIONS                                         |              |  |  |  |  |

|------------------------------------------------------------|--------------|--|--|--|--|

|                                                            |              |  |  |  |  |

| Input Pulse levels                                         | GND to 3.0 V |  |  |  |  |

| Input rise & fall times (t <sub>r</sub> & t <sub>f</sub> ) | ≤ 5ns        |  |  |  |  |

| Input timing reference levels                              | 1.5 V        |  |  |  |  |

| Output reference levels                                    | 1.5 V        |  |  |  |  |

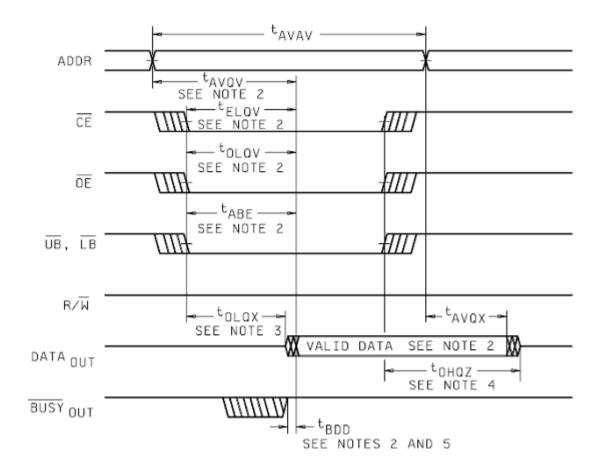

### **Read Cycle Timing**

#### Notes on read operation:

- SEM = V<sub>IH</sub>

- Start of valid data dependant upon which timing becomes effective last ( $t_{ABE}$ ,  $t_{OLQV}$ ,  $t_{ELQV}$ ,  $t_{AVQV}$ ,  $t_{BDD}$ )

- Timing dependant upon which signal asserted last ( OE , CE , LB OR UB ).

- Timing dependant upon which signal de-asserted first ( OE , CE , LB OR UB ).

- t<sub>BDD</sub> delay is required only in the case where opposite port is completing a write operation to the same address location. For simultaneous read operations, BUSY has no relation to valid output data.

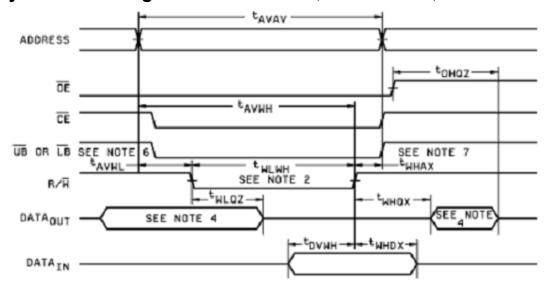

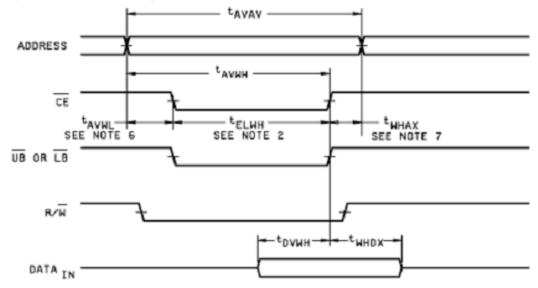

# Write Cycle Nº 1 Timing- R/ W Controlled (see notes 1, 3, 5, 8)

## Write Cycle Nº 2 Timing- CE, UB, LB Controlled (see notes 1, 3, 5, 8)

#### Notes on Write Cycle

- 1. R/W or CE or UB and LB must be high during all address transitions.

- 2. A write occurs during the overlap (t<sub>ELWH</sub> or t<sub>WLWH</sub>) of a low UB or LB and a low CE and a low R/ W for memory array write cycle.

- 3.  $t_{WHAX}$  is measured from the earlier of  $\overline{CE}$  or  $R/\overline{W}$  (or  $\overline{SEM}$  or  $R/\overline{W}$ ) going high to the end of the write cycle.

- 4. During this period, the I/O pins are in the output state and input signals must not be applied.

- 5. If the CE or SEM low transition occurs simultaneously with or after the R/W low transition, the outputs remain in the high impedance state.

- 6. Timing dependant upon which enable signal is asserted last.

- 7. Timing dependant upon which enable signal is de-asserted first.

- 8. For Write Cycle No.1, if OE is low during R/W controlled write cycle, the write pulse width must be the larger of twlwh or (twloz + tdvwh) to allow the I/O drivers to turn off and data to be placed on the bus for the required tdvwh. If OE is high during the R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified twlwh.

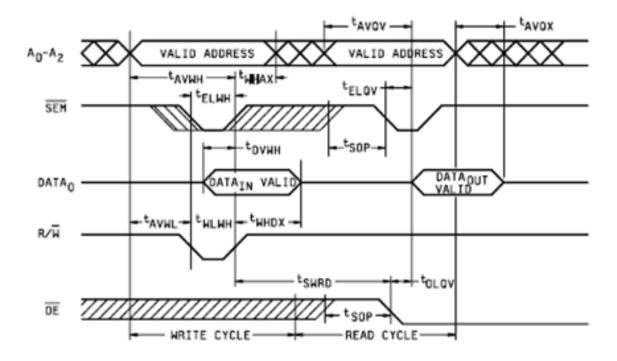

### **Semaphore Read After Write Timing**

#### Notes

- $\overline{CE} = V_{IH}$  or  $\overline{UB}$ ;  $\overline{LB} = V_{IH}$  for period of above timing for both the read and write operation.

- All inputs and outputs equal to the same semaphore value for DATA<sub>OUT</sub> VALID condition.

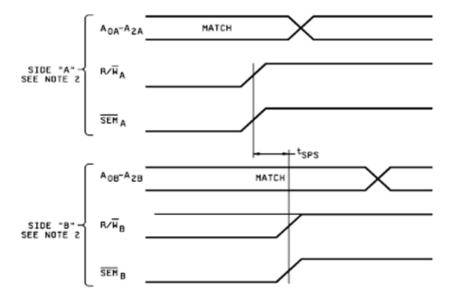

### **Semaphore Write Contention Timing**

- D<sub>OR</sub> = D<sub>OL</sub>,  $\overline{\text{CE}}$  R =  $\overline{\text{CE}}$  L = H, semaphore flag is released from both sides (reads as one from both sides) at cycle start.

- 'A' may either be the left or right port. 'B' is the opposite port from 'A'

- This parameter is measured from R/W<sub>A</sub> or SEM<sub>A</sub> going high to R/W<sub>B</sub> or SEM<sub>B</sub> going high.

- If t<sub>SPS</sub> is violated, semaphore will fall positively to one side or the other, but there is no guarantee which side will obtain the flag.

- CE = H for the duration of the Semaphore Read After Write Timing (both read and write cycle)

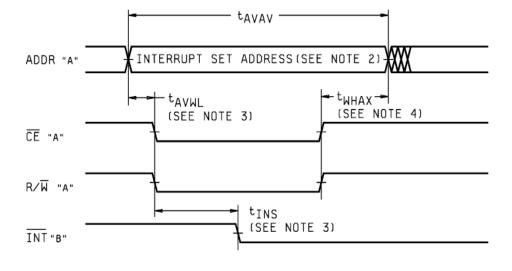

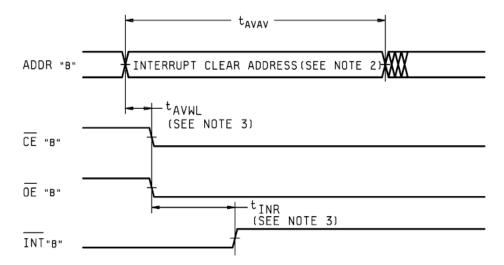

### **Interrupt Timing**

- All timing is the same for left and right ports.

- 2. Port 'A' may be either the left or right port.

- 3. See Interrupt Truth Table

- Timing is dependant upon which enable signal is asserted last ( CE or R/W)

- Timing is dependant upon which enable signal is de-asserted first ( CE or R/W)

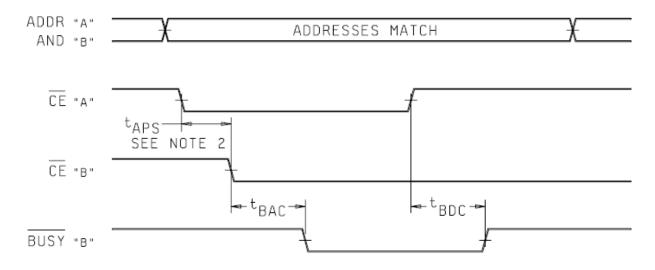

# Busy Arbitration ( $\overline{CE}$ Controlled) (M/ $\overline{S}$ = H)

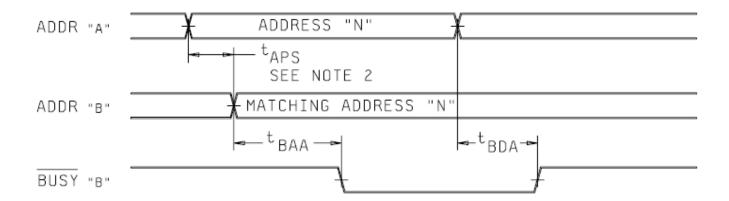

## Busy Arbitration Cycle (Address Match Controlled) (M/ $\overline{S}$ = H)

- All timing is the same for left and right ports. Port 'A' may be either the left or right port. Port 'B' is the port opposite from 'A'.

- If tAPS is violated, the busy signal will be asserted on one side or the other, but there is no guarantee on which side the busy signal will be asserted.

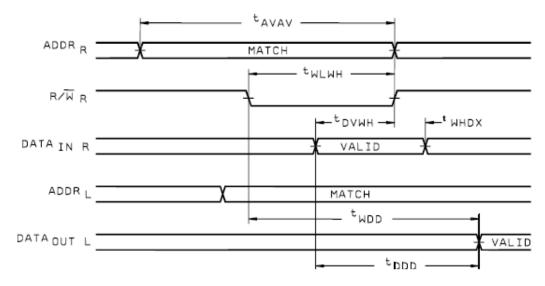

### Write with Port - to - Port Delay (M/S = L)

# Slave Write $(M/\overline{S} = L)$

### **Power-Up / Power-Down Timing**

### **Truth Table: Non-contention read write control**

| Inputs |      |    |    |    |     | Outp                | outs                |                          |

|--------|------|----|----|----|-----|---------------------|---------------------|--------------------------|

| CE     | R /W | OE | UB | LB | SEM | I/O <sub>8-15</sub> | I/O <sub>0-7</sub>  | Mode                     |

| Н      | Х    | Χ  | Χ  | Χ  | Н   | High-Z              | High-Z              | Deselected: Power-down   |

| Χ      | Х    | Χ  | Н  | Н  | Н   | High-Z              | High-Z              | Both Bytes Deselected    |

| L      | L    | Χ  | L  | Н  | Н   | DATAIN              | High-Z              | Write to Upper Byte Only |

| L      | L    | Χ  | Н  | L  | Н   | High-Z              | DATA <sub>IN</sub>  | Write to Lower Byte Only |

| L      | L    | Χ  | L  | L  | Н   | DATA <sub>IN</sub>  | DATA <sub>IN</sub>  | Write to Both Bytes      |

| L      | Н    | L  | L  | Н  | Н   | DATA <sub>OUT</sub> | High-Z              | Read Upper Byte Only     |

| L      | Н    | L  | Н  | L  | Н   | High-Z              | DATA <sub>OUT</sub> | Read Lower Byte Only     |

| L      | Н    | L  | L  | L  | Н   | DATA <sub>OUT</sub> | DATA <sub>OUT</sub> | Read Both Bytes          |

| Χ      | Χ    | Н  | Χ  | Χ  | Χ   | High-Z              | High-Z              | Outputs Disabled         |

#### Notes:

1. Read/Write controls are separate for independent left and right address ports  $(A_{0L} - A_{12L})$  and  $A_{0R} - A_{12R}$

**Truth Table: Semaphore Read/Write Control**

|    |          | Inp | outs |    |     | Outp                | outs                |                                            |

|----|----------|-----|------|----|-----|---------------------|---------------------|--------------------------------------------|

| CE | R W      | OE  | UB   | LB | SEM | I/O <sub>8-15</sub> | I/O <sub>0-7</sub>  | Mode                                       |

| Н  | Н        | L   | Х    | Χ  | L   | DATA <sub>OUT</sub> | DATA <sub>OUT</sub> | Read semaphore flag data out               |

| Χ  | Н        | L   | Н    | Н  | L   | DATA <sub>OUT</sub> | DATA <sub>OUT</sub> | Read semaphore flag data out               |

| Н  | <b>↑</b> | Х   | Χ    | X  | L   | DATA <sub>IN</sub>  | DATA <sub>IN</sub>  | Write I/O <sub>0</sub> into semaphore flag |

| Χ  | <b>↑</b> | Χ   | Н    | Н  | L   | DATA <sub>IN</sub>  | DATA <sub>IN</sub>  | Write I/O <sub>0</sub> into semaphore flag |

| L  | Χ        | Χ   | L    | Χ  | L   | _                   | -                   | -                                          |

| L  | Χ        | Χ   | Χ    | L  | L   | -                   | _                   | -                                          |

- 1. Semaphore flags are addressed by  $A_0 A_2$

- 2. Semaphore Flags are written via  $I/O_0$  and read from  $I/O_0 I/O_{15}$ .

# Truth Table: Address BUSY Arbitration

|      | Outpu           | ts                                       | Inpu   | uts                |                            |

|------|-----------------|------------------------------------------|--------|--------------------|----------------------------|

| CE L | CE <sub>R</sub> | $A_{0L} - A_{12L}$<br>$A_{0R} - A_{12R}$ | BUSY   | BUSY R             | Function                   |

| Χ    | Χ               | No Match                                 | Н      | High-Z             | Normal                     |

| Н    | Χ               | Match                                    | Н      | High-Z             | Normal                     |

| Χ    | Н               | Match                                    | Н      | High-Z             | Normal                     |

| L    | L               | Match                                    | High-Z | DATA <sub>IN</sub> | Write Inhibit <sup>2</sup> |

**Truth Table: Interrupt Flag**

|       |      | Left Port |                                    |       |                  | R               | ight Port |                                    |       |                                   |

|-------|------|-----------|------------------------------------|-------|------------------|-----------------|-----------|------------------------------------|-------|-----------------------------------|

| R/W L | CE L | OE L      | A <sub>0L</sub> - A <sub>12L</sub> | INT L | R/W <sub>R</sub> | CE <sub>R</sub> | OE R      | A <sub>0R</sub> – A <sub>12R</sub> | INT R | Function                          |

| L     | L    | Х         | 1FFF                               | Х     | Х                | Х               | Х         | Х                                  | L     | Set right INT R flag              |

| X     | X    | X         | Х                                  | X     | Х                | L               | L         | 1FFF                               | Н     | Reset right INT <sub>R</sub> flag |

| Х     | X    | Х         | Х                                  | L     | L                | L               | X         | 1FFE                               | Х     | Set left INT ∟ flag               |

| Х     | L    | L         | 1FFE                               | Н     | ×                | Х               | Х         | Х                                  | Х     | Set left INT ∟ flag               |

- 1. Assumes  $\overline{BUSY}_L = \overline{BUSY}_R = V_{IH}$

- 2. If  $\overline{BUSY}_L = V_{IL}$ , no change

- 3. If  $\overline{BUSY}_R = V_{IL}$ , no change

- $\overline{\mbox{INT}}_{\mbox{\ L}}$  and  $\overline{\mbox{INT}}_{\mbox{\ R}}$  must be initialized at power-up

**Ordering Information**

| Part Number     | Package (Mil-Std-1835) | Generic     |

|-----------------|------------------------|-------------|

| 5962-9161701MXA | CMGA15-PN              | QP7025S70GB |

| 5962-9161701MYA | CQFP84 –See Note 2     | QP7025S70FB |

| 5962-9161702MXA | CMGA15-PN              | QP7025L70GB |

| 5962-9161702MYA | CQFP84 –See Note 2     | QP7025L70FB |

| 5962-9161703MXA | CMGA15-PN              | QP7025S55GB |

| 5962-9161703MYA | CQFP84 –See Note 2     | QP7025S55FB |

| 5962-9161704MXA | CMGA15-PN              | QP7025L55GB |

| 5962-9161704MYA | CQFP84 –See Note 2     | QP7025L55FB |

| 5962-9161705MXA | CMGA15-PN              | QP7025S45GB |

| 5962-9161705MYA | CQFP84 –See Note 2     | QP7025S45FB |

| 5962-9161706MXA | CMGA15-PN              | QP7025L45GB |

| 5962-9161706MYA | CQFP84 –See Note 2     | QP7025L45FB |

| 5962-9161707MXA | CMGA15-PN              | QP7025S35GB |

| 5962-9161707MYA | CQFP84 –See Note 2     | QP7025S35FB |

| 5962-9161708MXA | CMGA15-PN              | QP7025L35GB |

| 5962-9161708MYA | CQFP84 –See Note 2     | QP7025L35FB |

#### Notes:

- 1. Package outline information and specifications are defined by Mil-Std-1835 package dimension requirements.

- 2. See SMD 5962-91617 Fig.1 Case Outline 'Y' Fig. 1

- 3. QP Semiconductor supports Source Control Drawing (SCD), and custom package development for this product family.

- 4. The listed drawings, Mil-PRF-38535, Mil-Std-883 and Mil-Std-1835 are available online at http://www.dscc.dla.mil/

- 5. Additional information is available at our website <a href="http://www.gpsemi.com">http://www.gpsemi.com</a>

### **Document Revision History**

| Date         | Revision<br>Level | Description     |

|--------------|-------------------|-----------------|

| 20 June 2010 | 0                 | initial release |

|              |                   |                 |

|              |                   |                 |