### **Power Management IC for Automotive**

# **Power Management IC for ADAS Applications**

### **BD39031MUF-C**

### **General Description**

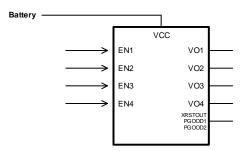

BD39031MUF-C is a power management IC with Primary Buck Controller (BUCK1), Dual Secondary Buck Converter (BUCK2/BUCK3), and Secondary Boost Converter (BOOST4). This device contains Reset, Power Good, Watchdog Timer functions, and is suitable for ADAS application such as radar, camera, and LiDAR. In addition, this device contributes to ASIL level improvement of the system by BIST (Built-In Self Test) function and Mutual Monitoring function.

#### Features

- AEC-Q100 Qualified (Note 1)

- Functional Safety Supportive Automotive Products

- Primary Buck Controller for 3.3 V Fixed

- Secondary Buck Converter for 1.2 V Output Fixed

- Secondary Buck Converter for Adjustable Output

- Secondary Boost Converter for 5.0 V Output Fixed

- Enable Input for Each Output

- Two Power Good Functions

- Reset Function for BUCK1

- Adjustable Window Watchdog Timer

- Spread Spectrum

- Over Current Protection

- Over Voltage Protection

- Short Circuit Protection

- Thermal Shut Down Protection

- **Thermal Warning Function**

- (Note 1) Grade 1

#### Applications

- ADAS Application (Radar Module, Camera Module, LiDAR Module, etc.)

- ADAS ECU

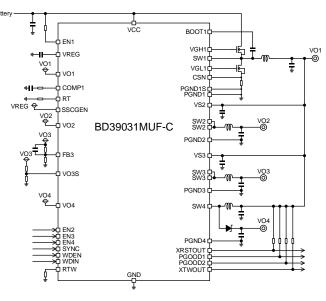

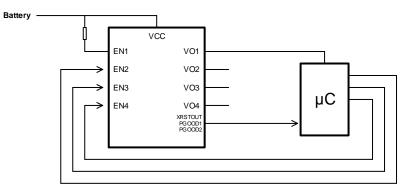

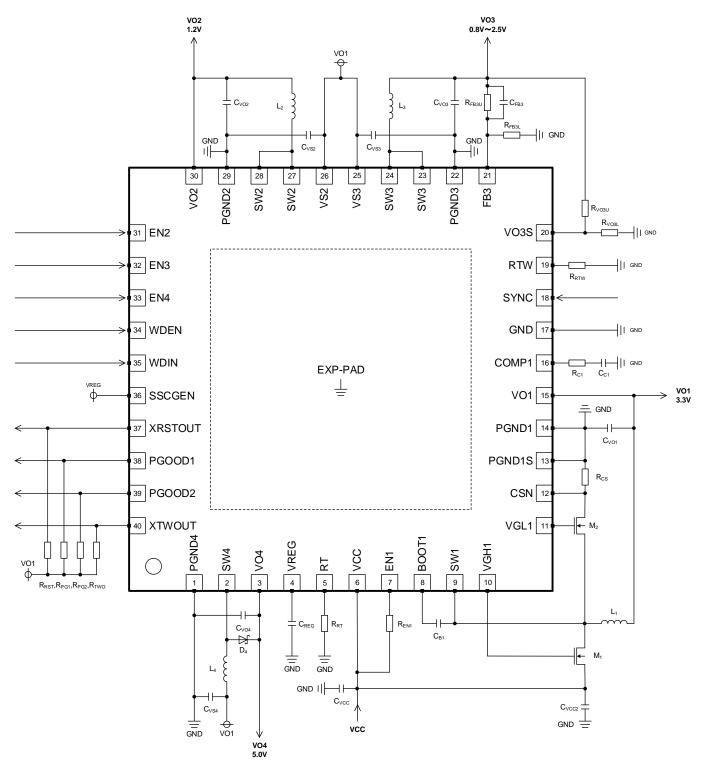

### **Typical Application Circuit**

#### **Key Specifications**

| Input Voltage Range:          | 4.0 V to 28 V     |

|-------------------------------|-------------------|

| Output Voltage:               |                   |

| BUCK1 Voltage                 | 3.3 V             |

| BUCK2 Voltage                 | 1.2 V             |

| BUCK3 Voltage                 | 0.8 V to 2.5 V    |

| BOOST4 Voltage                | 5.0 V             |

| Maximum Output Current:       |                   |

| BUCK2, BUCK3                  | 2.5 A             |

| BOOST4                        | 0.5 A             |

| Switching Frequency:          | 2.2 MHz (Typ)     |

| Standby Current:              | 0 µA (Typ)        |

| Operating Ambient Temperature |                   |

| Range:                        | -40 °C to +125 °C |

|                               |                   |

#### **Special Characteristics**

| Output Voltage Accuracy: |        |

|--------------------------|--------|

| BUCK1 VO1 Voltage        | ±1.5 % |

| BUCK2 VO2 Voltage        | ±1.5 % |

| BUCK3 FB Voltage         | ±1.5 % |

| BOOST4 VO4 Voltage       | ±2.0 % |

#### Package

VQFN40FV6060

W (Typ) x D (Typ) x H (Max) 6.0 mm x 6.0 mm x 1.0 mm

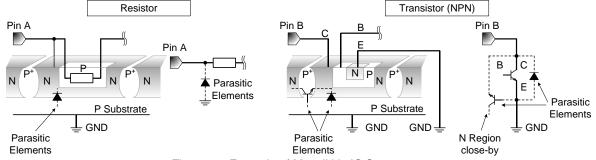

OProduct structure : Silicon integrated circuit OThis product has no designed protection against radioactive rays.

www.rohm.com © 2020 ROHM Co., Ltd. All rights reserved. TSZ22111 • 14 • 001

TSZ02201-0A2A0AP00440-1-2 05.Mar.2020 Rev.001

## Contents

| General Description                          | 1  |

|----------------------------------------------|----|

| Features                                     | 1  |

| Applications                                 | 1  |

| Key Specifications                           | 1  |

| Package                                      | 1  |

| Typical Application Circuit                  | 1  |

| Pin Configurations                           | 3  |

| Pin Descriptions                             | 4  |

| Block Diagrams                               | 5  |

| Description of Blocks                        | 8  |

| Absolute Maximum Ratings                     | 17 |

| Thermal Resistance                           | 17 |

| Recommended Operating Conditions             | 18 |

| Electrical Characteristics                   | 18 |

| Typical Performance Curves                   | 22 |

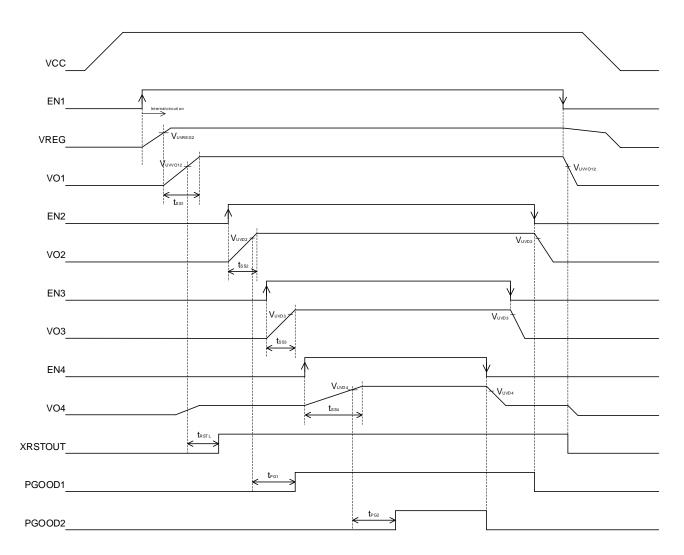

| Timing Chart                                 | 29 |

| Application Example                          | 34 |

| Selection of Components Externally Connected | 35 |

| Operational Notes                            | 46 |

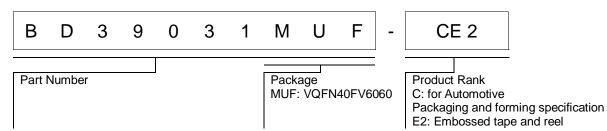

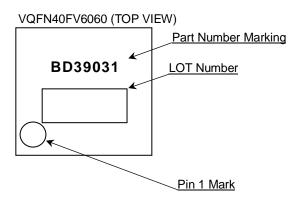

| Ordering Information                         |    |

| Marking Diagrams                             | 48 |

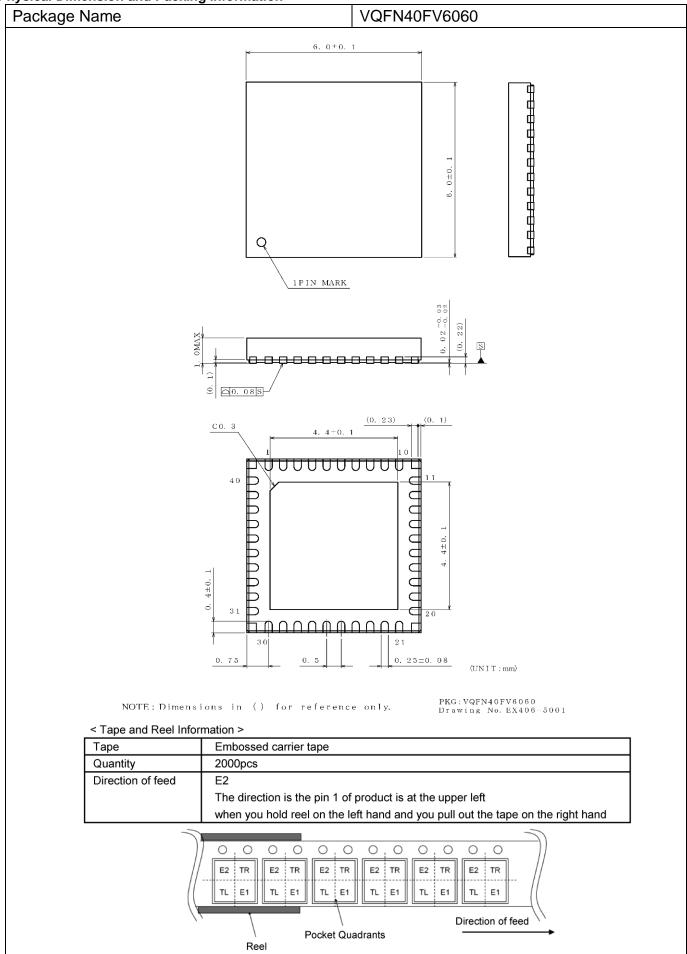

| Physical Dimension and Packing Information   | 49 |

| Revision History                             | 50 |

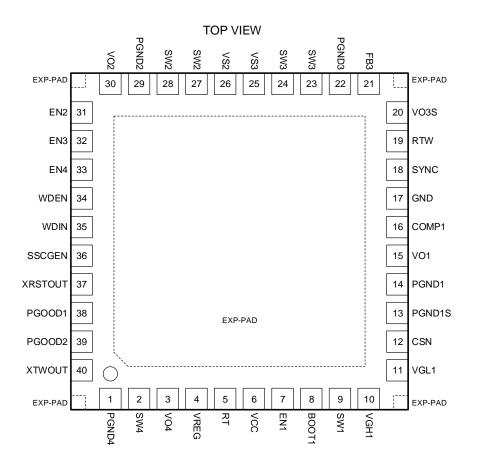

### **Pin Configurations**

### **Pin Descriptions**

| Pin No. | Pin Name | Function                                                                                                                                                       |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PGND4    | Power ground of BOOST4 converter.                                                                                                                              |

| 2       | SW4      | BOOST4 switching node.                                                                                                                                         |

| 3       | VO4      | BOOST4 feedback pin. Connect to VO4 output voltage.                                                                                                            |

| 4       | VREG     | Internal regulator of 5 V output. Connect output capacitor.<br>Can't be used for external power supply.                                                        |

| 5       | RT       | Switching frequency set pin. Connect resistor between RT and GND.                                                                                              |

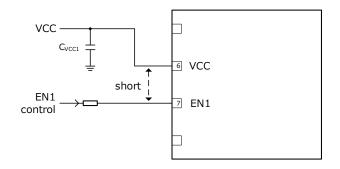

| 6       | VCC      | Power supply.                                                                                                                                                  |

| 7       | EN1      | Enable input for internal reference circuit and BUCK1. Controlled by external microcomputer or pulled up to VCC.                                               |

| 8       | BOOT1    | BUCK1 power supply for high side FET. Connect capacitor between BOOT1 and SW1.                                                                                 |

| 9       | SW1      | BUCK1 switching node. (Floating ground for high side FET)                                                                                                      |

| 10      | VGH1     | BUCK1 gate driver for high side FET.                                                                                                                           |

| 11      | VGL1     | BUCK1 gate driver for low side FET.                                                                                                                            |

| 12      | CSN      | Differential current sense for BUCK1. Connect resistor between CSN and PGND1S.                                                                                 |

| 13      | PGND1S   | Differential current sense for BUCK1. Connect resistor between CSN and PGND1S.                                                                                 |

| 14      | PGND1    | Power ground of BUCK1.                                                                                                                                         |

| 15      | VO1      | BUCK1 feedback pin.                                                                                                                                            |

| 16      | COMP1    | Error amplifier output for BUCK1 controller.                                                                                                                   |

| 17      | GND      | Analog ground.                                                                                                                                                 |

| 18      | SYNC     | Synchronization input pin. This pin can be driven by external clock to set desired switching frequency.                                                        |

| 19      | RTW      | WDT frequency setting pin. Put resistor between the RTW pin and GND.                                                                                           |

| 20      | VO3S     | BUCK3 input for external sense voltage of VO3.                                                                                                                 |

| 21      | FB3      | BUCK3 feedback pin. Input external resistance division between output and GND.                                                                                 |

| 22      | PGND3    | Power ground for BUCK3.                                                                                                                                        |

| 23      | SW3      | BUCK3 switching node.                                                                                                                                          |

| 24      | SW3      | BUCK3 switching node.                                                                                                                                          |

| 25      | VS3      | Power supply for BUCK3. Connect to VO1 output voltage.                                                                                                         |

| 26      | VS2      | Power supply for BUCK2. Connect to VO1 output voltage.                                                                                                         |

| 27      | SW2      | BUCK2 switching node.                                                                                                                                          |

| 28      | SW2      | BUCK2 switching node.                                                                                                                                          |

| 29      | PGND2    | Power ground for BUCK2.                                                                                                                                        |

| 30      | VO2      | BUCK2 feedback pin.                                                                                                                                            |

| 31      | EN2      | Enable pin for BUCK2.                                                                                                                                          |

| 32      | EN3      | Enable pin for BUCK3.                                                                                                                                          |

| 33      | EN4      | Enable pin for BOOST4.                                                                                                                                         |

| 34      | WDEN     | Enable pin for WDT.                                                                                                                                            |

| 35      | WDIN     | Clock input pin for WDT.                                                                                                                                       |

| 36      | SSCGEN   | Enable pin for Spread Spectrum function. Connect to VREG or GND.                                                                                               |

| 37      | XRSTOUT  | Reset Nch open drain output pin.                                                                                                                               |

| 38      | PGOOD1   | Power Good Nch open drain output pin for BUCK2.                                                                                                                |

| 39      | PGOOD2   | Power Good Nch open drain output pin for all outputs.                                                                                                          |

| 40      | XTWOUT   | Thermal warning Nch open drain output pin.                                                                                                                     |

| -       | EXP-PAD  | The EXP-PAD of the center of product is connected to PCB ground plane.<br>The EXP-PADs on the center and corner of the product are shorted inside the package. |

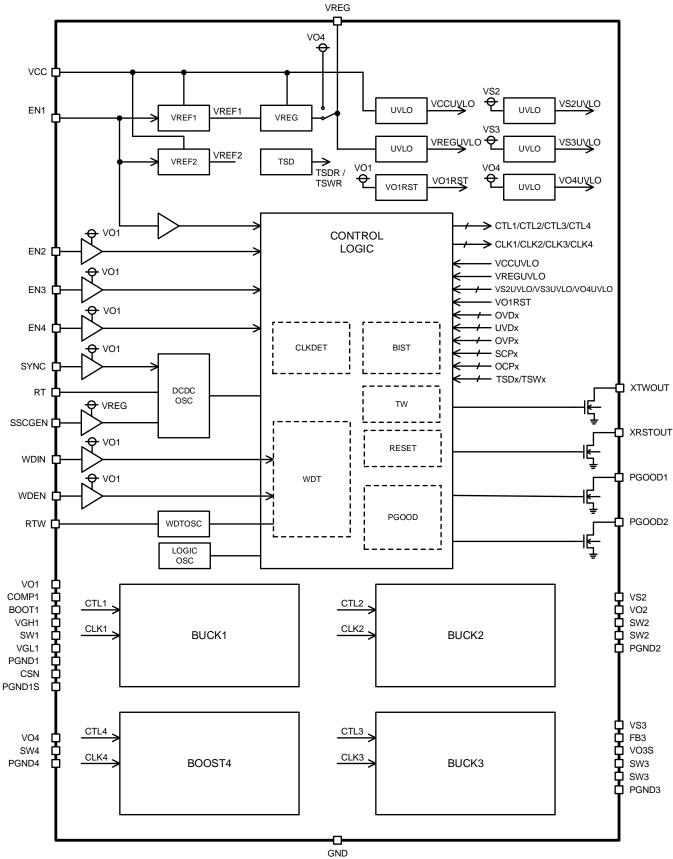

### **Block Diagrams**

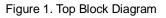

<TOP BLOCK>

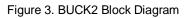

### **Block Diagrams - continued**

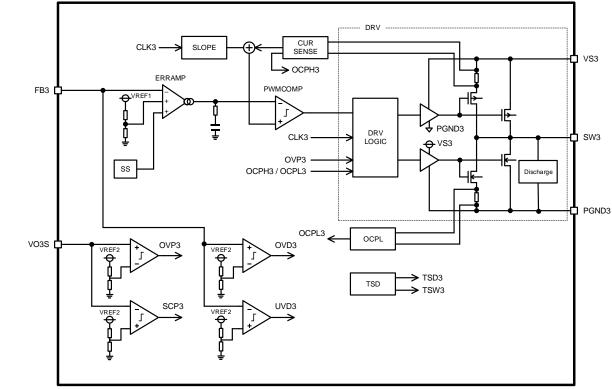

### **Block Diagrams - continued**

<BUCK3>

### **Description of Blocks**

#### 1. TOP BLOCK

#### Reference Voltage (VREF1, VREF2)

There are 2 reference voltages; VREF1 and VREF2.

VREF1 is used for each regulator control reference voltage and VREF2 is used for each protection function reference voltage.

After VCC input, VREF1 and VREF2 will startup when EN1 is turned to high. VREF1 and VREF2 will stop when EN1 is turned to low.

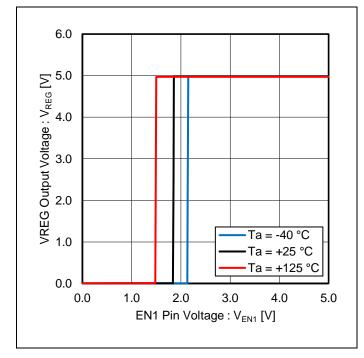

#### Internal Regulator (VREG)

VREG is 5 V (Typ) regulator for internal circuit. Needs to connect external capacitor to the VREG pin. After VCC input, VREG will startup when EN1 is turned to high. VREG will stop when EN1 is turned to low. Do not use VREG for any other purposes. Also internal regulator will be switched to VO4 after VO4 output becomes more than 4.5 V (Typ) and soft start of BOOST4 is completed.

#### Under Voltage Lock-Out (UVLO)

UVLO is under voltage lockout circuit. Prevents internal circuit malfunction when power supply startup or is at lower input voltage. Monitors VCC, VREG, VS2, VS3, and VO4 voltage and activates when each voltage goes under each threshold voltage. When VCCUVLO or VREGUVLO is detected, all the outputs will turn off. When VS2UVLO is detected, BUCK2 will turn off. When VS3UVLO is detected, BUCK3 will turn off. When VO4UVLO is detected, BOCST4 will turn off.

#### Oscillator (LOGICOSC, WDTOSC, DCDCOSC)

There are 3 types of oscillator. One for Control Logic, the second for Watch Dog Timer and the third for BUCK1, BUCK2, BUCK3 and BOOST4. BUCK3 clock phase is 180 deg shifted from BUCK1, BUCK2 and BOOST4 to reduce switching noise. Connect 9.1 k $\Omega$  between RT and GND.

#### Spread Spectrum Clock Generator (SSCG)

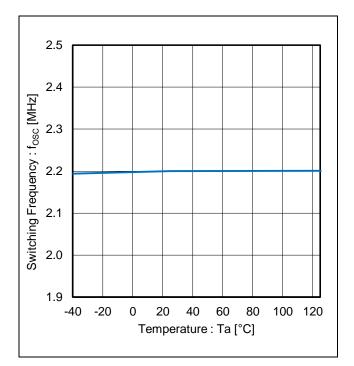

OSC block built in spread spectrum clock generator (SSCG) function. This function activates when the SSCGEN pin is connected to VREG. When the SSCGEN pin is connected to GND, SSCG function is disable. The modulation range of Spread Spectrum is between +6.2% (Typ) and -6.2% (Typ) from the typical frequency. Also, modulation frequency is set to 1.075 kHz (Typ). The modulation range and modulation frequency are fixed.

#### Synchronization mode (SYNC)

Switching frequency can be synchronized to an external clock signal using the SYNC pin. The SYNC pin allows the operating frequency to be varied above and below the frequency setting. Adjustment range is from +10 % to -10 %. The RT resistor must always be connected to initialize the operating frequency.

#### Control Logic (CONTROL LOGIC)

This block controls startup/stop sequence, Reset, Power Good, Watch Dog Timer, mutual monitoring function, Built-In Self Test (BIST), and each protection. Control Logic will be active when internal power supply VREGUVLO is released. When VREGUVLO is detected, Control Logic will reset and initialize.

#### Reset (RESET)

This block informs output voltage for microcomputer which is completely ON by reset signal. Pull up this pin to VO1 or external power supply using resistor. The XRSTOUT pin goes low when internal circuit is in abnormal conditions. The XRSTOUT pin goes high when all the following conditions are satisfied.

- a) VO1 voltage is higher than 2.6 V (Typ)

- b) BIST result are OK

- c) Mutual monitoring result are OK

- d) No detection of WDT FAST Timeout / SLOW Timeout

XRSTOUT goes High 10 ms (Typ) after all conditions are satisfied.

#### Power Good (PGOOD)

This block informs whether each regulator output startups normally or not. Power Good have UVD and OVD for each regulator and asserts it by Power Good pin. Pull up this pin to VO1 or to external power supply using resistor.

This product has 2 Power Good pins. Each pin monitors the following regulator.

- PGOOD1 : Only BUCK2

- PGOOD2 : BUCK1, BUCK2, BUCK3, and BOOST4

PGOOD1, PGOOD2 goes High 10 ms (Typ) after all conditions are satisfied.

### **TOP BLOCK - continued**

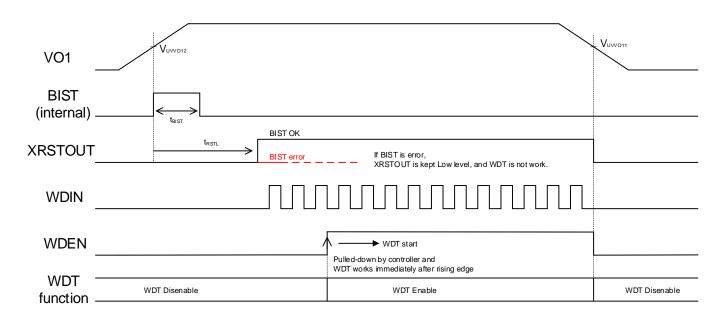

#### Built-In Self Test (BIST)

When VCCUVLO and VREGUVLO are released, and VO1 voltage is higher than 2.6 V (Typ), BIST is performed and self-test for each OVD/UVD and RESET comparators are executed to check if each comparator correctly toggles their high/low output based on input voltage change. Once BIST ends without any error, the XRSTOUT pin becomes high. If an error is found during BIST, the XRSTOUT pin keeps low and BIST is repeated until it passes.

#### Clock Mutual Detect (CLKDET)

CLKDET block monitors each clock outputted from each OSC blocks mutually. If any one of their frequency exceeds range, XRSTOUT goes low.

Thermal Warning (TW)

This block monitors internal temperature and detect when it reaches 135 degree (Typ). Pull up this pin to VO1 or external power supply using resistor. The XTWOUT pin goes Low when internal temperature is higher than threshold. The XTWOUT pin goes High when internal temperature is lower than threshold. This block only warns of internal temperature getting high. Hence, all function works normally even with this function detected. Thermal Warning function works when VCCUVLO, VREGUVLO, and Reset function are not detected. When it is not working, the XTWOUT pin is kept at high level.

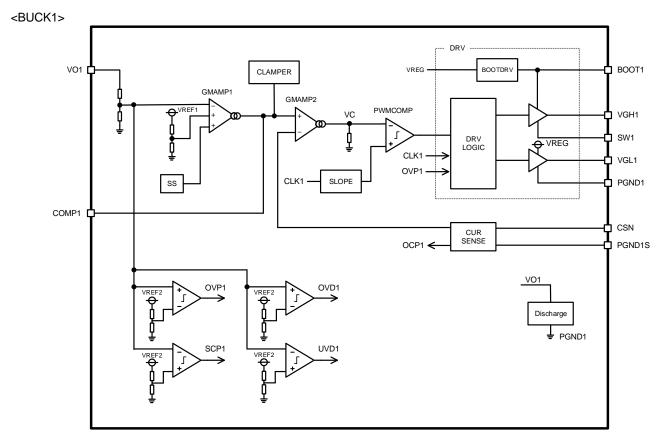

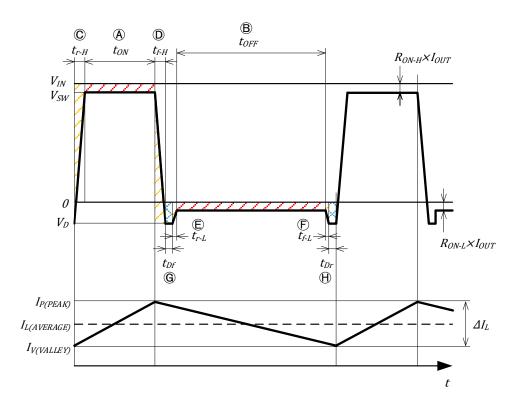

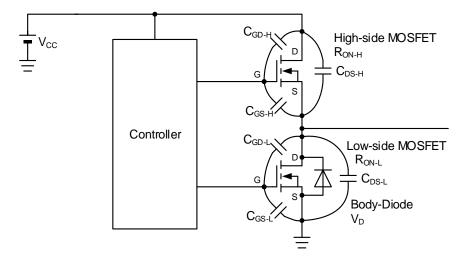

#### 2. BUCK1 BLOCK

BUCK1 is Primary Buck Controller. It is necessary to connect external MOSEFT. Output voltage is 3.3 V (Typ) fixed.

- GMAMP1 Error amplifier which have reference voltage VREF1 and VO1 divider input. Also phase compensation of BUCK1 can be adjust by inserting capacitor and resistor to the COMP1 pin.

- GMAMP2 Error amplifier which have output of GMAMP1 and current sense signal input. This block generates the VC voltage to control duty.

- SS Soft Start (SS) function prevent overshoot of output voltage and rush current by gradually increasing ON duty of switching pulse. Soft start time is fixed internally.

- CLAMPER CLAMPER limits the maximum and minimum value of coil current and works as over current protection. When coil current reaches maximum value, it makes duty small and reduces the output voltage. Similarly, when coil current reaches and minimum value, it increases duty and raise the output voltage.

- CURSENSE Detects the amount of current flowing through the inductance using resistor which is connected between the CSN pin and the PGND1S pin, and feedbacks current sense signal to GMAMP2.

- SLOPE This is the block which makes slope waveform from clock generated at OSC block. This slope waveform is combined with current sense and sends to PWMCOMP.

- PWMCOMP This compares slope waveform including current information with GMAMP2 output, and sends output signal to DRV block.

- BUCK1 Driver block. Drives external FET which is connect to VGH1 and VGL1 by using signal from PWMCOMP.

**Pulse Skip Function**

BUCK1 controller needs on time for low side FET to charge the BOOT1 pin, because high side FET is driven by boot strap. Therefore, it sets minimum off time, and the output voltage is limited by this in the condition where the input and output voltage are close

As for this countermeasure, DRV skips off pulse when the voltage difference of the input and output becomes small, and continuously turns on high side FET and keeps max duty to rise. The off pulse skip will occer 4 consectutive times as maximum.

### **Description of Blocks - continued**

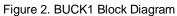

#### 3. BUCK2 BLOCK

BUCK2 is Secondary Buck converter. Output voltage is 1.2 V (Typ) fixed. EN2 = High turns on BUCK2 and EN2 = Low turns off BUCK2.

| • ERRAMP | Error Amplifier with reference voltage and VO2 divider input.<br>Controls on duty width of switching pulse by internal COMP2 node which is an ERRAMP output.<br>Capacitor and resistor for phase compensation are fixed. |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • SS     | Soft Start (SS) function prevent overshoot of output voltage and rush current by gradually increasing on duty of switching pulse. Soft start time is fixed internally.                                                   |

| SLOPE    | This is the block which makes slope waveform from clock generated at OSC block. This slope waveform is combined with current sense and is sent to PWMCOMP.                                                               |

| PWMCOMP  | This compares slope waveform including current information with ERRAMP output, and sends output signal to DRV block.                                                                                                     |

| • DRV    | BUCK2 Driver block. Drives internal FET by using signal from PWMCOMP.                                                                                                                                                    |

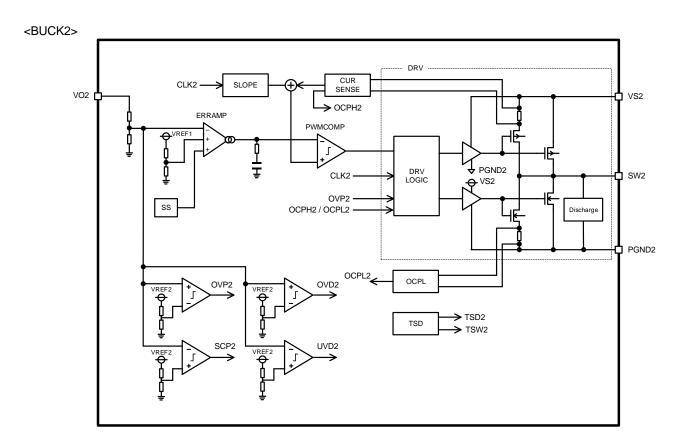

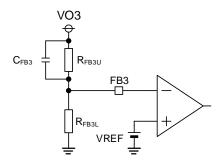

#### 4. BUCK3 BLOCK

BUCK3 is Secondary Buck converter. Output voltage can be set by external resistor. EN3 = High turns on BUCK3 and EN3 = Low turns off BUCK3.

- ERRAMP Error Amplifier with reference voltage and FB3 input. Controls on duty width of switching pulse by internal COMP3 node which is an ERRAMP output. Capacitor and resistor for phase compensation are fixed.

SS Soft Start (SS) function prevent overshoot of output voltage and rush current by gradually increasi

- SS Soft Start (SS) function prevent overshoot of output voltage and rush current by gradually increasing on duty of switching pulse. Soft start time is fixed internally.

- SLOPE This is the block which makes slope waveform from clock generated at OSC block. This slope waveform is combined with current sense and is sent to PWMCOMP.

- PWMCOMP This compares slope waveform including current information with ERRAMP output, and sends output signal to DRV block.

- BUCK3 Driver block. Drives internal FET by using signal from PWMCOMP.

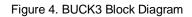

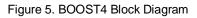

#### 5. BOOST4 BLOCK

BOOST4 is Secondary Boost converter. Output voltage is 5.0 V (Typ) fixed. EN4 = High turns on BOOST4 and EN4 = Low turns off BOOST4.

- ERRAMP Error Amplifier with reference voltage and VO4 divider input. Controls on duty width of switching pulse by internal COMP4 node which is an ERRAMP output. Capacitor and resistor for phase compensation are fixed.

SS Soft Start (SS) function prevent overshoot of output voltage and rush current by gradually increasing on duty of switching pulse. Soft start time is fixed internally.

- SLOPE This is the block which makes slope waveform from clock generated at OSC block. This slope waveform is combined with current sense and is sent to PWMCOMP.

- PWMCOMP After compared with slope waveform which has been combined with current sense and ERRAMP output, sends signal to DRV block.

- DRV BOOST4 Driver block. Drives internal FET by using signal from PWMCOMP.

### **Description of Blocks - continued**

#### 6. Detection Function

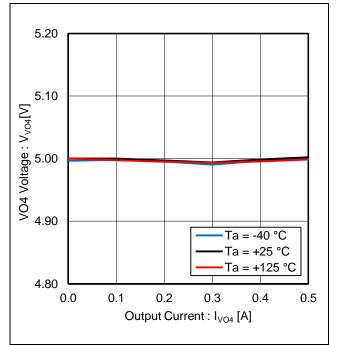

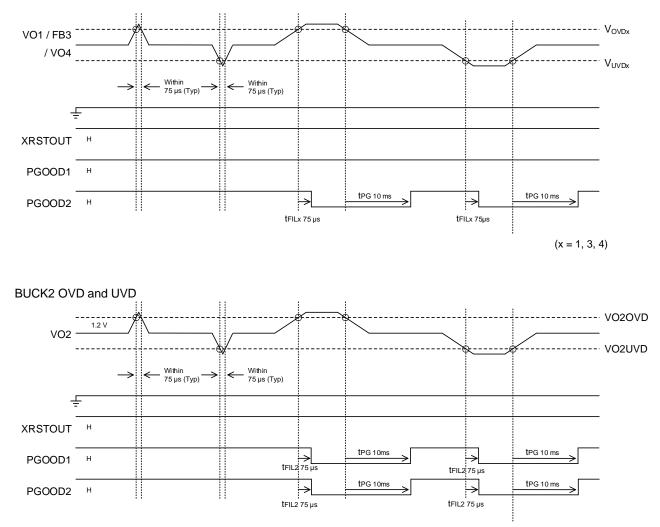

#### Over Voltage Detection (OVD)

If output voltage goes higher than threshold voltage, OVD is detected and the PGOOD pin goes down to low. Detection pins are VO1, VO2, FB3, and VO4. If VO2 detects OVD, PGOOD1 goes down to low and if either VO1, VO2, FB3, or VO4 detects OVD, PGOOD2 goes down to low.

Under Voltage Detection (UVD)

If output voltage goes lower than threshold voltage, UVD is detected and the PGOOD pin goes down to low. Detection pins are VO1, VO2, FB3 and VO4. If VO2 detects UVD, PGOOD1 goes down to low and if either VO1, VO2, FB3, or VO4 detects UVD, PGOOD2 goes down to low.

#### 7. Protection Function

Over Voltage Protection (OVP)

If output voltage goes higher than threshold voltage, OVP is detected and switching will turn off. Detection pins are VO1, VO2, VO3S, and VO4. If OVP is detected for continuous 1ms (Typ), switching will turn off and soft start will discharge. After that, output continues to stop for 10 ms (Typ) and re-starts automatically by soft start.

#### Short Circuit Protection (SCP)

When output voltage is shorted to GND (or when output voltage is lower than SCP threshold voltage) for 1 ms (Typ), switching will turn off and soft start will discharge. After that, output continues to stop for 10 ms (Typ) and re-starts automatically by soft start. Detection pins are VO1, VO2, VO3S, and VO4. Before each voltage startups, or are in soft start status, SCP function is masked.

#### Over Current Protection (OCP)

When over current goes through output FET, over current protection will be detected and output pulse width will be limited. For BUCK1, over current protection will be detected when the voltage between CSN and PGND1S goes more than 75 mV (Typ).

For BUCK2 and BUCK3, over current protection will be detected when current goes through more than 3.0 A to integrated FET. For BOOST4, over current protection will be detected when current goes through more than 1.0 A to integrated FET.

When OCP is detected continuously for more than 1 ms (Typ), switching will turn off and soft start will discharge. However, time counter is not stated until soft start of each output is completed.

After turn off by OCP, output continues to stop for 10 ms (Typ) and re-starts automatically by soft start.

#### BUCK1 OCP

BUCK1 contains OCP detection function to protect FET. To prevent destruction between source and drain of high side FET, when SW1 voltage falls 0.35 V lower than VCC (Typ), high side FET keeps to turn off.

#### OCPL2/OCPL3

These OCP watches the negative current of low side FET. This is designed to protect lower FET when output is applied from outside. If OCPL2 or OCPL3 detects, each low side FET will turn off. At the time of BUCK2 and BUCK3 startup, detection level of OCPL2/OCPL3 is at lower setting than normal operation for stable startup of the system.

### **Protection Function - continued**

Protection

The value in this list is typical unless otherwise specified.

| Block  | Protection | Detect                                            | Release                                           | Detection action                                                                                                       |

|--------|------------|---------------------------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|        | VCCUVLO    | V <sub>CC</sub> < 3.8 V                           | V <sub>CC</sub> > 4.2 V                           | BUCK1, BUCK2, BUCK3, BOOST4 OFF<br>XRSTOUT = PGOOD1 = PGOOD2 = Low                                                     |

| ALL    | VREGUVLO   | V <sub>REG</sub> < 3.5 V                          | V <sub>REG</sub> > 3.6 V                          | BUCK1, BUCK2, BUCK3, BOOST4 OFF<br>Internal OSC OFF<br>XRSTOUT = PGOOD1 = PGOOD2 = Low                                 |

|        | TSD        | Tj > 175 °C                                       | -                                                 | BUCK1, BUCK2, BUCK3, BOOST4 OFF<br>After 10 ms, re-startup                                                             |

|        | OVP1       | V <sub>V01</sub> > 4.25 V                         | V <sub>V01</sub> < 4.0 V                          | BUCK1 VGH = Low, VGL = Low<br>Detected continuous 1 ms, BUCK1, BUCK2, BUCK3,<br>BOOST4 OFF<br>After 10 ms, re-startup  |

| BUCK1  | SCP1       | V <sub>VO1</sub> < 1.65 V                         | V <sub>VO1</sub> > 1.815 V                        | Detected continuous 1 ms, BUCK1, BUCK2, BUCK3,<br>BOOST4 OFF<br>After 10 ms, re-startup                                |

|        | OCP1       | V <sub>CSN</sub> - V <sub>PGND1S</sub><br>> 75 mV | V <sub>CSN</sub> - V <sub>PGND1S</sub><br>< 75 mV | Pulse width will be limited<br>Detected continuous 1 ms, BUCK1, BUCK2, BUCK3,<br>BOOST4 OFF<br>After 10 ms, re-startup |

|        | VS2UVLO    | V <sub>S2</sub> < 2.5 V                           | V <sub>S2</sub> > 2.7 V                           | BUCK2 OFF                                                                                                              |

| BUCK2  | OVP2       | V <sub>VO2</sub> > 1.44 V                         | V <sub>VO2</sub> < 1.32 V                         | SW2 Hiz<br>Detected continuous 1 ms, BUCK2 OFF,<br>After 10 ms, re-startup                                             |

| DOORZ  | SCP2       | V <sub>VO2</sub> < 0.60 V                         | $V_{VO2} > 0.72 V$                                | Detected continuous 1 ms, BUCK2 OFF,<br>After 10 ms, re-startup                                                        |

|        | OCP2       | I <sub>VS2</sub> > 3.0 A (Min)                    | I <sub>VS2</sub> < 3.0 A (Min)                    | Pulse width will be limited<br>Detected continuous 1 ms, BUCK2 OFF,<br>After 10 ms, re-startup                         |

|        | VS3UVLO    | V <sub>S3</sub> < 2.5 V                           | V <sub>S3</sub> > 2.7 V                           | BUCK3 OFF                                                                                                              |

| BUCK3  | OVP3       | V <sub>VO3S</sub> > 0.96 V                        | V <sub>VO3S</sub> < 0.88 V                        | SW3 Hiz<br>Detected continuous 1 ms, BUCK3 OFF,<br>After 10 ms, re-startup                                             |

| Deento | SCP3       | V <sub>VO3S</sub> < 0.40 V                        | V <sub>VO3S</sub> > 0.48 V                        | Detected continuous 1 ms, BUCK3 OFF,<br>After 10 ms, re-startup                                                        |

|        | OCP3       | I <sub>VS3</sub> > 3.0 A (Min)                    | I <sub>VS3</sub> < 3.0 A (Min)                    | Pulse width will be limited<br>Detected continuous 1 ms, BUCK3 OFF,<br>After 10 ms, re-startup                         |

|        | VO4UVLO    | V <sub>VO4</sub> < 1.8 V                          | V <sub>VO4</sub> > 2.0 V                          | BOOST4 OFF                                                                                                             |

| BOOST4 | OVP4       | V <sub>VO4</sub> > 6.5 V                          | V <sub>VO4</sub> < 6.25 V                         | SW4 Hiz<br>Detected continuous 1 ms, BOOST4 OFF,<br>After 10 ms, re-startup                                            |

|        | SCP4       | V <sub>VO4</sub> < 2.5 V                          | V <sub>VO4</sub> > 3.0 V                          | Detected continuous 1 ms, BOOST4 OFF,<br>After 10 ms, re-startup                                                       |

|        | OCP4       | I <sub>SW4</sub> > 1.0 A (Min)                    | I <sub>SW4</sub> < 1.0 A (Min)                    | Pulse width will be limited<br>Detected continuous 1 ms, BOOST4 OFF,<br>After 10 ms, re-startup                        |

### **Description of Blocks - continued**

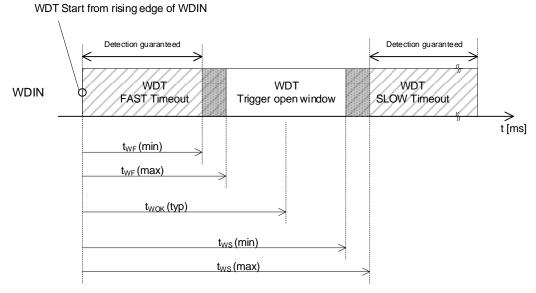

#### 8. Watchdog Timer (WDT)

Watch Dog Timer (WDT) monitors microprocessor's operation by detecting the time between rising edge of WDIN signal. When both WDEN and XRSTOUT are high, WDT is activated. If BIST result is an error, WDT will not work for XRSTOUT is kept low.

As long as the period of WDIN clock is kept within "Trigger Open Window" as in Figure 6., WDT will not detect any error and XRSTOUT will stay at high.

Figure 6. WDT Window Description

### Watchdog Timer - continued

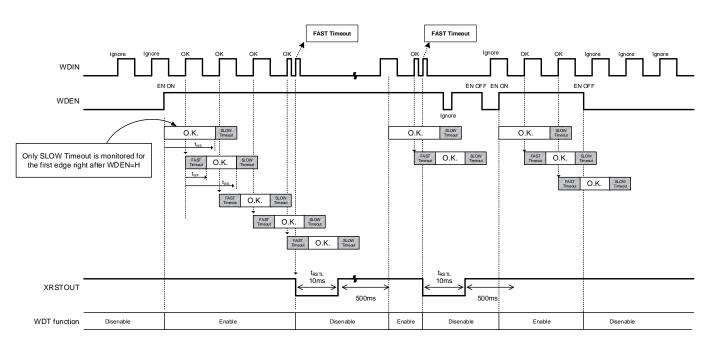

#### WDT FAST Timeout Detection

When WDEN is low, WDT is disabled. During this period WDIN input signal is ignored and XRSTOUT output is not affected. When both WDEN and XRSTOUT are high, WDT is activated. Just after WDT is active during this first period, only SLOW Timeout detection works and FAST Timeout doesn't work. The rising edge of WDIN comes within SLOW Timeout, both FAST Timeout and SLOW Timeout detection start to work. WDT detection monitors the time between this rising edge and the next rising edge. When it detects WDIN rising edge within FAST Timeout ( $t_{WF}$ ), XRSTOUT becomes low. XRSTOUT goes back to high after 10 ms delay. Then, WDT works after 500 ms delay again. This delay time is implemented as a time for microprocessor to be reset normally and to stabilized. If this time is unnecessary and WDT should be activated as soon as possible, WDEN may be controlled from low to high.

Figure 7. WDT FAST Timeout detection

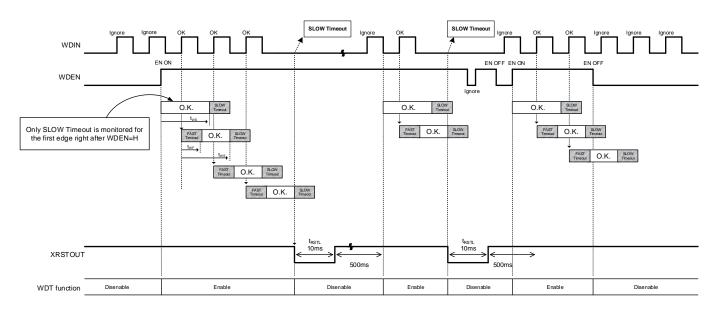

### Watchdog Timer - continued

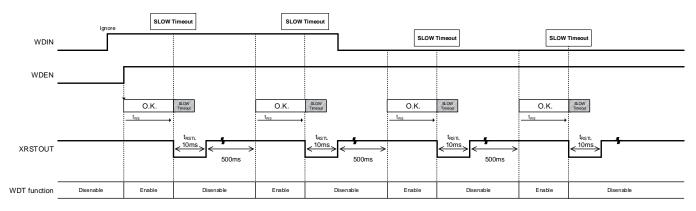

#### WDT SLOW Timeout Detection

When WDEN is low, WDT is disabled. During this period WDIN input signal is ignored and XRSTOUT output is not affected. When both WDEN and XRSTOUT are high, WDT is activated. Just after WDT is active during this first period, only SLOW Timeout detection works and FAST Timeout doesn't work. The rising edge of WDIN comes within SLOW Timeout, both FAST Timeout and SLOW Timeout detection start to work. WDT detection monitors the time between this rising edge and the next rising edge. When it can't detect WDIN rising edge within SLOW Timeout (tws), XRSTOUT becomes low. XRSTOUT goes back to high after 10 ms delay. Then, WDT works after 500 ms delay again. This delay time is implemented as a time for microprocessor to be reset normally and to stabilized. If this time is unnecessary and WDT should be activated as soon as possible, WDEN may be controlled from low to high.

Figure 8. WDT SLOW Timeout Detection

### WDT SLOW timeout detection - continued

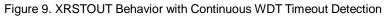

The window time for detection can be changed by the resistor value between RTW and GND. Following figure shows the detection time determined by  $R_{RTW}$  resistor value. Refer to a table of electric characteristic regarding an accuracy. Customer can choose the value ranging from 10 k $\Omega$  to 47 k $\Omega$  according to their clock frequency. The ratio for detection time is fixed and can be shown like this, FAST Timeout: SLOW Timeout = 1: 4.

Figure 10. Detection time vs R<sub>RTW</sub> resistance

#### **Absolute Maximum Ratings**

| Parameter                               | Symbol                                                  | Rating                        | Unit |

|-----------------------------------------|---------------------------------------------------------|-------------------------------|------|

| VCC Voltage                             | V <sub>cc</sub>                                         | -0.3 to +42                   | V    |

| VS2, VS3 Voltage                        | V <sub>S2,</sub> V <sub>S3</sub>                        | -0.3 to +6                    | V    |

| EN1 Voltage                             | V <sub>EN1</sub>                                        | -0.3 to +42                   | V    |

| EN2, EN3, EN4 Voltage                   | V <sub>EN2,</sub> V <sub>EN3,</sub><br>V <sub>EN4</sub> | -0.3 to +7                    | V    |

| VO1 Voltage                             | V <sub>VO1</sub>                                        | -0.3 to +7                    | V    |

| VO2 Voltage                             | V <sub>VO2</sub>                                        | -0.3 to V <sub>REG</sub> +0.3 | V    |

| FB3 Voltage                             | V <sub>FB3</sub>                                        | -0.3 to V <sub>REG</sub> +0.3 | V    |

| VO3S Voltage                            | V <sub>VO3S</sub>                                       | -0.3 to V <sub>REG</sub> +0.3 | V    |

| VO4 Voltage                             | V <sub>VO4</sub>                                        | -0.3 to +7                    | V    |

| PGND1S, CSN Voltage                     | V <sub>PGND1S</sub> , V <sub>CSN</sub>                  | -0.3 to +0.3                  | V    |

| SYNC Voltage                            | V <sub>SYNC</sub>                                       | -0.3 to +6                    | V    |

| WDEN Voltage                            | Vwden                                                   | -0.3 to +6                    | V    |

| WDIN Voltage                            | V <sub>WDIN</sub>                                       | -0.3 to +6                    | V    |

| SSCGEN Voltage                          | V <sub>SSCGEN</sub>                                     | -0.3 to V <sub>REG</sub> +0.3 | V    |

| XRSTOUT, PGOOD1, PGOOD2, XTWOUT Voltage | Vxrstout<br>Vpgood1<br>Vpgood2<br>Vxtwout               | -0.3 to +7                    | V    |

| Maximum Junction Temperature            | Tjmax                                                   | 150                           | °C   |

| Storage Temperature Range               | Tstg                                                    | -55 to +150                   | °C   |

Caution 1: Operating the IC over the absolute maximum ratings may damage the IC. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the IC is operated over the absolute maximum ratings.

Caution 2: Should by any chance the maximum junction temperature rating be exceeded the rise in temperature of the chip may result in deterioration of the properties of the chip. In case of exceeding this absolute maximum rating, design a PCB boards with thermal resistance taken into consideration by increasing board size and copper area so as not to exceed the maximum junction temperature rating.

### Thermal Resistance (Note 1)

| Parameter                                           | Symbol          | Thermal Res | Unit          |      |

|-----------------------------------------------------|-----------------|-------------|---------------|------|

| Falameter                                           | Symbol          | 1s (Note 3) | 2s2p (Note 4) | Unit |

| VQFN40FV6060                                        |                 |             |               |      |

| Junction to Ambient                                 | θ <sub>JA</sub> | 83.7        | 27.0          | °C/W |

| Junction to Top Characterization Parameter (Note 2) | $\Psi_{JT}$     | 8.0         | 4.0           | °C/W |

(Note 1) Based on JESD51-2A (Still-Air).

(Note 2) The thermal characterization parameter to report the difference between junction temperature and the temperature at the top center of the outside surface of the component package.

(Note 3) Using a PCB board based on JESD51-3. (Note 4) Using a PCB board based on JESD51-5, 7.

| Layer Number of<br>Measurement Board | Material  | Board Size               |                              |                  |                                      |                               |   |         |

|--------------------------------------|-----------|--------------------------|------------------------------|------------------|--------------------------------------|-------------------------------|---|---------|

| Single                               | FR-4      | 114.3 mm x 76.2 mm x     | x 1.57 mmt                   |                  |                                      |                               |   |         |

| Тор                                  |           |                          |                              |                  |                                      |                               |   |         |

| Copper Pattern                       | Thickness |                          |                              |                  |                                      |                               |   |         |

| Footprints and Traces                | 70 µm     |                          |                              |                  |                                      |                               |   |         |

| Layer Number of<br>Measurement Board | Material  | Board Size               |                              | Thermal<br>Pitch |                                      | <sup>ote 5)</sup><br>Diameter |   |         |

| 4 Layers                             | FR-4      | 114.3 mm x 76.2 mm       | 114.3 mm x 76.2 mm x 1.6 mmt |                  | 114.3 mm x 76.2 mm x 1.6 mmt 1.20 mr |                               | Φ | 0.30 mm |

| Тор                                  |           | 2 Internal Laye          | 2 Internal Layers            |                  | om                                   |                               |   |         |

| Copper Pattern                       | Thickness | Copper Pattern Thickness |                              | Copper Patter    | n                                    | Thickness                     |   |         |

| Footprints and Traces                | 70 µm     | 74.2 mm x 74.2 mm        | 35 µm                        | 74.2 mm x 74.2   | mm                                   | 70 µm                         |   |         |

(Note 5) This thermal via connects with the copper pattern of all layers.

#### **Recommended Operating Conditions**

| Parameter                       | Symbol                              | Min | Тур | Max          | Unit |

|---------------------------------|-------------------------------------|-----|-----|--------------|------|

| Supply Voltage 1 (Note 6)       | Vcc                                 | 4   | 12  | 28           | V    |

| Supply Voltage 2                | V <sub>S2,</sub> V <sub>S3</sub>    | 3.0 | 3.3 | 5.5          | V    |

| VO2/VO3 Output Current          | I <sub>VO2</sub> , I <sub>VO3</sub> | -   | -   | 2.5 (Note 7) | А    |

| SW4 Current                     | I <sub>SW4</sub>                    | -   | -   | 1.0 (Note 7) | А    |

| SYNC Input Frequency            | <b>f</b> sync                       | 1.9 | 2.2 | 2.5          | MHz  |

| SYNC Input Duty Cycle           | D <sub>SYNC</sub>                   | 40  | 50  | 60           | %    |

| WDIN Input Frequency            | <b>f<sub>WDIN</sub></b>             | 10  | -   | 50           | Hz   |

| WDIN Minimum ON Pulse/OFF Pulse | t <sub>WDP</sub>                    | -   | -   | 100          | μs   |

| VO3 Output Voltage Range        | V <sub>VO3</sub>                    | 0.8 | -   | 2.5          | V    |

| Operating Ambient Temperature   | Topr                                | -40 | +25 | +125         | °C   |

(Note 6) Initial startup is over 4.5 V.

(Note 7) ASO should not be exceeded

### **Electrical Characteristics**

### (Unless otherwise specified V<sub>CC</sub> = 12 V, V<sub>S2</sub> = V<sub>S3</sub> = 3.3 V, Tj = -40 °C to +150 °C)

| Parameter                        | Symbol                                     | Min  | Тур | Max  | Unit | Conditions                                                                                                                                                        |  |

|----------------------------------|--------------------------------------------|------|-----|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| All                              |                                            |      |     |      |      |                                                                                                                                                                   |  |

| Standby Current 1                | I <sub>st1</sub>                           | -    | 0   | 10   | μA   | V <sub>EN1</sub> = 0 V, Tj = 25 °C                                                                                                                                |  |

| Standby Current 2                | I <sub>st2</sub>                           | -    | -   | 50   | μA   | V <sub>EN1</sub> = 0 V, Tj = 125 °C                                                                                                                               |  |

| Circuit Current                  | Ivcc                                       | -    | 5   | -    | mA   | $\begin{array}{l} V_{\text{EN1}} = 12 \text{ V}, \\ V_{\text{EN2}} = V_{\text{EN3}} = V_{\text{EN4}} = 3.3 \text{ V} \\ \text{Non-switching current} \end{array}$ |  |

| VREG Output Voltage              | $V_{REG}$                                  | 4.6  | 5.0 | 5.4  | V    | I <sub>VREG</sub> = -10 mA                                                                                                                                        |  |

| VCC UVLO Threshold Voltage 1     | V <sub>UVVCC1</sub>                        | 3.6  | 3.8 | 4.0  | V    | VCC voltage sweep down                                                                                                                                            |  |

| VCC UVLO Threshold Voltage 2     | V <sub>UVVCC2</sub>                        | 4.0  | 4.2 | 4.4  | V    | VCC voltage sweep up                                                                                                                                              |  |

| VCC UVLO Hysteresis              | V <sub>HYSVCC</sub>                        | -    | 0.4 | -    | V    |                                                                                                                                                                   |  |

| VREG UVLO Threshold Voltage 1    | V <sub>UVREG1</sub>                        | 3.2  | 3.5 | 3.8  | V    | VREG voltage sweep down                                                                                                                                           |  |

| VREG UVLO Threshold Voltage 2    | V <sub>UVREG2</sub>                        | 3.3  | 3.6 | 3.9  | V    | VREG voltage sweep up                                                                                                                                             |  |

| VREG UVLO Hysteresis             | V <sub>HYSREG</sub>                        | -    | 0.1 | -    | V    |                                                                                                                                                                   |  |

| VREG Switch Over Voltage 1       | V <sub>SWREG1</sub>                        | 4.15 | 4.5 | 4.85 | V    | VO4 voltage sweep up                                                                                                                                              |  |

| VREG Switch Over Voltage 2       | V <sub>SWREG2</sub>                        | 4.05 | 4.4 | 4.75 | V    | VO4 voltage sweep down                                                                                                                                            |  |

| VREG Switch Hysteresis           | V <sub>HYSSW</sub>                         | -    | 0.1 | -    | V    |                                                                                                                                                                   |  |

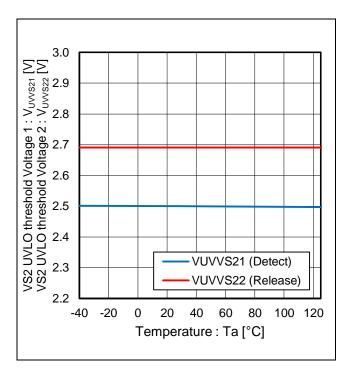

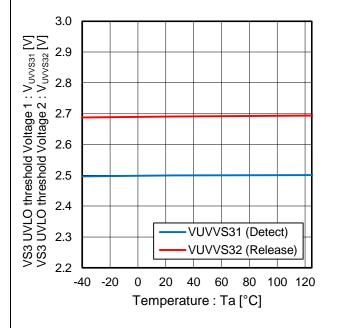

| VS2/VS3 UVLO Threshold Voltage 1 | V <sub>UVVS21</sub><br>V <sub>UVVS31</sub> | 2.2  | 2.5 | 2.8  | V    | VS2/VS3 voltage sweep down                                                                                                                                        |  |

| VS2/VS3 UVLO Threshold Voltage 2 | V <sub>UVVS22</sub><br>V <sub>UVVS32</sub> | 2.4  | 2.7 | 3.0  | V    | VS2/VS3 voltage sweep up                                                                                                                                          |  |

| VS2/VS3 UVLO Hysteresis          | V <sub>HYSVS2</sub><br>V <sub>HYSVS3</sub> | -    | 0.2 | -    | V    |                                                                                                                                                                   |  |

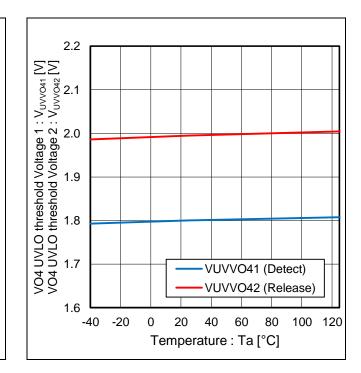

| VO4 UVLO Threshold Voltage 1     | V <sub>UVVO41</sub>                        | 1.6  | 1.8 | 2.0  | V    | VO4 voltage sweep down                                                                                                                                            |  |

| VO4 UVLO Threshold Voltage 2     | V <sub>UVVO42</sub>                        | 1.8  | 2.0 | 2.2  | V    | VO4 voltage sweep up                                                                                                                                              |  |

| VO4 UVLO Hysteresis              | V <sub>HYSVO4</sub>                        | -    | 0.2 | -    | V    |                                                                                                                                                                   |  |

| Switching Frequency              | f <sub>OSC</sub>                           | 1.9  | 2.2 | 2.5  | MHz  | $  R_{RT} = 9.1 \ k\Omega \\ V_{SSCGEN} = 0 \ V $                                                                                                                 |  |

### Electrical Characteristics – continued

(Unless otherwise specified V<sub>CC</sub> = 12 V, V<sub>S2</sub> = V<sub>S3</sub> = 3.3 V, Tj = -40 °C to +150 °C)

| Parameter                              | Symbol               | Min   | Тур   | Max   | Unit | Conditions                             |

|----------------------------------------|----------------------|-------|-------|-------|------|----------------------------------------|

| BUCK1 (Primary Buck Controller)        |                      |       |       |       |      |                                        |

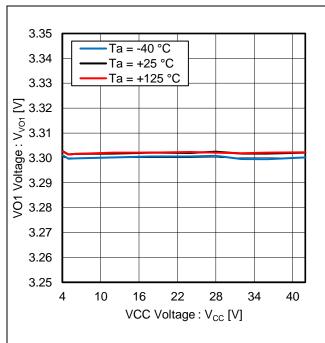

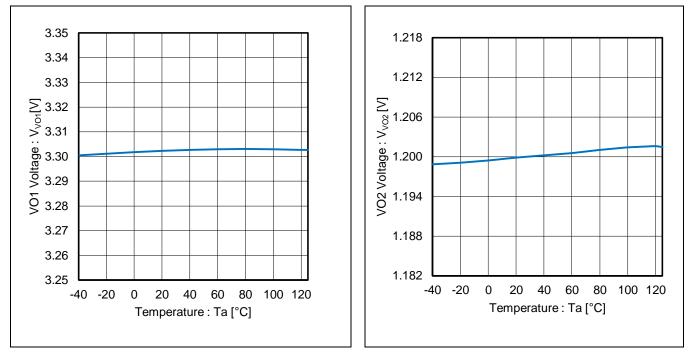

| VO1 Voltage                            | V <sub>VO1</sub>     | 3.250 | 3.300 | 3.350 | V    |                                        |

| Soft Start Time1                       | t <sub>SS1</sub>     | 0.75  | -     | 3.0   | ms   |                                        |

| VGH1 High Side ON Resistance           | R <sub>ONVGH1H</sub> | -     | 10    | 20    | Ω    | I <sub>VGH1</sub> = -10 mA             |

| VGH1 Low Side ON Resistance            | R <sub>ONVGH1L</sub> | -     | 1.5   | 4     | Ω    | I <sub>VGH1</sub> = +10 mA             |

| VGL1 High Side ON Resistance           | R <sub>ONVGL1H</sub> | -     | 10    | 25    | Ω    | $I_{VGL1} = -10 \text{ mA}$            |

| VGL1 Low Side ON Resistance            | R <sub>ONVGL1L</sub> | -     | 1.5   | 4     | Ω    | $I_{VGL1} = +10 \text{ mA}$            |

| Over Current Protection CSN<br>Voltage | V <sub>CSN</sub>     | 60    | 75    | 90    | mV   | V <sub>CSN</sub> - V <sub>PGND1S</sub> |

| OVP Detect Voltage 1                   | V <sub>OVP11</sub>   | 4.00  | 4.25  | 4.50  | V    | VO1 voltage sweep up                   |

| OVP Release Voltage 1                  | V <sub>OVP12</sub>   | -     | 4.00  | -     | V    | VO1 voltage sweep down                 |

| SCP Detect Voltage 1                   | V <sub>SCP11</sub>   | 1.485 | 1.650 | 1.815 | V    | VO1 voltage sweep down                 |

| SCP Release Voltage 1                  | V <sub>SCP12</sub>   | -     | 1.815 | -     | V    | VO1 voltage sweep up                   |

| OVD Detect Voltage 1                   | V <sub>OVD1</sub>    | 3.365 | 3.415 | 3.465 | V    | VO1 voltage sweep up                   |

| UVD Detect Voltage 1                   | $V_{\text{UVD1}}$    | 3.135 | 3.185 | 3.235 | V    | VO1 voltage sweep down                 |

| OVD/UVD Filter Time 1                  | t <sub>FIL1</sub>    | 50    | 75    | 100   | μs   |                                        |

| VO1 Discharge Resistor                 | R <sub>DIS1</sub>    | -     | -     | 500   | Ω    | Resistance between VO1 and PGND1       |

| BUCK2 (Secondary Buck)                 |                      |       |       |       |      | 1                                      |

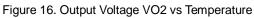

| VO2 Voltage                            | V <sub>VO2</sub>     | 1.182 | 1.200 | 1.218 | V    |                                        |

| Soft Start Time 2                      | t <sub>SS2</sub>     | 0.6   | -     | 2.4   | ms   |                                        |

| SW2 High Side On Resistance            | R <sub>ON2H</sub>    | -     | 75    | 150   | mΩ   | I <sub>SW2</sub> = -50 mA              |

| SW2 Low Side On Resistance             | R <sub>ON2L</sub>    | -     | 75    | 150   | mΩ   | I <sub>SW2</sub> = +50 mA              |

| OVP Detect Voltage 2                   | V <sub>OVP21</sub>   | 1.36  | 1.44  | 1.52  | V    | VO2 voltage sweep up                   |

| OVP Release Voltage 2                  | V <sub>OVP22</sub>   | -     | 1.32  | -     | V    | VO2 voltage sweep down                 |

| SCP Detect Voltage 2                   | V <sub>SCP21</sub>   | 0.54  | 0.60  | 0.66  | V    | VO2 voltage sweep down                 |

| SCP Release Voltage 2                  | V <sub>SCP22</sub>   | -     | 0.72  | -     | V    | VO2 voltage sweep up                   |

| OVD Detect Voltage 2                   | V <sub>OVD2</sub>    | 1.224 | 1.242 | 1.260 | V    | VO2 voltage sweep up                   |

| UVD Detect Voltage 2                   | V <sub>UVD2</sub>    | 1.140 | 1.158 | 1.176 | V    | VO2 voltage sweep down                 |

| OVD/UVD Filter Time 2                  | t <sub>FIL2</sub>    | 50    | 75    | 100   | μs   |                                        |

| VO2 Discharge Resistor                 | $R_{DIS2}$           | -     | -     | 100   | Ω    | Resistance between SW2<br>and PGND2    |

| BUCK3 (Secondary Buck)                 |                      |       |       |       |      | 1                                      |

| FB3 Voltage                            | $V_{FB3}$            | 0.788 | 0.800 | 0.812 | V    |                                        |

| Soft Start Time 3                      | t <sub>SS3</sub>     | 0.6   | -     | 2.4   | ms   |                                        |

| SW3 High Side On Resistance            | R <sub>ON3H</sub>    | -     | 75    | 150   | mΩ   | I <sub>SW3</sub> = -50 mA              |

| SW3 Low Side On Resistance             | R <sub>ON3L</sub>    | -     | 75    | 150   | mΩ   | I <sub>SW3</sub> = +50 mA              |

| OVP Detect Voltage 3                   | V <sub>OVP31</sub>   | 0.90  | 0.96  | 1.02  | V    | VO3S voltage sweep up                  |

| OVP Release Voltage 3                  | V <sub>OVP32</sub>   | -     | 0.88  | -     | V    | VO3S voltage sweep down                |

| SCP Detect Voltage 3                   | V <sub>SCP31</sub>   | 0.36  | 0.40  | 0.44  | V    | VO3S voltage sweep down                |

| SCP Release Voltage 3                  | V <sub>SCP32</sub>   | -     | 0.48  | -     | V    | VO3S voltage sweep up                  |

| OVD Detect Voltage 3                   | V <sub>OVD3</sub>    | 0.816 | 0.828 | 0.840 | V    | FB3 voltage sweep up                   |

| UVD Detect Voltage 3                   | V <sub>UVD3</sub>    | 0.760 | 0.772 | 0.784 | V    | FB3 voltage sweep down                 |

| OVD/UVD Filter Time 3                  | t <sub>FIL3</sub>    | 50    | 75    | 100   | μs   |                                        |

| VO3 Discharge Resistor                 | R <sub>DIS3</sub>    | -     | -     | 100   | Ω    | Resistance between SW3 and PGND3       |

### **Electrical Characteristics - continued**

### (Unless otherwise specified V<sub>CC</sub> = 12 V, V<sub>S2</sub> = V<sub>S3</sub> = 3.3 V, Tj = -40 °C to +150 °C)

| Parameter                                         | Symbol                                                          | Min                       | Тур   | Max                       | Unit | Conditions                                                        |

|---------------------------------------------------|-----------------------------------------------------------------|---------------------------|-------|---------------------------|------|-------------------------------------------------------------------|

| BOOST4 (Secondary Boost)                          |                                                                 |                           |       |                           |      |                                                                   |

| VO4 Voltage                                       | V <sub>VO4</sub>                                                | 4.90                      | 5.00  | 5.10                      | V    |                                                                   |

| Soft Start Time of BOOST 4                        | t <sub>SS4</sub>                                                | 1                         | -     | 4                         | ms   |                                                                   |

| SW4 On Resistance                                 | R <sub>ON4</sub>                                                | -                         | 200   | -                         | mΩ   | I <sub>SW4</sub> = 50 mA                                          |

| OVP Detect Voltage 4                              | V <sub>OVP41</sub>                                              | 6.0                       | 6.5   | 7.0                       | V    | VO4 voltage sweep up                                              |

| OVP Release Voltage 4                             | V <sub>OVP42</sub>                                              | -                         | 6.25  | -                         | V    | VO4 voltage sweep down                                            |

| SCP Detect Voltage 4                              | V <sub>SCP41</sub>                                              | 2.25                      | 2.50  | 2.75                      | V    | VO4 voltage sweep down                                            |

| SCP Release Voltage 4                             | V <sub>SCP42</sub>                                              | -                         | 3.00  | -                         | V    | VO4 voltage sweep up                                              |

| OVD Detect Voltage 4                              | V <sub>OVD4</sub>                                               | 5.150                     | 5.325 | 5.500                     | V    | VO4 voltage sweep up                                              |

| UVD Detect Voltage 4                              | $V_{\text{UVD4}}$                                               | 4.500                     | 4.675 | 4.850                     | V    | VO4 voltage sweep down                                            |

| OVD/UVD Filter Time 4                             | t <sub>FIL4</sub>                                               | 50                        | 75    | 100                       | μs   |                                                                   |

| Enable                                            |                                                                 |                           |       |                           |      |                                                                   |

| EN1 Low Voltage                                   | V <sub>ENL1</sub>                                               | -                         | -     | 0.8                       | V    |                                                                   |

| EN1 High Voltage                                  | V <sub>ENH1</sub>                                               | 2.6                       | -     | -                         | V    |                                                                   |

| EN1 Pull down Resistor                            | R <sub>EN1</sub>                                                | 125                       | 250   | 375                       | kΩ   | V <sub>EN1</sub> = 5 V                                            |

| EN2, EN3, EN4 Low Voltage                         | V <sub>ENL2</sub> ,<br>V <sub>ENL3</sub> ,<br>V <sub>ENL4</sub> | -                         | -     | V <sub>VO1</sub><br>x 0.2 | V    |                                                                   |

| EN2, EN3, EN4 High Voltage                        | V <sub>enh2</sub> ,<br>V <sub>enh3</sub> ,<br>V <sub>enh4</sub> | V <sub>VO1</sub><br>x 0.8 | -     | -                         | V    |                                                                   |

| EN2, EN3, EN4 Pull Down Resistor                  | R <sub>EN2/3/4</sub>                                            | 50                        | 100   | 150                       | kΩ   |                                                                   |

| Synchronous                                       |                                                                 |                           |       |                           |      |                                                                   |

| SYNC Low Voltage                                  | V <sub>SYNCL</sub>                                              | -                         | -     | V <sub>VO1</sub><br>x 0.2 | V    |                                                                   |

| SYNC High Voltage                                 | V <sub>SYNCH</sub>                                              | V <sub>VO1</sub><br>x 0.8 | -     | -                         | V    |                                                                   |

| SYNC Pull down Resistor                           | R <sub>SYNC</sub>                                               | 50                        | 100   | 150                       | kΩ   |                                                                   |

| SSCGEN                                            | 1                                                               |                           |       |                           | r    | 1                                                                 |

| SSCGEN Low Voltage                                | VSSCGENL                                                        | -                         | -     | V <sub>REG</sub><br>x 0.2 | V    |                                                                   |

| SSCGEN High Voltage                               | V <sub>SSCGENH</sub>                                            | V <sub>REG</sub><br>x 0.8 | -     | -                         | V    |                                                                   |

| SSCGEN Pull up Resistor                           | RSSCGEN                                                         | 50                        | 100   | 150                       | kΩ   | Between VREG and SSCGEN                                           |

| RESET                                             |                                                                 |                           |       | [                         | -    |                                                                   |

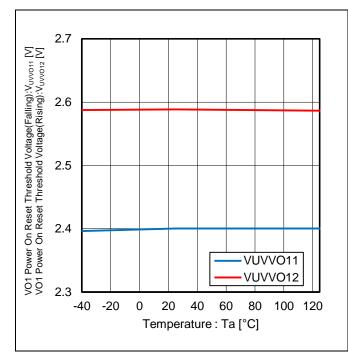

| VO1 Power On Reset Threshold<br>Voltage (Falling) | V <sub>UVVO11</sub>                                             | 2.3                       | 2.4   | 2.5                       | V    | VO1 voltage sweep down                                            |

| VO1 Power On Reset Threshold<br>Voltage (Rising)  | V <sub>UVVO12</sub>                                             | 2.5                       | 2.6   | 2.7                       | V    | VO1 voltage sweep up                                              |

| VO1 Power On Reset Hysteresis                     | V <sub>VO1HYS</sub>                                             | -                         | 0.2   | -                         | V    |                                                                   |

| XRSTOUT On Resistance                             | R <sub>ONRST</sub>                                              | -                         | -     | 200                       | Ω    | I <sub>RSTOUT</sub> = 1 mA                                        |

| XRSTOUT Leak Current                              | I <sub>LRST</sub>                                               | -                         | -     | 10                        | μA   | V <sub>RSTOUT</sub> = 5 V                                         |

| XRSTOUT Low Hold Time                             | t <sub>RSTL</sub>                                               | 7                         | 10    | 13                        | ms   |                                                                   |

| Power Good                                        |                                                                 |                           |       |                           |      |                                                                   |

| PGOOD On Resistance                               | R <sub>ONPG</sub>                                               | -                         | -     | 200                       | Ω    | PGOOD1, PGOOD2<br>IPGOOD1, IPGOOD2 = 1 mA                         |

| PGOOD Leak Current                                | I <sub>LPG</sub>                                                | -                         | -     | 10                        | μA   | PGOOD1, PGOOD2<br>V <sub>PGOOD1</sub> , V <sub>PGOOD2</sub> = 5 V |

| Power On Delay Time                               | t <sub>PG</sub>                                                 | 7                         | 10    | 13                        | ms   | PGOOD1, PGOOD2                                                    |

| Thermal Warning                                   |                                                                 |                           |       |                           |      |                                                                   |

| XTWOUT On Resistance                              | Rontw                                                           | -                         | -     | 200                       | Ω    | I <sub>XTWOUT</sub> = 1 mA                                        |

| XTWOUT Leak Current                               | ILTW                                                            | -                         | -     | 10                        | μA   | V <sub>XTWOUT</sub> = 5 V                                         |

### Electrical Characteristics - continued

### (Unless otherwise specified $V_{CC}$ = 12 V, $V_{S2}$ = $V_{S3}$ = 3.3 V, Tj = -40 °C to +150 °C)

| Parameter                     | Symbol             | Min                       | Тур   | Max                       | Unit | Conditions               |

|-------------------------------|--------------------|---------------------------|-------|---------------------------|------|--------------------------|

| Watch Dog Timer               |                    |                           |       |                           |      |                          |

| WDEN Low Level Input Voltage  | Vwdenl             | -                         | -     | V <sub>V01</sub><br>x 0.2 | V    |                          |

| WDEN High Level Input Voltage | Vwdenh             | V <sub>V01</sub><br>x 0.8 | -     | -                         | V    |                          |

| WDEN Pull Down Resistor       | RWDEN              | 50                        | 100   | 150                       | kΩ   |                          |

| WDIN Low Level Input Voltage  | V <sub>WDINL</sub> | -                         | -     | V <sub>VO1</sub><br>x 0.2 | V    |                          |

| WDIN High Level Input Voltage | V <sub>WDINH</sub> | V <sub>V01</sub><br>x 0.8 | -     | -                         | V    |                          |

| WDIN Pull Up Resistor         | Rwdin              | 50                        | 100   | 150                       | kΩ   |                          |

| WDT OK Time 1                 | t <sub>WOK1</sub>  | 12.5                      | 25.5  | 38.5                      | ms   | R <sub>RTW</sub> = 10 kΩ |

| WDT FAST Timeout Detect 1     | t <sub>WF1</sub>   | 9.6                       | 11.1  | 12.5                      | ms   | R <sub>RTW</sub> = 10 kΩ |

| WDT SLOW Timeout Detect 1     | t <sub>WS1</sub>   | 38.5                      | 44.3  | 50.1                      | ms   | R <sub>RTW</sub> = 10 kΩ |

| WDT OK Time 2                 | t <sub>WOK2</sub>  | 33.8                      | 68.9  | 104.1                     | ms   | R <sub>RTW</sub> = 27 kΩ |

| WDT FAST Timeout Detect 2     | t <sub>WF2</sub>   | 26.0                      | 29.9  | 33.8                      | ms   | R <sub>RTW</sub> = 27 kΩ |

| WDT SLOW Timeout Detect 2     | t <sub>WS2</sub>   | 104.1                     | 119.6 | 135.2                     | ms   | R <sub>RTW</sub> = 27 kΩ |

| WDT OK Time 3                 | t <sub>woкз</sub>  | 58.8                      | 120.0 | 181.1                     | ms   | R <sub>RTW</sub> = 47 kΩ |

| WDT FAST Timeout Detect 3     | t <sub>WF3</sub>   | 45.3                      | 52.1  | 58.8                      | ms   | $R_{RTW} = 47 \ k\Omega$ |

| WDT SLOW Timeout Detect 3     | t <sub>WS3</sub>   | 181.1                     | 208.2 | 235.3                     | ms   | $R_{RTW} = 47 \ k\Omega$ |

21/50

### **Typical Performance Curves**

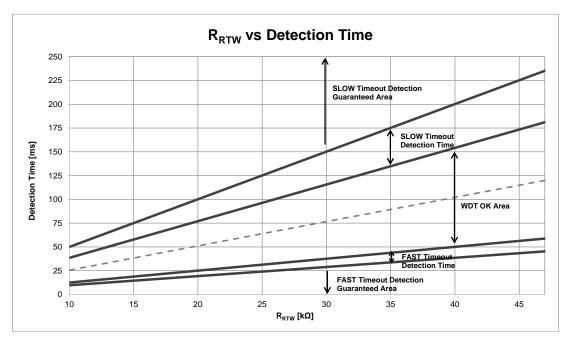

Figure 11. Stand-by Current vs VCC Voltage

Figure 12. Circuit Current vs VCC Voltage

Figure 13. VREG Output Voltage vs the EN1 Pin Voltage ("EN1 Threshold Voltage")

Figure 14. Output Voltage VO1 vs VCC Voltage

Figure 15. Output Voltage VO1 vs Temperature  $(V_{CC} = 12 \text{ V})$

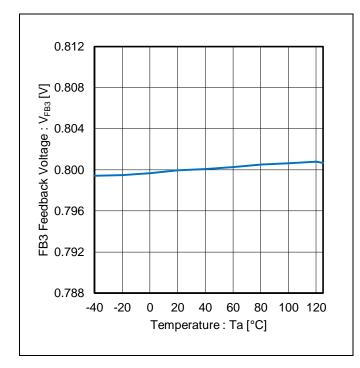

Figure 17. Feedback Voltage FB3 vs Temperature Ta

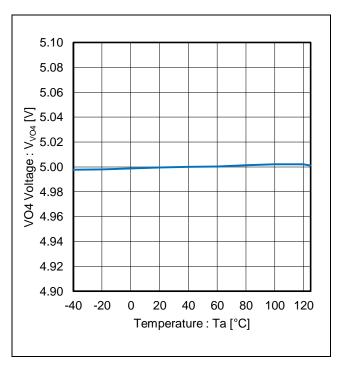

Figure 18. Output Voltage VO4 vs Temperature Ta

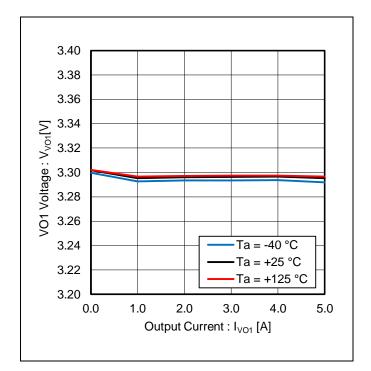

Figure 19. Output Voltage VO1 vs Output Current ("VO1 Load Regulation",  $V_{CC}$  = 12 V)

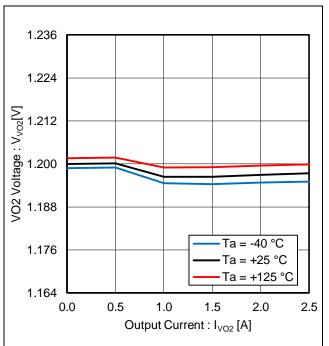

Figure 20. Output Voltage VO2 vs Output Current ("VO2 Load Regulation",  $V_{S2}$  = 3.3 V)

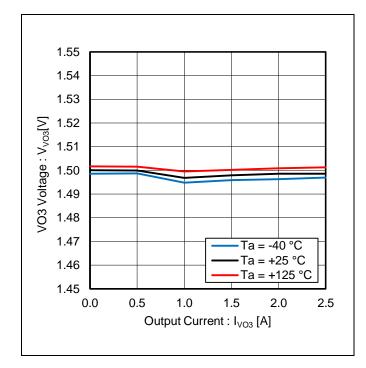

Figure 21. Output Voltage VO3 vs Output Current ("VO3 Load Regulation",  $V_{S3}$  = 3.3 V, VO3 = 1.5 V setting)

Figure 22. Output Voltage VO4 vs Output Current ("VO4 Load Regulation",  $V_{S4}$  = 3.3 V)

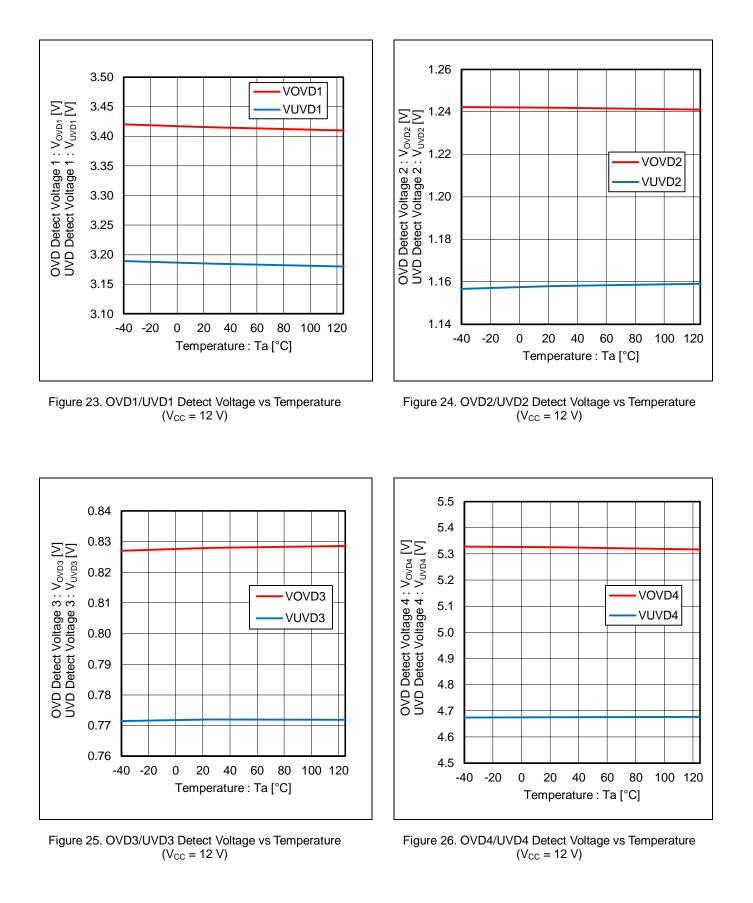

Figure 27. VCC UVLO Threshold Voltage vs Temperature ("VCC UVLO Threshold")

Figure 28. VS2 UVLO Threshold Voltage vs Temperature ("VS2 UVLO Threshold",  $V_{CC}$  = 12 V)

Figure 30. VO4 UVLO Threshold Voltage vs Temperature ("VO4 UVLO Threshold",  $V_{CC}$  = 12 V)

Figure 29. VS3 UVLO Threshold Voltage vs Temperature ("VS3 UVLO Threshold",  $V_{CC}$  = 12 V)

Figure 31. VO1 Power On Reset Threshold Voltage vs Temperature ("VO1RST Threshold", V<sub>CC</sub> = 12 V)

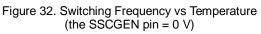

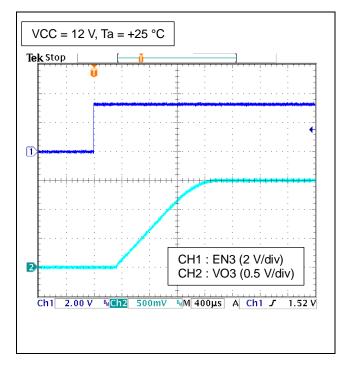

Figure 33. VO1 Power On Waveform ( $V_{CC}$  = 12 V, Ta = +25 °C)

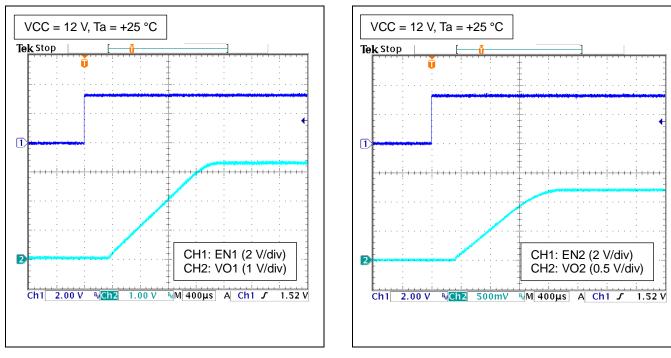

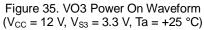

Figure 36. VO4 Power On Waveform (V<sub>CC</sub> = 12 V, Ta = +25 °C)

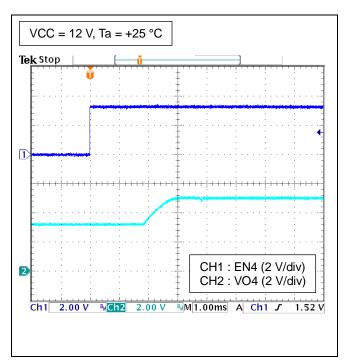

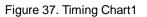

### **Timing Chart**

An example of EN1 tied to VCC, and EN2, EN3, and EN4 controlled by microcomputer.

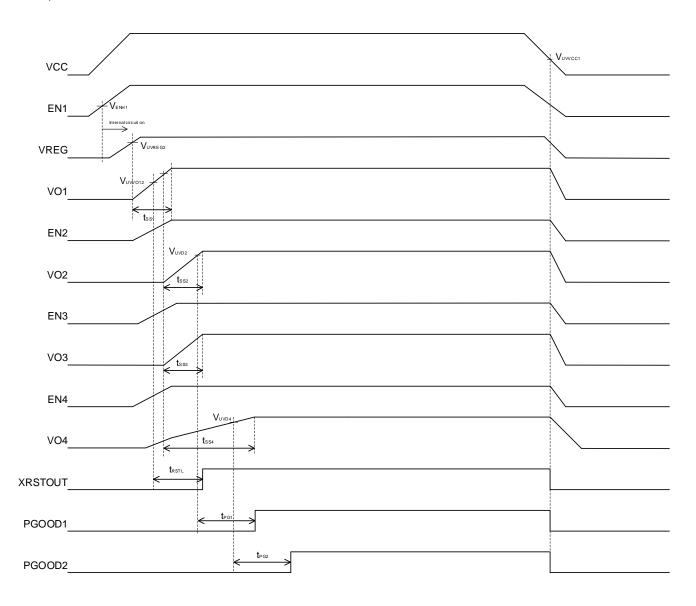

An example of EN1 tied to VCC, and EN2, EN3 and EN4 tied to VO1.

Figure 38. Timing Chart2

An example of enable signals sequentially controlled.

Figure 39. Timing Chart3

An example of WDEN controlled by external signal.

#### Figure 40. Timing Chart of WDEN controlled by External Signal

An example of WDEN tied to VO1

| VO1                 | V <sub>UW012</sub> |              |                                                          | Vuwo11        |

|---------------------|--------------------|--------------|----------------------------------------------------------|---------------|

| BIST<br>(internal)  |                    |              |                                                          |               |

| XRSTOUT             |                    |              | is error,<br>DUT is kept Low level, and WDT is not work. |               |

| WDIN                |                    |              |                                                          |               |

| WDEN                |                    | 500 ms (Typ) | WDT works after 500 ms after XRSTOUT is High             | VWDENL        |

| WDT —<br>function — | WDT Disenable      |              | WDT Enable                                               | WDT Disenable |

Figure 41. Timing Chart of WDEN tied to VO1

Figure 42. Timing Chart of OVD/UVD Detect

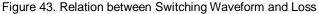

### **Application Example**

### Selection of Components Externally Connected

| Item              |                 |       | Value           |      |                                |                          |                                                        |

|-------------------|-----------------|-------|-----------------|------|--------------------------------|--------------------------|--------------------------------------------------------|

|                   | Min<br>(Note 1) | Тур   | Max<br>(Note 2) | unit | Parts No.                      | Maker                    | Note                                                   |

| IC                | -               | -     | -               | -    | BD39031MUF-C                   | ROHM                     |                                                        |

| R <sub>EN1</sub>  | 9.7             | 10    | 100             | kΩ   | MCR01 series                   | ROHM                     | EN1 pull up resistor                                   |

| R <sub>C1</sub>   | 32              | 33    | 34              | kΩ   | MCR01 series                   | ROHM                     | VO1 compensation resistor                              |

| Rcs               | 8.7             | 9     | 15              | mΩ   | PMR18EZPJU9L0                  | ROHM                     | VO1 current sense resistor                             |

| R <sub>FB3U</sub> | 1               | 13    | 47              | kΩ   | MCR01 series                   | ROHM                     | VO3 feedback resistor<br>(Upper side)                  |

| R <sub>FB3L</sub> | 1               | 15    | 47              | kΩ   | MCR01 series                   | ROHM                     | VO3 feedback resistor<br>(Lower side)                  |

| R <sub>VO3U</sub> | 1               | 13    | 47              | kΩ   | MCR01 series                   | ROHM                     | VO3 sense resistor (Upper side)                        |

| R <sub>VO3L</sub> | 1               | 15    | 47              | kΩ   | MCR01 series                   | ROHM                     | VO3 sense resistor (Lower side)                        |

| R <sub>RT</sub>   | 8.8             | 9.1   | 9.4             | kΩ   | MCR01 series                   | ROHM                     | Switching frequency setting resistor                   |

| R <sub>RTW</sub>  | 9.7             | 27    | 48.5            | kΩ   | MCR01 series                   | ROHM                     | WDT detection time setting resistor                    |

| R <sub>RST</sub>  | 0.97            | 10    | 48.5            | kΩ   | MCR01 series                   | ROHM                     | XRSTOUT pull up resistor                               |

| R <sub>PG1</sub>  | 0.97            | 10    | 48.5            | kΩ   | MCR01 series                   | ROHM                     | PGOOD1 pull up resistor                                |

| R <sub>PG2</sub>  | 0.97            | 10    | 48.5            | kΩ   | MCR01 series                   | ROHM                     | PGOOD2 pull up resistor                                |

| R <sub>two</sub>  | 0.97            | 10    | 48.5            | kΩ   | MCR01 series                   | ROHM                     | XTWOUT pull up resistor                                |

| Cvcc              | 0.7             | 1     | 1.5             | μF   | GCM21BR71H105MA03              | Murata                   | VCC input capacitor, Range: 50<br>V                    |

| C <sub>VCC2</sub> | 7               | 10    | 22              | μF   | GCM32EC71H106KA03              | Murata                   | VCC input capacitor, Range: 50                         |

| C <sub>REG</sub>  | 1.54            | 2.2   | 2.86            | μF   | GCM21BR71A225MA37              | Murata                   | VREG5 output capacitor, Range:<br>10 V                 |

| C <sub>B1</sub>   | 0.07            | 0.1   | 0.13            | μF   | GCM188R71C104MA37              | Murata                   | VO1 boot strap capacitor,<br>Range : 16 V              |

| C <sub>C1</sub>   | 840             | 1200  | 1560            | pF   | GCM155R71H122KA37              | Murata                   | VO1 phase compensation capacitor                       |

| C <sub>VO1</sub>  | 47 x3           | 47 x4 | 47 x8           | μF   | GCM32ER70J476ME19              | Murata                   | VO1 output capacitor, Range:<br>6.3 V                  |

| C <sub>VS2</sub>  | 1.5             | 2.2   | 4.3             | μF   | GCM188R70J225ME22              | Murata                   | VO2 input capacitor, Range: 6.3<br>V                   |

| C <sub>VO2</sub>  | 32.9            | 47    | 122             | μF   | GCM32ER70J476ME19              | Murata                   | VO2 output capacitor, Range:<br>6.3 V                  |

| C <sub>VS3</sub>  | 1.5             | 2.2   | 4.3             | μF   | GCM188R70J225ME22              | Murata                   | VO3 input capacitor, Range: 6.3<br>V                   |

| C <sub>FB3</sub>  | 154             | 220   | 286             | pF   | GCM155R71H221KA37              | Murata                   | VO3 feedback capacitor                                 |