SLAS363D-MARCH 2002-REVISED APRIL 2005

# Low-Power, Highly-Integrated, Programmable 16-Bit, 26-KSPS, Dual-Channel CODEC

# FEATURES

- Stereo 16-Bit Oversampling Sigma-Delta A/D Converter

- Stereo 16-Bit Oversampling Sigma-Delta D/A Converter

- Support Maximum Master Clock of 100 MHz to Allow DSPs Output Clock to be Used as a Master Clock

- Selectable FIR/IIR Filter With Bypassing Option

- **Programmable Sampling Rate up to:** - Max 26 Ksps With On-Chip IIR/FIR Filter - Max 104 Ksps With IIR/FIR Bypassed

- **On-Chip FIR Produced 84-dB SNR for ADC** . and 92-dB SNR for DAC over 13-Khz BW

- Smart Time Division Multiplexed (SMARTDM<sup>®</sup>) Serial Port

- Glueless 4-Wire Interface to DSP

- Automatic Cascade Detection (ACD) Self-Generates Master/Slave Device Addresses

- Programming Mode to Allow On-The-Fly Reconfiguration

- Continuous Data Transfer Mode to Minimize **Bit Clock Speed**

- Support Different Sampling Rate for Each Device

- Turbo Mode to Maximize Bit Clock For Faster Data Transfer and Allow Multiple Serial Devices to Share the Same Bus

- Allows up to Eight Devices to be Connected to a Single Serial Port

- Host port

- 2-Wire Interface

- Selectable I<sup>2</sup>C or S<sup>2</sup>C

- **Differential and Single-Ended Analog** • Input/Output

- **Built-In Analog Functions:**

- Analog and Digital Sidetone

- Antialiasing Filter (AAF)

- Programmable Input and Output Gain Control (PGA)

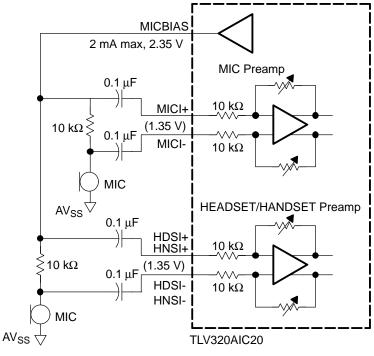

- Microphone/Handset/Headset Amplifiers

- AIC20/21/20K Have a Built-In 8-Ω Speaker Driver

- Power Management With Hardware/Software Power-Down Modes 30 µW

- Separate Software Control for ADC and DAC Power Down

- Fully Compatible With Common TMS320<sup>®</sup> DSP **Family and Microcontroller Power Supplies**

- 1.65-V 1.95-V Digital Core Power

- 1.1-V 3.6-V Digital I/O

- 2.7-V 3.6-V Analog

- Internal Reference Voltage (V<sub>ref</sub>)

- **2s Complement Data Format**

- **Test Mode Which Includes Digital Loopback** and Analog Loopback

# **APPLICATIONS**

- **Wireless Accessories**

- Hands-Free Car Kits

- VOIP

- Cable Modem

- **Speech Processing**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. SMARTDM, TMS320, TMS320C5000, TMS320C6000 are registered trademarks of Texas Instruments.

SLAS363D-MARCH 2002-REVISED APRIL 2005

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

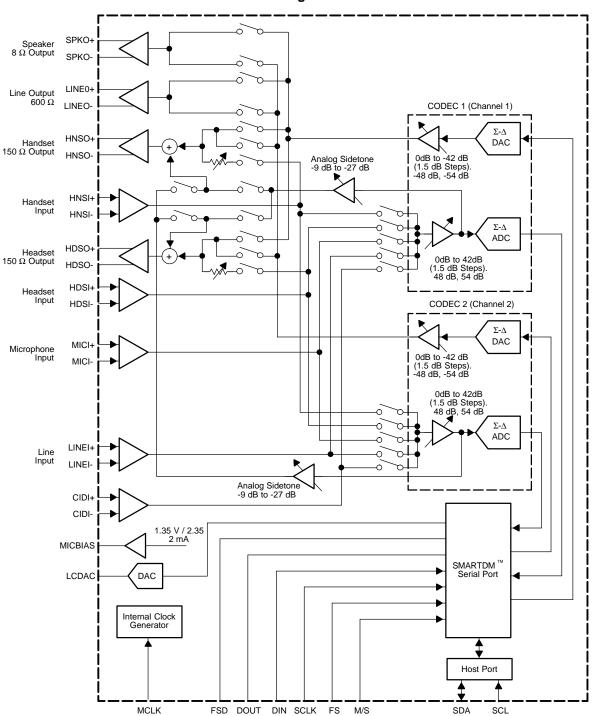

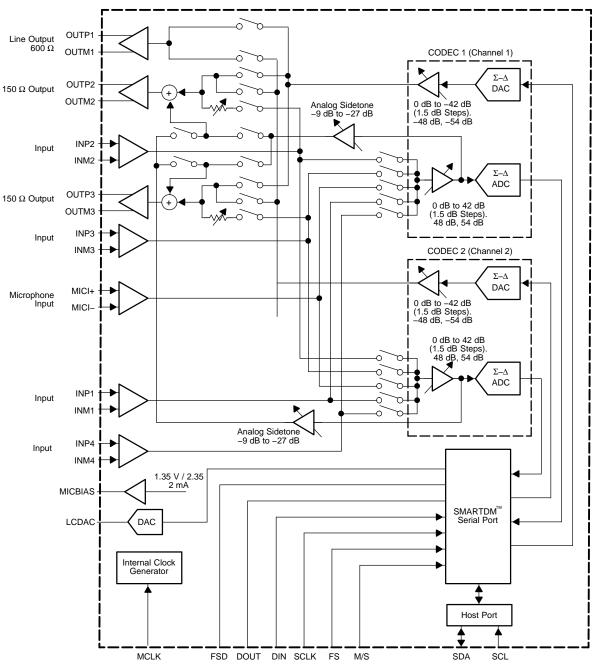

# DESCRIPTION

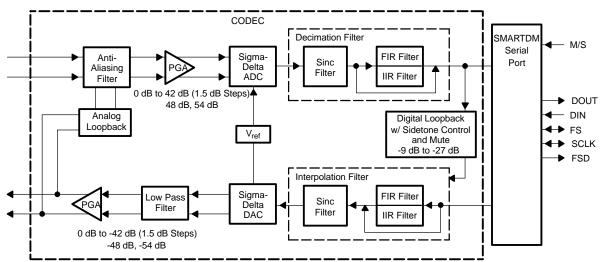

The TLV320AIC2x is a low-cost, low-power, highly-integrated, high-performance, dual-voice codec. It features two 16-bit analog-to-digital (A/D) channels and two 16-bit digital-to-analog (D/A) channels, which can be connected to a handset, headset, speaker, microphone, or a subscriber line via a programmable analog crosspoint.

The TLV320AIC2x provides high resolution signal conversion from digital-to-analog (D/A) and from analog-to-digital (A/D) using oversampling sigma-delta technology with programmable sampling rate.

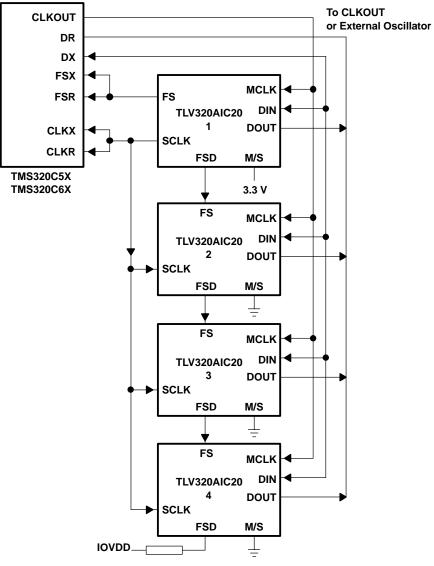

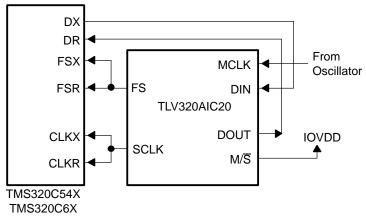

The TLV320AIC2x implements the smart time division multiplexed serial port (SMARTDM<sup>™</sup>). The SMARTDM port is a synchronous 4-wire serial port in TDM format for glue-free interface to TI DSPs (i.e., TMS320C5000<sup>®</sup>, TMS320C6000<sup>®</sup> DSP platforms) and microcontrollers. The SMARTDM<sup>™</sup> supports both continuous data transfer mode and on-the-fly reconfiguration programming mode. The TLV320AIC2x can be gluelessly cascaded to any SMARTDM-based device to form a multichannel codec, and up to eight TLV320AIC2x codecs can be cascaded to a single serial port.

The TLV320AIC2x provides a flexible host port. The host port interface is a two-wire serial interface that can be programmed to be either an industrial standard  $I^2C$  or a simple  $S^2C$  (start-stop communication protocol).

The TLV320AIC2x integrates all of the critical functions needed for most voice-band applications including MIC preamplifier, handset amplifier headset amplifier, 8-Ω speaker driver, sidetone control, antialiasing filter (AAF), input/output programmable gain amplifier (PGA), and selectable low-pass IIR/FIR filters.

The TLV320AIC2x implements an extensive power management; including device power-down, independent software control for turning off ADC, DAC, operational-amplifiers, and IIR/FIR filter (bypassable) to maximize system power conservation. The TLV320AIC2x consumes only 14.9 mW per channel at 3 V.

The TLV320AIC2x low power operation from 2.7-V to 3.6-V power supplies along with extensive power management make it ideal for portable applications including wireless accessories, hands-free car kits, VOIP, cable modem, and speech processing. Its low group delay characteristic makes it suitable for single or multichannel active control applications.

The TLV320AIC2x is characterized for commercial operation from 0°C to 70°C, and industrial operation from -40°C to 85°C. The TLV320AIC2xk is characterized for industrial operation from -40°C to 85°C.

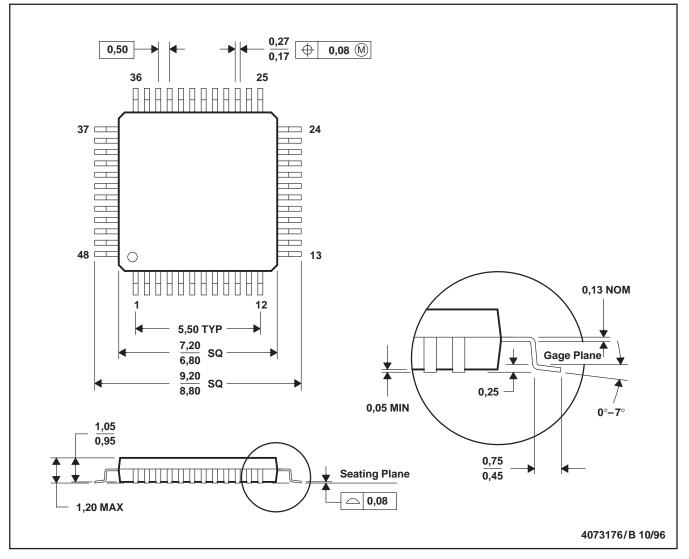

| T <sub>A</sub> | 48-TQFP PFB PACKAGE <sup>(1)</sup> |

|----------------|------------------------------------|

| 0°C to 70°C    | TLV320AIC2xC                       |

| -40°C to 85°C  | TLV320AIC2xI                       |

#### **ORDERING INFORMATION**

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

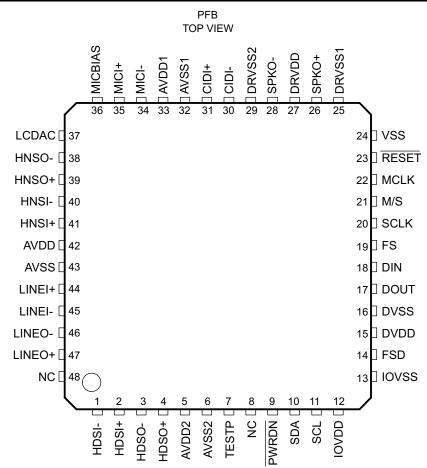

#### **Terminal Functions**

| TERMI          | NAL    |     |                                                                                  |

|----------------|--------|-----|----------------------------------------------------------------------------------|

| NAME           | NO.    | I/O | DESCRIPTION                                                                      |

| HDSI-<br>HDSI+ | 1<br>2 | I   | Head-set input. The Head-set input can be treated similar to the Line-input pins |

| HDSO-<br>HDSO+ | 3<br>4 | 0   | 150- $Ω$ output                                                                  |

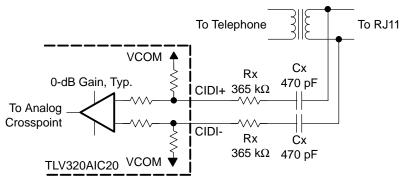

| AVDD2          | 5      | I   | Analog power supply                                                              |

| AVSS2          | 6      | I   | Analog ground                                                                    |

| TESTP          | 7      | I   | Test pin. Should be connected to digital ground.                                 |

| NC             | 8, 48  |     | Not connected                                                                    |

| PWRDN          | 9      | Ι   | Power down                                                                       |

| SDA            | 10     | I/O | I <sup>2</sup> C/S <sup>2</sup> C data                                           |

| SCL            | 11     | I   | I <sup>2</sup> C/S <sup>2</sup> C clock                                          |

| IOVDD          | 12     | I   | I/O power supply                                                                 |

| IOVSS          | 13     | I   | I/O ground                                                                       |

| FSD            | 14     | 0   | Frame sync delayed                                                               |

| DVDD           | 15     | I   | Digital supply (1.8 V)                                                           |

| DVSS           | 16     | I   | Digital ground                                                                   |

| DOUT           | 17     | 0   | Data OUT                                                                         |

| DIN            | 18     | I   | Data IN                                                                          |

| FS             | 19     | I/O | Frame sync                                                                       |

| SCLK           | 20     | I/O | Serial clock                                                                     |

SLAS363D-MARCH 2002-REVISED APRIL 2005

## **Terminal Functions (continued)**

| TERMIN           | IAL      |     |                                                                                    |

|------------------|----------|-----|------------------------------------------------------------------------------------|

| NAME             | NO.      | I/O | DESCRIPTION                                                                        |

| M/S              | 21       | I   | Master slave select applied to CODEC1 only. CODEC2 is always a slave.              |

| MCLK             | 22       | I   | Master clock                                                                       |

| RESET            | 23       | I   | Reset                                                                              |

| VSS              | 24       | I   | Device ground. Typically this should be connected to the Analog Ground.            |

| DRVSS1           | 25       | I   | Driver ground                                                                      |

| SPKO+<br>SPKO-   | 26<br>28 | 0   | 8-Ω output                                                                         |

| DRVDD            | 27       | I   | Driver supply                                                                      |

| DRVSS2           | 29       | I   | Driver ground                                                                      |

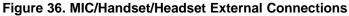

| CIDI-<br>CIDI+   | 30<br>31 | I   | Caller-ID input. The Caller-ID input can be treated similar to the Line-input pins |

| AVDD1            | 33       | I   | Analog supply                                                                      |

| AVSS1            | 32       | I   | Analog ground                                                                      |

| MICI-            | 34       | I   | Microphone input                                                                   |

| MICI+            | 35       | I   | Microphone input                                                                   |

| MICBIAS          | 36       | Ι   | Microphone bias                                                                    |

| LCDAC            | 37       | 0   | 6-Bit DAC output may be used to drive LCDAC                                        |

| HNSO-<br>HNSO+   | 38<br>39 | 0   | 150-Ω output                                                                       |

| HNSI-<br>HNSI+   | 40<br>41 | I   | Hand-set input. The Hand-set input can be treated similar to the Line-input pins   |

| AVDD             | 42       | I   | Analog supply                                                                      |

| AVSS             | 43       | I   | Analog ground                                                                      |

| LINEI+<br>LINEI- | 44<br>45 | I   | Line input                                                                         |

| LINEO-<br>LINEO+ | 46<br>47 | 0   | 600-Ω output                                                                       |

## **Electrical Characteristics**

All specifications are common across the AIC20, AIC21, AIC24, AIC25, AIC20K, and AIC24K except where explicitly stated.

AIC20/21/24/25: Over Recommended Operating Free-Air Temperature Range, AVDD = 3.3 V, DVDD = 1.8 V, IOVDD = 3.3 V (Unless Otherwise Noted)

AIC20K/24K: Over Recommended Operating Free-Air Temperature Range, AVDD = 3.3 V, DVDD = 1.8 V, IOVDD = 3.3 V (Unless Otherwise Noted)

## Absolute Maximum Ratings<sup>(1)</sup>

over Operating Free-Air Temperature Range (Unless Otherwise Noted)

|                  |                                                  |                                   | TLV320AIC2x             |

|------------------|--------------------------------------------------|-----------------------------------|-------------------------|

| $V_{CC}$         | Supply voltage range:                            | DVDD <sup>(2)</sup>               | -0.3 V to 2.25 V        |

|                  |                                                  | AVDD, IOVDD, DRVDD <sup>(2)</sup> | -0.3 V to 4 V           |

| Vo               | Output voltage range, all digital output signals |                                   | -0.3 V to IOVDD + 0.3 V |

| VI               | Input voltage range, all digital inp             | ut signals                        | -0.3 V to IOVDD + 0.3 V |

| T <sub>A</sub>   | Operating free-air temperature ra                | nge                               | -40°C to 85°C           |

| T <sub>stg</sub> | Storage temperature range                        |                                   | -65°C to 150°C          |

|                  | Case temperature for 10 seconds                  | s: package                        | 260°C                   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to  $V_{SS}$ .

## **Recommended Operating Conditions**

|                 |                            |                                                | MIN  | NOM | MAX  | UNIT |

|-----------------|----------------------------|------------------------------------------------|------|-----|------|------|

|                 |                            | Analog, AVDD                                   | 2.7  | 3.3 | 3.6  | V    |

| v               | Cupply voltage             | Analog output driver, DRVDD <sup>(1)</sup>     | 2.7  | 3.3 | 3.6  | V    |

| V <sub>CC</sub> | Supply voltage             | Digital core, DVDD                             | 1.65 | 1.8 | 1.95 | V    |

|                 |                            | Digital I/O, IOVDD                             | 1.1  | 3.3 | 3.6  | V    |

|                 | Analog single-ended peak   | -to-peak input voltage, V <sub>I(analog)</sub> |      |     | 2    | V    |

|                 |                            | Between LINEO+ and LINEO- (differential)       |      | 600 |      |      |

| Б               | Output load registeres     | Between HDSO+ and HDSO- (differential)         |      | 150 |      | 0    |

| RL              | Output load resistance,    | Between HNSO+ and HDSO- (differential)         |      | 150 |      | Ω    |

|                 |                            | Between SPKO+ and SPKO- (differential)         |      | 8   |      |      |

| CL              | Analog output load capac   | itance                                         |      |     | 20   | pF   |

|                 | Digital output capacitance |                                                |      |     | 20   | pF   |

|                 | Master clock               |                                                |      |     | 100  | MHz  |

|                 | ADC or DAC conversion r    | ate                                            |      |     | 26   | kHz  |

| T <sub>A</sub>  | Operating free-air tempera | ature,                                         | -40  |     | 85   | °C   |

(1) DRVDD should be kept at the same voltage as AVDD.

SLAS363D-MARCH 2002-REVISED APRIL 2005

#### **Digital Inputs and Outputs**

FS = 8 KHz, outputs not loaded

|                 | PARAMETER                                   | MIN       | TYP | MAX       | UNIT |

|-----------------|---------------------------------------------|-----------|-----|-----------|------|

| V <sub>OH</sub> | High-level output voltage, DOUT             | 0.8 IOVDD |     |           | V    |

| V <sub>OL</sub> | Low-level output voltage, DOUT              |           |     | 0.1 IOVDD | V    |

| I <sub>IH</sub> | High-level input current, any digital input |           | 5   |           | μA   |

| IIL             | Low-level input current, any digital input  |           | 5   |           | μA   |

| Ci              | Input capacitance                           |           | 3   |           | pF   |

| Co              | Output capacitance                          |           | 5   |           | pF   |

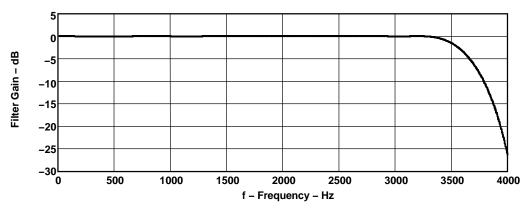

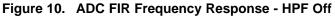

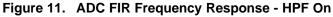

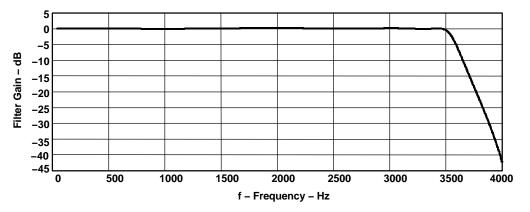

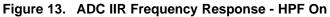

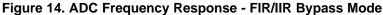

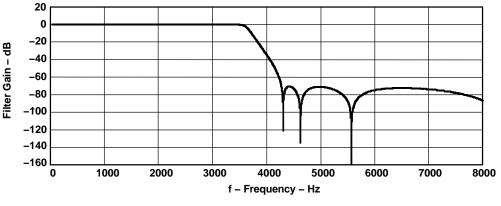

## ADC PATH FILTER

FS = 8 KHz (1)(2)

| PARAMETER                                  | TEST<br>CONDITIONS | MIN   | ТҮР       | МАХ          | MIN  | ТҮР        | МАХ          | UNIT |

|--------------------------------------------|--------------------|-------|-----------|--------------|------|------------|--------------|------|

| PATH FILTER                                |                    |       | FIR FILTE | R            |      | IIR FILTER |              |      |

|                                            | 0 Hz to 60 Hz      |       |           | -27 / 0.07   |      | -2         | 7 / 0.15     |      |

|                                            | 60 Hz to 200 Hz    |       |           | -1 / 0.07    |      | -0.7       | -0.75 / 0.15 |      |

|                                            | 200 Hz to 300 Hz   |       |           | -0.03 / 0.05 |      | 0. 1       | 1 / 0.15     |      |

|                                            | 300 Hz to 2.4 KHz  | -0.1  |           | 0.15         | -0.1 |            | 0.25         |      |

| Filter gain relative to gain<br>at 1020 Hz | 2.4 kHz to 3 kHz   | -0.05 |           | 0.15         | -0.5 |            | 0.2          | dB   |

|                                            | 3 kHz to 3.4 KHz   | -0.5  |           | 0.1          | -0.5 |            | 0.2          |      |

|                                            | 3.4 kHz to 3.6 KHz |       |           | -0.4         |      |            | 0.15         |      |

|                                            | 4 KHz              |       |           | -26          |      |            | -42          |      |

|                                            | 4.5 KHz to 72 kHz  |       |           | -52          |      |            | -52          |      |

(1) The filter gain outside of the passband is measured with respect to the gain at 1020 Hz. The analog input test signal is a sine wave with 0 dB = 4 V<sub>1(PP)</sub> as the reference level for the analog input signal. The pass band is 0 to 3600 Hz for an 8-KHz sample rate. This pass band scales linearly with the sample rate.

(2) The filter characteristics are specified by design and are not tested in production. In places where more than one value is specified, the first value is with the High Pass Filter on and the second value is with the HPF off

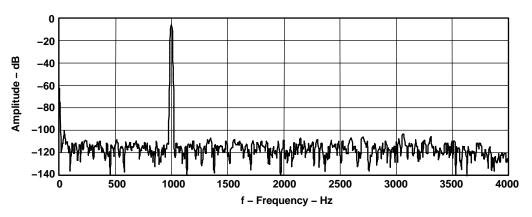

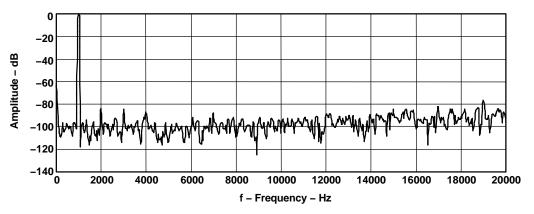

#### ADC DYNAMIC PERFORMANCE

With FIR Filter, FS = 8 KHz (1)

|           | PARAMETER                 | TEST<br>CONDITIONS     | MIN | ТҮР          | МАХ | MIN | ТҮР        | МАХ | UNIT |

|-----------|---------------------------|------------------------|-----|--------------|-----|-----|------------|-----|------|

| Line In D | Driver                    |                        | Α   | IC20/21/24/2 | 25  |     | AIC20k/24k |     |      |

| SNR       | Signal to poice ratio     | V <sub>I</sub> = -3 dB | 81  | 84           |     | 70  | 84         |     |      |

| SINK      | Signal-to-noise ratio     | V <sub>I</sub> = -9 dB | 73  | 76           |     |     | 76         |     |      |

| THD       | Total harmonic distortion | $V_I = -3 \text{ dB}$  | 83  | 90           |     | 70  | 90         |     | ٩D   |

| INU       | Total harmonic distortion | $V_I = -9 \text{ dB}$  | 81  | 88           |     |     | 88         |     | dB   |

|           | Signal-to-harmonic        | $V_I = -3 \text{ dB}$  | 80  | 83           |     |     | 83         |     |      |

| THD+N     | distortion + noise        | $V_I = -9 \text{ dB}$  | 73  | 76           |     |     | 76         |     |      |

(1) The test condition is a differential 1020-Hz input signal with an 8-KHz conversion rate. Input and output common mode is 1.35 V.

SLAS363D-MARCH 2002-REVISED APRIL 2005

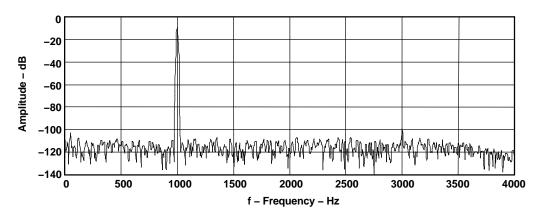

# ADC DYNAMIC PERFORMANCE

With IIR Filter, FS = 8 KHz

|       | PARAMETER                 | TEST<br>CONDITIONS    | MIN | ТҮР          | МАХ | MIN | ТҮР        | МАХ | UNIT |

|-------|---------------------------|-----------------------|-----|--------------|-----|-----|------------|-----|------|

|       |                           |                       | AI  | C20/21/24/25 | 5   |     | AIC20k/24k |     |      |

| SNR   | Signal to poigo ratio     | $V_I = -3 \text{ dB}$ |     | 82           |     |     | 82         |     |      |

| SINK  | Signal-to-noise ratio     | $V_I = -9 \text{ dB}$ |     | 76           |     |     | 76         |     |      |

| THD   | Total harmonia distortion | $V_I = -3 \text{ dB}$ |     | 83           |     |     | 83         |     | ٩D   |

| עחו   | Total harmonic distortion | $V_I = -9 \text{ dB}$ |     | 77           |     |     | 77         |     | dB   |

|       | Signal-to-harmonic        | $V_I = -3 \text{ dB}$ |     | 78           |     |     | 78         |     |      |

| THD+N | distortion + noise        | $V_I = -9 \text{ dB}$ |     | 70           |     |     | 70         |     |      |

## **ADC CHANNEL CHARACTERISTICS**

|                     | DADAMETED                                    | TEAT CONDITIONS                     | AIC20/21/24/25/20k/2 | 4k  |       |

|---------------------|----------------------------------------------|-------------------------------------|----------------------|-----|-------|

|                     | PARAMETER                                    | TEST CONDITIONS                     | MIN TYP              | MAX | UNIT  |

| V <sub>I(pp)</sub>  | Differential-ended input level               | PGA gain = 0 dB                     |                      | 4   | V     |

| V <sub>IO</sub>     | Input offset voltage                         |                                     | ±5                   |     | mV    |

| I <sub>B</sub>      | Input bias current                           |                                     | 125                  |     | μA    |

|                     | Common mode voltage                          |                                     | 1.35                 |     | V     |

|                     | Dynamic range                                | V <sub>I</sub> = -3 dB              | 87                   |     | dB    |

|                     | Mute attenuation                             | PGA = MUTE                          | Zero Digital<br>Code |     | dB    |

|                     | Intrachannel isolation                       |                                     | 87                   |     | dB    |

| E <sub>G</sub>      | Gain error                                   | V <sub>I</sub> = -3 dB at 1020 Hz   | -0.45                |     | dB    |

| E <sub>O(ADC)</sub> | ADC converter offset error                   |                                     | ±15                  |     | mV    |

| CMRR                | Common-mode rejection ratio at INMx and INPx | V <sub>I</sub> = -100 mV at 1020 Hz | 50                   |     | dB    |

|                     | Idle channel noise                           | $V_{(INP,INM,MICIN)} = 0 V$         | 70                   |     | μVrms |

| R <sub>i</sub>      | Input resistance                             | T <sub>A</sub> = 25°C               | 10                   |     | kΩ    |

| Ci                  | Input capacitance                            | T <sub>A</sub> = 25°C               | 2                    |     | pF    |

|                     |                                              | IIR                                 | 5/f <sub>s</sub>     |     | S     |

|                     | Channel delay                                | FIR                                 | 17/f <sub>s</sub>    |     | S     |

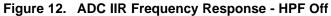

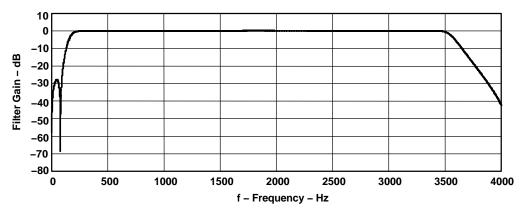

**DAC PATH FILTER**

FS = 8 KHz (1)(2)

| DADAMETED                    | TEST CONDITIONS    | FIF   | FIR FILTER |       |       | IIR FILTER |      |      |  |

|------------------------------|--------------------|-------|------------|-------|-------|------------|------|------|--|

| PARAMETER                    | TEST CONDITIONS    | MIN   | TYP        | MAX   | MIN   | TYP        | MAX  | UNIT |  |

| PATH FILTER, FS = 8 KHz      |                    | ÷     |            |       |       |            |      |      |  |

|                              | 0 Hz to 200 Hz     |       |            | 0.1   |       |            | 0.05 |      |  |

|                              | 200 Hz to 300 Hz   |       |            | -0.05 |       |            | 0.05 | dB   |  |

|                              | 300 Hz to 2.4 KHz  | -0.25 |            | 0.15  | -0.1  |            | 0.1  |      |  |

| Filter gain relative to gain | 2.4 kHz to 3 kHz   | -0.3  |            | 0.1   | -0.2  |            | 0.1  |      |  |

| at 1020 Hz                   | 3 kHz to 3.4 KHz   | -0.55 |            | 0.05  | -0.25 |            | 0.05 |      |  |

|                              | 3.4 kHz to 3.6 KHz |       |            | -30   |       |            | 0    |      |  |

|                              | 4 KHz              |       |            | -28   |       |            | -34  |      |  |

|                              | 4.5 KHz to 72 KHZ  |       |            | -70   |       |            | -70  |      |  |

(1) The filter gain outside of the passband is measured with respect to the gain at 1020 Hz. The input signal is the digital equivalent of a sine wave (digital full scale = 0 dB). The nominal differential DAC channel output with this input condition is 4 V<sub>I(PP)</sub>. The pass band is 0 to 3600 Hz for an 8-kHz sample rate. This pass band scales linearly with the conversion rate. The filter characteristics are specified by design and are not tested in production.

(2)

SLAS363D-MARCH 2002-REVISED APRIL 2005

## TEXAS INSTRUMENTS www.ti.com

## DAC DYNAMIC PERFORMANCE

|                | DADAMETED                                                                                        | TEAT CONDITIONS                                                                                                                                                                                            | AIC2                             | 20/21/24/2                                              | 5                      | AIC                         | C20k/24k                                             |                         |                      |

|----------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------------------------|------------------------|-----------------------------|------------------------------------------------------|-------------------------|----------------------|

|                | PARAMETER                                                                                        | TEST CONDITIONS                                                                                                                                                                                            | MIN                              | TYP                                                     | MAX                    | MIN                         | TYP                                                  | MAX                     | UNIT                 |

| DAC Line       | e Output (LINEO-, LINEO+)<br>Using FIR Filter                                                    | The test condition is the digita<br>The test is measured at output<br>16-bit mode.                                                                                                                         |                                  |                                                         |                        |                             |                                                      |                         |                      |

| SNR            | Signal to poice ratio                                                                            | $V_I = 0 dB$                                                                                                                                                                                               | 88                               | 92                                                      |                        | 80                          | 92                                                   |                         |                      |

| SINK           | Signal-to-noise ratio                                                                            | V <sub>I</sub> = -9 dB                                                                                                                                                                                     | 81                               | 83                                                      |                        |                             | 83                                                   |                         |                      |

| TUD            | Tatal I la ma ania Diata dian                                                                    | $V_I = 0 dB$                                                                                                                                                                                               | 84                               | 90                                                      |                        | 70                          | 90                                                   |                         | -10                  |

| THD            | Total Harmonic Distortion                                                                        | V <sub>I</sub> = -9 dB                                                                                                                                                                                     | 77                               | 84                                                      |                        |                             | 84                                                   |                         | dB                   |

| THD+N          | Signal-to-total Harmonic                                                                         | $V_I = 0 dB$                                                                                                                                                                                               | 82                               | 88                                                      |                        |                             | 88                                                   |                         |                      |

|                | Distortion + noise                                                                               | V <sub>I</sub> = -9 dB                                                                                                                                                                                     | 76                               | 80                                                      |                        |                             | 80                                                   |                         |                      |

| DAC Line       | e Output (LINEO-, LINEO+)<br>Using IIR Filter                                                    | The test condition is the digita<br>The test is measured at output<br>16-bit mode.                                                                                                                         | al equivalent<br>it of the appli | of a 1020<br>ication scl                                | -Hz input<br>nematic l | signal with a ow-pass filte | an 8-kHz<br>r. The tes                               | conversic<br>t is condu | on rate.<br>ucted ir |

| SNR            | Cignal to poice ratio                                                                            | $V_I = 0 dB$                                                                                                                                                                                               |                                  | 83                                                      |                        |                             | 83                                                   |                         |                      |

| SINK           | Signal-to-noise ratio                                                                            | V <sub>I</sub> = -9 dB                                                                                                                                                                                     |                                  | 74                                                      |                        |                             | 74                                                   |                         |                      |

| THD            | Total Harmonic Distortion                                                                        | $V_I = 0 dB$                                                                                                                                                                                               |                                  | 85                                                      |                        |                             | 85                                                   |                         | dB                   |

| שחו            |                                                                                                  | V <sub>I</sub> = -9 dB                                                                                                                                                                                     |                                  | 80                                                      |                        |                             | 80                                                   |                         |                      |

| THD+N          | Signal-to-total Harmonic                                                                         | $V_I = 0 dB$                                                                                                                                                                                               |                                  | 80                                                      |                        |                             | 80                                                   |                         |                      |

| I HD+N         | Distortion + noise                                                                               | V <sub>I</sub> = -9 dB                                                                                                                                                                                     |                                  | 73                                                      |                        |                             | 73                                                   |                         |                      |

| DAC He<br>HDSC | adphone Output (HDSO-,<br>)+), (HNSO-, HNSO+) <sup>(1)</sup>                                     | The test condition is the digita<br>The test is measured at output<br>16-bit mode.                                                                                                                         |                                  |                                                         |                        |                             |                                                      |                         |                      |

| SNR            | Signal-to-noise ratio                                                                            | $V_I = 0 dB$                                                                                                                                                                                               |                                  | 92                                                      |                        |                             | 92                                                   |                         |                      |

| SINK           | Signal-to-hoise ratio                                                                            | V <sub>I</sub> = -9 dB                                                                                                                                                                                     |                                  | 83                                                      |                        |                             | 83                                                   |                         |                      |

| THD            | Total Harmonic Distortion                                                                        | $V_I = 0 dB$                                                                                                                                                                                               |                                  | 90                                                      |                        |                             | 90                                                   |                         |                      |

|                | Total Harmonic Distortion                                                                        | $V_1 = -9 \text{ dB}$                                                                                                                                                                                      |                                  | ~ ~                                                     |                        |                             |                                                      |                         | dB                   |

|                |                                                                                                  | V  = -5 GD                                                                                                                                                                                                 |                                  | 89                                                      |                        |                             | 89                                                   |                         | dB                   |

|                | Signal-to-total Harmonic                                                                         | $V_{I} = 0 \text{ dB}$                                                                                                                                                                                     |                                  | 89<br>88                                                |                        |                             | 89<br>88                                             |                         | dB                   |

| THD+N          | Signal-to-total Harmonic<br>Distortion + noise                                                   |                                                                                                                                                                                                            |                                  |                                                         |                        |                             |                                                      |                         | dB                   |

|                |                                                                                                  | $V_I = 0 dB$                                                                                                                                                                                               |                                  | 88<br>82<br>of a 1020                                   |                        |                             | 88<br>82<br>an 8-kHz                                 |                         | on rate.             |

| DAC S          | Distortion + noise<br>peaker Output (SPKO-,<br>SPKO+) <sup>(1)(2)</sup>                          | $V_{I} = 0 \text{ dB}$ $V_{I} = -9 \text{ dB}$ The test condition is the digitation the test is measured at output                                                                                         |                                  | 88<br>82<br>of a 1020                                   |                        |                             | 88<br>82<br>an 8-kHz                                 |                         | on rate.             |

|                | Distortion + noise                                                                               | $V_{I} = 0 \text{ dB}$ $V_{I} = -9 \text{ dB}$ The test condition is the digita<br>The test is measured at output<br>16-bit mode.                                                                          |                                  | 88<br>82<br>of a 1020-<br>ication scl                   |                        |                             | 88<br>82<br>an 8-kHz<br>r. The tes                   |                         | on rate.             |

| DAC S          | Distortion + noise<br>peaker Output (SPKO-,<br>SPKO+) <sup>(1)(2)</sup><br>Signal-to-noise ratio | $V_{I} = 0 \text{ dB}$ $V_{I} = -9 \text{ dB}$ The test condition is the digita<br>The test is measured at output<br>16-bit mode.<br>$V_{I} = 0 \text{ dB}$                                                |                                  | 88<br>82<br>of a 1020<br>ication sch<br>91              |                        |                             | 88<br>82<br>an 8-kHz<br>r. The tes<br>91             |                         | on rate.             |

|                | Distortion + noise<br>peaker Output (SPKO-,<br>SPKO+) <sup>(1)(2)</sup>                          | $V_{I} = 0 \text{ dB}$ $V_{I} = -9 \text{ dB}$ The test condition is the digita<br>The test is measured at output<br>16-bit mode.<br>$V_{I} = 0 \text{ dB}$ $V_{I} = -9 \text{ dB}$                        |                                  | 88<br>82<br>of a 1020<br>ication sch<br>91<br>83        |                        |                             | 88<br>82<br>an 8-kHz<br>r. The tes<br>91<br>83       |                         | on rate.             |

| DAC S          | Distortion + noise<br>peaker Output (SPKO-,<br>SPKO+) <sup>(1)(2)</sup><br>Signal-to-noise ratio | $V_{I} = 0 \text{ dB}$ $V_{I} = -9 \text{ dB}$ The test condition is the digita<br>The test is measured at output<br>16-bit mode.<br>$V_{I} = 0 \text{ dB}$ $V_{I} = -9 \text{ dB}$ $V_{I} = 0 \text{ dB}$ |                                  | 88<br>82<br>of a 1020-<br>ication sch<br>91<br>83<br>91 |                        |                             | 88<br>82<br>an 8-kHz<br>r. The tes<br>91<br>83<br>91 |                         | on rate.             |

The conversion rate is 8 kHz.

The speaker driver is valid only for the AIC20/21/20K.

SLAS363D-MARCH 2002-REVISED APRIL 2005

## DAC CHANNEL CHARACTERISTICS

|                                                     | PARAMETER                                         | TEST CONDITIONS                  | MIN  | TYP               | MAX  | UNIT  |  |

|-----------------------------------------------------|---------------------------------------------------|----------------------------------|------|-------------------|------|-------|--|

|                                                     | Dynamic range                                     | V <sub>I</sub> = 0 dB at 1020 Hz | 92   |                   |      | dB    |  |

|                                                     | Interchannel isolation                            |                                  |      | 90                |      | dB    |  |

| E <sub>G</sub><br>V <sub>oo</sub><br>V <sub>o</sub> | Gain error, 0 dB                                  | V <sub>O</sub> = 0 dB at 1020 Hz |      | -0.7              |      | dB    |  |

|                                                     | Mute attenuation                                  | PGA = Mute                       |      | 90                |      | dB    |  |

|                                                     | Common-mode voltage                               |                                  |      | 1.35              |      | V     |  |

|                                                     | Idle channel narrow band noise                    | 0 - 4 kHz <sup>(1)</sup>         |      | 40                |      | V rms |  |

| V <sub>OO</sub>                                     | Output offset voltage at OUTP1_150 (differential) | DIN = All zeros                  |      | ±8                |      | V     |  |

| Vo                                                  | Analog output voltage, (3.3 V)                    | HDSO+                            | 0.35 |                   | 2.35 | V     |  |

|                                                     | Channel delay                                     | IIR                              |      | 5/f <sub>s</sub>  |      | S     |  |

|                                                     | Channel delay                                     | FIR                              |      | 18/f <sub>s</sub> |      | S     |  |

(1) The conversion rate is 8 kHz.

## **OUTPUT AMPLIFIER CHARACTERISTICS**

| DADAMETER                        | TEST CONDITIONS                         | AIC20/21 | łk  |     |      |

|----------------------------------|-----------------------------------------|----------|-----|-----|------|

| PARAMETER                        | TEST CONDITIONS                         | MIN      | TYP | MAX | UNIT |

| SPEAKER INTERFACE <sup>(1)</sup> |                                         |          |     | i   |      |

| Speaker output power             | $V_{CC} = 3.3 \text{ V}, \text{ fully}$ |          | 250 |     | mW   |

| Maximum output current           | differential, 8-Ω load                  |          | mA  |     |      |

| HANDSET AND HEADSET INTERFACE    | · · ·                                   |          |     | L   |      |

| Speaker output power             | $V_{CC} = 3.3 \text{ V}, \text{ fully}$ |          | 13  |     | mW   |

| Maximum output current           | differential, 150-Ω load                |          |     | mA  |      |

| LINE INTERFACE                   |                                         |          |     | i   |      |

| Speaker output power             | $V_{CC} = 3.3 V$ , fully                |          | 3.5 |     |      |

| Maximum output current           | differential, 600-Ω load                | 3.5      |     |     | mA   |

(1) The speaker driver is valid only for the AIC20/21/20k.

## **BIAS AMPLIFIER CHARACTERISTICS**

|         | PARAMETER           | TEST CONDITIONS | AIC20/2 |           |     |      |

|---------|---------------------|-----------------|---------|-----------|-----|------|

|         | PARAMETER           | TEST CONDITIONS | MIN     | TYP       | MAX | UNIT |

| Vo      | Output voltage      |                 |         | 1.35/2.35 |     | V    |

|         | Integrated noise    | 300 Hz – 13 KHz |         | 20        |     | μV   |

| $V_{S}$ | Offset voltage      |                 |         | 10        |     | mV   |

|         | Current drive       |                 |         | 5         |     | mA   |

|         | Unity gain bandwith |                 |         | 1         |     | MHz  |

|         | DC gain             |                 |         | 90        |     | dB   |

|         | PSRR                |                 |         | 70        |     | dB   |

## **POWER-SUPPLY REJECTION**<sup>(1)</sup>

|           | PARAMETER                                                                | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------|--------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| $AV_{DD}$ | Supply-voltage rejection ratio, analog supply (fj = 0 to $f_{\rm g}/2$ ) | Differential    |     | 75  |     |      |

(1) Power supply rejection measurements are made with both the ADC and the DAC channels idle and a 200 mV peak-to-peak signal applied to the appropriate supply.

SLAS363D-MARCH 2002-REVISED APRIL 2005

#### **POWER-CONSUMPTION**

| DADAMETED                         | TEAT CONDITIONS    | AIC20/2  | 1/24/25/20k/24 | (  |    |  |

|-----------------------------------|--------------------|----------|----------------|----|----|--|

| PARAMETER                         | TEST CONDITIONS    | MIN      | MIN TYP MA     |    |    |  |

| ADC (single channel)              |                    |          | 5.7            |    |    |  |

| DAC (single channel)              | Without drivers    |          | 3.5            |    |    |  |

| Speaker driver <sup>(1)</sup>     | No signal          |          | 9.3            |    |    |  |

| Handset driver                    | No signal          |          | 2              |    |    |  |

| Headset driver                    | No signal          | 2        |                | mW |    |  |

| Lineout driver                    | No signal          | 2<br>2.3 |                |    |    |  |

| Reference                         |                    |          |                |    |    |  |

| Digital                           | PLL off            |          | 3.4            |    |    |  |

|                                   | Analog             |          | 4.6            |    |    |  |

| PLL                               | Digital            |          | 1.8            |    |    |  |

| Total Analog with all sections on | No signal, PLL off |          | 35.8           |    |    |  |

| POWER DOWN CURRENT                |                    |          |                |    |    |  |

| Hardware power-down (no clock)    |                    |          | 1              |    |    |  |

| Cottures accurated accura         | Analog, PLL off    | . off 2  |                |    | μA |  |

| Software power-down               | Digital            |          | 650            |    |    |  |

TEXAS INSTRUMENTS www.ti.com

(1) The speaker driver is valid only for the AIC20/21/20k.

## LCD DAC

|         | PARAMETER      | AIC  |       |      |      |

|---------|----------------|------|-------|------|------|

|         | FARAMETER      | MIN  | TYP   | MAX  | UNIT |

| Vo      | Output range   | 0.35 |       | 2.35 | V    |

|         | Sampling rate  |      |       | 104  | kHz  |

|         | INL            |      | ±0.5  |      | LSB  |

|         | DNL            |      | ±0.25 |      | LSB  |

| $V_{S}$ | Offset voltage |      | ±25   |      | mV   |

| $E_G$   | Gain error     |      | ±0.02 |      | dB   |

# Typical ADC performance With PGA Gain Setting Using FIR<sup>(1)</sup>

| PGA GAIN SETTING | SNR | THD | SINAD | UNIT |

|------------------|-----|-----|-------|------|

| 9 dB             | 83  | 90  | 81    |      |

| 18 dB            | 83  | 97  | 83    | dB   |

| 24 dB            | 78  | 95  | 77    |      |

| 36 dB            | 72  | 95  | 72    |      |

(1) Test condition is a 1020-Hz input differential signal with an 8-kHz conversion rate. Input amplitude is given such that output of PGA is at -3 dB level.

SLAS363D-MARCH 2002-REVISED APRIL 2005

SLAS363D-MARCH 2002-REVISED APRIL 2005

U

Texas INSTRUMENTS

www.ti.com

SLAS363D-MARCH 2002-REVISED APRIL 2005

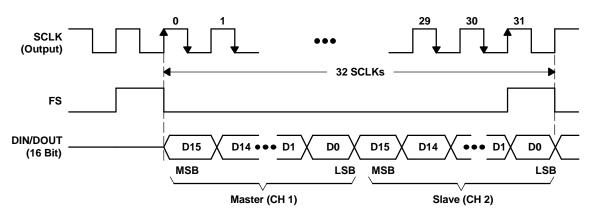

**Definitions and Terminology**

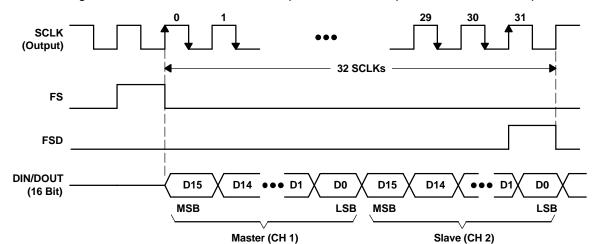

| Data Transfer<br>Interval      | The time during which data is transferred from DOUT and to DIN.<br>The interval is 16 shift clocks, and the data transfer is initiated by<br>the falling edge of the FS signal.                                                          |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Data                    | This refers to the input signal and all of the converted representations<br>through the ADC channel and the signal through the DAC channel to the<br>analog output. This is contrasted with the purely digital software control<br>data. |

| Frame Sync                     | Frame sync refers only to the falling edge of the signal FS that initiates the data transfer interval                                                                                                                                    |

| Frame Sync and Sampling Period | Frame sync and sampling period is the time between falling edges of successive FS signals.                                                                                                                                               |

| f <sub>s</sub>                 | The sampling frequency                                                                                                                                                                                                                   |

| ADC Channel                    | ADC channel refers to all signal processing circuits between the analog input and the digital conversion result at DOUT.                                                                                                                 |

| DAC channel                    | DAC channel refers to all signal processing circuits between the digital data word applied to DIN and the differential output analog signal available at OUTP and OUTM.                                                                  |

| Dxx                            | Bit position in the primary data word (xx is the bit number)                                                                                                                                                                             |

| DSxx                           | Bit position in the secondary data word (xx is the bit number)                                                                                                                                                                           |

| d                              | The alpha character d represents valid programmed or default data in the control register format (see Section 3.2, Secondary Serial Communication) when discussing other data bit portions of the register.                              |

| PGA                            | Programmable gain amplifier                                                                                                                                                                                                              |

| IIR                            | Infinite impulse response                                                                                                                                                                                                                |

| FIR                            | Finite impulse response                                                                                                                                                                                                                  |

SLAS363D-MARCH 2002-REVISED APRIL 2005

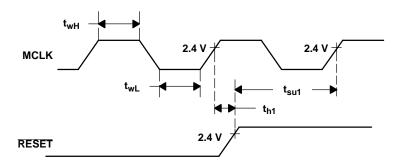

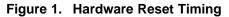

TIMING REQUIREMENTS

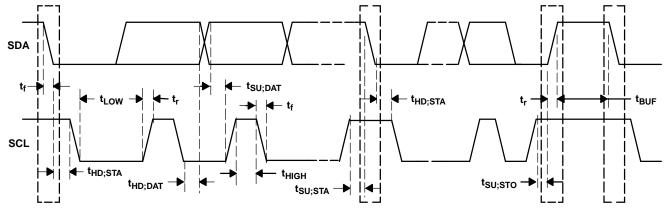

Figure 2. Serial Communication Timing

|                  |                                                    | TEST CONDITIONS        | MIN | TYP | MAX | UNIT |

|------------------|----------------------------------------------------|------------------------|-----|-----|-----|------|

| t <sub>wH</sub>  | Pulse duration, MCLK high                          |                        | 5   |     |     |      |

| t <sub>wL</sub>  | Pulse duration, MCLK low                           |                        | 5   |     |     |      |

| t <sub>su1</sub> | Setup time, RESET, before MCLK high (see Figure 1) |                        | 3   |     |     |      |

| t <sub>h1</sub>  | Hold time, RESET, after MCLK high (see Figure 1)   |                        | 2   |     |     |      |

| t <sub>d1</sub>  | Delay time, SCLK $\uparrow$ to FS/FSD $\downarrow$ | C <sub>L</sub> = 20 pF |     |     | 5   | ns   |

| t <sub>d2</sub>  | Delay time, SCLK↑ to FS/FSD↑                       |                        |     |     | 5   |      |

| t <sub>d3</sub>  | Delay time, SCLK <sup>↑</sup> to DOUT              |                        |     |     | 15  |      |

| t <sub>en</sub>  | Enable time, SCLK <sup>↑</sup> to DOUT             |                        |     |     | 15  |      |

| t <sub>dis</sub> | Disable time, SCLK↑ to DOUT                        |                        |     |     | 15  |      |

| t <sub>su2</sub> | Setup time, DIN, before SCLK $\downarrow$          |                        | 10  |     |     |      |

| t <sub>h2</sub>  | Hold time, DIN, after SCLK $\downarrow$            |                        | 10  |     |     |      |

SLAS363D-MARCH 2002-REVISED APRIL 2005

## Figure 3. I<sup>2</sup>C / S<sup>2</sup>C Timing Diagram

| PARAMETER                                                                                   | SYMBOL              | MIN | MAX | UNIT |

|---------------------------------------------------------------------------------------------|---------------------|-----|-----|------|

| SCL clock frequency                                                                         | t <sub>SCL</sub>    | 0   | 900 | kHz  |

| Hold time (repeated START condition. After this period, the first clock pulse is generated. | t <sub>HD;STA</sub> | 100 |     |      |

| Low period of the SCL clock                                                                 | t <sub>LOW</sub>    | 560 |     |      |

| High period of the SCL clock                                                                | t <sub>HIGH</sub>   | 560 |     |      |

| Set-up time for a repeated START condition                                                  | t <sub>SU;STA</sub> | 100 |     |      |

| Data hold time                                                                              | t <sub>HD;DAT</sub> | 50  |     | ns   |

| Data set-up time                                                                            | t <sub>SU;DAT</sub> | 50  |     |      |

| Rise time of both SDA and SCL signals                                                       | t <sub>r</sub>      |     | 300 |      |

| Fall time of both SDA and SCL signals                                                       | t <sub>f</sub>      |     | 100 |      |

| Set-up time for STOP condition                                                              | t <sub>SU;STO</sub> | 100 |     |      |

| Bus free time between a STOP and START condition                                            | t <sub>BUF</sub>    | 500 |     |      |

SLAS363D-MARCH 2002-REVISED APRIL 2005

#### PARAMETER MEASUREMENT INFORMATION

SLAS363D-MARCH 2002-REVISED APRIL 2005

SLAS363D-MARCH 2002-REVISED APRIL 2005

SLAS363D-MARCH 2002-REVISED APRIL 2005

SLAS363D-MARCH 2002-REVISED APRIL 2005

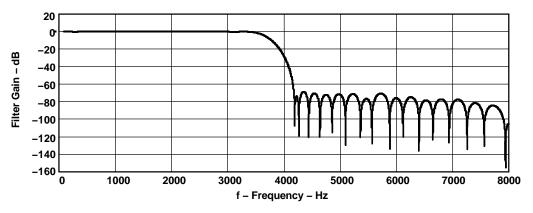

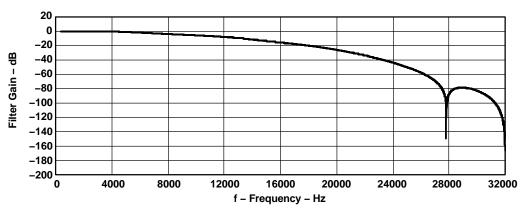

Figure 17. DAC Channel Frequency Response - FIR/IIR Bypass Mode

## **Functional Description**

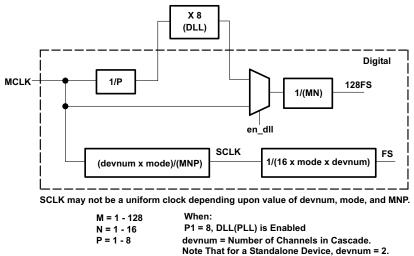

## **Operating Frequencies**

The sampling frequency is the frequency of the frame sync (FS) signal where falling edge starts digital-data transfer for both ADC and DAC. The sampling frequency is derived from the master clock (MCLK) input by the following equations:

- Coarse sampling frequency (default):

- The coarse sampling is selected by programming P = 8 in the control register 4, which is the default configuration of AIC2x on power-up or reset.

- FS = Sampling (conversion) frequency = MCLK / (16 x M x N x 8)

- Fine sampling frequency (see Note 5):

- FS = Sampling (conversion) frequency = MCLK/ (16 x M x N x P)

#### NOTE:

- 1. Use control register 4 to set the following values of M, N, and P

- 2. M = 1, 2, . . . , 128

- 3. N = 1, 2, . . . , 16

- 4. P = 1, 2, ..., 8

- 5. The fine sampling rate needs an on-chip phase lock loop (frequency multiplier) to generate internal clocks. The output of the PLL is only used to generate internal clocks that are needed by the data converters. Other clocks such as the serial interface clocks in master mode are not generated from the PLL output. The clock generation scheme is as shown in Figure 18. The PLL requires the relationship between MCLK and P to meet the following condition: 10 MHz  $\leq$  (MCLK/P)  $\leq$  25 MHz.

- Mode = 1 (For Continious Data Transfer Mode)

- Mode = 2 (For Programming Mode)

#### Figure 18. Clock Timing

6. Selecting the Fine sampling mode turns on the analog PLL, which starts generating after a finite time delay. The internal clocks are required to be present in order to enable the DAC output drivers. Therefore, turning on any output drivers immediately after turning on the PLL causes the output of the DAC to go to the common-mode voltage. While using the PLL, the output drivers must first be enabled before the PLL is enabled in order to ensure correct operation of the part. This implies that register 6B for channel 1 and channel 2 in the codec must be programmed before register 4.

TEXAS INSTRUMENTS www.ti.com

SLASSOSD-MARCH 2002-REVISED AFRIL 2005

#### **Functional Description (continued)**

- 7. Both equations of FS require that the following conditions should be met

- $(M \times N \times P) \le (devnum mode)$  if the FIR/IIR filter is not bypassed.

- [Integer(M/4) x N x P]  $\geq$  (devnum mode) if the FIR/IIR filter is bypassed.

Where:

devnum is the number of codec channels connecting in cascade (devnum = 2 for standalone AIC20) mode is equal to 1 for continuous data transfer mode and 2 for programming mode.

If the DAC OSR is set to 512, then M needs to be a multiple of 4. If the DAC OSR is set to 256, then M needs to be a multiple of 2. M can take any value between 1 and 128 if the OSR is set to 128.

Example:

The MCLK comes from the DSP C5402 CLKOUT and equals to 20.48 MHz and the conversion rate of 8 kHz is desired. First, set P = 1 to satisfy condition 5 so that (MCLK/P) = 20.48 MHz/1 = 20.48 MHz. Next, pick M = 10 and N = 16 to satisfy condition 65 and derive 8 kHz for FS. That is, FS = 20.48 MHz/ (16 x 10 x 16 x 1) = 8 kHz.

#### Internal Architecture

#### Analog Low Pass Filter

The built-in analog low pass antialiasing filter is a two-pole filter that has a 20-dB attenuation at 1 MHz.

#### Sigma-Delta ADC

The sigma-delta analog-to-digital converter is a sigma-delta modulator with 128x oversampling. The ADC provides high-resolution, low-noise performance using oversampling techniques.

#### **Decimation Filter**

The decimation filters consist of a sinc filter stage followed by either FIR filters or IIR filters selected by bit D5 of the control register 1. The FIR filter provides linear-phase output with  $17/f_s$  group delay, whereas the IIR filter generates nonlinear phase output with negligible group delay. The decimation filters reduce the digital data rate to the sampling rate. This is accomplished by decimating with a ratio of 1:128. The output of the decimation filter is a 16-bit 2s-complement data word clocking at the sample rate selected for that particular data channel. The BW of the filter is (0.45 x FS) and scales linearly with the sample rate.

#### Sigma-Delta DAC

The sigma-delta digital-to-analog converter is a sigma-delta modulator with 128x oversampling. The DAC provides high-resolution, low-noise performance using oversampling techniques. The oversampling ratio (OSR) in DAC is programmable to 256/512 using bits D0-D1 of register 3C, the default being 128. The OSR of 512 is recommended when the FS is a maximum of 8 Ksps, and an OSR of 256 is recommended when the FS is a maximum of 16 Ksps. It is also required that the value of M used in programming the PLL be a multiple of 4 if the OSR is set to 512 and 2 if the OSR is set to 256

#### Interpolation Filter

The interpolation filters consist of either FIR or IIR filters selected by bit D5 of control register 1 followed by a sinc filter stage. The FIR filter provides linear-phase output with  $18/f_s$  group delay, whereas the IIR filter generates nonlinear phase output with negligible group delay. The interpolation filter resamples the digital data at a rate of 128 times the incoming sample rate. The high-speed data output from the interpolation filter is then used in the sigma-delta DAC. The BW of the filter is  $(0.45 \times FS)$  and scales linearly with the sample rate.

## **Functional Description (continued)**

#### **Analog/Digital Loopback**

The analog and digital loopbacks provide a means of testing the data ADC/DAC channels and can be used for in-circuit system level tests. The analog loopback always has the priority to route the DAC low pass filter output into the analog input where it is then converted by the ADC to a digital word. The digital loopback routes the ADC output to the DAC input on the device. Analog loopback is enabled by writing a 1 to bit D2 in the control register 1. Digital loopback is enabled by writing a 1 to bit D1 in control register 1.

#### **Analog Sidetone**

The analog sidetone attenuates the analog input and mixes it with the output of the DAC. The control register 5C selects the attenuation level of the analog sidetone.

#### **Digital Sidetone**

The digital sidetone attenuates the ADC output and mixes it with the input of the DAC. The control register 5C selects the attenuation level of the digital sidetone.

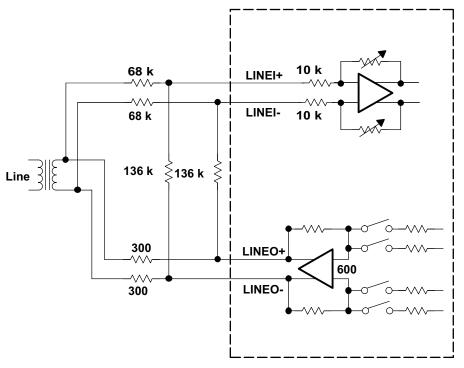

#### Analog Input/Output

To produce excellent common-mode rejection of unwanted signal performance, the analog signal is processed differentially until it is converted to digital data. The signal source driving the analog inputs should have low source impedance for lowest noise performance and accuracy. To obtain maximum dynamic range, the signal must be ac coupled to the input terminal. The analog output is differential from the digital-to-analog converter.

#### **Analog Crosspoint**

The analog crosspoint is a lossless analog switch matrix controlled via the serial control port. It allows any source device to be connected to any sink device. Additionally, special summing connections with adjustable loss (7 × 3 dB steps) are included to implement sidetone for the headset and handset ports. (Also included is muting function on any of the sink devices). The control of the analog crosspoint, defined in the control register 6, is to allow any analog input or output to connect to a codec at one time. If more than one input is selected, these inputs are mixed together before the conversion. Caution needs to be taken to make sure that both DAC channels are not connected to the same output.

#### Analog Input Amplifier

The integrated programmable gain amplifier (PGA) controls the amplification of any analog input before the analog-to-digital converter converts the signal. The PGA's gain from 0 dB to 42 dB in 1.5-dB steps and 48 dB and 54 dB are selected using the control register 5A.

#### **Microphone Bias**

To operate electret microphones properly, a bias voltage and current are provided. Typically, the current drawn by the microphone is in the order of 100  $\mu$ A to 800  $\mu$ A and the bias voltage is specified across the microphone at 1.35 V or 2.35 V. The MICBIAS has good power supply noise rejection in the audio band and the bias voltage is selectable, via bit D3 of control register 1, for each interface.

#### **Output Drivers**

The HSNO and HDSO are output from two audio amplifiers to drive low-voltage speakers like those in the handset and headset. They can drive a load of 150  $\Omega$ . The drive amplifier is differential to minimize noise and EMC immunity problems. The frequency response is flat up to 26 kHz.

#### **Speaker Driver**

The SPKO is output from the audio amplifier that can drive an 8- $\Omega$  speaker load. The drive amplifier is differential to minimize noise and EMC immunity problems. The frequency response is flat up to 26 kHz.

SLAS363D-MARCH 2002-REVISED APRIL 2005

#### Functional Description (continued)

#### **IIR/FIR Control**

#### **Overflow Flags**

The decimation IIR/FIR filter sets an overflow flag (bit D7) of control register 1 indicating that the input analog signal has exceeded the range of internal decimation filter calculations. The interpolation IIR/FIR filter sets an overflow flag (bit D4) of control register 1 indicating that the digital input has exceeded the range of internal interpolation filter calculations. When the IIR/FIR overflow flag is set in the register, it remains set until the user reads the register. Reading this value resets the overflow flag. These flags need to be reset after power up by reading the register. If FIR/IIR overflow occurs, the input signal should be attenuated by either the PGA or some other method.

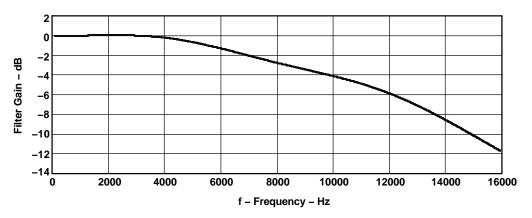

#### **IIR/FIR Bypass Mode**

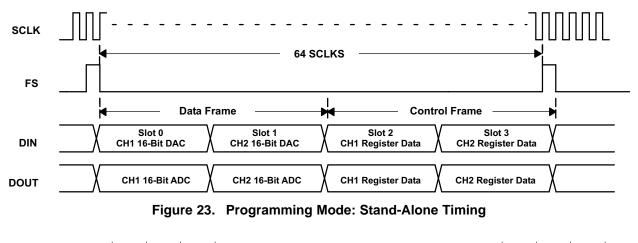

An option is provided to bypass IIR/FIR filter sections of the decimation filter and the interpolation filter. This mode is selected through bit D6 of control register 2 and effectively increases the frequency of the FS signal to four times normal output rate of the IIR/FIR-filter. For example, for a normal sampling rate of 8 Ksps (i.e., FS = 8 kHz) with IIR/FIR, if the IIR/FIR is bypassed, the frequency of FS is readjusted to 4x8 kHz = 32 kHz. The sync filters of the two paths can not be bypassed. A maximum of four devices in cascade can be supported in the IIR/FIR bypass mode.

In this mode , the ADC channel outputs data which has been decimated only till 4 FS. Similarly DAC channel input needs to be preinterpolated to 4 FS before being given to the device. This mode allows users the flexibility to implement their own filter in DSP for decimation and interpolation. M should be a multiple of 4 during IIR/FIR bypass mode.

#### System Reset and Power Management

#### Software and Hardware Reset

The TLV320AIC2x resets internal counters and registers in response to either of two events:

- A low-going reset pulse is applied to terminal RESET

- A 1 is written to the programmable software reset bits (D3 of control register 3A)

NOTE: The TLV320AIC2x requires a power-up reset applied to the RESET pin.

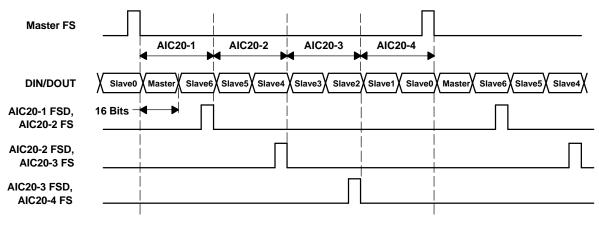

Either event resets the control registers and clears all sequential circuits in the device. The H/W RESET (active low) signal is at least 6 master clock periods long. As soon as the RESET input is applied, the TLV320AIC2x enters the initialization cycle that lasts for 132 MCLKs, during which the serial port of the DSP must be 3-stated. The initialization sequence performed by the AIC2x is known as Auto Cascade Detection (ACD). ACD is a mechanism that allows a device to know its address in a cascade chain. Up to 8 AIC2x devices can be cascaded together.

The Master device is the first device on the chain i.e. the FS of the Master is connected to the FS of the DSP.

During ACD, each device gets to know the number of devices in the chain as well as its relative position in the chain. This is done upon hardware reset. Therefore, after power up, a hardware reset must be completed. ACD requires 132 MCLKs after reset to complete operation. The number of MCLKs is independent of the number of devices in the chain.

Adjacent devices in the chain have their FS and FSD pins connected to each other. The master device's FS is connected to the FS pin of the DSP. The FSD pin on the last device in the chain is pulled high for master-slave configuration, and it is pulled low for stand-alone slave configuration.

The master device has the highest address i.e., the master device has address equal to total no of channels in cascade minus 1. For example, if 8 devices are cascaded, then the master device has address 15 and 14 followed by the next device which has 13 and 12 etc.

During the first 64 MCLKs, FS is configured as an output and FSD as an input.

During the next 64 MCLKs, FS is configured as an input and FSD as an output.

#### **Functional Description (continued)**

The Master device always has its FS configured as an output and the last slave in the cascade (i.e. channel with address 0) always has its FSD configured as an input.

To calculate the channel address, during the first 64 MCLKs, the device counts the number of clocks between ACD starting (reset) and the FSD going high.

During the next 64 MCLKs, the device counts the number of clocks till FS is pulled low.

The sum total of the counts in the first phase and the second phase is the number of devices in the channel.

For a cascaded system the rise time of H/W RESET must be less than the MCLK period and should satisfy setup time requirement of 2 ns with respect to MCLK rise-edge. If more than one codec is cascaded together, RESET must be synchronized to MCLK. Additionally all devices must see the same edge of MCLK within a window of 0.5 ns. This requirement does not exist for a single master or slave. MCLK and RESET can be asynchronous events.

#### Power Management

Most of the device (all except the digital interface) enters the power-down mode when D5 and D4, in control register 3A, are set to 1. When the PWRDN pin is low, the entire device is powered down. In either case, register contents are preserved and the output of the amplifier is held at midpoint voltage to minimize pops and clicks.

The amount of power drawn during software power down is higher than during a hardware power down because of the current required to keep the digital interface active. Additional differences between software and hardware power-down modes are detailed in the following paragraphs.

#### Software Power-Down

Data bits D5 and D4 of control register 3A are used by TLV320AIC2x to turn on or off the software power-down mode, which takes effect in the next frame FS. The ADC and DAC can be powered down individually. In the software power-down, the digital interface circuit is still active while the internal ADC and DAC channel and all differential analog outputs are disabled, and DOUT is put in 3-state in the data frame only. Register data in the control frame is still accepted via DIN, but data in the data frame is ignored. The device returns to normal operation when D7 and D6 of control register 3A are reset.

If the PLL is enabled (i.e., P is not set to 8), then executing a software power down and power up of the device causes the output drivers to go to the common-mode voltage. Therefore, before executing a software power down, the PLL must first be disabled (i.e., P should first be set to 8) before control register 3A is programmed. While bringing the codec out of software power down, the PLL should be re-enabled only after the codec is brought out of power down (i.e., register 3A must be programmed first followed by register 4).

#### Hardware Power-Down

The TLV320AIC2x requires the PWRDN signal to be synchronized with MCLK. When PWRDN is held low, the device enters hardware power-down mode. In this state, the internal clock control circuit and the differential outputs are disabled. All other digital I/Os are disabled and DIN can not accept any data input. The device can only be returned to normal operation by holding PWRDN high. When not holding the device in the hardware power-down mode, PWRDN must be tied high.

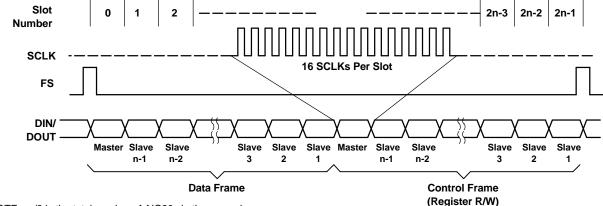

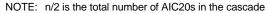

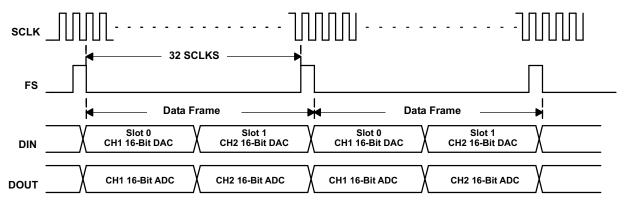

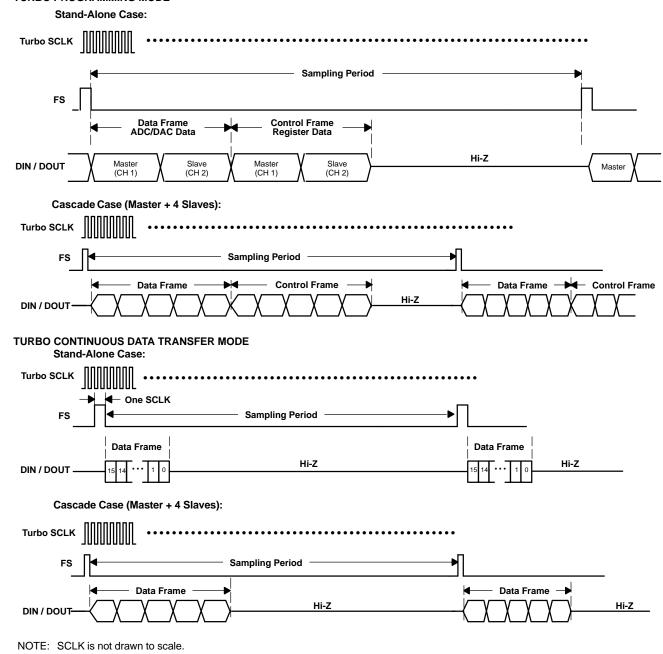

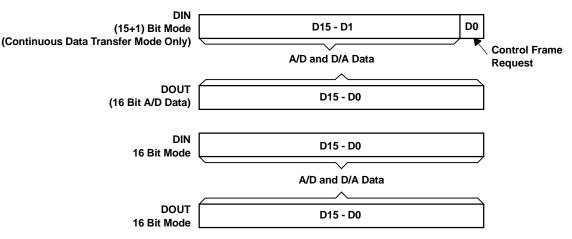

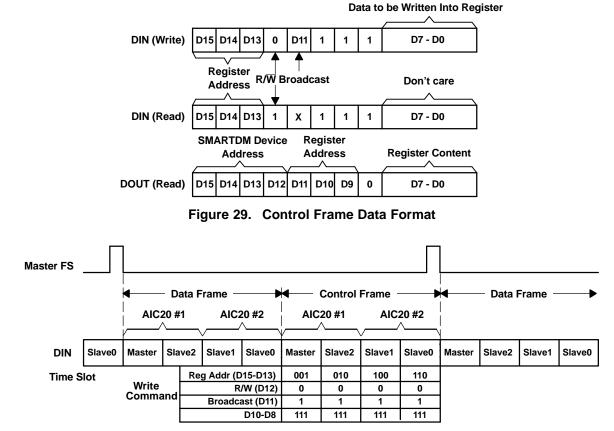

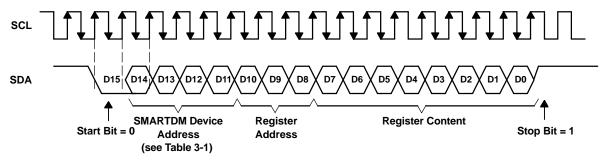

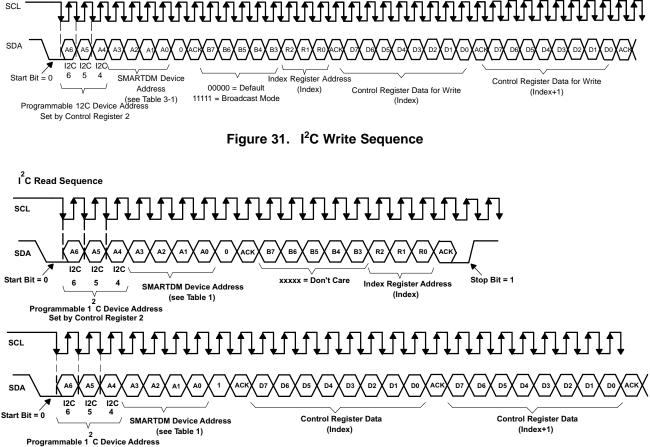

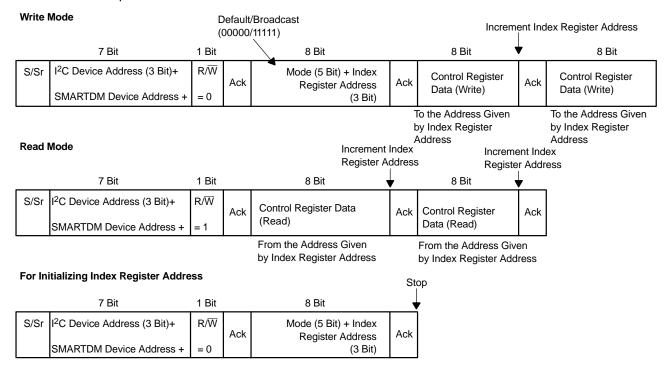

#### Smart Time Division Multiplexed Serial Port (SMARTDM)