# High Performance Narrow-Band Transceiver IC

# **Data Sheet**

# **ADF7021**

### FEATURES

Low power, narrow-band transceiver Frequency bands using dual VCO 80 MHz to 650 MHz 862 MHz to 950 MHz **Modulation schemes** 2FSK, 3FSK, 4FSK, MSK Spectral shaping Gaussian and raised cosine filtering **Data rates supported** 0.05 kbps to 32.8 kbps 2.3 V to 3.6 V power supply Programmable output power -16 dBm to +13 dBm in 63 steps **Automatic PA ramp control Receiver sensitivity** -130 dBm at 100 bps, 2FSK -122 dBm at 1 kbps, 2FSK -113 dBm at 25 kbps, raised cosine 2FSK Patent pending, on-chip image rejection calibration On-chip VCO and fractional-N PLL On-chip, 7-bit ADC and temperature sensor Fully automatic frequency control loop (AFC) Digital received signal strength indication (RSSI) Integrated Tx/Rx switch 0.1 µA leakage current in power-down mode

### APPLICATIONS

Narrow-band standards ETSI EN 300 220, FCC Part 15, FCC Part 90, FCC Part 95,

- ARIB STD-T67 Low cost, wireless data transfer

- Remote control/security systems

- Wireless metering

- Private mobile radio

- Wireless medical telemetry service (WMTS)

- Keyless entry

- Home automation

- Process and building control

- Pagers

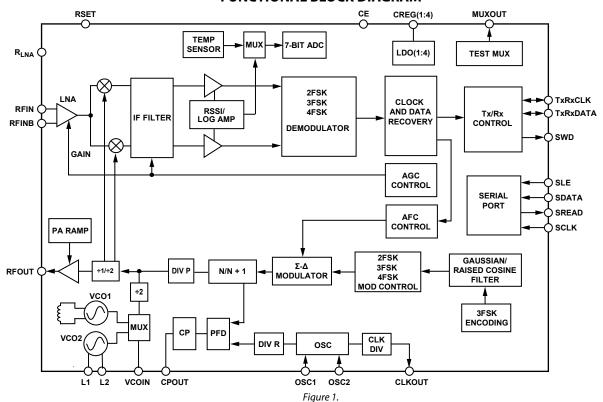

### FUNCTIONAL BLOCK DIAGRAM

#### Rev. D Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2007–2016 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

05876-001

# TABLE OF CONTENTS

| Features 1                                      |

|-------------------------------------------------|

| Applications1                                   |

| Functional Block Diagram 1                      |

| Revision History                                |

| General Description                             |

| Specifications                                  |

| RF and PLL Specifications5                      |

| Transmission Specifications                     |

| Receiver Specifications8                        |

| Digital Specifications10                        |

| General Specifications11                        |

| Timing Characteristics11                        |

| Absolute Maximum Ratings15                      |

| ESD Caution15                                   |

| Pin Configuration and Function Descriptions     |

| Typical Performance Characteristics             |

| Frequency Synthesizer                           |

| Reference Input                                 |

| MUXOUT                                          |

| Voltage Controlled Oscillator (VCO)             |

| Choosing Channels for Best System Performance25 |

| Transmitter                                     |

| RF Output Stage                                 |

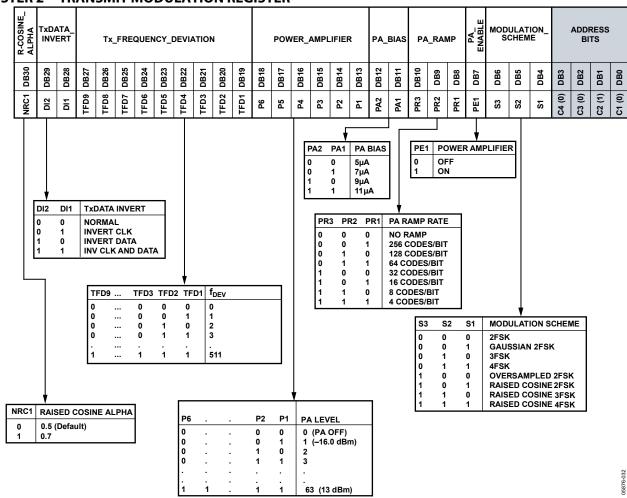

| Modulation Schemes                              |

| Spectral Shaping                                |

| Modulation and Filtering Options                |

| Transmit Latency                                |

| Test Pattern Generator                          |

| Receiver Section                                |

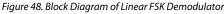

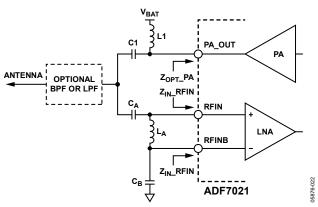

| RF Front End                                    |

| IF Filter                                       |

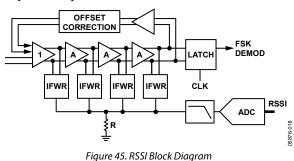

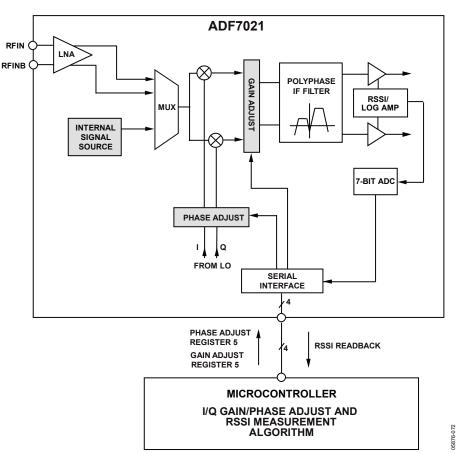

| RSSI/AGC                                        |

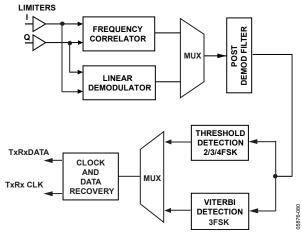

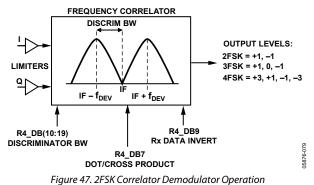

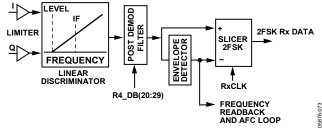

| Demodulation, Detection, and CDR                |

### **REVISION HISTORY**

| 9/2016—Rev. C to Rev. D                                   |

|-----------------------------------------------------------|

| Changes to General Description Section4                   |

| Changes to Interfacing to Microcontroller/DSP Section and |

| Figure 5846                                               |

### 10/2014-Rev. B to Rev. C

| Changes to Table 8                                      | 16 |

|---------------------------------------------------------|----|

| Change to Figure 36                                     | 24 |

| Change to IF Filter Fine Calibration Overview Section   | 30 |

| Change to Post Demodulator Filter Setup Section         | 34 |

| Change to Battery Voltage/ADCIN/Temperature Sensor      |    |

| Readback Section                                        | 45 |

| Change to Register 4—Demodulator Setup Register Section | 51 |

| Change to Register 7-Readback Setup Register Section    | 54 |

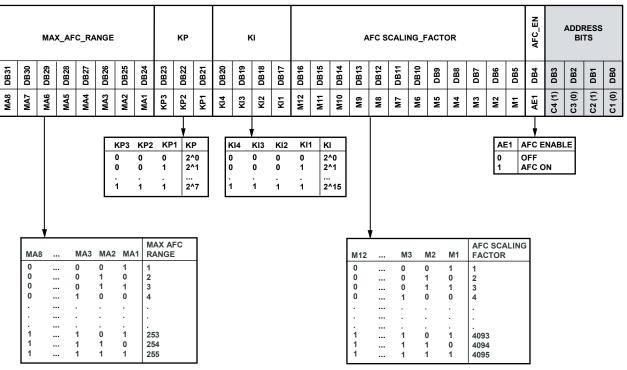

| Change to Register 10—AFC Register Section              | 57 |

|                                                         |    |

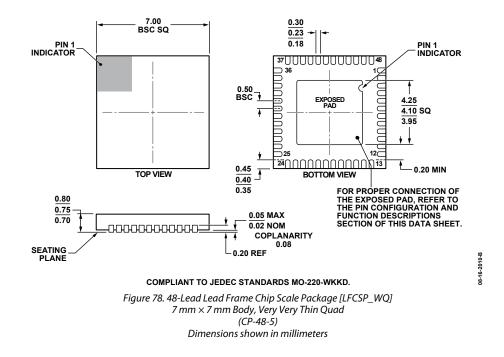

### 4/2013—Rev. A to Rev. B

| Changes to Figure 10       | 16 |

|----------------------------|----|

| Updated Outline Dimensions |    |

| Changes to Ordering Guide  | 62 |

#### 9/2007—Rev. 0 to Rev. A

| Change to UART/SPI Mode Section14                         |

|-----------------------------------------------------------|

| Changes to Figure 10                                      |

| Change to Table 816                                       |

| Changes to Figure 12                                      |

| Change to Internal Inductor VCO Section                   |

| Changes to Figure 40                                      |

| Changes to Figure 47                                      |

| Change to Table 19                                        |

| Changes to Figure 56                                      |

| Change to SPI Mode Section                                |

| Changes to Figure 5946                                    |

| Changes to Figure 60                                      |

| Change to Register 3—Transmit/Receive Clock               |

| Register Section                                          |

| Change to Register 4—Demodulator Setup Register Section51 |

| Change to Register 7—Readback Setup Register54            |

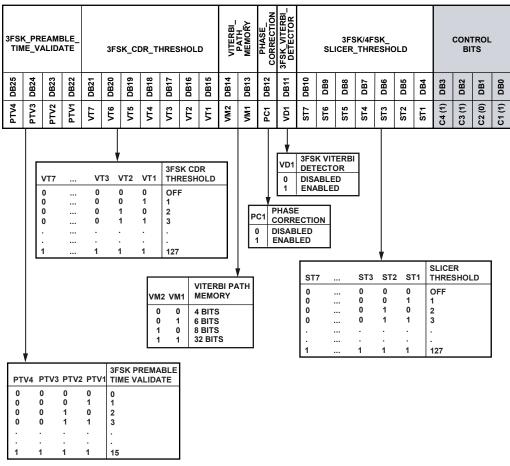

| Change to Register 13—3FSK/4FSK Demod Register Heading 59 |

3/2007—Revision 0: Initial Version

# **GENERAL DESCRIPTION**

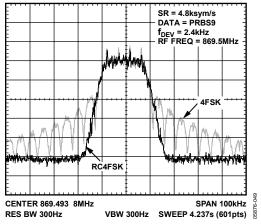

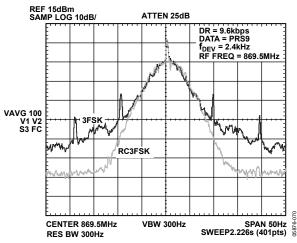

The ADF7021 is a high performance, low power, highly integrated 2FSK/3FSK/4FSK transceiver. It is designed to operate in the narrowband, license-free ISM bands, and in the licensed bands with frequency ranges of 80 MHz to 650 MHz and 862 MHz to 950 MHz. The device has both Gaussian and raised cosine transmit data filtering options to improve spectral efficiency for narrowband applications. It is suitable for circuit applications targeted at European ETSI EN 300 220, the Japanese ARIB STD-T67, the Chinese short range device regulations, and the North American FCC Part 15, Part 90, and Part 95 regulatory standards. A complete transceiver can be built using a small number of external discrete components, making the ADF7021 very suitable for price sensitive and area sensitive applications.

The range of on-chip FSK modulation and data filtering options allows users greater flexibility in their choice of modulation schemes while meeting tight spectral efficiency requirements. The ADF7021 also supports protocols that dynamically switch between 2FSK/3FSK/4FSK to maximize communication range and data throughput.

The transmit section contains dual voltage controlled oscillators (VCOs) and a low noise fractional-N PLL with an output resolution of <1 ppm. The ADF7021 has a VCO using an internal LC tank (431 MHz to 475 MHz, 862 MHz to 950 MHz) and a VCO using an external inductor as part of its tank circuit (80 MHz to 650 MHz). The dual VCO design allows dual-band operation where the user can transmit and/or receive at any frequency supported by the internal inductor VCO and can also transmit and/or receive at a particular frequency band supported by the external inductor VCO.

The frequency agile PLL allows the ADF7021 to be used in frequency hopping spread spectrum (FHSS) systems. Both VCOs operate at twice the fundamental frequency to reduce spurious emissions and frequency pulling problems.

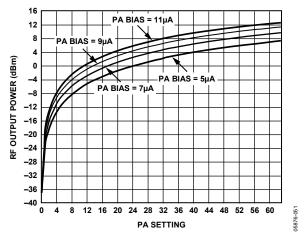

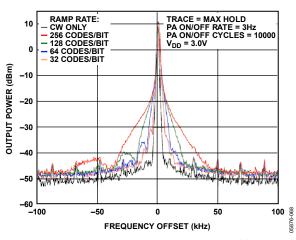

The transmitter output power is programmable in 63 steps from -16 dBm to +13 dBm, and has an automatic power ramp control to prevent spectral splatter and help meet regulatory standards. The transceiver RF frequency and modulation are programmable using a simple 3-wire interface. The device operates with a power supply range of 2.3 V to 3.6 V and can be powered down when not in use.

A low IF architecture is used in the receiver (100 kHz), which minimizes power consumption and the external component count, yet avoids dc offset and flicker noise at low frequencies. The IF filter has programmable bandwidths of 12.5 kHz, 18.75 kHz, and 25 kHz. The ADF7021 supports a wide variety of programmable features including Rx linearity, sensitivity, and IF bandwidth, allowing the user to trade off receiver sensitivity and selectivity against current consumption, depending on the application. The receiver also features a patent-pending automatic frequency control (AFC) loop with programmable pull-in range that allows the PLL to track out the frequency error in the incoming signal.

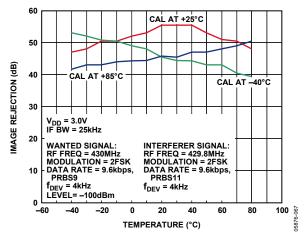

The receiver achieves an image rejection performance of 56 dB using a patent-pending IR calibration scheme that does not require the use of an external RF source.

An on-chip ADC provides readback of the integrated temperature sensor, external analog input, battery voltage, and RSSI signal, which provides savings on an ADC in some applications. The temperature sensor is accurate to  $\pm 10^{\circ}$ C over the full operating temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C. This accuracy can be improved by performing a 1-point calibration at room temperature and storing the result in memory.

# **SPECIFICATIONS**

$V_{DD} = 2.3 \text{ V}$  to 3.6 V, GND = 0 V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical specifications are at  $V_{DD} = 3 \text{ V}$ ,  $T_A = 25^{\circ}$ C. All measurements are performed with the EVAL-ADF7021DB evaluation boards using the PN9 data sequence, unless otherwise noted.

### **RF AND PLL SPECIFICATIONS**

#### Table 1.

| Parameter                                             | Min    | Тур         | Max   | Unit   | Test Conditions/Comments                                                                                             |

|-------------------------------------------------------|--------|-------------|-------|--------|----------------------------------------------------------------------------------------------------------------------|

| RF CHARACTERISTICS                                    |        |             |       |        | See Table 9 for required VCO_BIAS and VCO_ADJUST settings                                                            |

| Frequency Ranges (Direct Output)                      | 160    |             | 650   | MHz    | External inductor VCO                                                                                                |

|                                                       | 862    |             | 950   | MHz    | Internal inductor VCO                                                                                                |

| Frequency Ranges (RF Divide-by-2 Mode)                | 80     |             | 325   | MHz    | External inductor VCO, RF divide-by-2 enabled                                                                        |

|                                                       | 431    |             | 475   | MHz    | Internal inductor VCO, RF divide-by-2 enabled                                                                        |

| Phase Frequency Detector (PFD) Frequency <sup>1</sup> | RF/256 |             | 26/30 | MHz    | Crystal reference/external reference                                                                                 |

| PHASE-LOCKED LOOP (PLL)                               |        |             |       |        |                                                                                                                      |

| VCO Gain <sup>2</sup>                                 |        |             |       |        |                                                                                                                      |

| 868 MHz, Internal Inductor VCO                        |        | 58          |       | MHz/V  | VCO_ADJUST = 0, VCO_BIAS = 8                                                                                         |

| 434 MHz, Internal Inductor VCO                        |        | 29          |       | MHz/V  | VCO_ADJUST = 0, VCO_BIAS = 8                                                                                         |

| 426 MHz, External Inductor VCO                        |        | 27          |       | MHz/V  | VCO_ADJUST = 0, VCO_BIAS = 3                                                                                         |

| 160 MHz, External Inductor VCO                        |        | 6           |       | MHz/V  | VCO_ADJUST = 0, VCO_BIAS = 2                                                                                         |

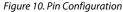

| Phase Noise (In-Band)                                 |        |             |       |        |                                                                                                                      |

| 868 MHz, Internal Inductor VCO                        |        | -97         |       | dBc/Hz | 10 kHz offset, PA = 10 dBm, V <sub>DD</sub> = 3.0 V,<br>PFD = 19.68 MHz, VCO_BIAS = 8                                |

| 433 MHz, Internal Inductor VCO                        |        | -103        |       | dBc/Hz | 10 kHz offset, PA = 10 dBm, V <sub>DD</sub> = 3.0 V,<br>PFD = 19.68 MHz, VCO_BIAS = 8                                |

| 426 MHz, External Inductor VCO                        |        | -95         |       | dBc/Hz | 10 kHz offset, PA = 10 dBm, $V_{DD}$ = 3.0 V,<br>PFD = 9.84 MHz, VCO_BIAS = 3                                        |

| Phase Noise (Out-of-Band)                             |        | -124        |       | dBc/Hz | 1 MHz offset, $f_{RF}$ = 433 MHz, PA = 10 dBm,<br>V <sub>DD</sub> = 3.0 V, PFD = 19.68 MHz, VCO_BIAS = 8             |

| Normalized In-Band Phase Noise Floor <sup>3</sup>     |        | -203        |       | dBc/Hz |                                                                                                                      |

| PLL Settling                                          |        | 40          |       | μs     | Measured for a 10 MHz frequency step to within<br>5 ppm accuracy, PFD = 19.68 MHz, loop<br>bandwidth (LBW) = 100 kHz |

| REFERENCE INPUT                                       |        |             |       |        |                                                                                                                      |

| Crystal Reference <sup>₄</sup>                        | 3.625  |             | 26    | MHz    |                                                                                                                      |

| External Oscillator <sup>4, 5</sup>                   | 3.625  |             | 30    | MHz    |                                                                                                                      |

| Crystal Start-Up Time <sup>6</sup>                    |        |             |       |        |                                                                                                                      |

| XTAL Bias = $20 \ \mu A$                              |        | 0.930       |       | ms     | 10 MHz XTAL, 33 pF load capacitors, $V_{DD} = 3.0 V$                                                                 |

| XTAL Bias = $35 \mu A$                                |        | 0.438       |       | ms     | 10 MHz XTAL, 33 pF load capacitors, $V_{DD} = 3.0 V$                                                                 |

| Input Level for External Oscillator <sup>7</sup>      |        |             |       |        |                                                                                                                      |

| OSC1                                                  |        | 0.8         |       | V р-р  | Clipped sine wave                                                                                                    |

| OSC2                                                  |        | CMOS levels |       | V      |                                                                                                                      |

| ADC PARAMETERS                                        |        |             |       |        |                                                                                                                      |

| INL                                                   |        | ±0.4        |       | LSB    | $V_{DD} = 2.3 V$ to 3.6 V, $T_A = 25^{\circ}C$                                                                       |

| DNL                                                   |        | ±0.4        |       | LSB    | $V_{DD} = 2.3 \text{ V to } 3.6 \text{ V}, T_A = 25^{\circ}\text{C}$                                                 |

<sup>1</sup> The maximum usable PFD at a particular RF frequency is limited by the minimum N divide value.

<sup>2</sup> VCO gain measured at a VCO tuning voltage of 1 V. The VCO gain varies across the tuning range of the VCO. The software package ADIsimPLL<sup>™</sup> can be used to model this variation.

<sup>3</sup> This value can be used to calculate the in-band phase noise for any operating frequency. Use the following equation to calculate the in-band phase noise performance as seen at the PA output:  $-203 + 10 \log(f_{PFD}) + 20 \log N$ .

<sup>4</sup> Guaranteed by design. Sample tested to ensure compliance.

<sup>5</sup> A TCXO, VCXÓ, or OCXO can be used as an external oscillator.

<sup>6</sup> Crystal start-up time is the time from chip enable (CE) being asserted to correct clock frequency on the CLKOUT pin.

<sup>7</sup> Refer to the Reference Input section for details on using an external oscillator.

## TRANSMISSION SPECIFICATIONS

#### Table 2.

| Parameter                                            | Min   | Тур     | Мах               | Unit | Test Conditions/Comments                                                                                                                                                                             |

|------------------------------------------------------|-------|---------|-------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA RATE                                            |       |         |                   |      |                                                                                                                                                                                                      |

| 2FSK, 3FSK                                           | 0.05  |         | 251               | kbps | $IF_BW = 25 \text{ kHz}$                                                                                                                                                                             |

| 4FSK                                                 | 0.05  |         | 32.8 <sup>2</sup> | kbps | $IF_BW = 25 \text{ kHz}$                                                                                                                                                                             |

| MODULATION                                           |       |         |                   |      |                                                                                                                                                                                                      |

| Frequency Deviation (f <sub>DEV</sub> ) <sup>3</sup> | 0.056 |         | 28.26             | kHz  | PFD = 3.625 MHz                                                                                                                                                                                      |

|                                                      | 0.306 |         | 156               | kHz  | PFD = 20 MHz                                                                                                                                                                                         |

| Deviation Frequency Resolution                       | 56    |         |                   | Hz   | PFD = 3.625 MHz                                                                                                                                                                                      |

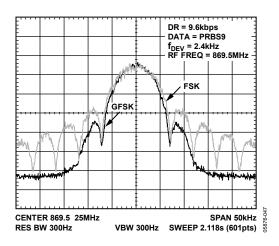

| Gaussian Filter BT                                   |       | 0.5     |                   |      |                                                                                                                                                                                                      |

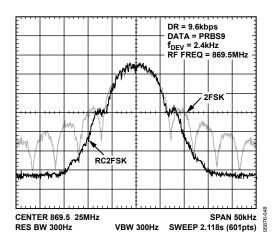

| Raised Cosine Filter Alpha                           |       | 0.5/0.7 |                   |      | Programmable                                                                                                                                                                                         |

| TRANSMIT POWER                                       |       |         |                   |      |                                                                                                                                                                                                      |

| Maximum Transmit Power⁴                              |       | +13     |                   | dBm  | $V_{DD} = 3.0 \text{ V}, T_A = 25^{\circ}\text{C}$                                                                                                                                                   |

| Transmit Power Variation vs.<br>Temperature          |       | ±1      |                   | dB   | –40°C to +85°C                                                                                                                                                                                       |

| Transmit Power Variation vs. VDD                     |       | ±1      |                   | dB   | 2.3 V to 3.6 V at 915 MHz, T <sub>A</sub> = 25°C                                                                                                                                                     |

| Transmit Power Flatness                              |       | ±1      |                   | dB   | 902 MHz to 928 MHz, 3 V, T <sub>A</sub> = 25°C                                                                                                                                                       |

| Programmable Step Size                               |       | 0.3125  |                   | dB   | –20 dBm to +13 dBm                                                                                                                                                                                   |

| ADJACENT CHANNEL POWER (ACP)                         |       |         |                   |      |                                                                                                                                                                                                      |

| 426 MHz, External Inductor VCO                       |       |         |                   |      | PFD = 9.84 MHz                                                                                                                                                                                       |

| 12.5 kHz Channel Spacing                             |       | -50     |                   | dBc  | Gaussian 2FSK modulation, measured in a $\pm$ 4.25 kHz bandwidth at $\pm$ 12.5 kHz offset, 2.4 kbps PN9 data, 1.2 kHz frequency deviation, compliant with ARIB STD-T67                               |

| 25 kHz Channel Spacing                               |       | -50     |                   | dBc  | Gaussian 2FSK modulation, measured in a $\pm 8$ kHz bandwidth at $\pm 25$ kHz offset, 9.6 kbps PN9 data, 2.4 kHz frequency deviation, compliant with ARIB STD-T67                                    |

| 868 MHz, Internal Inductor VCO                       |       |         |                   |      | PFD = 19.68  MHz                                                                                                                                                                                     |

| 12.5 kHz Channel Spacing                             |       | -46     |                   | dBm  | Gaussian 2FSK modulation, 10 dBm output power, measured in<br>a $\pm 6.25$ kHz bandwidth at $\pm 12.5$ kHz offset, 2.4 kbps PN9 data,<br>1.2 kHz frequency deviation, compliant with ETSI EN 300-220 |

| 25 kHz Channel Spacing                               |       | -43     |                   | dBm  | Gaussian 2FSK modulation, 10 dBm output power, measured in a $\pm 12.5$ kHz bandwidth at $\pm 25$ kHz offset, 9.6 kbps PN9 data, 2.4 kHz frequency deviation, compliant with ETSI EN 300-220         |

| 433 MHz, Internal Inductor VCO                       |       |         |                   |      | PFD = 19.68 MHz                                                                                                                                                                                      |

| 12.5 kHz Channel Spacing                             |       | -50     |                   | dBm  | Gaussian 2FSK modulation, 10 dBm output power, measured in a $\pm$ 6.25 kHz bandwidth at $\pm$ 12.5 kHz offset, 2.4 kbps PN9 data, 1.2 kHz frequency deviation, compliant with ETSI EN 300-220       |

| 25 kHz Channel Spacing                               |       | -47     |                   | dBm  | Gaussian 2FSK modulation, 10 dBm output power, measured in a $\pm$ 12.5 kHz bandwidth at $\pm$ 25 kHz offset, 9.6 kbps PN9 data, 2.4 kHz frequency deviation, compliant with ETSI EN 300-220         |

| OCCUPIED BANDWIDTH                                   |       |         |                   |      | 99.0% of total mean power; 12.5 kHz channel spacing (2.4 kbps<br>PN9 data, 1.2 kHz frequency deviation); 25 kHz channel spacing<br>(9.6 kbps PN9 data, 2.4 kHz frequency deviation)                  |

| 2FSK Gaussian Data Filtering                         |       |         |                   |      |                                                                                                                                                                                                      |

| 12.5 kHz Channel Spacing                             |       | 3.9     |                   | kHz  |                                                                                                                                                                                                      |

| 25 kHz Channel Spacing                               |       | 9.9     |                   | kHz  |                                                                                                                                                                                                      |

| 2FSK Raised Cosine Data Filtering                    |       |         |                   |      |                                                                                                                                                                                                      |

| 12.5 kHz Channel Spacing                             |       | 4.4     |                   | kHz  |                                                                                                                                                                                                      |

| 25 kHz Channel Spacing                               |       | 10.2    |                   | kHz  |                                                                                                                                                                                                      |

| 3FSK Raised Cosine Filtering                         |       |         |                   |      |                                                                                                                                                                                                      |

| 12.5 kHz Channel Spacing                             |       | 3.9     |                   | kHz  |                                                                                                                                                                                                      |

| 25 kHz Channel Spacing                               |       | 9.5     |                   | kHz  |                                                                                                                                                                                                      |

| 4FSK Raised Cosine Filtering                         |       |         |                   |      | 19.2 kbps PN9 data, 1.2 kHz frequency deviation                                                                                                                                                      |

| 25 kHz Channel Spacing                               |       | 13.2    |                   | kHz  |                                                                                                                                                                                                      |

| Parameter                              | Min | Тур       | Max | Unit | Test Conditions/Comments                                       |

|----------------------------------------|-----|-----------|-----|------|----------------------------------------------------------------|

| SPURIOUS EMISSIONS                     |     |           |     |      |                                                                |

| Reference Spurs                        |     | -65       |     | dBc  | 100 kHz loop bandwidth                                         |

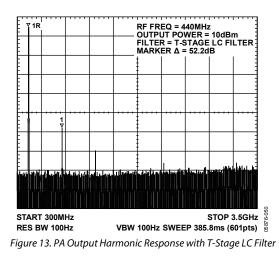

| HARMONICS <sup>5</sup>                 |     |           |     |      | 13 dBm output power, unfiltered conductive/filtered conductive |

| Second Harmonic                        |     | -35/-52   |     | dBc  |                                                                |

| Third Harmonic                         |     | -43/-60   |     | dBc  |                                                                |

| All Other Harmonics                    |     | -36/-65   |     | dBc  |                                                                |

| OPTIMUM PA LOAD IMPEDANCE <sup>6</sup> |     |           |     |      |                                                                |

| $f_{RF} = 915 \text{ MHz}$             |     | 39 + j61  |     | Ω    |                                                                |

| $f_{RF} = 868 \text{ MHz}$             |     | 48 + j54  |     | Ω    |                                                                |

| $f_{RF} = 450 \text{ MHz}$             |     | 98 + j65  |     | Ω    |                                                                |

| $f_{RF} = 426 \text{ MHz}$             |     | 100 + j65 |     | Ω    |                                                                |

| $f_{RF} = 315 \text{ MHz}$             |     | 129 + j63 |     | Ω    |                                                                |

| $f_{RF} = 175 \text{ MHz}$             |     | 173 + j49 |     | Ω    |                                                                |

<sup>1</sup> Using Gaussian or raised cosine filtering. Choose the frequency deviation to ensure that the transmit occupied signal bandwidth is within the receiver IF filter <sup>2</sup> Using raised cosine filtering with an alpha = 0.7. The inner frequency deviation = 1.78 kHz, and the POST\_DEMOD\_BW = 24.6 kHz. <sup>3</sup> For the definition of frequency deviation, refer to the Register 2—Transmit Modulation Register section.

<sup>4</sup> Measured as maximum unmodulated power.

<sup>5</sup> Conductive filtered harmonic emissions measured on the EVAL-ADF7021DB models, which includes a T-stage harmonic filter (two inductors and one capacitor). <sup>6</sup> For matching details, refer to the LNA/PA Matching section.

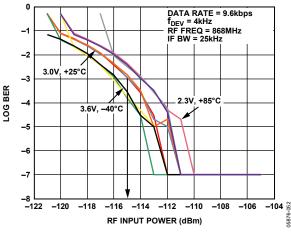

## **RECEIVER SPECIFICATIONS**

# Table 3.

| Parameter                           | Min Typ | Max Un | it Test Conditions/Comments                                                                     |

|-------------------------------------|---------|--------|-------------------------------------------------------------------------------------------------|

| SENSITIVITY                         |         |        | Bit error rate (BER) = $10^{-3}$ , low noise amplifier (LNA) and                                |

| 2FSK                                |         |        | power amplifier (PA) matched separately                                                         |

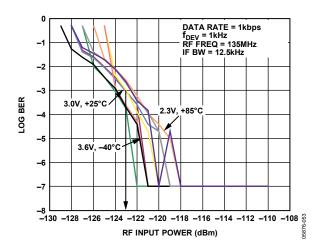

| Sensitivity at 0.1 kbps             | -130    | dBi    | $f_{DEV} = 1 \text{ kHz}$ , high sensitivity mode, IF_BW = 12.5 kHz                             |

| Sensitivity at 0.25 kbps            | -127    | dBi    |                                                                                                 |

| Sensitivity at 1 kbps               | -122    | dBi    |                                                                                                 |

| Sensitivity at 9.6 kbps             | -115    | dBi    |                                                                                                 |

| Sensitivity at 25 kbps              | -110    | dBi    |                                                                                                 |

| Gaussian 2FSK                       |         |        |                                                                                                 |

| Sensitivity at 0.1 kbps             | -129    | dBi    | $f_{DEV} = 1 \text{ kHz}$ , high sensitivity mode, IF_BW = 12.5 kHz                             |

| Sensitivity at 0.25 kbps            | -127    | dBi    |                                                                                                 |

| Sensitivity at 1 kbps               | -121    | dBi    |                                                                                                 |

| Sensitivity at 9.6 kbps             | -114    | dBi    | <b>C P</b>                                                                                      |

| Sensitivity at 25 kbps              | -111    | dBi    |                                                                                                 |

| GMSK                                |         |        |                                                                                                 |

| Sensitivity at 9.6 kbps             | -113    | dBi    | n f <sub>DEV</sub> = 2.4 kHz, high sensitivity mode, IF_BW = 18.75 kHz                          |

| Raised Cosine 2FSK                  |         |        |                                                                                                 |

| Sensitivity at 0.25 kbps            | -127    | dBi    | $f_{DEV} = 1 \text{ kHz}$ , high sensitivity mode, IF_BW = 12.5 kHz                             |

| Sensitivity at 1 kbps               | -121    | dBi    |                                                                                                 |

| Sensitivity at 9.6 kbps             | -114    | dBi    |                                                                                                 |

| Sensitivity at 25 kbps              | -113    | dBi    |                                                                                                 |

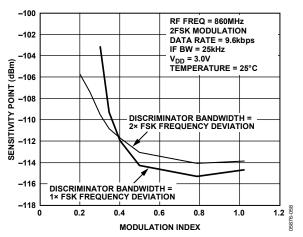

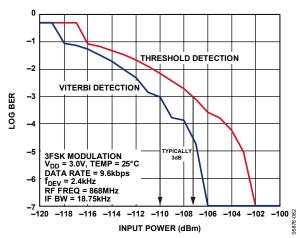

| 3FSK                                |         |        |                                                                                                 |

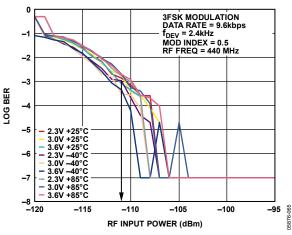

| Sensitivity at 9.6 kbps             | -110    | dBi    | $f_{DEV} = 2.4$ kHz, high sensitivity mode, IF_BW = 18.75 kHz, Viterbi detection on             |

| Raised Cosine 3FSK                  |         |        |                                                                                                 |

| Sensitivity at 9.6 kbps             | -110    | dBi    | $f_{DEV} = 2.4$ kHz, high sensitivity mode, IF_BW = 12.5 kHz, alpha = 0.5, Viterbi detection on |

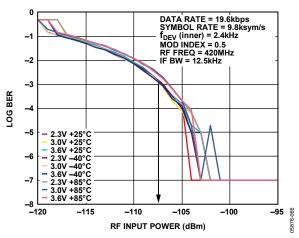

| Sensitivity at 19.6 kbps            | -106    | dBi    |                                                                                                 |

| 4FSK                                |         |        |                                                                                                 |

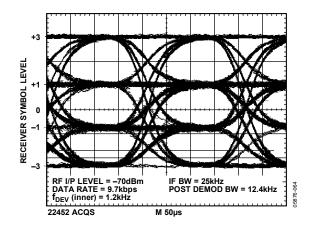

| Sensitivity at 9.6 kbps             | -112    | dBr    | $f_{DEV}$ (inner) = 1.2 kHz, high sensitivity mode, IF_BW = 12.5 kHz                            |

| Sensitivity at 19.6 kbps            | -107    | dBr    | $f_{DEV}$ (inner) = 2.4 kHz, high sensitivity mode, IF_BW = 25 kHz                              |

| Raised Cosine 4FSK                  |         |        |                                                                                                 |

| Sensitivity at 9.6 kbps             | -109    | dBi    | m $f_{DEV}$ (inner) = 1.2 kHz, high sensitivity mode,<br>IF_BW = 12.5 kHz, alpha = 0.5          |

| Sensitivity at 19.2 kbps            | -103    | dBi    | n $f_{DEV}$ (inner) = 1.2 kHz, high sensitivity mode,<br>IF_BW = 18.75 kHz, alpha = 0.5         |

| Sensitivity at 32.8 kbps            | -100    | dBi    | m $f_{DEV}$ (inner) = 1.8 kHz, high sensitivity mode, IF_BW = 25 kHz, alpha = 0.7               |

| INPUT IP3                           |         |        | Two-tone test, $f_{LO} = 860$ MHz, $F1 = f_{LO} + 100$ kHz, $F2 = f_{LO} - 800$ kH              |

| Low Gain Enhanced Linearity<br>Mode | -3      | dBi    | m LNA_GAIN = 3, MIXER_LINEARITY = 1                                                             |

| Medium Gain Mode                    | -13.5   | dBi    | m LNA_GAIN = 10, MIXER_LINEARITY = 0                                                            |

| High Sensitivity Mode               | -24     | dBi    | n LNA_GAIN = 30, MIXER_LINEARITY = 0                                                            |

# ADF7021

| Parameter                          | Min Typ | Max                | Unit     | Test Conditions/Comments                                                                                                          |

|------------------------------------|---------|--------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------|

| ADJACENT CHANNEL REJECTION         |         |                    |          |                                                                                                                                   |

| 868 MHz                            |         |                    |          | Wanted signal is 3 dB above the sensitivity point (BER = $10^{-3}$ );                                                             |

|                                    |         |                    |          | unmodulated interferer is at the center of the adjacent                                                                           |

|                                    |         |                    |          | channel; rejection measured as the difference between<br>interferer level and wanted signal level in dB                           |

| 12.5 kHz Channel Spacing           | 25      |                    | dB       | 12.5 kHz IF_BW                                                                                                                    |

| 25 kHz Channel Spacing             | 23      |                    | dB       | 25 kHz IF_BW                                                                                                                      |

| 25 kHz Channel Spacing             | 39      |                    | dB       | 18 kHz IF_BW                                                                                                                      |

| 426 MHz, External Inductor VCO     | 59      |                    | uв       | Wanted signal 3 dB above reference sensitivity point (BER = $10^{-2}$ );                                                          |

|                                    |         |                    |          | modulated interferer (1 kHz sine, ±2 kHz deviation) at the center                                                                 |

|                                    |         |                    |          | of the adjacent channel; rejection measured as the difference                                                                     |

|                                    |         |                    |          | between interferer level and reference sensitivity level in dB                                                                    |

| 12.5 kHz Channel Spacing           | 25      |                    | dB       | 12.5 kHz IF_BW                                                                                                                    |

| 25 kHz Channel Spacing             | 30      |                    | dB       | 25 kHz IF_BW                                                                                                                      |

| 25 kHz Channel Spacing             | 41      |                    | dB       | 18 kHz IF_BW, compliant with ARIB STD-T67                                                                                         |

| CO-CHANNEL REJECTION               |         |                    |          | Wanted signal (2FSK, 9.6 kbps, ±4 kHz deviation) is 10 dB                                                                         |

|                                    |         |                    |          | above the sensitivity point (BER = $10^{-3}$ ), modulated interferer                                                              |

| 868 MHz                            | -3      |                    | dB       |                                                                                                                                   |

| IMAGE CHANNEL REJECTION            |         |                    |          | Wanted signal (2FSK, 9.6 kbps, ±4 kHz deviation) is 10 dB                                                                         |

|                                    |         |                    |          | above the sensitivity point (BER = $10^{-3}$ ); modulated interferer<br>(2FSK, 9.6 kbps, ±4 kHz deviation) is placed at the image |

|                                    |         |                    |          | frequency of $f_{RF}$ – 200 kHz; interferer level is increased until                                                              |

|                                    |         |                    |          | $BER = 10^{-3}$                                                                                                                   |

| 900 MHz                            | 23/39   |                    | dB       | Uncalibrated/calibrated <sup>1</sup> , $V_{DD} = 3.0 \text{ V}$ , $T_A = 25^{\circ}\text{C}$                                      |

| 450 MHz                            | 29/50   |                    | dB       | Uncalibrated/calibrated <sup>1</sup> , $V_{DD} = 3.0 V$ , $T_A = 25^{\circ}C$                                                     |

| 450 MHz, External Inductor VCO     | 38/53   |                    | dB       | Uncalibrated/calibrated <sup>1</sup> , $V_{DD} = 3.0 V$ , $T_A = 25^{\circ}C$                                                     |

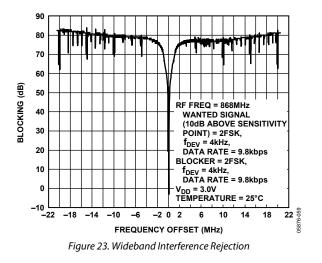

| BLOCKING                           |         |                    |          | Wanted signal is 10 dB above the input sensitivity level;                                                                         |

|                                    |         |                    |          | CW interferer level is increased until BER = $10^{-3}$                                                                            |

| ±1 MHz                             | 69      |                    | dB       |                                                                                                                                   |

| ±2 MHz                             | 75      |                    | dB       |                                                                                                                                   |

| ±5 MHz                             | 78      |                    | dB       |                                                                                                                                   |

| ±10 MHz                            | 78.5    |                    | dB       |                                                                                                                                   |

| SATURATION                         | 12      |                    | dBm      | $2FSK \mod BER = 10^{-3}$                                                                                                         |

| (MAXIMUM INPUT LEVEL)              |         |                    |          |                                                                                                                                   |

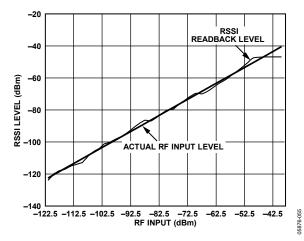

| RSSI                               |         |                    |          |                                                                                                                                   |

| Range at Input <sup>2</sup>        | -120 to |                    | dBm      |                                                                                                                                   |

|                                    | -47     |                    |          |                                                                                                                                   |

| Linearity                          | ±2      |                    | dB       | Input power range = $-100 \text{ dBm to } -47 \text{ dBm}$                                                                        |

| Absolute Accuracy                  | ±3      |                    | dB       | Input power range = $-100 \text{ dBm to } -47 \text{ dBm}$                                                                        |

| Response Time                      | 300     |                    | μs       | See the RSSI/AGC section                                                                                                          |

| AFC                                |         |                    | <b>.</b> |                                                                                                                                   |

| Pull-In Range                      | 0.5     | $1.5 \times IF_BW$ | kHz      | The range is programmable, R10_DB[24:31]                                                                                          |

| Response Time                      | 48      |                    | Bits     |                                                                                                                                   |

| Accuracy                           | 0.5     |                    | kHz      | Input power range = $-100 \text{ dBm to } +12 \text{ dBm}$                                                                        |

| Rx SPURIOUS EMISSIONS <sup>3</sup> |         |                    |          |                                                                                                                                   |

| Internal Inductor VCO              | -91/-97 | 1                  | dBm      | <1 GHz at antenna input, unfiltered conductive/filtered                                                                           |

|                                    | F2/ 7/  | <b>`</b>           | dDaa     | conductive                                                                                                                        |

|                                    | -52/-70 | J                  | dBm      | >1 GHz at antenna input, unfiltered conductive/filtered conductive                                                                |

| External Inductor VCO              | -62/-72 | )                  | dBm      | <1 GHz at antenna input, unfiltered conductive/filtered                                                                           |

|                                    | _02/-/2 | -                  |          | conductive                                                                                                                        |

|                                    | -64/-85 | 5                  | dBm      | >1 GHz at antenna input, unfiltered conductive/filtered                                                                           |

|                                    |         |                    | 1        | conductive                                                                                                                        |

| Parameter                         | Min | Тур        | Max | Unit | Test Conditions/Comments |

|-----------------------------------|-----|------------|-----|------|--------------------------|

| LNA INPUT IMPEDANCE               |     |            |     |      | RFIN to RFGND            |

| $f_{\text{RF}} = 915 \text{ MHz}$ |     | 24 – j60   |     | Ω    |                          |

| $f_{\text{RF}} = 868 \text{ MHz}$ |     | 26 – j63   |     | Ω    |                          |

| $f_{\text{RF}} = 450 \text{ MHz}$ |     | 63 – j129  |     | Ω    |                          |

| $f_{RF} = 426 \text{ MHz}$        |     | 68 – j134  |     | Ω    |                          |

| $f_{RF} = 315 \text{ MHz}$        |     | 96 – j160  |     | Ω    |                          |

| $f_{RF} = 175 \text{ MHz}$        |     | 178 – j190 |     | Ω    |                          |

<sup>1</sup> Calibration of the image rejection used an external RF source. <sup>2</sup> For received signal levels < -100 dBm, it is recommended to average the RSSI readback value over a number of samples to improve the RSSI accuracy at low input powers. <sup>3</sup> Filtered conductive receive spurious emissions measured on the EVAL-ADF7021DB evaluation boards, which includes a T-stage harmonic filter (two inductors and one capacitor).

### **DIGITAL SPECIFICATIONS**

#### Table 4.

| Parameter                                         | Min                    | Тур                              | Max                        | Unit | Test Conditions/Comments                                                                                                                                               |

|---------------------------------------------------|------------------------|----------------------------------|----------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIMING INFORMATION                                |                        |                                  |                            |      |                                                                                                                                                                        |

| Chip Enabled to Regulator Ready                   |                        | 10                               |                            | μs   | $C_{REG} = 100 \text{ nF}$                                                                                                                                             |

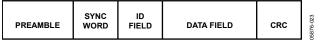

| Chip Enabled to Tx Mode                           |                        |                                  |                            |      | 32-bit register write time = 50 $\mu$ s                                                                                                                                |

| TCXO Reference                                    |                        | 1                                |                            | ms   |                                                                                                                                                                        |

| XTAL                                              |                        | 2                                |                            | ms   |                                                                                                                                                                        |

| Chip Enabled to Rx Mode                           |                        |                                  |                            |      | 32-bit register write time = 50 $\mu$ s, IF filter coarse calibration only                                                                                             |

| TCXO Reference                                    |                        | 1.2                              |                            | ms   |                                                                                                                                                                        |

| XTAL                                              |                        | 2.2                              |                            | ms   |                                                                                                                                                                        |

| Tx to Rx Turnaround Time                          |                        | 300 µs + (5 × t <sub>BIT</sub> ) |                            |      | Time to synchronized data out, includes AGC settling and CDR synchronization; see AGC Information and Timing section for more details; $t_{BIT} = data \ bit \ period$ |

| LOGIC INPUTS                                      |                        |                                  |                            |      |                                                                                                                                                                        |

| Input High Voltage, V <sub>INH</sub>              | $0.7 \times V_{DD}$    |                                  |                            | V    |                                                                                                                                                                        |

| Input Low Voltage, V <sub>INL</sub>               |                        |                                  | $0.2 \times V_{\text{DD}}$ | V    |                                                                                                                                                                        |

| Input Current, I <sub>INH</sub> /I <sub>INL</sub> |                        |                                  | ±1                         | μΑ   |                                                                                                                                                                        |

| Input Capacitance, C <sub>IN</sub>                |                        |                                  | 10                         | pF   |                                                                                                                                                                        |

| Control Clock Input                               |                        |                                  | 50                         | MHz  |                                                                                                                                                                        |

| LOGIC OUTPUTS                                     |                        |                                  |                            |      |                                                                                                                                                                        |

| Output High Voltage, V <sub>он</sub>              | $DV_{\text{DD}} - 0.4$ |                                  |                            | V    | І <sub>ОН</sub> = 500 μА                                                                                                                                               |

| Output Low Voltage, Vol                           |                        |                                  | 0.4                        | V    | $I_{OL} = 500 \ \mu A$                                                                                                                                                 |

| CLKOUT Rise/Fall                                  |                        |                                  | 5                          | ns   |                                                                                                                                                                        |

| CLKOUT Load                                       |                        |                                  | 10                         | рF   |                                                                                                                                                                        |

### **GENERAL SPECIFICATIONS**

| Parameter                                 |     | Min Typ Max |     |    | Test Conditions/Comments                                  |

|-------------------------------------------|-----|-------------|-----|----|-----------------------------------------------------------|

| TEMPERATURE RANGE (T <sub>A</sub> )       | -40 | <i>,</i> ,  | +85 | °C |                                                           |

| POWER SUPPLIES                            |     |             |     |    |                                                           |

| Voltage Supply, V <sub>DD</sub>           | 2.3 |             | 3.6 | v  | All VDD pins must be tied together                        |

| TRANSMIT CURRENT CONSUMPTION <sup>1</sup> |     |             |     |    | $V_{DD} = 3.0 \text{ V}$ , PA is matched into 50 $\Omega$ |

| 868 MHz                                   |     |             |     |    | VCO_BIAS = 8                                              |

| 0 dBm                                     |     | 20.2        |     | mA |                                                           |

| 5 dBm                                     |     | 24.7        |     | mA |                                                           |

| 10 dBm                                    |     | 32.3        |     | mA |                                                           |

| 450 MHz, Internal Inductor VCO            |     |             |     |    | $VCO_BIAS = 8$                                            |

| 0 dBm                                     |     | 19.9        |     | mA |                                                           |

| 5 dBm                                     |     | 23.2        |     | mA |                                                           |

| 10 dBm                                    |     | 29.2        |     | mA |                                                           |

| 426 MHz, External Inductor VCO            |     |             |     |    | $VCO_BIAS = 2$                                            |

| 0 dBm                                     |     | 13.5        |     | mA |                                                           |

| 5 dBm                                     |     | 17          |     | mA |                                                           |

| 10 dBm                                    |     | 23.3        |     | mA |                                                           |

| RECEIVE CURRENT CONSUMPTION               |     |             |     |    | $V_{DD} = 3.0 \text{ V}$                                  |

| 868 MHz                                   |     |             |     |    | VCO_BIAS = 8                                              |

| Low Current Mode                          |     | 22.7        |     | mA |                                                           |

| High Sensitivity Mode                     |     | 24.6        |     | mA |                                                           |

| 433MHz, Internal Inductor VCO             |     |             |     |    | VCO_BIAS = 8                                              |

| Low Current Mode                          |     | 24.5        |     | mA |                                                           |

| High Sensitivity Mode                     |     | 26.4        |     | mA |                                                           |

| 426 MHz, External Inductor VCO            |     |             |     |    | $VCO_BIAS = 2$                                            |

| Low Current Mode                          |     | 17.5        |     | mA |                                                           |

| High Sensitivity Mode                     |     | 19.5        |     | mA |                                                           |

| POWER-DOWN CURRENT CONSUMPTION            |     |             |     |    |                                                           |

| Low Power Sleep Mode                      |     | 0.1         | 1   | μA | CE low                                                    |

<sup>1</sup> The transmit current consumption tests used the same combined PA and LNA matching network as that used on the EVAL-ADF7021DB evaluation boards. Improved PA efficiency is achieved by using a separate PA matching network.

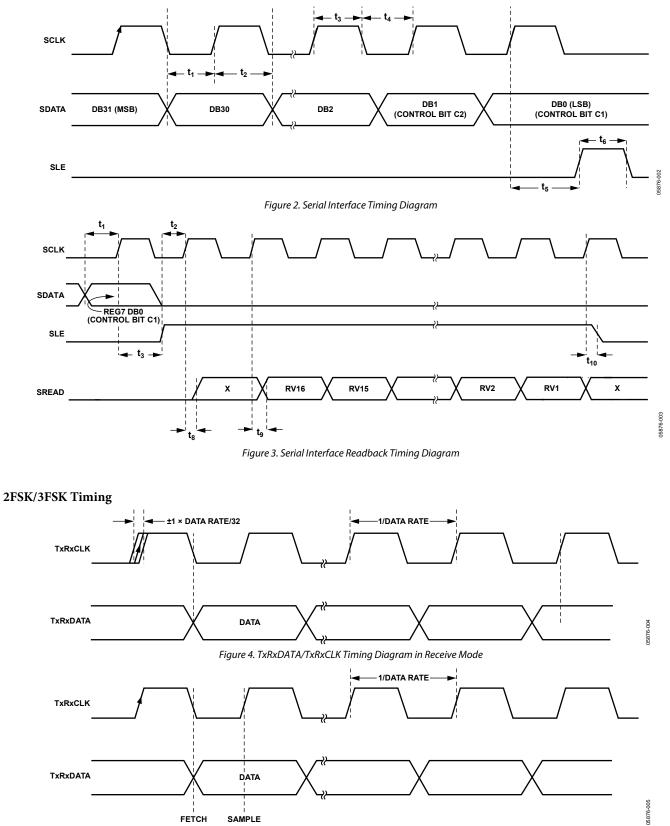

### TIMING CHARACTERISTICS

$V_{DD}$  = 3 V ± 10%, DGND = AGND = 0 V,  $T_A$  = 25°C, unless otherwise noted. Guaranteed by design but not production tested.

| Parameter       | Limit at T <sub>MIN</sub> to T <sub>MAX</sub>             | Unit | Test Conditions/Comments                      |

|-----------------|-----------------------------------------------------------|------|-----------------------------------------------|

| t1              | >10                                                       | ns   | SDATA to SCLK setup time                      |

| t <sub>2</sub>  | >10                                                       | ns   | SDATA to SCLK hold time                       |

| t3              | >25                                                       | ns   | SCLK high duration                            |

| t4              | >25                                                       | ns   | SCLK low duration                             |

| ts              | >10                                                       | ns   | SCLK to SLE setup time                        |

| t <sub>6</sub>  | >20                                                       | ns   | SLE pulse width                               |

| t <sub>8</sub>  | <25                                                       | ns   | SCLK to SREAD data valid, readback            |

| t <sub>9</sub>  | <25                                                       | ns   | SREAD hold time after SCLK, readback          |

| <b>t</b> 10     | >10                                                       | ns   | SCLK to SLE disable time, readback            |

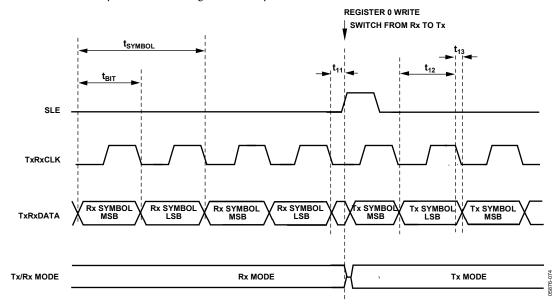

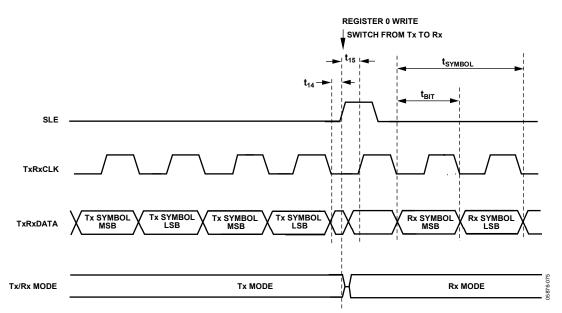

| t <sub>11</sub> | $5 < t_{11} < (\frac{1}{4} \times t_{BIT})$               | ns   | TxRxCLK negative edge to SLE                  |

| t <sub>12</sub> | >5                                                        | ns   | TxRxDATA to TxRxCLK setup time (Tx mode)      |

| <b>t</b> 13     | >5                                                        | ns   | TxRxCLK to TxRxDATA hold time (Tx mode)       |

| t <sub>14</sub> | $>$ <sup>1</sup> / <sub>4</sub> $\times$ t <sub>BIT</sub> | μs   | TxRxCLK negative edge to SLE                  |

| t15             | $> \frac{1}{4} \times t_{BIT}$                            | μs   | SLE positive edge to positive edge of TxRxCLK |

### **Timing Diagrams**

#### Serial Interface

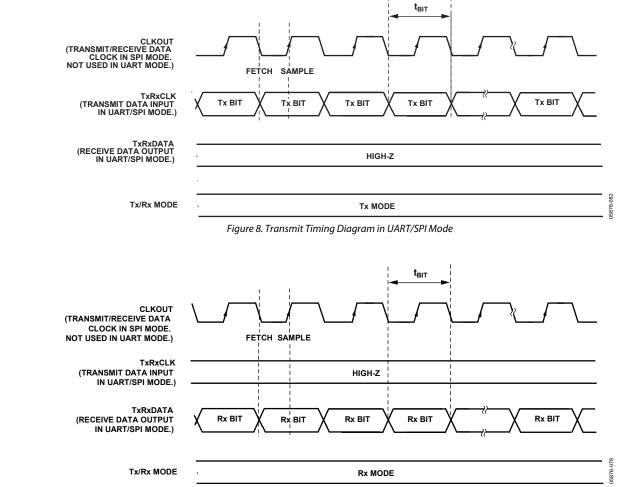

Figure 5. TxRxDATA/TxRxCLK Timing Diagram in Transmit Mode

### **4FSK Timing**

In 4FSK receive mode, MSB/LSB synchronization is guaranteed by SWD in the receive bit stream.

Figure 6. Receive-to-Transmit Timing Diagram in 4FSK Mode

Figure 7. Transmit-to-Receive Timing Diagram in 4FSK Mode

#### **UART/SPI Mode**

UART mode is enabled by setting R0\_DB28 to 1. SPI mode is enabled by setting R0\_DB28 to 1 and setting R15\_DB[17:19] to 0x7. The transmit/receive data clock is available on the CLKOUT pin.

Figure 9. Receive Timing Diagram in UART/SPI Mode

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 7.

| Parameter                           | Rating                               |

|-------------------------------------|--------------------------------------|

| V <sub>DD</sub> to GND <sup>1</sup> | –0.3 V to +5 V                       |

| Analog I/O Voltage to GND           | -0.3 V to AV <sub>DD</sub> + 0.3 V   |

| Digital I/O Voltage to GND          | $-0.3$ V to $DV_{\text{DD}}$ + 0.3 V |

| Operating Temperature Range         |                                      |

| Industrial (B Version)              | -40°C to +85°C                       |

| Storage Temperature Range           | –65°C to +125°C                      |

| Maximum Junction Temperature        | 150°C                                |

| MLF $\theta_{JA}$ Thermal Impedance | 26°C/W                               |

| Reflow Soldering                    |                                      |

| Peak Temperature                    | 260°C                                |

| Time at Peak Temperature            | 40 sec                               |

$^{1}$  GND = CPGND = RFGND = DGND = AGND = 0 V.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

This device is a high performance RF integrated circuit with an ESD rating of <2 kV and it is ESD sensitive. Take proper precautions for handling and assembly.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

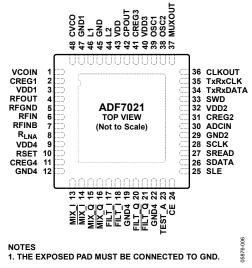

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### **Table 8. Pin Function Descriptions**

| Pin No.    | Mnemonic                                                | Description                                                                                                                                                                                                              |

|------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VCOIN                                                   | Regulator Voltage for PA Block and VCO Cores. The tuning voltage on this pin determines the output frequency of the voltage controlled oscillator (VCO). The higher the tuning voltage, the higher the output frequency. |

| 2          | CREG1                                                   | Regulator Voltage for PA Block. Place a series 3.9 $\Omega$ resistor and a 100 nF capacitor between this pin and ground for regulator stability and noise rejection.                                                     |

| 3          | VDD1                                                    | Voltage Supply for PA Block and VCO Cores. Place decoupling capacitors of 0.1 $\mu$ F and 100 pF as close as possible to this pin. Tie all VDD pins together.                                                            |

| 4          | RFOUT                                                   | The modulated signal is available at this pin. Output power levels are from –16 dBm to +13 dBm. Impedance match the output to the desired load using suitable components (see the Transmitter section).                  |

| 5          | RFGND                                                   | Ground for Output Stage of Transmitter. Tie all GND pins together.                                                                                                                                                       |

| 6          | RFIN                                                    | LNA Input for Receiver Section. Input matching is required between the antenna and the differential LNA input to ensure maximum power transfer (see the LNA/PA Matching section).                                        |

| 7          | RFINB                                                   | Complementary LNA Input (see the LNA/PA Matching section).                                                                                                                                                               |

| 8          | R <sub>LNA</sub>                                        | External Bias Resistor for LNA. Optimum resistor is 1.1 k $\Omega$ with 5% tolerance.                                                                                                                                    |

| 9          | VDD4                                                    | Voltage Supply for LNA/MIXER Block. Decouple this pin to ground with a 10 nF capacitor.                                                                                                                                  |

| 10         | RSET                                                    | External Resistor. Sets charge pump current and some internal bias currents. Use a 3.6 k $\Omega$ resistor with 5% tolerance.                                                                                            |

| 11         | CREG4                                                   | Regulator Voltage for LNA/MIXER Block. Place a 100 nF capacitor between this pin and GND for regulator stability and noise rejection.                                                                                    |

| 12, 19, 22 | GND4                                                    | Ground for LNA/MIXER Block.                                                                                                                                                                                              |

| 13 to 18   | MIX_I, <u>MIX_I,</u><br>MIX_Q, MIX_Q,<br>FILT_I, FILT_I | Signal Chain Test Pins. These pins are high impedance under normal conditions; leave the pins unconnected.                                                                                                               |

| 20, 21, 23 | FILT_Q, FILT_Q,<br>TEST_A                               | Signal Chain Test Pins. These pins are high impedance under normal conditions; leave the pins unconnected.                                                                                                               |

| 24         | CE                                                      | Chip Enable. Bringing CE low puts the ADF7021 into complete power-down. Register values are lost when CE is low, and the device must be reprogrammed once CE is brought high.                                            |

| 25         | SLE                                                     | Load Enable, CMOS Input. When SLE goes high, the data stored in the shift registers is loaded into one of the four latches. A latch is selected using the control bits.                                                  |

| 26         | SDATA                                                   | Serial Data Input. The serial data is loaded MSB first with the 4 LSBs as the control bits. This pin is a high impedance CMOS input.                                                                                     |

| 27         | SREAD                                                   | Serial Data Output. This pin is used to feed readback data from the ADF7021 to the microcontroller. The SCLK input is used to clock each readback bit (for example, AFC or ADC) from the SREAD pin.                      |

| 28         | SCLK                                                    | Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched into the 32-bit shift register on the CLK rising edge. This pin is a digital CMOS input.                 |

ADF7021

| Pin No. | Mnemonic  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29      | GND2      | Ground for Digital Section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 30      | ADCIN     | Analog-to-Digital Converter Input. The internal 7-bit ADC can be accessed through this pin. Full scale is 0 V to 1.9 V. Readback is made using the SREAD pin.                                                                                                                                                                                                                                                                                                                                                                               |

| 31      | CREG2     | Regulator Voltage for Digital Block. Place a 100 nF capacitor between this pin and ground for regulator stability and noise rejection.                                                                                                                                                                                                                                                                                                                                                                                                      |

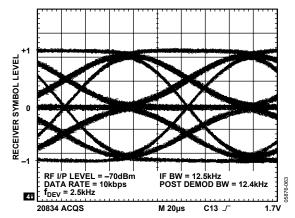

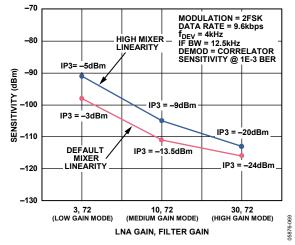

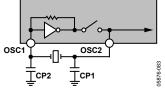

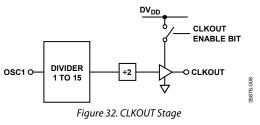

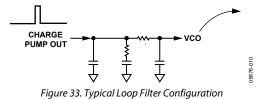

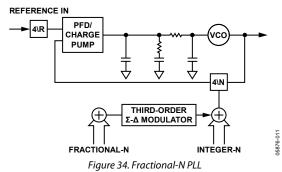

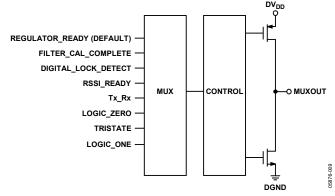

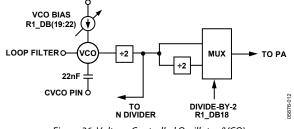

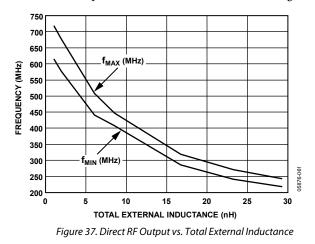

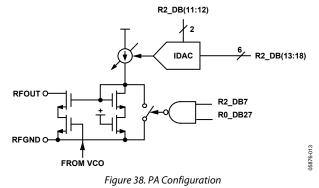

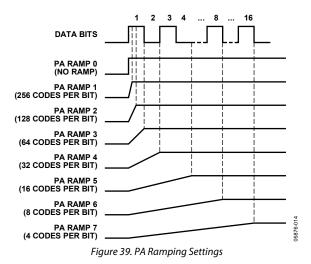

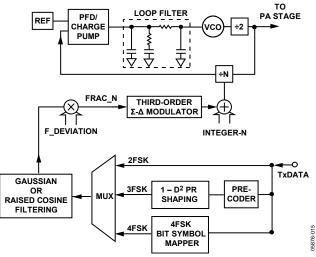

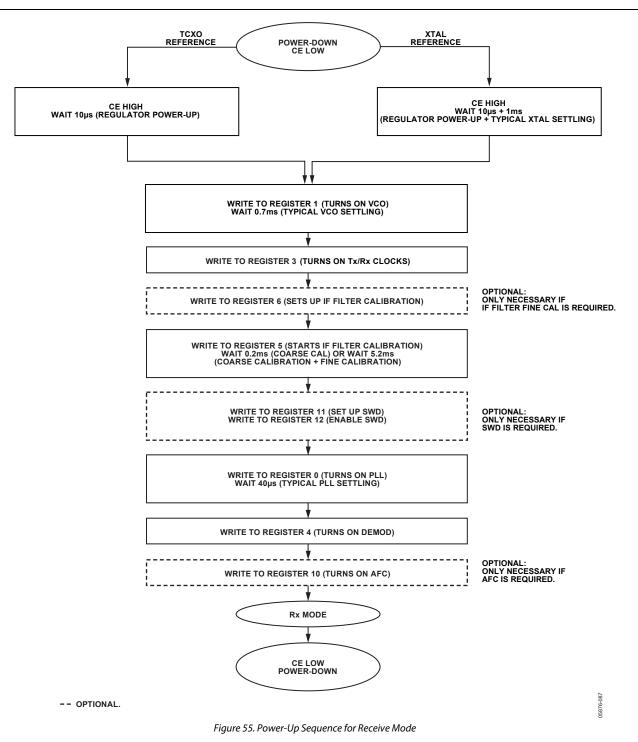

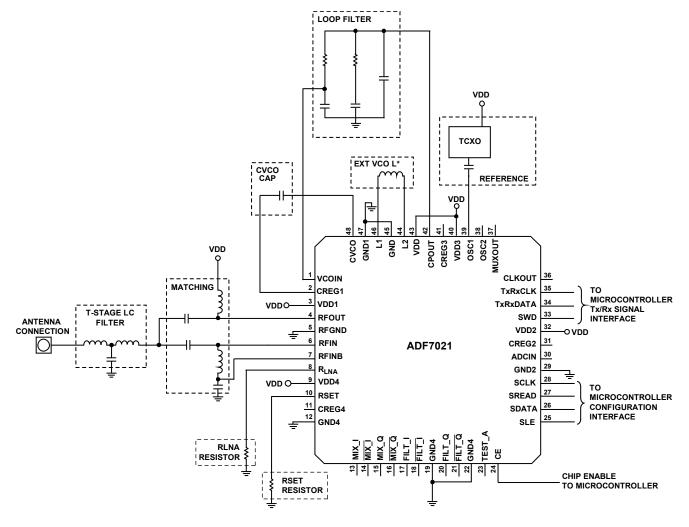

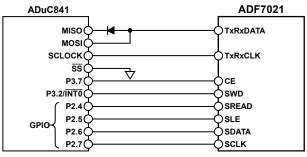

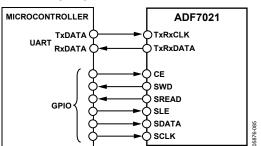

| 32      | VDD2      | Voltage Supply for Digital Block. Place a decoupling capacitor of 10 nF as close as possible to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                   |