#### **Features**

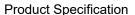

- 192 macrocells in 12 Logic Array Blocks (LABs)

- Eight dedicated inputs, 64 bidirectional I/O pins

- Programmable interconnect array

- Advanced 0.65-micron CMOS technology to increase performance

- Parametric compatibility with the 5962-92062 SMD

- 384 expander product terms

- Processing in accordance with MIL-PRF-38535 Class Q

- Available in the 84-pin Ceramic PGA package

## **Functional Description**

The TD7C341B is an Erasable Programmable Logic Device (EPLD) which uses CMOS EPROM cells to configure logic functions within the device. The architecture is 100% userconfigurable, allowing the devices to accommodate independent logic functions in a variety of ways.

The 192 macrocells in the TD7C341B are divided into 12 Logic Array Blocks (LABs), 16 per LAB. With 32 per LAB, there are 384 expander product terms to be used and shared by the macrocells within each LAB.

Each LAB features being interconnected with a programmable interconnect array. The architecture allows signals to be routed throughout the chip.

The speed and density of the TD7C341B supports a wide range of applications, from replacement of large amounts of 5400-series TTL logic, to complex controllers and multifunction chips. With 37 times the functionality of 20-pin PLDs, the TD7C341B allows the replacement of over 75 TTL-logic devices reducing board space, part count, and increasing system reliability.

Each LAB contains 16 macrocells. In LABs A, F, G, and L, 8 macrocells are connected to I/O pins and eight are buried, while for LABs B, C, D, E, H, I, J, and K, four macrocells are connected to I/O pins and 12 are buried. Moreover, in addition to the I/O and buried macrocells, there are 32 single product term logic expanders in each LAB. This results in an enhanced capability of the macrocells without the accompanying increase in the number of product terms in each macrocell.

#### Selection Guide

|                     | TD7C341B-30 |

|---------------------|-------------|

| Maximum Access Time | 30 ns       |

# **Logic Block Diagram**

FIGURE 1. TD7C341B Logic Block Diagram

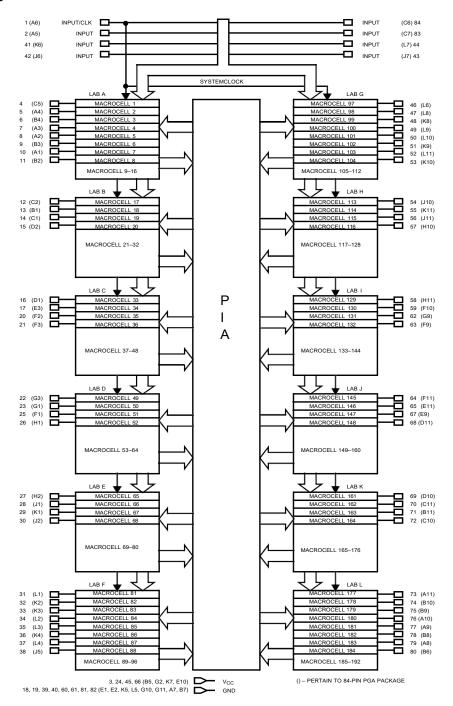

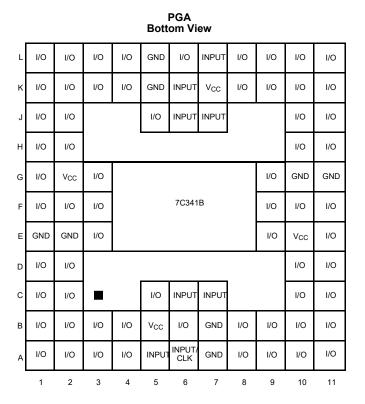

# **Pin Configurations**

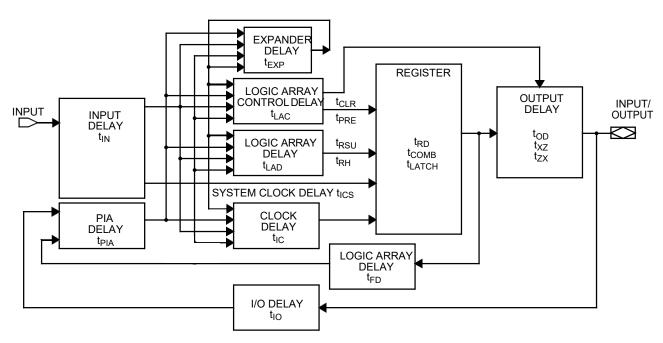

FIGURE 2. TD7C341B Internal Timing Model

# **Logic Array Blocks**

There are 12 logic array blocks in the TD7C341B. Each LAB consists of a macrocell array containing 16 macrocells, an expander product term array containing 32 expanders, and an I/O block. The LAB is fed by the programmable interconnect array and the dedicated input bus. All macrocell feedbacks go to the macrocell array, the expander array, and the programmable interconnect array. Expanders feed themselves and the macrocell array. All I/O feedbacks go to the programmable interconnect array so that they may be accessed by macrocells in other LABs as well as the macrocells in the LAB in which they are situated.

Externally, the TD7C341B provides eight dedicated inputs, one of which may be used as a system clock. There are 64 I/O pins that may be individually configured for input, output, or bidirectional data flow.

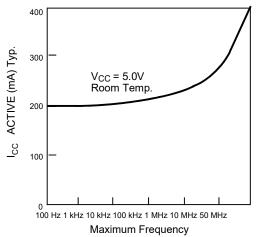

Typical I<sub>CC</sub> vs. f<sub>MAX</sub>

### **Programmable Interconnect Array**

The Programmable Interconnect Array (PIA) solves interconnect limitations by routing only the signals needed by each logic array block. The inputs to the PIA are the outputs of every macrocell within the device and the I/O pin feedback of every pin on the device.

Unlike masked or programmable gate arrays, which induce variable delay dependent on routing, the PIA has a fixed delay. This eliminates undesired skews among logic signals, which may cause glitches in internal or external logic. The fixed delay, regardless of programmable interconnect array configuration, simplifies design by assuring that internal signal skews or races are avoided. The result is ease of design implementation, often in a single pass, without the multiple internal

logic placement and routing iterations required for a programmable gate array to achieve design timing objectives.

#### **Design Recommendations**

For proper operation, input and output pins must be constrained to the range GND  $\leq$  (VIN or VOUT)  $\leq$  VCC. Unused inputs must always be tied to an appropriate logic level (either VCC or GND). Each set of VCC and GND pins must be connected together directly at the device. Power supply decoupling capacitors of at least 0.2 mF must be connected between VCC and GND. For the most effective decoupling, each VCC pin should be separately decoupled to GND, directly at the device. Decoupling capacitors should have good frequency response, such as monolithic ceramic types.

### **Design Security**

The TD7C341B contains a programmable design security feature that controls the access to the data programmed into the device. If this programmable feature is used, a proprietary design implemented in the device cannot be copied or retrieved. This enables a high level of design control to be obtained since programmed data within EPROM cells is invisible. The bit that controls this function, along with all other program data, may be reset simply by erasing the device.

The TD7C341B is fully functionally tested and guaranteed through complete testing of each programmable EPROM bit and all internal logic elements thus ensuring 100% programming yield.

The erasable nature of these devices allows test programs to be used and erased during early stages of the production flow. The devices also contain on-board logic test circuitry to allow verification of function and AC specification once encapsulated in non-windowed packages.

# **Ordering Information**

| Speed<br>(ns) | Ordering Code  | Package Letter<br>Designator | Package Type                            | Operating Range<br>Tcase |  |

|---------------|----------------|------------------------------|-----------------------------------------|--------------------------|--|

| 30            | TD7C341B-30RMB | R                            | 84-lead Windowed Ceramic Pin Grid Array | -55 °C to +125 °C        |  |

## 1. SCOPE

1.1 **Device type(s)**. The device type(s) identify the circuit function as follows:

Part Number Generic number 1/ Circuit function Propagation delay time

TD7C341B-30RMB 7C341B 192 Macrocell EPLD 30 ns

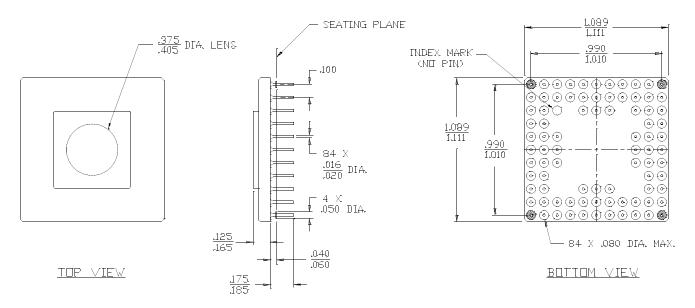

1.2 **Case outlines**. The case outline is designated in Figure 8 and as follows:

<u>Package Letter Designator</u> <u>Descriptive designator</u> <u>Terminals</u>

R Ceramic Windowed Pin Grid Array 84-Lead 2

1.2.1 **Lead finish**. The lead finish is as specified in MIL-PRF-38535 for device classes Q.

## 1.3 Absolute maximum ratings. 3/

| Supply voltage range (V <sub>CC</sub> )                                             | 2.0 V dc to +7.0 V dc <u>4</u> /<br>2.5 W <u>5</u> / |

|-------------------------------------------------------------------------------------|------------------------------------------------------|

| Thermal resistance, junction-to-case $(\theta_{JC})$ :<br>Case outlines X, Y, and Z | +175 °C                                              |

| Storage temperature range Temperature under bias range                              |                                                      |

| Endurance Data retention                                                            |                                                      |

# 1.4 Recommended operating conditions.

| Supply voltage range (V <sub>CC</sub> )            |                             |

|----------------------------------------------------|-----------------------------|

| Ground voltage (GND)                               | - 0 V dc                    |

| Input high voltage (V <sub>IH</sub> )              | · 2.2 V dc minimum          |

| Input low voltage (V <sub>IL</sub> )               | · 0.8 V dc maximum          |

| Case operating temperature range (T <sub>C</sub> ) | 55 °C to +125 °C <u>6</u> / |

| Input rise time (t <sub>R</sub> )                  | 100 ns maximum              |

| Input fall time (t <sub>F</sub> )                  | 100 ns maximum              |

<sup>1/</sup> As defined

<sup>2/</sup> Lid shall be transparent to permit ultraviolet light erasure.

<sup>3/</sup> Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

<sup>4/</sup> Minimum dc input voltage is -0.3 V. During transitions, inputs may undershoot to -2.0 V for periods less than 20 ns. Maximum dc voltage on output pins is V<sub>CC</sub> + 0.3 V, which may overshoot to +7.0 V for periods less than 20 ns under no load conditions.

<sup>5/</sup> Must withstand the added P<sub>D</sub> due to short circuit test (e.g., I<sub>SC</sub>).

<sup>&</sup>lt;u>6</u>/ Case temperatures are instant on.

#### 2. REQUIREMENTS

- 2.1 <u>Case outlines</u>. The case outlines shall be in accordance with the Package Diagram herein.

- 2.2 **Terminal connections**. The terminal connections shall be as specified on figure 3. 2.3

- 2.3 **Truth table**. The truth table shall be as specified on figure 4.

- 2.4 **Unprogrammed devices**. The truth table for unprogrammed devices for contracts involving no altered item drawing shall be as specified on figure 4. When required in screening or qualification conformance inspection groups A, B, C, or D, the devices shall be programmed by the manufacturer prior to test. A minimum of 50 percent of the total number of gates shall be programmed or at least 25 percent of the total number of gates to any altered item drawing.

- 2.5 **Programmed devices**. The truth table for programmed devices shall be as specified by an attached altered item drawing.

- 2.6 **Electrical performance characteristics**. Unless otherwise specified herein, the electrical performance characteristics parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 2.7 Electrical test requirements. The electrical tests for each subgroup are defined in table I.

- 2.8 **Erasure of EPLDs**. The recommended erasure procedure is exposure to shortwave ultraviolet light which has a wavelength of 2537 angstroms (Å). The integrated dose (i.e., ultraviolet intensity x exposure time) for erasure should be a minimum of fifteen (15) Ws/cm². The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with a 1200  $\mu$ W/cm² power rating. The device should be placed within one inch of the lamp tubes during erasure. The maximum integrated dose the device can be exposed to without damage is 7258 Ws/cm2 (1 week at 12,000  $\mu$ W/cm²). Exposure of the device to high intensity ultraviolet light for long periods may cause permanent damage.

- 2.9 **Programmability of EPLDs**. The programming procedures shall be as specified by the device manufacturer of the die.

Document #: TD7C341B-04-2020 Rev-

# TABLE I. Electrical performance characteristics

| Test                                                                                          | Symbol           | Conditions $-55 \text{ °C} \le T_C \le +125 \text{ °C}$                                              | Group A subgroups | Lir | mits | Unit |

|-----------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------|-------------------|-----|------|------|

|                                                                                               |                  | $4.5 \text{ V} \le \text{V}_{\text{CC}} \le 5.5 \text{ V}$ unless otherwise specified                |                   | Min | Max  |      |

| Output high voltage                                                                           | V <sub>OH</sub>  | V <sub>CC</sub> = 4.5 V, I <sub>OH</sub> = -4 mA<br>V <sub>IH</sub> = 2.2 V, V <sub>IL</sub> = 0.8 V | 1,2,3             | 2.4 |      | ٧    |

| Output low voltage                                                                            | V <sub>OL</sub>  | V <sub>CC</sub> = 4.5 V, I <sub>OL</sub> = 8 mA<br>V <sub>IH</sub> = 2.2 V, V <sub>IL</sub> = 0.8 V  |                   |     | 0.45 |      |

| Input high voltage <u>1</u> / <u>2</u> /                                                      | V <sub>IH</sub>  |                                                                                                      |                   | 2.2 |      |      |

| Input low voltage <u>1</u> / <u>2</u> /                                                       | VIL              |                                                                                                      |                   |     | 0.8  |      |

| Input leakage current                                                                         | I <sub>IX</sub>  | V <sub>CC</sub> = 5.5 V,<br>V <sub>IN</sub> = 5.5 V and GND                                          |                   | -10 | +10  | μA   |

| Output leakage current                                                                        | l <sub>OZ</sub>  | V <sub>CC</sub> = 5.5 V,<br>V <sub>IN</sub> = 5.5 V and GND                                          |                   | -40 | +40  |      |

| Output short circuit current 3/4/                                                             | I <sub>SC</sub>  | $V_{CC} = 5.5 \text{ V}, V_{OUT} = 0.5 \text{ V}$                                                    | ] [               | -30 | -90  | mA   |

| Power supply current 4/ 5/                                                                    | I <sub>CC1</sub> | $V_{CC}$ = 5.5 V, $I_{OUT}$ = 0 mA,<br>$V_{IN}$ = $V_{CC}$ or GND<br>f = 1.0 MHz                     |                   |     | 480  |      |

| Power supply current (standby)                                                                | I <sub>CC2</sub> | $V_{CC}$ = 5.5 V, $I_{OUT}$ = 0 mA,<br>$V_{IN}$ = $V_{CC}$ or GND                                    |                   |     | 435  |      |

| Input capacitance <u>2</u> /                                                                  | C <sub>IN</sub>  | $V_{CC} = 5.0 \text{ V},$<br>$T_A = +25 ^{\circ}\text{C}, f = 1 \text{ MHz},$<br>(see 4.4.1f)        | 4                 |     | 10   | pF   |

| Output capacitance <u>2</u> /                                                                 | C <sub>OUT</sub> | $V_{CC} = 5.0 \text{ V},$ $T_A = +25 ^{\circ}\text{C}, f = 1 \text{ MHz},$ (see 4.4.1f)              | 4                 |     | 20   |      |

| Functional testing                                                                            |                  | See 4.4.1c                                                                                           | 7, 8A, 8B         |     |      |      |

| Dedicated input to combinatorial output delay 7/                                              | t <sub>PD1</sub> | See figures 3 (circuit A) and 4 6/                                                                   | 9, 10, 11         |     | 30   | ns   |

| I/O input to combinatorial output delay <u>8</u> /                                            | t <sub>PD2</sub> |                                                                                                      |                   |     | 45   |      |

| Dedicated input to combinatorial output delay with expander delay 9/                          | t <sub>PD3</sub> |                                                                                                      |                   |     | 44   |      |

| I/O input to combinatorial output delay with expander delay <u>2</u> / <u>4</u> / <u>10</u> / | t <sub>PD4</sub> |                                                                                                      |                   |     | 59   |      |

| Input to output enable delay 4/ 7/                                                            | t <sub>EA</sub>  |                                                                                                      |                   |     | 30   |      |

## TABLE I. <u>Electrical performance characteristics</u> - Continued

| Test                                                                     | Symbol           | Conditions<br>$-55 ^{\circ}\text{C} \le T_{\text{C}} \le +125 ^{\circ}\text{C}$<br>$4.5 \text{V} \le \text{V}_{\text{CC}} \le 5.5 \text{V}$ | Group A subgroups | Lir | nits | Unit |

|--------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|------|------|

|                                                                          |                  | unless otherwise specified                                                                                                                  |                   | Min | Max  |      |

| Input to output disable delay 4/ 7/                                      | t <sub>ER</sub>  | See figures 3 (circuit B) and 4 6/                                                                                                          | 9,10,11           |     | 30   | ns   |

| Synchronous clock input to output delay                                  | t <sub>CO1</sub> | See figures 3 (circuit A) and 4 6/                                                                                                          |                   |     | 35   |      |

| Dedicated input or feedback setup time to synchronous clock input 7/ 12/ | t <sub>S1</sub>  | See figures 3 (circuit A) and 4 6/                                                                                                          |                   | 20  |      |      |

| I/O input setup time to synchronous clock input 4/ 7/ 12/                | t <sub>S2</sub>  |                                                                                                                                             |                   | 39  |      |      |

| Input hold time from synchronous clock input <u>7</u> /                  | t <sub>H</sub>   |                                                                                                                                             |                   | 0   |      |      |

| Synchronous clock input high time <u>2</u> /                             | t <sub>WH</sub>  |                                                                                                                                             |                   | 10  |      |      |

| Synchronous clock input low time 2/                                      | t <sub>WL</sub>  |                                                                                                                                             |                   | 10  |      |      |

| Asynchronous clear width 2/ 4/ 7/                                        | t <sub>RW</sub>  |                                                                                                                                             |                   | 30  |      |      |

| Asynchronous clear recovery time 2/ 4/ 7/                                | t <sub>RR</sub>  |                                                                                                                                             |                   | 30  |      |      |

| Asynchronous clear to registered output delay 2/ 7/                      | t <sub>RO</sub>  |                                                                                                                                             |                   |     | 30   |      |

TABLE I. <u>Electrical performance characteristics</u> – Continued

| Test                                                                                                                                       | Symbol            | -55 °C ≤ T <sub>C</sub> ≤ +125 °C<br>4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V | Group A subgroups | Liı  | mits | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------|-------------------|------|------|------|

|                                                                                                                                            |                   | unless otherwise specified                                           |                   | Min  | Max  |      |

| Asynchronous preset width 2/ 4/ 7/                                                                                                         | t <sub>PW</sub>   | See figures 3 (circuit A) and 4 6/                                   | 9, 10, 11         | 30   |      | ns   |

| Asynchronous preset to registered output delay 2/ 7/                                                                                       | t <sub>PO</sub>   |                                                                      |                   |      | 30   |      |

| Synchronous clock to local feedback input 4/ 13/                                                                                           | t <sub>CF</sub>   |                                                                      |                   |      | 3    |      |

| External synchronous clock period (1/ <sub>fMAX3</sub> ) <u>4</u> /                                                                        | t <sub>P</sub>    |                                                                      |                   | 20   |      |      |

| External feedback maximum frequency (1/(t <sub>CO1</sub> + t <sub>S1</sub> )) <u>4</u> / <u>14</u> /                                       | f <sub>MAX1</sub> |                                                                      |                   | 27.7 |      | MHz  |

| Internal local feedback maximum frequency, lesser of (1/(t <sub>S1</sub> + t <sub>CF</sub> )) or (1/t <sub>CO1</sub> ) 4/ 15/              | f <sub>MAX2</sub> |                                                                      |                   | 43   |      |      |

| Data path maximum frequency, least of $1/(t_{WL} + t_{WH})$ , $1/(t_{S1} + t_{H})$ or $(1/(t_{WL} + t_{WH}) \underline{4}/\underline{16}/$ | f <sub>MAX3</sub> |                                                                      |                   | 50   |      |      |

| Maximum register toggle frequency (1/(t <sub>W</sub> L + t <sub>WH</sub> )) <u>4</u> / <u>17</u> /                                         | f <sub>MAX4</sub> |                                                                      |                   | 50   |      |      |

| Output data stable time from synchronous clock input 4/ 18/                                                                                | t <sub>OH</sub>   |                                                                      |                   | 3    |      | ns   |

| External asynchronous switchir                                                                                                             | ng charac         | teristics                                                            |                   |      |      |      |

| Dedicated asynchronous clock input to output delay <u>6</u> /                                                                              | t <sub>ACO1</sub> | See figures 3 (circuit A) and 4 6/                                   | 9, 10, 11         |      | 30   | ns   |

| Asynchronous clock input to local feedback to combinatorial output 2/ 19/                                                                  | t <sub>ACO2</sub> |                                                                      |                   |      | 46   |      |

TABLE I. <u>Electrical performance characteristics</u> – Continued

| Test                                                                                                                      | Symbol             | $ \begin{array}{c c} \text{Conditions} & \text{Group A} \\ -55  ^{\circ}\text{C} \leq \text{T}_{\text{C}} \leq +125  ^{\circ}\text{C} & \text{subgroups} \\ 4.5  \text{V} \leq \text{V}_{\text{CC}} \leq 5.5  \text{V} & \text{unless otherwise specified} \\ \end{array} $ |           | Lir  | nits | Unit |

|---------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|------|------|

|                                                                                                                           |                    |                                                                                                                                                                                                                                                                             |           | Min  | Max  |      |

| Dedicated input or feedback setup time to asynchronous clock input <u>6</u> /                                             | t <sub>AS1</sub>   | See figures 3 (circuit A) and 4 6/                                                                                                                                                                                                                                          | 9, 10, 11 | 6    |      | ns   |

| I/O input setup time to asynchronous clock input 4/ 6/                                                                    | t <sub>AS2</sub>   |                                                                                                                                                                                                                                                                             |           | 27   |      |      |

| Input hold time from asynchronous clock input <u>6</u> /                                                                  | t <sub>AH</sub>    |                                                                                                                                                                                                                                                                             |           | 8    |      |      |

| Asynchronous clock input high time <u>2</u> / <u>6</u> /                                                                  | t <sub>AWH</sub>   |                                                                                                                                                                                                                                                                             |           | 14   |      |      |

| Asynchronous clock input low time <u>2</u> / <u>7</u> / <u>20</u> /                                                       | t <sub>AWL</sub>   |                                                                                                                                                                                                                                                                             |           | 11   |      |      |

| Asynchronous clock to local feedback input <u>4</u> / <u>21</u> /                                                         | t <sub>ACF</sub>   |                                                                                                                                                                                                                                                                             |           |      | 18   |      |

| External asynchronous clock period (1/f <sub>MAXA4</sub> ) <u>4</u> /                                                     | t <sub>AP</sub>    |                                                                                                                                                                                                                                                                             |           | 25   |      |      |

| External feedback maximum frequency in asynchronous mode 1/(t <sub>ACO1</sub> + t <sub>AS1</sub> ) <u>4</u> / <u>22</u> / | f <sub>MAXA1</sub> |                                                                                                                                                                                                                                                                             |           | 27   |      | MHz  |

| Maximum internal asynchronous frequency <u>4</u> / <u>23</u> /                                                            | f <sub>MAXA2</sub> |                                                                                                                                                                                                                                                                             |           | 40   |      |      |

| Data path frequency in asynchronous mode <u>4</u> / <u>24</u> /                                                           | f <sub>MAXA3</sub> |                                                                                                                                                                                                                                                                             |           | 33.3 |      |      |

| TABLE I. Electrical I | performance | characteristics - | Continued |

|-----------------------|-------------|-------------------|-----------|

|-----------------------|-------------|-------------------|-----------|

| Test                                                                                                           | Symbol             | Conditions<br>-55 °C $\leq$ T <sub>C</sub> $\leq$ +125 °C<br>4.5 V $\leq$ V <sub>CC</sub> $\leq$ 5.5 V | Group A subgroups | Lir | nits | Unit |

|----------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------|-------------------|-----|------|------|

|                                                                                                                |                    | unless otherwise specified                                                                             |                   | Min | Max  |      |

| Maximum asynchronous register toggle frequency 1/(t <sub>AWH</sub> + t <sub>AWL</sub> ) <u>4</u> / <u>25</u> / | f <sub>MAXA4</sub> | See figures 3 (circuit A) and 4 6/                                                                     | 9, 10, 11         | 40  |      | MHz  |

| Output data stable time from asynchronous clock input 4/ 26/                                                   | t <sub>AOH</sub>   |                                                                                                        |                   | 15  |      | ns   |

- 1/ These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

- 2/ Tested initially and after any design or process changes that affect that parameter, and therefore shall be guaranteed to the limits specified in table I.

- 3/ For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 1 second.

- 4/ May not be tested but shall be guaranteed to the limits specified in table I.

- Measured with device programmed as a 16-bit counter in each LAB.

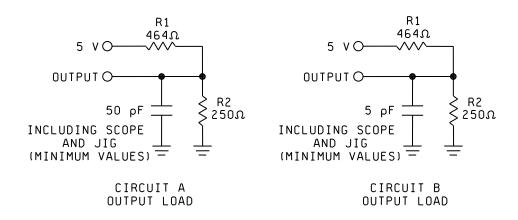

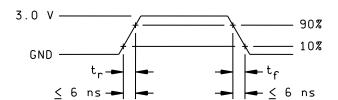

- 6/ AC tests are performed with input rise and fall times of 6 ns or less, timing reference levels of 1.5 V, input pulse levels of 0 to 3.0 V, and the output loads on figure 5.

- This specification is a measure of the delay from input signal applied to a dedicated input to combinatorial output on any output pin. This delay assumes no expander terms are used to form the logic function. When this note is applied to any parameter specification it indicates that the signal (data, asynchronous clock, asynchronous clear, and/or asynchronous preset) is applied to a dedicated input only and no signal path (either clock or data) employs expander logic. If an input signal is applied to an I/O pin, an additional delay equal to t<sub>PIA</sub> should be added to the comparable delay for a dedicated input. If expanders are used, add the maximum expander delay t<sub>EXP</sub> to the overall delay for the comparable delay for a dedicated input.

- 8/ This specification is a measure of the delay from an input signal applied to an I/O macrocell pin to any output. This delay assumes no expander terms are used to form the logic function.

- 9/ This specification is a measure of the delay from an input signal applied to a dedicated input to combinatorial output on any output pin. This delay assumes expander terms are used to form the logic function and includes the worst-case expander logic delay for one pass through the expander logic.

- 10/ This specification is a measure of the delay from an input signal applied to an I/O macrocell pin to any output. This delay assumes expander terms are used to form the logic function and includes the worst-case expander logic delay for one pass through the expander logic.

- 11/ This specification is a measure of the delay from synchronous register clock to internal feedback of the register output signal to the input of the LAB logic array and then to a combinatorial output. This delay assumes no expanders are used, register is synchronously clocked and all feedback is within the same LAB.

- 12/ If data is applied to an I/O input for capture by a macrocell register, the I/O pin set-up time minimums should be observed. These parameters are t<sub>AS2</sub> for synchronous operation and t<sub>AS2</sub> for asynchronous operation.

- 13/ This specification is a measure of the delay associated with the internal register feedback path. This is the delay from synchronous state machine configuration. This delay is for feedback within the same LAB.

- 14/ This specification indicates the guaranteed maximum frequency, in synchronous mode, at which a state machine configuration with external feedback can operate. It is assumed that all data inputs and feedback signals are applied to dedicated inputs. All feedback is assumed to be local, originating within the same LAB.

- 15/ This specification indicates the guaranteed maximum frequency at which a state machine, with internal-only feedback, can operate. If register output states must also control external points, this frequency can still be observed as long as this frequency is less than 1/tco1.

- 16/ This frequency indicates the maximum frequency at which the device may operate in data path mode. This delay assumes data input signals are applied to dedicated inputs and no expander logic is used. If any of the data inputs are I/O pins, t<sub>S2</sub> is the appropriate t<sub>S</sub> for calculation.

- 17/ This specification indicates the guaranteed maximum frequency, in synchronous mode, at which an individual output or buried register can be cycled by a clock signal applied to the dedicated clock input pin.

- 18/ This parameter indicates the minimum time after a maximum time after synchronous register clock input that the previous register output data is maintained on the output pin.

#### TABLE I. Electrical performance characteristics - Continued

- 19/ This specification is a measure of the delay from an asynchronous register clock input to internal feedback of the register output signal to the input of the LAB logic array and then to a combinatorial output. This delay assumes no expanders are used in the logic of combinatorial output or the asynchronous clock input. The clock signal is applied to a dedicated input pin and all feedback is within a single LAB.

- 20/ This parameter is measured with a positive-edge triggered clock at the register. For negative edge triggering, the t<sub>AWH</sub> and t<sub>AWL</sub> parameters must be swapped. If a given input is used to clock multiple registers with both positive and negative polarity, t<sub>AWH</sub> should be used for both t<sub>AWH</sub> and t<sub>AWL</sub>.

- 21/ This specification is a measure of the input delay associated with the internal register feedback path for an asynchronous clock to LAB logic array input. This delay plus the asynchronous register set-up time, t<sub>AS1</sub>, is the minimum internal period for an internal asynchronous clocked state machine configuration. This delay is for feedback within the same LAB, assumes no expander logic in the clock path, and assumes that the clock input signal is applied to a dedicated input pin.

- 22/ This specification indicates the guaranteed maximum frequency at which an asynchronously clocked state machine configuration with external feedback can operate. It is assumed that all data inputs, clock inputs, and feedback signals are applied to dedicated inputs, and that no expander logic is employed in the clock signal path or data path.

- 23/ This specification indicates the guaranteed maximum frequency at which an asynchronously clocked state machine with internal-only feedback can operate. This parameter is determined by the lesser of (1/(t<sub>ACF</sub> + 1/t<sub>AS1</sub>)) or (1/(t<sub>AWH</sub> + t<sub>AWL</sub>)). If register output states must also control external points, this frequency can still be observed as long as this frequency is less than 1/t<sub>ACO1</sub>.

- 24/ This frequency is the maximum frequency at which the device may operate in the asynchronously clocked data path mode. This specification is determined by the least of 1/(t<sub>AWH</sub> + t<sub>AWL</sub>),1/(t<sub>AS1</sub> + t<sub>AH</sub>) or 1/t<sub>ACO1</sub>. It assumes data and clock input signals are applied to dedicated input pins and no expander logic is used.

- 25/ This specification indicates the guaranteed maximum frequency at which an individual output or buried register can be cycled in asynchronously clocked mode by a clock signal applied to an external dedicated input pin.

- 26/ This parameter indicates the minimum time that the previous register output data is maintained on the output after an asynchronous register clock input applied to an external dedicated input pin.

### TD7C341B: CY7C341 Replacement System Design Considerations

The TD7C341B was developed as a process miniaturization of the Cypress CY7C341. The differences between die revisions may manifest with differences in performance. The Cypress CY7C341B device is 0.65-micron shrink of the original 0.8-micron CY7C341. This system design consideration guideline is provided so that system design engineers can evaluate their system in replacing the CY7C341 with the TD7C341B given a known performance difference.

During the qualification of the TD7C341B, it was observed that Vcc Power Up delay times between the two devices were different. Further testing indicated that the TD7C341B Vcc Power Up delay has a cold temperature dependence as shown in Table 1. In particular, the Vcc Power Up delay time increased from ~190  $\mu$ s at room temperature to 115 ms at cold temperature (Tambient = -55 °C). Further testing indicated that the TD7C341B begins exhibiting this longer power up delay time at Tambient =  $\sim -35$  °C. Testing of CY7C341 indicated that there was no cold temperature dependence on the Power Up delay time measurements.

| Device Under Test | T <sub>ambient</sub> = 25 °C | T <sub>ambient</sub> = -55 °C |

|-------------------|------------------------------|-------------------------------|

| CY7C341           | 95 µs                        | 96 µs                         |

| TD7C341B          | 190 µs                       | 114.6 ms                      |

**TABLE 2: Vcc Power Up Delay Time Comparison**

The system impact of this longer Vcc Power Up delay time requires system level knowledge as it relates to the Vcc power regulator and overall system power-up sequencing. The system designer should review the power up sequencing between the Vcc power supply enabling and TD7C341B data access. If there is sufficient time between the Vcc power supply enabling and the data access of the TD7C341B, this longer power up delay time will not cause a system disruption. Careful attention should also be given to:

- 1) Vcc supply regulator current limit and under-voltage control circuitry.

- 2) TD7C341B Vcc supply decoupling capacitor size and placement.

- 3) System supervisory circuit (if applicable) implementation of the Vcc supply regulator under-voltage.

For system designers looking to replace the obsolete CY7C341 with TD7C341B, a system review should be conducted to verify that this form-fit-function replacement will suffice in the application given the power up delay time vs temperature variation.

## 84-CPGA

| Device<br>types                                                                                                                                                           | All                                                                               | Device<br>types                                                                                | All                                                                         | Device<br>types                                                                           | All                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Terminal number                                                                                                                                                           | Terminal<br>symbol                                                                | Terminal number                                                                                | Terminal<br>symbol                                                          | Terminal number                                                                           | Terminal<br>symbol                                          |

| A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11<br>B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7<br>B8<br>B9<br>B10<br>B11<br>C1<br>C2<br>C5<br>C6<br>C7<br>C10 | I/O I/O I/O I/O I/O INPUT INPUT / CLK GND I/O | C11 D1 D2 D10 D11 E1 E2 E3 E9 E10 E11 F1 F2 F3 F9 F10 F11 G1 G2 G3 G9 G10 G11 H1 H2 H10 H11 J1 | I/O I/O I/O I/O I/O I/O I/O GND GND I/O | J2 J5 J6 J7 J10 J11 K1 K2 K3 K4 K5 K6 K7 K8 K9 K10 K11 L1 L2 L3 L4 L5 L6 L7 L8 L9 L10 L11 | I/O I/O INPUT INPUT I/O |

FIGURE 3. Terminal connections

| Truth Table |   |             |  |  |

|-------------|---|-------------|--|--|

| Input pins  |   | Output pins |  |  |

| I / CLK     | I | I/O         |  |  |

| Х           | Х | Z           |  |  |

#### NOTES:

X = Don't care.

- 1. Z = High impedance.

- 2 FIGURE 4. Truth table (unprogrammed)

# INPUT PULSES

#### AC test conditions

| Input pulse level             | GND to 3.0 V |

|-------------------------------|--------------|

| Input rise and fall levels    | ≤ 6 ns       |

| Input timing reference levels | 1.5 V        |

| Output reference levels       | 1.5 V        |

FIGURE 5. Output load circuits and test conditions

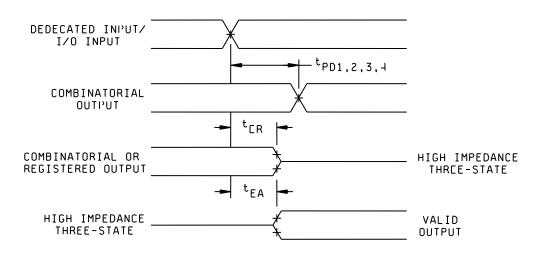

#### EXTERNAL COMBINATORIAL

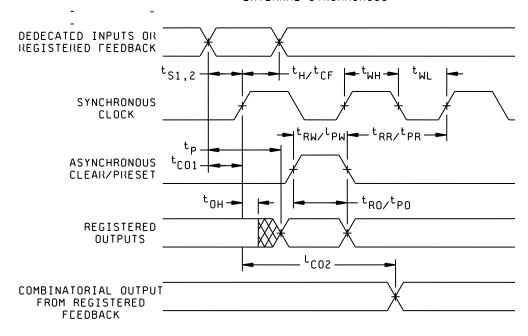

#### EXTERNAL SYNCHRONOUS

FIGURE 6. Switching waveforms

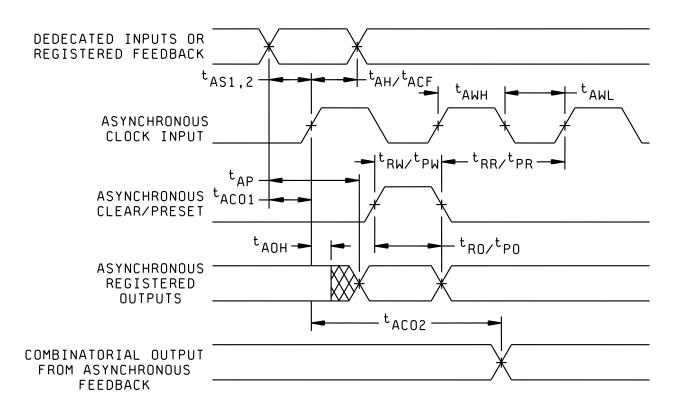

# EXTERNAL ASYNCHRONOUS

FIGURE 7. Switching waveforms - Continued

3.0 **Abbreviations, symbols, and definitions.** The abbreviations, symbols, and definitions used herein are defined in MIL-PRF-38535 and MIL-HDBK-1331, and as follows:

| C <sub>IN</sub> | Input terminal capacitance.    |  |

|-----------------|--------------------------------|--|

|                 | Output terminal capacitance.   |  |

| GND             | Ground zero voltage potential. |  |

| I <sub>CC</sub> |                                |  |

| I <sub>IX</sub> | Input current.                 |  |

| l <sub>oz</sub> | Output current.                |  |

| T <sub>C</sub>  | Case temperature.              |  |

| V <sub>CC</sub> | Positive supply voltage.       |  |

|                 |                                |  |

3.1 **Timing limits.** The table of timing values shows either a minimum or a maximum limit for each parameter. Input requirements are specified from the external system point of view. For example, address setup time would be shown as a minimum since the system must supply at least that much time (even though most devices do not require it). On the other hand, responses from the memory are specified from the device point of view. For example, the access time would be shown as a maximum since the device never provides data later than that time.

# 3.2 Waveforms.

| Waveform<br>symbol | Input                                 | Output                        |

|--------------------|---------------------------------------|-------------------------------|

|                    | MUST BE<br>VALID                      | WILL BE<br>VALID              |

|                    | CHANGE FROM<br>H TO L                 | WILL CHANGE<br>FROM<br>H TO L |

|                    | CHANGE FROM<br>L TO H                 | WILL CHANGE<br>FROM<br>L TO H |

|                    | DON'T CARE<br>ANY CHANGE<br>PERMITTED | CHANGING<br>STATE<br>UNKNOWN  |

|                    |                                       | HIGH<br>IMPEDANCE             |

## 4.0 Package Diagram

### 84-Lead Ceramic Windowed Pin Grid Array

FIGURE 8. Package Diagram

### **Contact Information:**

Teledyne e2v HiRel Electronics at: www.tdehirel.com Contact us via email: tdemarketing@teledyne.com

Trademarks are the property of their respective owners.

**Preliminary Specification:** The product is in a formative or design stage. The data sheet contains design target specifications for product development. Specifications and features may change in any manner without notice. **Advanced Information:** The data sheet contains preliminary data. Additional data may be added at a later date. Teledyne e2v HiRel Electronics reserves the right to change specifications at any time without notice in order to supply the best possible product.

**Product Specification** - The data sheet contains final data. In the event Teledyne e2v HiRel Electronics decides to change the specifications, Teledyne e2v HiRel will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

The information in this data sheet is believed to be reliable. However, Teledyne e2v HiRel Electronics assumes no liability for the use of this information. Use shall be entirely at the user's own risk. No patent rights or licenses to any circuits described in this data sheet are implied or granted to any third party. Teledyne e2v HiRel products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Teledyne e2v HiRel product could create a situation in which personal injury or death might occur. Teledyne e2v HiRel assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in suchapplications.

**Disclaimers:** The information in this document is believed to be reliable. However, Teledyne e2v HiRel Electronics assumes no liability for the use of this information. Use shall be entirely at the user's own risk. No patent rights or licenses to any circuits described in this document are implied or granted to any third party. Teledyne e2v HiRel's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Teledyne e2v HiRel's product could create a situation in which personal injury or death might occur. Teledyne e2v HiRel Electronics assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

Document #: TD7C341B-04-2020 Rev-