# 20A/40V Integrated Power Module in SIP23 package

The STK984-090A-E is a fully-integrated inverter power stage consisting of a gate driver, six MOSFET's and a high-side shunt resistor, suitable for driving permanent magnet synchronous (PMSM) motors and brushless-DC (BLDC) motors. The MOSFET's are configured in a 3-phase bridge with a single drain connection for the lower legs. The power stage has a full range of protection functions including cross-conduction protection, external shutdown and undervoltage lockout.

#### **Features**

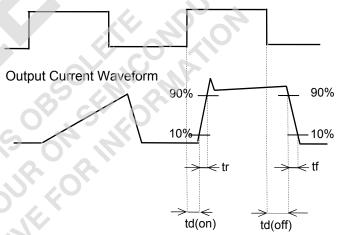

- Module with six 40V/20A MOSFETs, driver and sense resistor

- 59.8mm × 26.7mm single in-line package with 90° lead bend

- Built-in charge pump for operation with low battery voltage

- Over-current protection on both high-side and low-side MOSFETs

- Over-temperature shutdown

- Undervoltage and overvoltage shutdown for defined operation at all input voltages

- Integrated high-side resistor for external current sensing

#### **Typical Applications**

- Automotive Fans

- Automotive Pumps

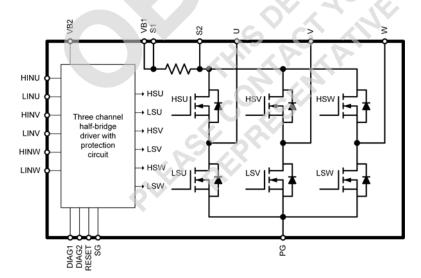

Figure 1: Functional Diagram

#### ON Semiconductor®

www.onsemi.com

#### PACKAGE PICTURE

SIP23 / SIP2E 2nd

#### **MARKING DIAGRAM**

STK984-090A

ABCCDD

STK984-090A-E = Specific Device Code

A = Year

B = Month

C = Production Site

DD = Factory Lot Code

#### **PIN CONNECTIONS**

#### ORDERING INFORMATION

| Device        | Package                        | Shipping<br>(Qty / Packing) |

|---------------|--------------------------------|-----------------------------|

| STK984-090A-E | SIP23 / SIP2E 2nd<br>(Pb-Free) | 9 / Tube                    |

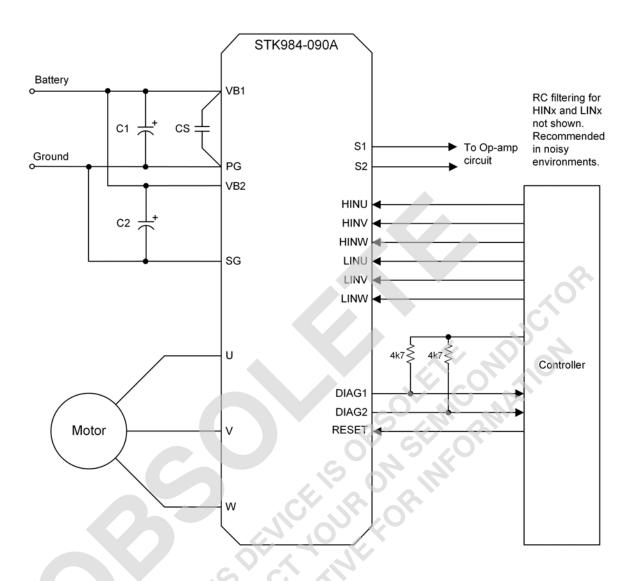

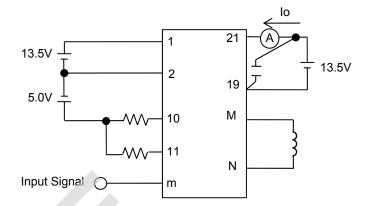

Figure 2: Application Schematic

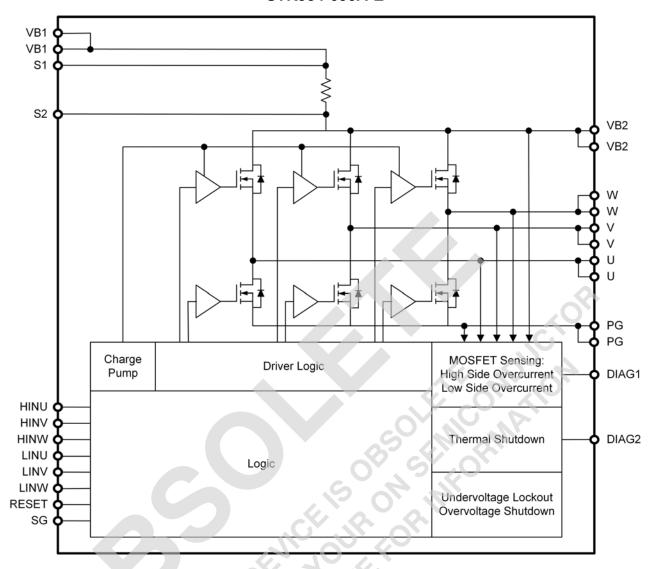

Figure 3: Simplified Block Diagram

# PIN FUNCTION DESCRIPTION

| Pin Number   | Pin Name       | Description                                 |

|--------------|----------------|---------------------------------------------|

| 1 III Number | VB2            | Control System Power                        |

| 2            | SG             | Control System GND                          |

| 3            | RESET          | RESET Terminal                              |

| 4            | HINU           | Driving Signal Input Upper U-phase          |

| 5            | HINV           | Driving Signal Input Upper V-phase          |

| 6            | HINW           | Driving Signal Input Upper W-phase          |

| 7            | LINU           | Driving Signal Input Lower U-phase          |

| 8            | LINV           | Driving Signal Input Lower V-phase          |

| 9            | LINW           | · · · · · · · · · · · · · · · · · · ·       |

| 10           |                | Driving Signal Input Lower W-phase          |

| 11           | DIAG1<br>DIAG2 | Fault Diagnosis Output 1 (Overcurrent)      |

|              |                | Fault Diagnosis Output 2 (Over Temperature) |

| 12           | U              | U-phase Output                              |

| 13           | U              | U-phase Output                              |

| 14           | V              | V-phase Output                              |

| 15           | V              | V-phase Output                              |

| 16           | W              | W-phase Output                              |

| 17           | W              | W-phase Output                              |

| 18           | PG             | Power System GND                            |

| 19           | PG             | Power System GND                            |

| 20           | VB1            | Power System Supply                         |

| 21           | VB1            | Power System Supply                         |

| 22           | S1             | Current Sense Resistor Sensing (+) terminal |

| 23           | S2             | Current Sense Resistor Sensing (–) terminal |

|              |                | Table 1: Pin Function Description           |

| Ý            |                |                                             |

#### ABSOLUTE MAXIMUM RATINGS (Notes 1, 2)

| Rating                | Symbol  | Conditions                 | Value       | Unit |

|-----------------------|---------|----------------------------|-------------|------|

| Supply Voltage        | VB1 max | VB1 to PG                  | -0.3 to 40  | V    |

|                       | VB2 max | VB2 to SG                  | -0.3 to 40  | V    |

| Control Input Voltage | Vin max | HINx, LINx to SG (x=U,V,W) | –0.3 to 6   | V    |

| DIAG Terminal Voltage | VDIAG   | DIAG1, DIAG2 to SG         | –0.3 to 6   | V    |

| D : 0 . 1             |         | DC                         | 20          | Α    |

| Drain Current         | ld max  | Pulse (Single 10µs pulse)  | 180         | Α    |

| Junction Temperature  | Tjmax   | Semiconductor Device       | 150         | °C   |

| Storage Temperature   | Tstg    | <u></u>                    | -40 to +125 | °C   |

- Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for

- Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

#### **RECOMMENDED OPERATING RANGES (Note 3)**

| Rating                          | Symbol | Test Conditions                               | Min   | Тур  | Max | Unit |

|---------------------------------|--------|-----------------------------------------------|-------|------|-----|------|

| 0 1 1/1                         | VB1    | VB1 to PG                                     | 8     | 13.5 | 18  | V    |

| Supply Voltage                  | VB2    | VB2 to SG                                     | 8     | 13.5 | 18  | V    |

| Output Current                  | lo     | 120deg Excitation Method with 100% duty cycle | (v- ; | O.   | 20  | Α    |

| Operating Substrate Temperature | Tc     | . 4                                           | -40   | -    | 125 | °C   |

| Drive PWM Frequency             | fo     | Duty cycle 10% to 90%, or 100%                |       | -    | 20  | kHz  |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# **ELECTRICAL CHARACTERISTICS** (Note 4)

at Ta = 25°C, VB1, VB2 = 13.5V unless otherwise specified

| Parameter                                                   | Test Conditions                                         | Symbol                | Min  | Тур  | Max        | Unit |

|-------------------------------------------------------------|---------------------------------------------------------|-----------------------|------|------|------------|------|

| Power output section                                        |                                                         |                       |      |      |            |      |

| Current consumption (Control system)                        | VB1=16V, VB2=16V                                        | Icc                   | -    | 10   | 15         | mA   |

| Output saturation voltage                                   | I <sub>O</sub> =20A. VB1 to U, V, W                     | \/= = (0.0t)          | -    | 0.3  | 0.5        | V    |

|                                                             | I <sub>O</sub> =20A. U, V, W to PG                      | V <sub>DS</sub> (sat) | -    | 0.2  | 0.4        | V    |

| Current sensing resistor                                    |                                                         | Rs                    | 2.91 | 3.00 | 3.09       | mΩ   |

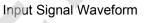

| Time delay (ON)                                             | I <sub>O</sub> =20A for U, V, W low to high             |                       | 0.9  | 1.8  | 2.8        | μs   |

|                                                             | I <sub>O</sub> =20A for U, V, W high to low             | td(on)                | 0.9  | 1.9  | 3.0        | μs   |

| Rise time                                                   | I <sub>O</sub> =20A                                     | tr                    | -    | 0.3  | -          | μS   |

| Time delay (OFF)                                            | I <sub>O</sub> =20A for U, V, W high to low             |                       | 1.3  | 2.9  | 4.5        | μs   |

|                                                             | I <sub>O</sub> =20A for U, V, W low to high             | td(off)               | 0.8  | 2.2  | 3.5        | μs   |

| Rise time                                                   | I <sub>O</sub> =20A                                     | tf                    | -    | 0.3  | -          | μS   |

| Thermal resistance                                          |                                                         |                       |      |      |            | •    |

| Chip to case Thermal Resistance                             | Junction-to-substrate (MOSFET)                          | θјс                   | -    | 4.5  | <b>D</b> . | °C/W |

| Protection Functions                                        |                                                         |                       |      | 70   | ,          |      |

| Undervoltage Lockout Falling Threshold                      |                                                         | Vuv                   | 4.45 | 4.75 | 5.1        | V    |

| Undervoltage Lockout Hysteresis                             |                                                         | Vuv(hy)               | 0.07 | 0.2  | 0.3        | V    |

| Undervoltage Lockout Output Delay                           |                                                         | tuvoff                | O    | 1.0  | -          | μS   |

| Over Current Threshold                                      | Automatic Recovery                                      | ISD                   | 21   | 34   | 44         | Α    |

| Over Current DIAG Output Delay Time                         | 0.5                                                     | tocdgoff              | 0-1  | 4.3  | -          | μS   |

| Over Current Shutdown Interval                              | Ov                                                      | t <sub>INT</sub>      | -    | 1    | -          | ms   |

| Over Current Shutdown Output Delay                          | .5                                                      | tocoff                | -    | 4.3  | -          | μS   |

| Ground Fault Short-Circuit Protection                       | Power-Cycle                                             | IOC                   | 47   | 84   | 113        | Α    |

| Ground Fault Short-Circuit Detection DIAG Output Delay Time | IIC JII                                                 | tspdgoff              | -    | 3.0  | -          | μS   |

| Ground Fault Short-Circuit Shutdown Output Delay Time       | SE, 4 16                                                | tspoff                | -    | 3.0  | -          | μS   |

| Temperature Protection Shutdown                             | IPM Substrate Temperature Rising Temperature Threshold  | Tst(rising)           | 146  | 155  | 165        | °C   |

| Temperature Protection Recovery                             | IPM Substrate Temperature Falling Temperature Threshold | Tst(falling)          | 126  | 135  | 145        | °C   |

| Over Temperature DIAG Output Delay Time                     | .07 (17                                                 | tthdgoff              | -    | 3.4  | -          | μS   |

| Over Temperature Shutdown Output Delay                      | 7 (2)                                                   | tthoff                | -    | 3.4  | -          | μS   |

| Over Voltage Protection Rising Threshold                    | O.C.                                                    | Vov                   | 24   | -    | -          | V    |

| Over Voltage Protection Hysteresis                          |                                                         | Vov(hy)               | -    | 0.5  | -          | V    |

| Over Voltage Protection Output Delay                        |                                                         | tovoff                | -    | 1.0  | -          | μS   |

| DIAG Output                                                 |                                                         |                       |      |      |            |      |

| DIAG Output Voltage (DIAG1, DIAG2)                          | DIAGx=LOW, Sink Current =1mA                            | VDIAG                 | -    | -    | 0.2        | V    |

| DIAG Output Leakage Current<br>(DIAG1, DIAG2)               | VDIAG=5V                                                | IDILK                 | -    | _    | 1          | μА   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### **ELECTRICAL CHARACTERISTICS** (Note 5)

at 8V≤VB1 VB2≤18V \_40°C≤Ta≤125°C

| Parameter                      | Test Conditions                                    | Symbol      | Min | Тур  | Max | Unit |

|--------------------------------|----------------------------------------------------|-------------|-----|------|-----|------|

| Motor Control Input Terminal   |                                                    |             |     |      |     |      |

| HIGH level input voltage       | Output ON. LINx, HINx to SG. x=U,V,W               | Vin(on)     | 3.5 | -    | -   | V    |

| LOW level input voltage        | Output OFF. LINx, HINx to SG. x=U,V,W              | Vin(off)    | -   | -    | 1.5 | V    |

| Reset Input Terminal           |                                                    |             |     |      |     |      |

| Reset HIGH level input voltage | Output ON                                          | Vreset(Hi)  | 3.5 | -    | -   | V    |

| Reset LOW level input voltage  | Output OFF                                         | Vreset(Lo)  | -   | -    | 1.5 | V    |

| Output Delay Time (ON)         | From Reset Input Terminal (RESET=Hi) to Output ON  | treset(on)  | -   | 0.25 | -   | ms   |

| Output Delay Time (OFF)        | From Reset Input Terminal (RESET=Lo) to Output OFF | treset(off) | -   | 2    | -   | μS   |

<sup>5.</sup> Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### TYPICAL CHARACTERISTICS

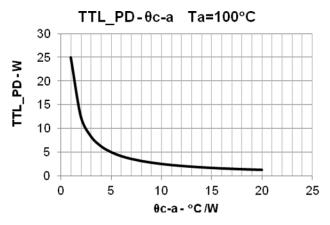

Figure 6 Power Dissipation versus Heatsink Size

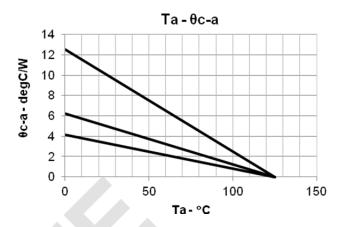

Figure 7 Heatsink size for PD=10W, 20W and 30W versus ambient temperature

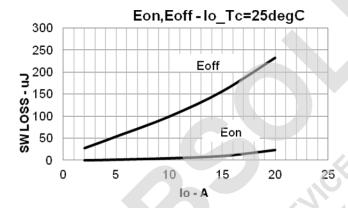

Figure 5 Switching losses versus current at 25°C

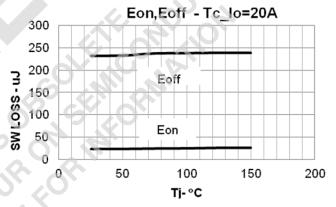

Figure 4 Switching losses versus temperature at 20A

#### **APPLICATIONS INFORMATION**

#### **Functional Description**

Table 2 shows the truth table for the normal operating mode. The truth table shows the U output which is controlled by the HINU and LINU inputs. The truth tables for the V and W outputs follow the same rules. The input signals are active HIGH. The RESET signal is active LOW.

An internal pull-down resistor (100k $\Omega$  typical) is connected to each input signal terminal. If an additional external pull-down resistor is used, it is important to ensure the input voltage threshold requirements are still met.

|      | Input |       |     | Output | Operation |            |

|------|-------|-------|-----|--------|-----------|------------|

| HINU | LINU  | RESET | U   | DIAG1  | DIAG2     | Mode       |

| L    | L     | Н     | OFF | L      | L         | Output OFF |

| L    | Н     | Н     | L   | L      | L         | Lo Side ON |

| Н    | L     | Н     | Н   | L      | L         | Hi Side ON |

| Н    | Н     | Н     | OFF | L      | L         | Output OFF |

| Х    | Х     | L     | OFF | Н      | Н         | Output OFF |

**Table 2: Truth Table Normal Operating Mode**

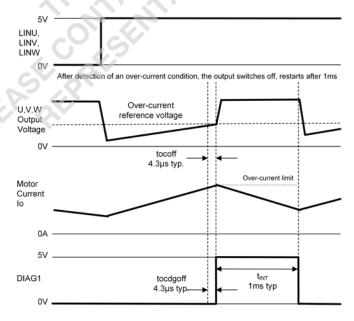

# Operation in over-current and short-circuit conditions

Table 3 shows the truth table for over-current and short-circuit protection operating conditions for the U output which is controlled by the HINU and LINU inputs. The truth tables for the V and W outputs follow the same rules.

Over-current protection is activated only if LINU, LINV and LINW are in the high state. Short-circuit protection is activated only if LINU, LINV and LINW are in the low state.

|      |       |       |     |        |       | <b>\</b>                                     |

|------|-------|-------|-----|--------|-------|----------------------------------------------|

|      | Input |       |     | Output |       | Operation                                    |

| HINU | LINU  | RESET | U   | DIAG1  | DIAG2 | Mode                                         |

| L    | L     | Н     | OFF | L      | L     | Output OFF                                   |

| L    | Н     | Н     | L   | Н      | L     | Over<br>Current<br>Protection<br>Operating   |

| Н    | L     | Н     | н   | Н      | L     | Short-<br>Circuit<br>Protection<br>Operating |

| Н    | Н     | Н     | OFF | L      | L     | Output OFF                                   |

| L/H  | L/H   | L     | OFF | Н      | Н     | Output OFF                                   |

Table 3:Truth Table Over-current and Short-circuit

Protection Modes

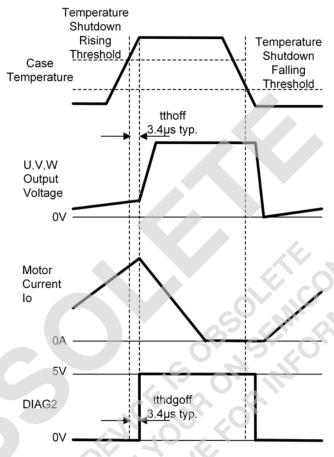

# Operation in over-temperature conditions

Table 4 shows the truth table for over-temperature operating conditions.

|      | Input Output |       |     |       |       | Operation                             |  |

|------|--------------|-------|-----|-------|-------|---------------------------------------|--|

| HINU | LINU         | RESET | U   | DIAG1 | DIAG2 | Mode                                  |  |

| х    | Х            | н     | OFF | L     | н     | Over Temperature Protection Operating |  |

| Х    | Х            | L     | OFF | Н     | Н     | Output OFF                            |  |

Table 4: Truth Table Over-temperature Protection

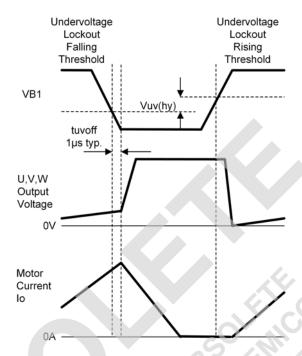

#### Operation in undervoltage conditions

Table 5 shows the truth table for low voltage protection operating conditions.

|      | Input |       |     | Output |       | Operation                              |  |

|------|-------|-------|-----|--------|-------|----------------------------------------|--|

| HINU | LINU  | RESET | U   | DIAG1  | DIAG2 | Mode                                   |  |

| х    | Х     | H     | OFF | L      | L     | Low voltage<br>Protection<br>Operating |  |

| Х    | Х     | L     | OFF | Н      | Н     | Output OFF                             |  |

**Table 5: Truth Table Low Voltage Protection**

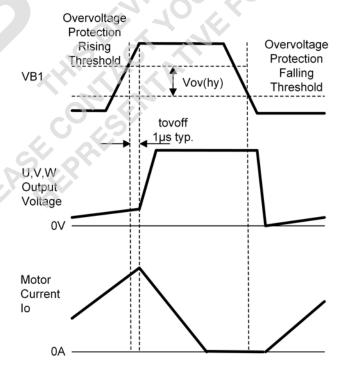

#### Operation in over-voltage conditions

Table 6 shows the truth table for over-voltage operating conditions.

| 4 | Input |      |       |     | Output |       | Operation                                  |  |

|---|-------|------|-------|-----|--------|-------|--------------------------------------------|--|

|   | HINU  | LINU | RESET | U   | DIAG1  | DIAG2 | Mode                                       |  |

| - | Х     | Х    | Н     | OFF | L      | L     | Over<br>Voltage<br>Protection<br>Operating |  |

|   | Х     | Х    | L     | OFF | Н      | Н     | Output OFF                                 |  |

**Table 6: Truth Table Over-Voltage Protection**

#### **DIAG Outputs**

Terminal DIAG1 and DIAG2 are open drain outputs. A pull-up resistor of  $4.7k\Omega$  for a 5V power supply is recommended.

#### Layout

Voltage ringing due to stray inductance, especially in the power source wiring between VB1 and PG, will occur during switching. Use layout techniques such as short traces and wide traces to minimize the inductance of the power loop. Further, a high frequency capacitor needs to be placed very close to the terminals VB1 and PG, in addition to the electrolytic bulk capacitor.

### System level fuse

A system level fuse in the VB1 power line is recommend to ensure a fail-safe design.

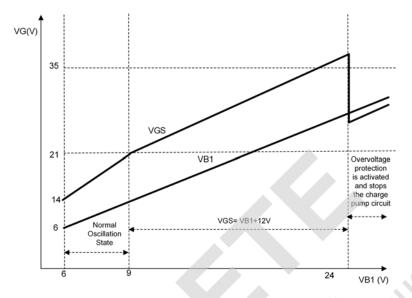

# Gate Driver Voltage: High-side and low-side

The high-side MOSFETs are driven with an internal charge pump. The gate voltage VG from the built-in charge pump circuit is set at VG=VB1+12V.

Figure 8: Gate drive voltage variation with battery voltage for high-side MOSFETs

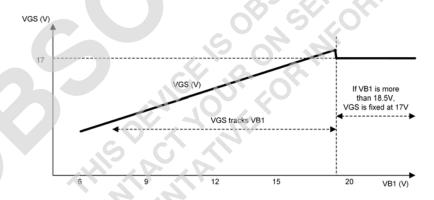

The gate drive voltage for the low-side MOSFETs follows the voltage on VB1. If VB1 exceeds 18.5V, the gate drive voltage is limited to 17V.

Figure 9: Gate drive voltage versus battery voltage for low-side MOSFETs

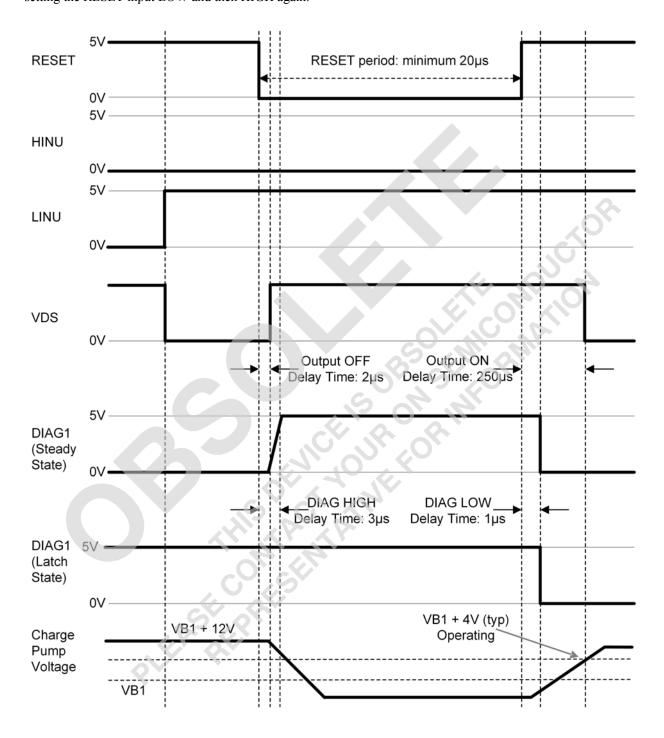

# **RESET input**

An internal pull-up resistor ( $100k\Omega$  typical) is connected to the RESET signal. When the RESET pin is HIGH or left open, the IPM operates normally. If the RESET line is LOW, all six gate driver outputs will be set to the OFF state. When the short-circuit protection operates and latches the output OFF, the latched output OFF can be released by setting the RESET input LOW and then HIGH again.

Figure 10: Timing diagram for RESET

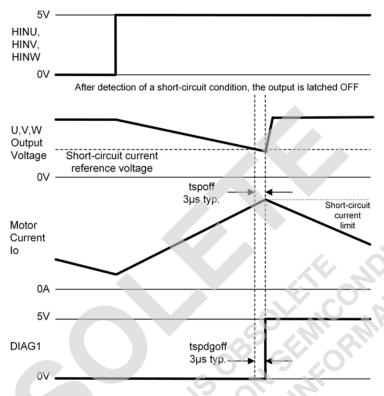

#### **Short-circuit Protection Circuit**

The Short-circuit Protection Circuit monitors the drain voltage of the high side MOSFET to detect short circuits. This circuit detects a short circuit when a short circuit current flows for longer than tspoff (typically 3µs). The outputs are switched to the OFF state and the DIAG1 signal is switched HIGH. The IPM is then latched in the short-circuit protection state. This state can be released by setting the RESET input LOW and then HIGH again.

Figure 11: Timing Diagram Short-circuit Condition

#### **Over-current Protection Circuit**

The Over-current Protection Circuit monitors the drain voltage of the low-side MOSFETs to detect over currents. This circuit detects a short circuit when a short circuit current flows for longer than tocoff (typically  $4.3\mu s$ ). When a short circuit is detected, the outputs are switched off and the short circuit condition is flagged by switching on DIAG1. The over-current protection state is held for time  $t_{INT}$  (typically 1ms) then released. It is not latched like the short-circuit current protection mode.

Figure 12: Timing Diagram for Over-current Protection

#### **Undervoltage Lockout Protection Circuit**

The Undervoltage Lockout Protection Circuit monitors voltages supplied to VB1 pin to detect low voltages. When the voltage on VB1 falls below the undervoltage lockout falling threshold, the outputs will be turned off. The undervoltage lockout circuit has a hysteresis. If the voltage on VB1 rises above the undervoltage lockout rising threshold, the module will return to normal operating mode.

Figure 13: Timing Diagram Low Voltage Protection

#### **Overvoltage Protection Circuit**

The Overvoltage Protection Circuit monitors the voltage on VB1. If the voltage on VB1 exceeds the overvoltage protection threshold, the outputs will be switched off. The Overvoltage Protection Circuit has hysteresis. The IPM will return to normal operation when the voltage on VB1 falls below the over-voltage protection falling threshold voltage.

**Figure 14 Timing Diagram Overvoltage Protection**

#### **Over-temperature Protection Circuit**

The Over-temperature Protection Circuit monitors the circuit substrate temperature to detect excessive temperatures. When the case temperature rises above the temperature shutdown rising threshold, the outputs are switched off and the over temperature condition is flagged on output DIAG2. There is hysteresis in the over-temperature protection circuit. When the case temperature falls below the temperature shutdown falling threshold, the circuit returns to normal operation and the over-temperature condition is no longer flagged on the DIAG2 output.

Figure 15: Timing Diagram Over-temperature Protection

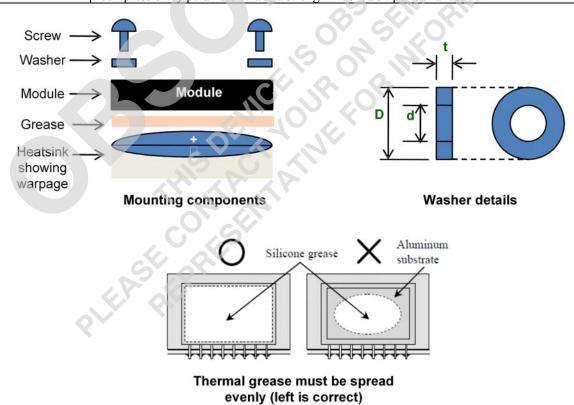

# **Mounting Instructions**

| Item              | Recommended Conditions                                                                                                                                                                                                                                          |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pitch             | 56.0 ± 0.2mm (Please refer to Package Outline Diagram)                                                                                                                                                                                                          |

| Screw             | Diameter: M3 Screw head types: pan head, truss head, binding head                                                                                                                                                                                               |

| Washer            | Plane washer dimensions (Figure 16) D = 7mm, d = 3.2mm and t = 0.5mm JIS B 1256                                                                                                                                                                                 |

| Heat sink         | Material: Aluminum or Copper Warpage (the surface that contacts IPM ): –50 to 100 μm Screw holes for the heat sink must be countersunk. No contamination on the heat sink surface that contacts IPM.                                                            |

| Torque            | Temporary tightening: 20 to 30 % of final tightening on first screw Temporary tightening: 20 to 30 % of final tightening on second screw Final tightening: 0.6 to 0.9Nm on first screw Final tightening: 0.6 to 0.9Nm on second screw                           |

| Thermal Interface | Silicone grease is recommended. Thickness: 100 to 200 µm Uniformly apply silicon grease to whole back. Thermal foils are only recommended after careful evaluation. Thickness, stiffness and compressibility parameters have a strong influence on performance. |

Figure 16: Module Mounting details: components; washer drawing; need for even spreading of thermal grease

# **Reliability Specification**

Ta=25°C±5°C, Relative humidity 65%±20% unless otherwise specified

| Parameter                              |                                           | Test Conditions                                                                              | Evaluation Time               | Evaluation<br>Method                                                        | Test Time |

|----------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------|-----------|

| Mechanical Strength Environmental Test | Free-Fall                                 | High = 75cm, drop on a woodblock<br>Woodblock : maple 30×30×3cm<br>Conform to JIS C 7021 A-8 | Drop Time = 3 times           | Electrical<br>Characteristics                                               | N = 5     |

|                                        | Vibration Fatigue                         | Vibration Frequently f = 10HZ to 55HZ<br>Logarithmic Sweep<br>Total Amplitude = 1.5+0.2mm    | X, Y, Z<br>Each direction 2hr | Electrical<br>Characteristics<br>Visual<br>Inspection                       | N = 11    |

|                                        | Thermal Shock<br>(Vapor Tank)             | Ta = -40°C↔125°C (30min. each) Elapsed time after the test =2hr                              | 1000 Cycles                   | Electrical<br>Characteristics<br>Visual<br>Inspection<br>Solder<br>Junction | N = 11    |

|                                        | Pressure Cooker                           | Ta = 121°C, RH=100%, 2 air pressure                                                          | 48hr                          | Electrical<br>Characteristics                                               | N = 11    |

|                                        | High-Temperature<br>Storage               | Ta = 125°C<br>Elapsed time after the test = 3hr<br>Conform to JIS C 7201 B-10                | 1000hr                        | Electrical<br>Characteristics                                               | N = 11    |

| Life Test                              | Low-Temperature<br>Storage                | Ta = -40°C<br>Elapsed time after the test=3hr<br>Conform to JIS C 7021 B-12                  | 1000hr                        | Electrical<br>Characteristics                                               | N = 11    |

|                                        | High Temperature<br>High Humidity<br>Bias | Ta = 85°C±2°C, RH = 85%±5%<br>VB1, VB2 = 70% of Maximum Rating                               | 1000hr                        | Electrical<br>Characteristics                                               | N = 11    |

|                                        | PLE                                       | Ta = 85°C±2°C, RH = 85%±5%<br>VB1, VB2 = 70% of Maximum Rating  Table 7: Reliability Specifi | cation                        |                                                                             |           |

#### **Test Circuits**

■ VDS(sat) measurement (Pulse Measurement)

Figure 17 VDS Measurement Circuit

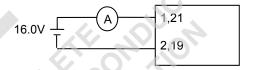

# ■ ICC Measurement

Figure 18 ICC Measurement Circuit

# ■ ISD Measurement

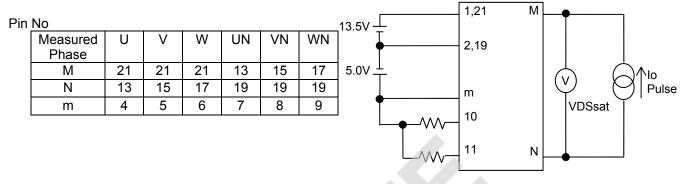

Pin No

| Measured | Short-Circuit<br>Threshold |      | Overcurrent<br>Threshold |    |    |    |

|----------|----------------------------|------|--------------------------|----|----|----|

| Phase    | U                          | V    | W                        | UN | VN | WN |

| M        | 19                         | 19   | 19                       | 13 | 15 | 17 |

| N        | 13                         | 15   | 17                       | 21 | 21 | 21 |

| m        | 4                          | 5    | 6                        | 7  | 8  | 9  |

|          | P                          | E.A. | PL                       | PR |    |    |

**Figure 19 ISD Measurement Circuit**

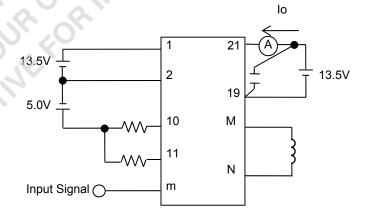

■ Measurement of rise, fall and delay times

# Pin No

| • | 1110     |    |    |    |    |    |    |  |

|---|----------|----|----|----|----|----|----|--|

|   | Measured | U  | V  | W  | UN | VN | WN |  |

|   | Phase    |    |    |    |    |    |    |  |

|   | M        | 19 | 19 | 19 | 13 | 15 | 17 |  |

|   | N        | 13 | 15 | 17 | 21 | 21 | 21 |  |

|   | m        | 4  | 5  | 6  | 7  | 8  | 9  |  |

Figure 20 Switch Time Measurement Circuit

**Figure 21 Switch Time Definitions**

#### **PACKAGE DIMENSIONS**

unit: mm

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent re