OGY Single-Ended 8-Channel/ Differential 4-Channel Analog Multiplexer with SMBus Interface

## **FEATURES**

- Micropower Operation: Supply Current = 20µA Max

- 2-Wire SMBus Interface

- Single 2.7V to ±5V Supply Operation

- Expandable to 32 Single or 16 Differential Channels

- Guaranteed Break-Before-Make

- Low  $R_{ON}$ : 35 $\Omega$  Single Ended/70 $\Omega$  Differential

- Low Charge Injection: 20pC Max

- Low Leakage: ±5nA Max

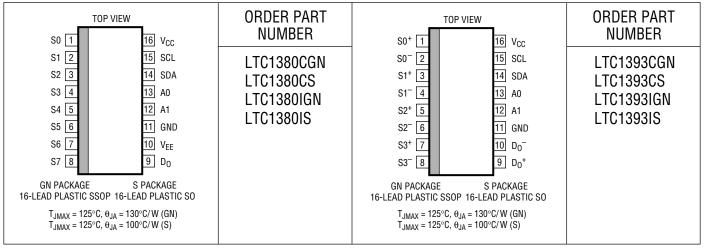

- Available in 16-Lead SO and GN Packages

## **APPLICATIONS**

- Data Acquisition Systems

- Process Control

- Laptop Computers

- Signal Multiplexing/Demultiplexing

- Analog-to-Digital Conversion Systems

## DESCRIPTION

The LTC®1380/LTC1393 are CMOS analog multiplexers with SMBus® compatible digital interfaces. The LTC1380 is a single-ended 8-channel multiplexer, while the LTC1393 is a differential 4-channel multiplexer. The SMBus digital interface requires only two wires (SCL and SDA). Both the LTC1380 and the LTC1393 have four hard-wired SMBus addresses, selectable with two external address pins. This allows four devices, each with a unique SMBus address, to coexist on one system and for four devices to be synchronized with one stop bit.

The supply current is typically  $10\mu A$ . Both digital interface pins are SMBus compatible over the full operating supply voltage range. The LTC1380 analog switches feature a typical  $R_{ON}$  of  $35\Omega$  ( $\pm5V$  supplies), typical switch leakage of 20pA and guaranteed break-before-make operation. Charge injection is  $\pm1pC$  typical.

The LTC1380/LTC1393 are available in 16-lead SO and GN packages. Operation is fully specified over the commercial and industrial temperature ranges.

(T), LTC and LT are registered trademarks of Linear Technology Corporation. SMBus is a registered trademark of Intel Corporation.

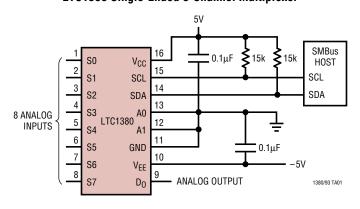

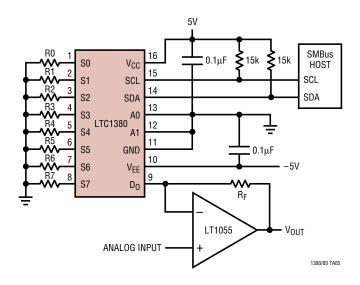

## TYPICAL APPLICATION

#### LTC1380 Single-Ended 8-Channel Multiplexer

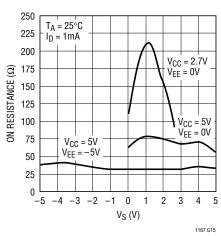

#### On Resistance vs V<sub>S</sub>

## **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                                                              |      |

|-----------------------------------------------------------------------|------|

| Total Supply Voltage                                                  |      |

| LTC1380 (V <sub>CC</sub> to V <sub>EE</sub> )                         | 15V  |

| LTC1393 (V <sub>CC</sub> to GND)                                      | 15V  |

| Analog Input Voltage                                                  |      |

| LTC1380 $V_{EE} - 0.3V$ to $V_{CC} + 0.3V$                            | 0.3V |

| LTC1393 0.3V to V <sub>CC</sub> + (                                   | 0.3V |

| Digital Inputs0.3V to                                                 | 15V  |

| LTC1380 ( $V_{CC}$ TO $V_{EE}$ ) ( $V_{EE}$ – 0.3V) to ( $V_{EE}$ + 1 | 15V) |

| LTC1393 (V <sub>CC</sub> to GND)0.3V to                               | 15V  |

| Maximum Switch-On Current            | 65mA                   |

|--------------------------------------|------------------------|

| Power Dissipation                    | 500mW                  |

| Operating Ambient Temperature Range  |                        |

| LTC1380C/LTC1393C0°C ≤ 1             | $T_A \le 70^{\circ}$ C |

| LTC1380I/LTC1393I40°C ≤ 1            | $T_A \le 85^{\circ}C$  |

| Junction Temperature                 | 125°C                  |

| Storage Temperature Range65°C        |                        |

| Lead Temperature (Soldering, 10 sec) | 300°C                  |

|                                      |                        |

## PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

# **ELECTRICAL CHARACTERISTICS** (Notes 2, 4)

| SYMBOL              | PARAMETER                                   | CONDITIONS                                                                                                          |   | MIN             | TYP   | MAX             | UNITS    |

|---------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---|-----------------|-------|-----------------|----------|

| V <sub>ANALOG</sub> | Analog Signal Range                         | LTC1380                                                                                                             | • | V <sub>EE</sub> |       | V <sub>CC</sub> | V        |

|                     |                                             | LTC1393                                                                                                             | • | 0               |       | V <sub>CC</sub> | V        |

| R <sub>ON</sub>     | On Resistance                               | LT1380: $V_{CC} = 5V$ , $V_{EE} = -5V$ , $V_{EE} \le (V_S, V_D) \le V_{CC}$ , $I_D = \pm 1 \text{mA}$               | • |                 | 35    | 70<br>120       | Ω        |

|                     |                                             | LT1393: $V_{CC} = 5V$ ,<br>$0V \le (V_S, V_D) \le V_{CC}$ , $I_D = \pm 1 \text{mA}$                                 | • |                 | 70    | 140<br>200      | Ω        |

|                     |                                             | LT1380/LTC1393: $V_{CC}$ = 2.7V, $V_{EE}$ = 0V, $0V \le (V_S, V_D) \le V_{CC}$ , $I_D$ = ±1mA                       | • |                 | 210   | 400<br>600      | Ω<br>Ω   |

|                     | $\Delta R_{ON}$ vs $V_S$                    | $V_{EE} \le (V_S, V_D) \le V_{CC}, V_{CC} = 5V$                                                                     |   |                 | 20    |                 | %        |

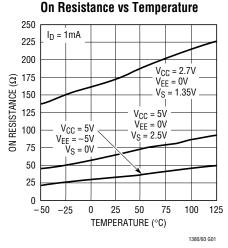

|                     | R <sub>ON</sub> vs Temperature              | V <sub>CC</sub> = 5V                                                                                                |   |                 | 0.5   |                 | %/°C     |

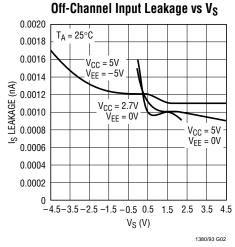

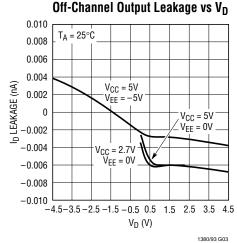

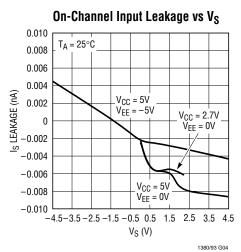

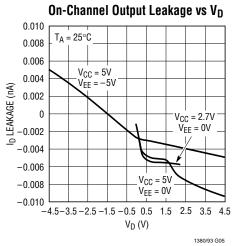

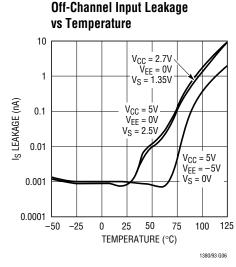

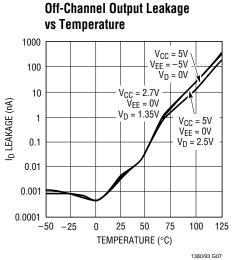

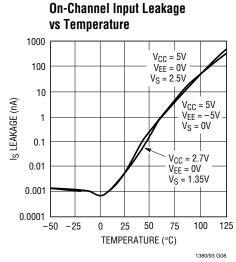

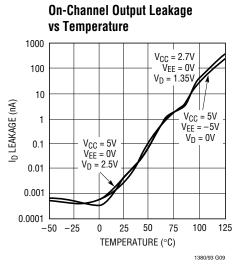

| I <sub>LEAK</sub>   | Off-Channel or On-Channel<br>Switch Leakage | LTC1380: $(V_{EE} + 0.5V) \le (V_S, V_D) \le (V_{CC} - 0.5V)$<br>LTC1393: $0.5V \le (V_S, V_D) \le (V_{CC} - 0.5V)$ | • |                 | ±0.05 | ±5<br>±50       | nA<br>nA |

# **ELECTRICAL CHARACTERISTICS** (Notes 2, 4)

| SYMBOL              | PARAMETER                                  | CONDITIONS                                                                                                                     |   | MIN | TYP                | MAX                  | UNITS          |

|---------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---|-----|--------------------|----------------------|----------------|

| $\overline{V_{IH}}$ | SCL, SDA Input High Voltage                |                                                                                                                                | • | 1.4 |                    |                      | V              |

| $\overline{V_{IL}}$ | SCL, SDA Input Low Voltage                 |                                                                                                                                | • |     |                    | 0.6                  | V              |

| $\overline{V_{0L}}$ | SDA Output Low Voltage                     | I <sub>SDA</sub> = 3mA                                                                                                         | • |     |                    | 0.4                  | V              |

| $V_{AH}$            | Address Input High Voltage                 | V <sub>CC</sub> = 5V                                                                                                           | • | 2   |                    |                      | V              |

| $\overline{V_{AL}}$ | Address Input Low Voltage                  | V <sub>CC</sub> = 5V                                                                                                           | • |     |                    | 0.8                  | V              |

| I <sub>IN</sub>     | SCL, SDA, Address Input Current            | $0V \le V_{IN} \le V_{CC}$                                                                                                     |   |     |                    | ±1                   | μΑ             |

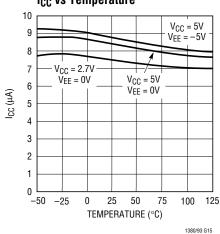

| I <sub>CC</sub>     | Positive Supply Current                    | V <sub>CC</sub> = 5V, All Digital Inputs at 5V                                                                                 | • |     | 10                 | 20                   | μΑ             |

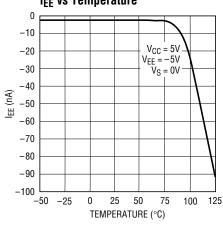

| I <sub>EE</sub>     | Negative Supply Current                    | LTC1380: V <sub>CC</sub> = 5V, V <sub>EE</sub> = -5V, All Digital Inputs at 5V                                                 | • |     | -0.1               | -5                   | μА             |

| $\overline{C_S}$    | Input Off Capacitance                      | (Note 3)                                                                                                                       |   |     | 3                  |                      | pF             |

| C <sub>D</sub>      | Output Off Capacitance                     | (Note 3) LTC1380<br>LTC1393                                                                                                    |   |     | 26<br>18           |                      | pF<br>pF       |

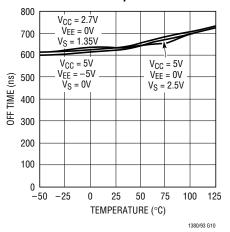

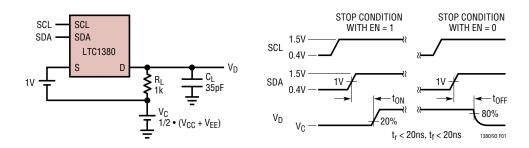

| t <sub>ON</sub>     | Switch Turn-On Time from<br>Stop Condition | Figure 1 LTC1380: $V_{CC} = 5V$ , $V_{EE} = -5V$<br>LTC1393: $V_{CC} = 5V$<br>LTC1380/LTC1393: $V_{CC} = 2.7V$ , $V_{EE} = 0V$ | • |     | 850<br>850<br>1130 | 1500<br>1500<br>2000 | ns<br>ns<br>ns |

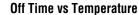

| t <sub>OFF</sub>    | Switch Turn-Off Time from Stop Condition   | Figure 1 LTC1380: $V_{CC} = 5V$ , $V_{EE} = -5V$<br>LTC1393: $V_{CC} = 5V$<br>LTC1380/LTC1393: $V_{CC} = 2.7V$ , $V_{EE} = 0V$ | • |     | 640<br>650<br>670  | 1200<br>1200<br>1200 | ns<br>ns<br>ns |

| topen               | Break-Before-Make Interval                 | t <sub>ON</sub> - t <sub>OFF</sub>                                                                                             | • | 75  | 210                |                      | ns             |

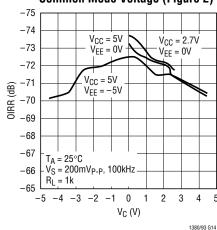

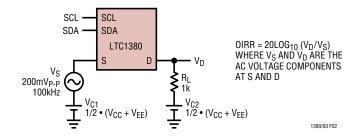

| OIRR                | Off-Channel Isolation                      | Figure 2, $V_S = 200 \text{mV}_{P-P}$ , $R_L = 1 \text{k}$ , $f = 100 \text{kHz}$ (Note 3)                                     |   |     | -65                |                      | dB             |

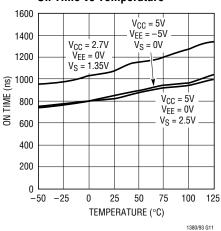

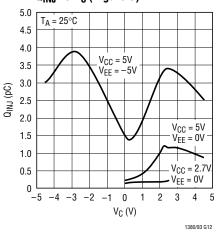

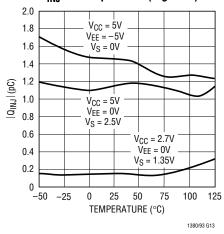

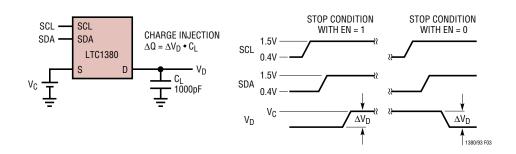

| $Q_{INJ}$           | Charge Injection                           | Figure 3, C <sub>L</sub> = 1000pF (Note 3)                                                                                     | • |     | ±1                 | ±20                  | pC             |

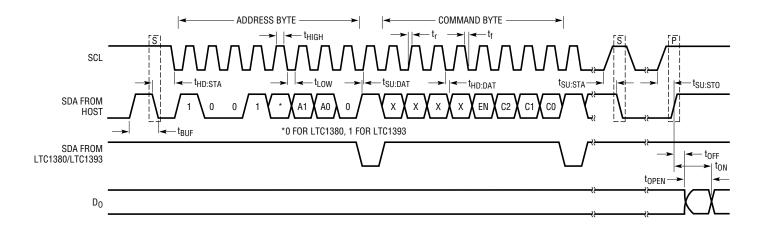

| SMBus Tii           | ming (Note 6)                              |                                                                                                                                |   |     |                    |                      |                |

| f <sub>SMB</sub>    | SMBus Operating Frequency                  |                                                                                                                                | • |     |                    | 100                  | kHz            |

| t <sub>BUF</sub>    | Bus Free Time Between Stop/Start           |                                                                                                                                | • | 4.7 |                    |                      | μs             |

| t <sub>HD:STA</sub> | Hold Time After (Repeated) Start           |                                                                                                                                | • | 4.0 |                    |                      | μS             |

| t <sub>SU:STA</sub> | Repeated Start Setup Time                  |                                                                                                                                | • | 4.7 |                    |                      | μS             |

| t <sub>SU:STO</sub> | Stop Condition Setup Time                  |                                                                                                                                | • | 4.0 |                    |                      | μs             |

| t <sub>HD:DAT</sub> | Data Hold Time                             |                                                                                                                                | • | 300 |                    |                      | ns             |

| t <sub>SU:DAT</sub> | Data Setup Time                            |                                                                                                                                | • | 250 |                    |                      | ns             |

| $t_{LOW}$           | Clock Low Period                           |                                                                                                                                | • | 4.7 |                    |                      | μs             |

| t <sub>HIGH</sub>   | Clock High Period                          |                                                                                                                                | • | 4.0 |                    |                      | μs             |

| t <sub>f</sub>      | SCL/SDA Fall Time                          | Time Interval Between 0.9V <sub>DD</sub> and (V <sub>ILMAX</sub> – 0.15)                                                       | • |     |                    | 300                  | ns             |

| t <sub>r</sub>      | SCL/SDA Rise Time                          | Time Interval Between (V <sub>ILMAX</sub> – 0.15)<br>and (V <sub>IHMIN</sub> + 0.15)                                           | • |     |                    | 1000                 | ns             |

The ullet denotes specifications which apply over the full operating temperature range.

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** All current into device pins is positive; all current out of device pins is negative. All voltages are referenced to ground unless otherwise specified. All typicals are given for  $T_A = 25$ °C,  $V_{CC} = 5V$  (for both LTC1380 and LTC1393) and  $V_{EE} = -5V$  (LTC1380).

**Note 3:** These typical parameters are based on bench measurements and are not production tested.

Note 4: Both SCL and SDA assume an external 15k pull-up resistor to a typical SMBus host power supply  $V_{DD}$  of 5V.

**Note 5:** Typical curves with  $V_{EE} = -5V$  apply to the LTC1380. Curves with  $V_{EE} = 0V$  apply to both the LTC1380 and the LTC1393.

**Note 6:** These parameters are guaranteed by design and are not tested in production.

## TYPICAL PERFORMANCE CHARACTERISTICS (Note 5)

# TYPICAL PERFORMANCE CHARACTERISTICS (Note 5)

### On Time vs Temperature

#### Q<sub>INJ</sub> vs V<sub>C</sub> (Figure 3)

### Q<sub>IN.I</sub> vs Temperature (Figure 3)

#### Off-Channel Isolation vs Input Common Mode Voltage (Figure 2)

#### I<sub>CC</sub> vs Temperature

I<sub>EE</sub> vs Temperature

## PIN FUNCTIONS

**S0 to S7/S0** $^{\pm}$ **to S3** $^{\pm}$ **(Pin 1 to Pin 8):** Single-Ended Analog Multiplexer Inputs (S0 to S7) for the LTC1380. Differential Analog Multiplexer Inputs (S0 $^{\pm}$ to S3 $^{\pm}$ ) for the LTC1393.

**D<sub>0</sub>/D<sub>0</sub><sup>+</sup> (Pin 9):** Analog Multiplexer Output for the LTC1380. Positive Differential Analog Multiplexer Output for the LTC1393.

$V_{EE}/D_0^-$  (Pin 10): Negative Supply Pin for the LTC1380. Negative Differential Multiplexer Output for the LTC1393. For the LTC1380,  $V_{EE}$  should be bypassed to GND with a 0.1 $\mu$ F ceramic capacitor when operating from split supplies or connected to GND for single supply operation.

GND (Pin 11): Ground Pin.

**A1, A0 (Pin 12, Pin 13):** Address Selection Pins. Tie these two pins to either  $V_{CC}$  or GND to select one of four possible addresses to which the LTC1380/LTC1393 will respond.

**SDA (Pin 14):** SMBus Bidirectional Digital Input/Output Pin. This pin has an open-drain output and requires a pull-up resistor or current source to the positive supply for normal operation. Data is shifted into and acknowledged by the LTC1380/LTC1393 using this pin.

**SCL (Pin 15):** SMBus Clock Input. SDA data is shifted in at rising edges of this clock during data transfer.

$V_{CC}$  (Pin 16): Positive Supply Pin. This pin should be bypassed to GND with a  $0.1\mu F$  ceramic capacitor.

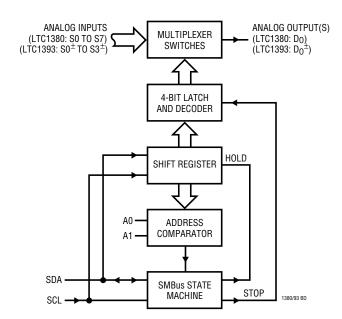

## **BLOCK DIAGRAM**

## **TEST CIRCUITS**

Figure 1. Switch  $t_{\text{ON}}/t_{\text{OFF}}$  Propagation Delay from SMBus STOP Condition

Figure 2. Off-Channel Isolation (OIRR) Test

Figure 3. Charge Injection Test

## TIMING DIAGRAM

### APPLICATIONS INFORMATION

### Theory of Operation

The LTC1380/LTC1393 are analog input multiplexers with an SMBus digital interface. The LTC1380 is a single-ended 8-to-1 multiplexer; the LTC1393 is a differential 4-to-1 mulitplexer. The LTC1380 operates on either bipolar or unipolar supplies, the LTC1393 operates on a single supply. The minimum  $V_{CC}$  supply for the LTC1380/LTC1393 is 2.7V. The maximum supply voltage ( $V_{CC}$  to  $V_{EE}$  for the LTC1380,  $V_{CC}$  for the LTC1393) should not exceed 14V. The multiplexer switches operate within the entire power supply range. The LTC1380  $V_{CC}$  and  $V_{EE}$  supplies can be offset such as 2.7V/-11V and 11V/-3V.

#### **Serial Interface**

The LTC1380/LTC1393 serial interface supports SMBus send byte protocol as shown below with two interface signals, SCL and SDA.

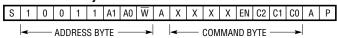

#### LTC1380 Send Byte Protocol

S | 1 | 0 | 0 | 1 | 0 | A1 | A0 | W | A | X | X | X | X | EN | C2 | C1 | C0 | A | P

#### LTC1393 Send Byte Protocol

S = SMBus START BIT

P = SMBus STOP BIT (THE FIRST STOP BIT AFTER A SUCCESSFUL COMMAND BYTE UPDATES THE MULTIPLEXER CONTROL LATCH)

A = ACKNOWLEDGE BIT FROM LTC1380/LTC1393

$\overline{W}$  = WRITE COMMAND BIT

A1, A0 = ADDRESS BITS

EN, C2, C1, C0 = MULTIPLEXER CONTROL BITS

A send byte protocol is initiated by the SMBus host with a start bit followed by a 7-bit address code and a write bit. Each slave compares the address code with its address. The send byte write bit is Low. The selected slaves then reply with an acknowledge bit by pulling the SDA line Low. Next, the host sends an 8-bit command byte. When the selected slave receives the whole command byte, it acknowledges and retains the command byte in the shift register. The host can terminate the serial transfer with a stop bit or communicate with another slave device with a repeat start. When a repeat start occurs but the slave is not selected, the command byte data is kept in the shift register but the multiplexer control is not updated. The multiplexer control latches the new command from the shift register on the first stop bit after a successful command byte transfer. This allows the host to synchronize several slave devices with a single stop bit. A1 and A0 select one of the four possible LTC1380/LTC1393 addresses as shown in Table 1. This allows up to four similar devices to share the same SMBus, expanding the multiplexer to 32 single-ended channels with the LTC1380; 16 differential channels with the LTC1393. The first stop bit after a successful send byte transfer will latch in the multiplexer control bits (EN, C2, C1 and C0) and initiate a break-before-make sequence.

## APPLICATIONS INFORMATION

Table 1. LTC1380/LTC1393 Address Selection

| A1 | A0 | LTC1380 | LTC1393 |

|----|----|---------|---------|

| 0  | 0  | 90H     | 98H     |

| 0  | 1  | 92H     | 9AH     |

| 1  | 0  | 94H     | 9CH     |

| 1  | 1  | 96H     | 9EH     |

SCL is the synchronizing clock generated by the host. SDA is the bidirectional data transfer between the host and the slave. The host initiates a start bit by dropping the SDA line from High to Low while the SCL is High. The stop bit is initiated by changing the SDA line from Low to High while SCL is High. All address, command and acknowledge signals must be valid and should not change while SCL is High. The acknowledge bit signals to the host the acceptance of a correct address byte or the command byte.

At  $V_{CC}$  supply above 2.7V, the SCL and SDA input threshold is typically 1V with an input hysteresis of 100mV. The typical SCL and SDA lines have either a resistive or current source pull-up at the host. The LTC1380/LTC1393 have an open-drain NMOS transistor at the SDA pin to sink 3mA below 0.4V during the slave acknowledge sequence. The address selection input A1 and A0 are TTL compatible at  $V_{CC} = 5V$ .

Both the LTC1380 and LTC1393 are compatible with the Philips/Signetics  $I^2C$  Bus interface. This 1V threshold for SCA and SDA should not pose an operational problem with  $I^2C$  applications.

The multiplexer switches are selected as shown in Table 2. Both the LTC1380 and the LTC1393 have an enable bit (EN). A Low disables all switches while a High enables the selected switch as programmed by bits C2, C1 and C0. A stop bit after a successful send byte sequence for LTC1380/LTC1393 will disable all switches before the new selected switch is connected.

**Table 2. Multiplexer Control Bits Truth Table**

| EN | C2 | C1 | CO | LTC1380 D <sub>0</sub><br>Channel Status | LTC1393 D <sub>0</sub> +, D <sub>0</sub> -<br>Channel Status |

|----|----|----|----|------------------------------------------|--------------------------------------------------------------|

| 0  | Χ  | Χ  | Χ  | All Off                                  | All Off                                                      |

| 1  | 0  | 0  | 0  | S0                                       | S0+, S0-                                                     |

| 1  | 0  | 0  | 1  | S1                                       |                                                              |

| 1  | 0  | 1  | 0  | S2                                       | S1+, S1-                                                     |

| 1  | 0  | 1  | 1  | S3                                       |                                                              |

| 1  | 1  | 0  | 0  | S4                                       | S2+, S2-                                                     |

| 1  | 1  | 0  | 1  | S5                                       |                                                              |

| 1  | 1  | 1  | 0  | S6                                       | S3+, S3 <sup>-</sup>                                         |

| 1  | 1  | 1  | 1  | S7                                       |                                                              |

## TYPICAL APPLICATIONS

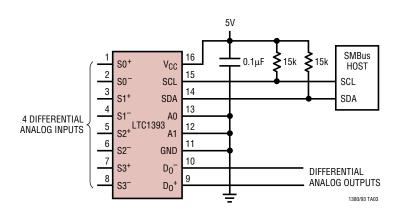

#### Simplified LTC1393 Application

# TYPICAL APPLICATIONS

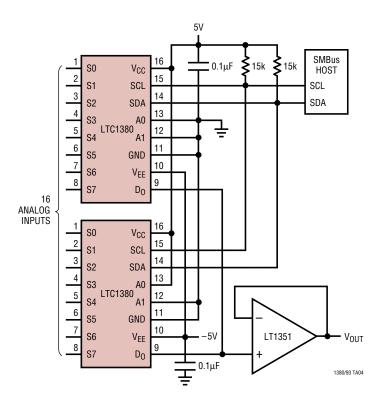

### **16-Channel Multiplexer with Buffer**

### **Programmable Gain Amplifier**

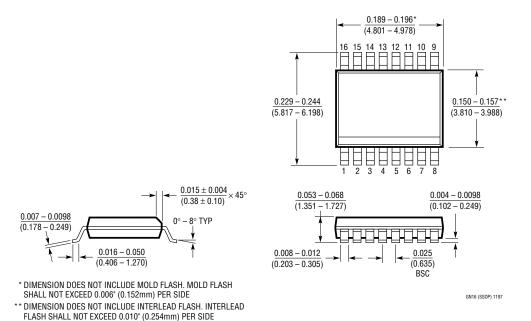

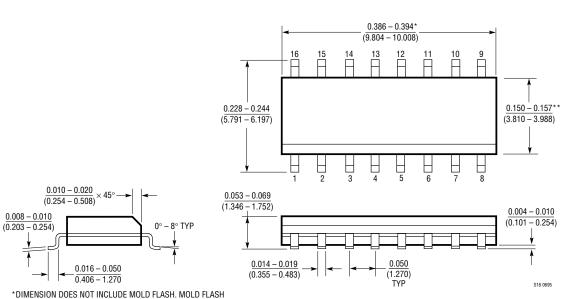

# PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

### **GN Package** 16-Lead Plastic SSOP (Narrow 0.150)

(LTC DWG # 05-08-1641)

# S Package

16-Lead Plastic Small Outline (Narrow 0.150) (LTC DWG # 05-08-1610)

SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

<sup>\*\*</sup>DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

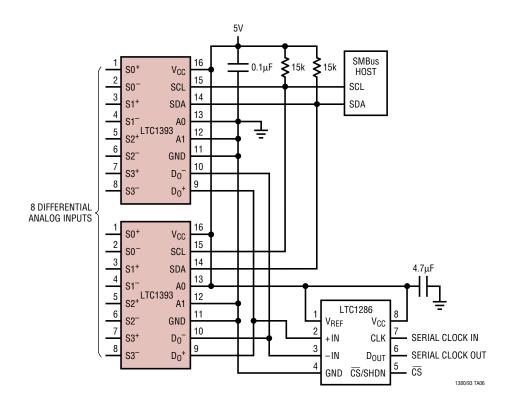

## TYPICAL APPLICATION

#### 8 Differential Channel Multiplexer with A/D Converter

## **RELATED PARTS**

| PART NUMBER               | DESCRIPTION                                                                      | COMMENTS                                                            |

|---------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------|

| LTC201A/LTC202/<br>LTC203 | Micropower, Low Charge Injection, Quad CMOS<br>Analog Switches with Data Latches | Each Channel is Independently Controlled                            |

| LTC221/LTC222             | Micropower, Low Charge Injection, Quad CMOS Analog Switches                      | Parallel Controlled with Data Latches                               |

| LTC1390/LTC1391           | 8-Channel, Analog Multiplexer with Serial Interface                              | 3V to ±5V in 16-Pin SO and PDIP                                     |

| LTC1623                   | High Side Switch with SMBus Interface                                            | Regulated On-Board Charge Pump Drives<br>External N-Channel MOSFETS |