#### Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to <a href="mailto:Fairchild\_questions@onsemi.com">Fairchild\_questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees

December 2014

# FAN8831 Sinusoidal Piezoelectric Actuator Driver with Step-Up DC-DC Converter

#### **Features**

#### Step-Up DC-DC Converter

- Integrated Step-up Power Switch up to 36 V

- Wide Operating Voltage Range of 2.7 to 5.5 V

- Adjustable Step-up Output Voltage

- Adjustable Step-up Current Limit

- Zero Current Detector (ZCD)

- Internal Soft-Start

- Built-in Protection Circuit

- Over Voltage Protection (OVP)

- Thermal Shutdown (TSD)

#### **Piezo Actuator Driver**

- Integrated Full-Bridge Switches (V<sub>DS</sub>=75 V)

- Digitally Implemented Sine Modulator

#### **Package Information**

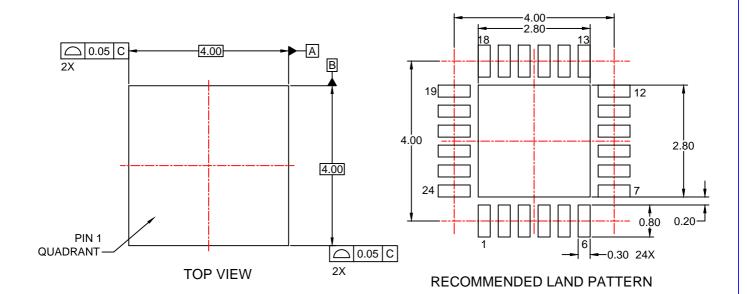

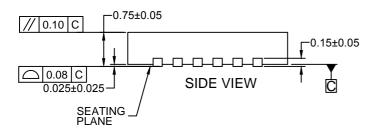

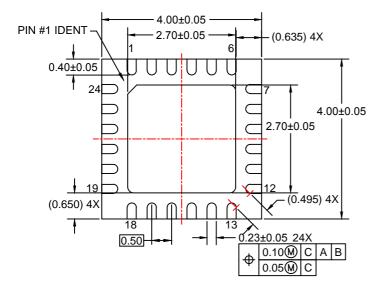

■ Small 4.0 mm × 4.0 mm MLP

# **Applications**

Piezo Actuator

#### Description

The FAN8831 is a single-chip piezoelectric actuator driver consisting of step-up DC-DC converter with integrated 36 V boost switch and a full-bridge output stage. The device is capable of driving a Piezo bi-directionally at 120 V peak-to-peak from a single 3 V lithium cell. The step-up DC-DC converter operates in Critical Conduction Mode (CRM) and is optimized to work in a coupled inductor configuration to provide output voltages in excess of 60 V. Over-voltage protection, over-current protection and thermal shutdown are all provided. An internal ready is used to enable the full-bridge gate driver when step-up DC-DC converter output voltage reaches the proper level with hysteresis.

The boost voltage is set using external resistors, and step-up current limit is programmable via the external resistor at OCP pin.

The output H-bridge features four integrated 75 V P and N-channel for sine wave drive of the Piezo actuator.

# **Ordering Information**

| Part Number | Operating<br>Temperature Range | Package      | Packing Method |

|-------------|--------------------------------|--------------|----------------|

| FAN8831MPX  | -40°C to +125°C                | 24-Lead, MLP | Tape & Reel    |

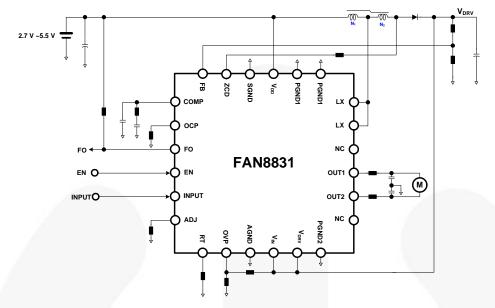

# **Application Diagram**

Figure 1. Typical Application Circuit for Piezo Actuator Driver

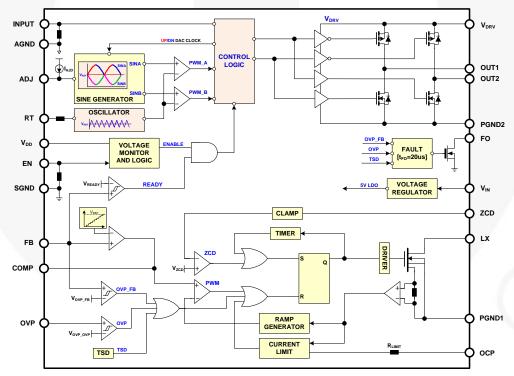

# **Internal Block Diagram**

Figure 2. Functional Block Diagram

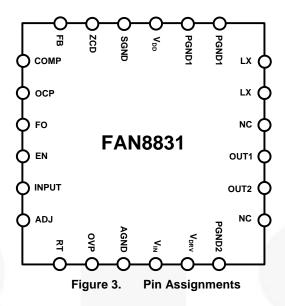

# **Pin Configuration**

# **Pin Definitions**

| Pin#   | Name            | Description                                                                                                                                                  |

|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,2    | PGND1           | Power Ground 1. It is connected to the source of the step-up switch.                                                                                         |

| 3      | $V_{DD}$        | Power supply of step-up DC-DC converter.                                                                                                                     |

| 4      | SGND            | Signal Ground. The signal ground for step-up DC-DC converter circuitry.                                                                                      |

| 5      | ZCD             | The input of the zero current detection.                                                                                                                     |

| 6      | FB              | Step-up DC-DC converter output voltage feedback input.                                                                                                       |

| 7      | COMP            | Output of the transconductance error amplifier.                                                                                                              |

| 8      | OCP             | Sets Step-up DC-DC converter current limit.                                                                                                                  |

| 9      | FO              | Fault Output.                                                                                                                                                |

| 10     | EN              | Enable pin to turn on and off the overall system. (Active Low Shutdown Mode).                                                                                |

| 11     | INPUT           | Logic input for sinusoidal waveform.                                                                                                                         |

| 12     | ADJ             | Output voltage adjust control pin. Connect to internal current source to change output voltage using an external resistor. Connect a small capacitor (1 nF). |

| 13     | RT              | Oscillator frequency control pin.                                                                                                                            |

| 14     | OVP             | Voltage sense input of Step-up DC-DC converter for Over-Voltage Protection.                                                                                  |

| 15     | AGND            | Analog Ground. The signal ground for full-bridge driver circuitry.                                                                                           |

| 16     | V <sub>IN</sub> | Power supply of 5 V LDO.                                                                                                                                     |

| 17     | $V_{DRV}$       | Power supply of full-bridge driver.                                                                                                                          |

| 18     | PGND2           | Power Ground 2. The power ground for full-bridge driver .                                                                                                    |

| 19     | NC              | Not Connected                                                                                                                                                |

| 20     | OUT2            | Output 2 for full-bridge driver.                                                                                                                             |

| 21     | OUT1            | Output 1 for full-bridge driver.                                                                                                                             |

| 22     | NC              | Not Connected                                                                                                                                                |

| 23, 24 | L <sub>X</sub>  | Switch Node. This pin is connected to the inductor.                                                                                                          |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol               |                                                           | Parame     | ter                                   | Min. | Max.                 | Unit |

|----------------------|-----------------------------------------------------------|------------|---------------------------------------|------|----------------------|------|

| V <sub>DRV</sub>     | DC Link Input Voltage Drain-Source Voltage of each MOSFET |            |                                       |      | 75                   | V    |

| V <sub>DD</sub>      | DC Supply Voltage for D                                   | OC-DC Conv | verter                                | -0.3 | 5.5                  | V    |

| V <sub>IN,DCDC</sub> | EN, INPUT, FB and CC                                      | MP to SGN  | D                                     | -0.3 | V <sub>DD</sub> +0.3 | V    |

| V <sub>IN</sub>      | DC Supply Voltage for LDO                                 |            |                                       | -0.3 | 75                   | V    |

| V <sub>LX</sub>      | LX to PGND                                                |            | -0.3                                  | 36   | V                    |      |

| П                    | Power Dissipation <sup>(2)</sup>                          |            | 1S0P with thermal vias <sup>(3)</sup> |      | 0.98                 | 14/  |

| P <sub>D</sub>       |                                                           |            | 1S2P with thermal vias <sup>(4)</sup> |      | 2.9                  | W    |

| 0                    | Thermal Resistance Junction-Air <sup>(2)</sup>            |            | 1S0P with thermal vias <sup>(3)</sup> | 1/   | 127                  | °C/M |

| $\theta_{JA}$        |                                                           |            | 1S2P with thermal vias <sup>(4)</sup> |      | 43                   | °C/W |

| T <sub>A</sub>       | Operating Ambient Temperature Range                       |            |                                       | -40  | 125                  | °C   |

| TJ                   | Operating Junction Temperature                            |            |                                       | -55  | 150                  | °C   |

| T <sub>STG</sub>     | Storage Temperature Range                                 |            |                                       | -55  | 150                  | °C   |

| ECD                  | Electrostatic Discharge                                   | Human Bo   | dy Model, JESD22-A114                 |      | 2                    | KV   |

| ESD                  | Capability                                                | Charged D  | Device Model, JESD22-C101             |      | 500                  | V    |

#### Notes:

- 1. All voltage values, except differential voltages, are given with respect to SGND, AGND and PGND pin.

- 2. JEDEC standard: JESD51-2, JESD51-3. Mounted on 76.2×114.3×1.6mm PCB (FR-4 glass epoxy material).

- 3. 1S0P with thermal vias: one signal layer with zero power plane and thermal vias.

- 4. 1S2P with thermal vias: one signal layer with two power plane and thermal vias.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol          | Parameter                               | Min. | Тур. | Max. | Unit |

|-----------------|-----------------------------------------|------|------|------|------|

| $V_{DRV}$       | Supply Voltage for Full-Bridge Driver   | 30   |      | 60   | V    |

| $V_{LX}$        | Boost Switch Voltage                    | 10   |      | 30   | V    |

| $V_{DD}$        | Operating Voltage for DC-DC Converter   | 2.7  | 3.0  | 3.3  | V    |

| V <sub>IN</sub> | Operating Voltage for Voltage Regulator | 10   |      | 60   | V    |

| Rocp            | Current Limit Control Resistor          | 7.0  |      | 150  | kΩ   |

#### **Electrical Characteristics**

$V_{DD}=3.0$  V,  $V_{IN}=15.0$  V,  $V_{DRV}=60$  V,  $R_{T}=70$  K $\Omega$  and  $T_{A}=-40$ °C to +125°C. Typical values  $T_{A}=25$ °C, unless otherwise specified.

| Symbol                | Parameter                                            | Conditions                                            | Min.  | Тур. | Max. | Unit |

|-----------------------|------------------------------------------------------|-------------------------------------------------------|-------|------|------|------|

| Power Sup             | ply Section                                          |                                                       | •     |      |      | •    |

| $I_{Q,DD}$            | Quiescent Current for V <sub>DD</sub> <sup>(5)</sup> | V <sub>EN</sub> =V <sub>COMP</sub> =V <sub>DD</sub> , |       | 700  | 1200 | μA   |

| I <sub>Q,IN</sub>     | Quiescent Current for V <sub>IN</sub>                | V <sub>FB</sub> =1.0 V                                |       | 300  | 500  | μΑ   |

| I <sub>Q,DRV</sub>    | Quiescent Current for V <sub>DRV</sub>               | Device not switching                                  |       | 200  | 300  | μA   |

| I <sub>SD,DD</sub>    | Shutdown Current for V <sub>DD</sub>                 |                                                       |       |      | 1    | μA   |

| I <sub>SD,IN</sub>    | Shutdown Current for V <sub>IN</sub>                 | $V_{EN}=0$ V,<br>$V_{DD}=V_{IN}=V_{DRV}=3$ V          |       |      | 1    | μA   |

| I <sub>SD,DRV</sub>   | Shutdown Current for V <sub>DRV</sub>                | V DD- V IN- V DRV -O V                                |       | 5    | 10   | μA   |

| V <sub>DDSTART</sub>  | Start Threshold Voltage                              |                                                       | 2.6   | 2.7  | 2.8  | V    |

| V <sub>DDUVHYS</sub>  | V <sub>DD</sub> UVLO Hysteresis Voltage              |                                                       | 0.1   | 0.2  | 0.3  | V    |

| Error Ampl            | ifier Section                                        |                                                       |       |      |      |      |

| $V_{FB}$              | Feedback Reference Voltage                           | T <sub>A</sub> =25°C                                  | 0.99  | 1.0  | 1.01 | V    |

| I <sub>FB</sub>       | FB pin Bias Current                                  | V <sub>FB</sub> =0 V ~ 2 V                            |       |      | 1    | μA   |

| $\Delta V_{FB1}$      | Feedback Voltage Line Regulation <sup>(6)</sup>      | 2.7 V < V <sub>DD</sub> < 5 V                         |       | 0.5  | 1.5  | %/V  |

| Gm                    | Transconductance                                     | T <sub>A</sub> =25°C                                  |       | 800  |      | μmho |

| Zero Curre            | nt Detect Section                                    |                                                       |       |      |      |      |

| $V_{ZCD}$             | Input Voltage Threshold <sup>(7)</sup>               |                                                       | 1.65  | 1.83 | 2.00 | V    |

| $V_{CLAMPH}$          | Input High Clamp Voltage                             | I <sub>DET</sub> =2.3 mA                              | 3.0   | 3.5  | 4.0  | V    |

| $V_{CLAMPL}$          | Input Low Clamp Voltage                              | I <sub>DET</sub> = -2.3 mA                            | -0.30 | 0.12 | 0.50 | V    |

| I <sub>ZCD,SR</sub>   | Source Current Capability                            |                                                       |       |      | -2.3 | mA   |

| I <sub>ZCD,SK</sub>   | Sink Current Capability                              |                                                       |       |      | 2.3  | mA   |

| t <sub>ZCD,D</sub>    | Delay From ZCD to Output Turn-On <sup>(7)</sup>      |                                                       |       | 50   | 200  | ns   |

| Maximum (             | On-Time Section                                      |                                                       |       |      |      |      |

| t <sub>ON,MAX</sub>   | Maximum On-Time                                      |                                                       | 15    | 25   | 35   | μs   |

| Restart / M           | aximum Switching Frequency Limit Section             |                                                       |       |      |      |      |

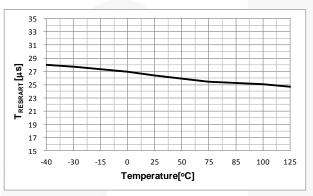

| t <sub>RST</sub>      | Restart Timer                                        |                                                       | 15    | 25   | 35   | μs   |

| f <sub>MAX</sub>      | Maximum Switching Frequency <sup>(7)</sup>           |                                                       |       | 900  | 1000 | KHz  |

| Soft-Start 7          | Fimer Section                                        |                                                       | 1     |      |      |      |

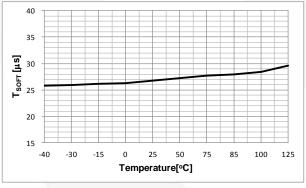

| tss                   | Internal Soft-Start                                  |                                                       | 16    | 28   | 40   | ms   |

| Current Lin           | nit Comparator Section                               |                                                       | •     |      |      | •    |

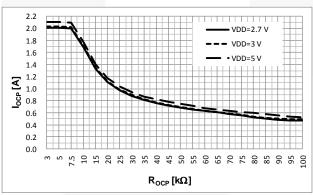

|                       | 0007:0                                               | R <sub>OCP</sub> =3.3 KΩ, V <sub>DD</sub> =3.3 V      | 1.85  | 2.00 | 2.15 | Α    |

| I <sub>OCP</sub>      | OCP Trip Current                                     | R <sub>OCP</sub> =22 KΩ, V <sub>DD</sub> =3.3 V       | 0.9   | 1.0  | 1.1  | Α    |

| t <sub>CS BLANK</sub> | Comparator Leading-Edge Blanking Time <sup>(7)</sup> |                                                       | 80    | 130  | 180  | ns   |

#### Notes:

5. This is the VDD current consumed when active but not switching. Does not include gate-drive current

$$\frac{\Delta V_{OUT}}{\Delta V_{IN}} \times \frac{1}{V_{OUT}}$$

- 6. The line regulation is calculated based on  $\overline{ \Delta V_{{\scriptscriptstyle I\!N}}}$

- 7. This parameter, although guaranteed by design, is not tested in production.

#### **Electrical Characteristics**

$V_{DD}$ =3.0 V,  $V_{IN}$ =15.0 V,  $V_{DRV}$ =60 V,  $R_T$ =70 K $\Omega$  and  $T_A$ =-40°C to +125°C. Typical values  $T_A$ =25°C, unless otherwise specified.

| Symbol                | Parameter                                            | Conditions                                   | Min. | Тур. | Max. | Unit |

|-----------------------|------------------------------------------------------|----------------------------------------------|------|------|------|------|

| Step-Up Sw            | vitch Section                                        | -                                            |      | · ·  | l    | u e  |

| R <sub>DSON</sub>     | N-Channel On Resistance                              | V <sub>DD</sub> =3.3 V, T <sub>A</sub> =25°C |      | 0.2  | 0.5  | Ω    |

| I <sub>LK_LX</sub>    | LX Leakage Current                                   | V <sub>LX</sub> =36 V                        |      |      | 1.0  | μA   |

| Oscillator S          | Section                                              |                                              | •    | •    | •    | •    |

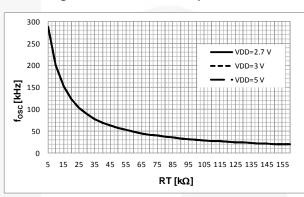

| t                     | On another a Farmana and                             | R <sub>T</sub> =58 KΩ                        | 40   | 50   | 60   | KHz  |

| fosc                  | Operating Frequency                                  | R <sub>T</sub> =121 KΩ                       | 20   | 25   | 30   | KHz  |

| Logic (EN a           | and INPUT) Section                                   |                                              | •    | •    |      | •    |

| V <sub>INPUT+</sub>   | INPUT Logic High Threshold Voltage                   |                                              | 1.34 |      |      | V    |

| V <sub>INPUT</sub> -  | INPUT Logic Low Threshold Voltage                    |                                              |      |      | 0.5  | V    |

| I <sub>INPUT</sub>    | Input Low Current for INPUT and EN                   | V <sub>EN</sub> =0 V                         |      |      | 1    | μA   |

| I <sub>INPUT+</sub>   | Input High Current for INPUT and EN                  | V <sub>EN</sub> =V <sub>DD</sub>             | 8    | 12   | 16   | μA   |

| RINPUT                | Input Logic Pull-Down Resistance                     | V <sub>EN</sub> = V <sub>INPUT</sub> =3 V    |      | 250  | 375  | ΚΩ   |

| f <sub>INPUT</sub>    | Input Logic Operating Frequency <sup>(8)</sup>       |                                              | 20   |      | 1000 | Hz   |

| Full-Bridge           | Switch Section                                       |                                              |      |      |      |      |

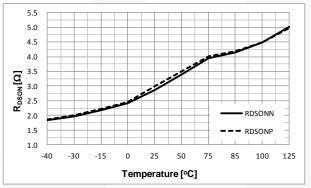

| R <sub>DS,ONP</sub>   | Output Upper-Side On Resistance                      | T <sub>A</sub> =25°C                         |      | 3.0  | 5.0  | Ω    |

| R <sub>DS,ONN</sub>   | Output Low-Side On Resistance                        | T <sub>A</sub> =25°C                         |      | 3.0  | 5.0  | Ω    |

| Output Cor            | ntrol Section                                        |                                              |      | V.   |      |      |

| $V_{ADJ,MAX}$         | Analog Output Control Maximum Voltage <sup>(8)</sup> | V <sub>DRV</sub> =100% of Target             |      | 1.0  |      | V    |

| $V_{ADJ,MIN}$         | Analog Output Control Minimum Voltage <sup>(8)</sup> |                                              |      | 0.1  |      | V    |

| I <sub>ADJ+</sub>     | Internal Current Source for ADJ Pin                  | T <sub>A</sub> =25°C                         | 9    | 10   | 11   | μA   |

| Protection            | (Ready, OVP and TSD)                                 | 7                                            |      |      |      |      |

| $V_{READY}$           | Output Ready Threshold Voltage                       |                                              | 0.75 | 0.80 | 0.85 | V    |

| HY <sub>READY</sub>   | Output Ready Hysteresis                              |                                              | 1    | 0.2  |      | V    |

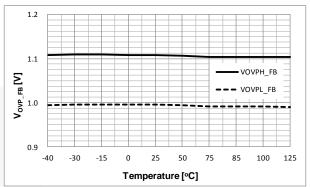

| V <sub>OVP_FB</sub>   | OVP Threshold Voltage at FB Pin                      |                                              | 1.05 | 1.10 | 1.15 | V    |

| HY <sub>OVP_FB</sub>  | OVP Hysteresis Voltage at FB Pin                     |                                              | .//  | 0.1  | 7    | V    |

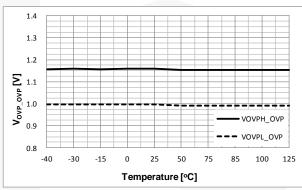

| V <sub>OVP_OVP</sub>  | OVP Threshold Voltage at OVP Pin                     |                                              | 1.10 | 1.15 | 1.20 | V    |

| HY <sub>OVP_OVP</sub> | OVP Hysteresis Voltage at OVP Pin                    |                                              |      | 0.15 |      | V    |

| T <sub>SD</sub>       | Thermal Shutdown Temperature <sup>(8)</sup>          |                                              |      | 150  |      | °C   |

| T <sub>HYS</sub>      | Hysteresis Temperature of TSD <sup>(8)</sup>         |                                              |      | 50   |      | °C   |

| T <sub>FO</sub>       | Fault Output Duration                                |                                              |      | 20   | 30   | μs   |

| $V_{FOL}$             | Fault Output Low Level Voltage                       | R <sub>PU</sub> =50 KΩ, V <sub>PU</sub> =3 V |      | 0.1  | 0.4  | V    |

#### Note:

8. This parameter, although guaranteed by design, is not tested in production.

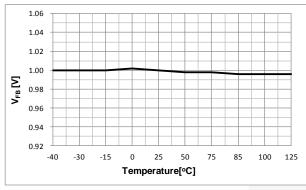

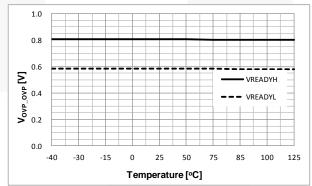

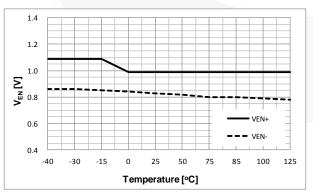

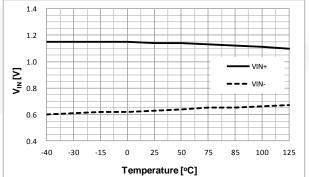

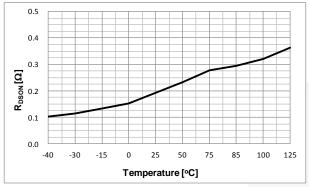

# **Typical Performance Characteristics**

Figure 4. Reference Voltage vs. Temperature

3.0

2.8

2.6

2.2

-30 -15

V<sub>VDD,UVLO</sub> [V]

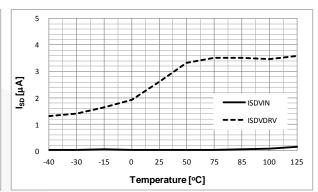

Figure 5. Shutdown Current for  $V_{DRV}$  &  $V_{IN}$  vs. Temperature

Temperature [°C]

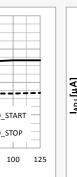

Figure 6. V<sub>DD</sub> UVLO vs. Temperature

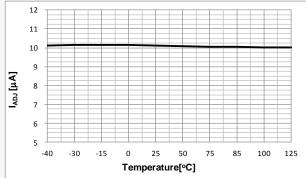

Figure 7. ADJ Current vs. Temperature

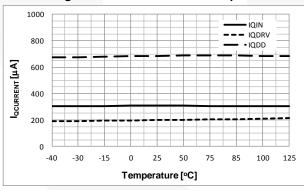

Figure 8. Quiescent Current for V<sub>DD</sub>, V<sub>DRV</sub>, & V<sub>IN</sub> vs. Temperature

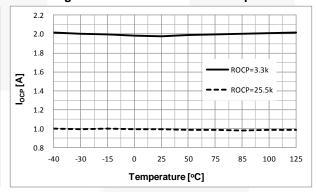

Figure 9. OCP Current vs. Temperature

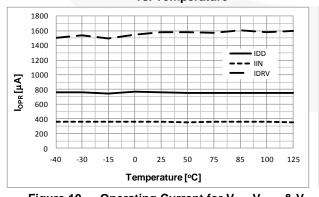

Figure 10. Operating Current for  $V_{DD},\,V_{DRV},\,\&\,V_{IN}$  vs. Temperature

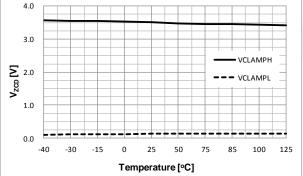

Figure 11. ZDC Clamp Voltage vs. Temperature

# **Typical Performance Characteristics**

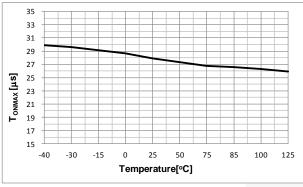

Figure 12. Maximum On-Time vs. Temperature

Figure 13. Fist OVP (FB) vs. Temperature

Figure 14. Restart-Time vs. Temperature

Figure 15. Second (OVP) vs. Temperature

Figure 16. Soft-Start Time vs. Temperature

Figure 17. Ready Voltage vs. Temperature

Figure 18. Enable (EN) Threshold Voltage vs. Temperature

Figure 19. INPUT Threshold Voltage vs. Temperature

Downloaded from Arrow.com.

# **Typical Performance Characteristics**

Figure 20. Boost Switch R<sub>DSON</sub> vs. Temperature

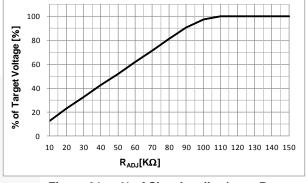

Figure 21. % of Sine Amplitude vs. R<sub>ADJ</sub>

Figure 22. Full-Bridge Switch R<sub>DSON</sub> vs. Temperature

Figure 23. fosc vs. RT

Figure 24. IOCP vs. ROCP

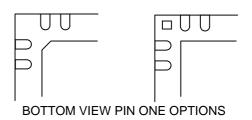

**BOTTOM VIEW**

#### NOTES:

- A. CONFORMS TO JEDEC REGISTRATION MO-220, VARIATION WGGD-6.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 2009.

- D. LAND PATTERN IPC REFERENCE : QFN50P400X400X80-25W6N.

- E. DRAWING FILENAME: MKT-MLP24Erev5.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hol

Phone: 81-3-5817-1050

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative