# **Automotive Power Management Device**

#### **Features**

- Low-cost, single-chip solution for Automotive Power Management

- Supports low-power Sleep Mode; wakeup due to:

- LIN bus / ECL activity

- Local event (e.g. ON switch)

- MOST Network optical/electrical activity

- Switch-To-Power (STP) event

- Power-supply monitoring:

- Configurable voltage trip points

- Configurable wakeup from Sleep Mode voltage

- Integrated LIN transceiver

- LIN 2.0 compliant

- Transmission rates up to 20 kHz

- MOST Electrical Control Line (ECL) compliant

- Adjustable slew rate for reduced EMI

- Over-temperature and low-voltage protection

- Short-circuit protection

- Optional TXD timeout (MOST ECL compliant)

- Optional I<sup>2</sup>C Control Port for configuration/status

- Programmable Precision Reset Generator

- 3.3 V MicroPower Regulator for continuous power requirements (e.g. Rx PHY, EOC/FOR, INIC persistent memory)

- Temperature monitoring with programmable alerts

- User available data storage (while in Sleep Mode)

- User available One-Time Programmable (OTP) permanent data storage

- Direct support for MOST INIC power status pins

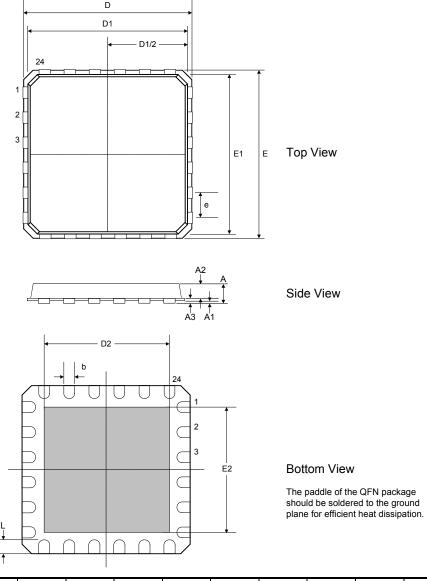

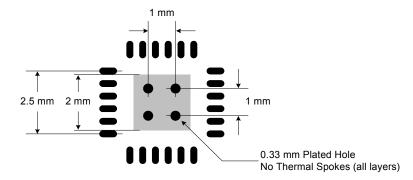

- 24-pin 4x4 mm<sup>2</sup> QFN package with exposed paddle

- Temperature range: -40 °C to +110 °C

#### **General Description**

The MPM85000 is an automotive system power management device intended for integration into an *Electrical Control Unit* (ECU). The MPM85000 includes a very low-power *Sleep Mode*, supporting wakeup transitions to *Active Mode* due to multiple signals. Wakeup event signal detection and qualification includes both glitch protection and power supply validation. Qualified inputs can generate interrupts for an *External Host Controller* (EHC).

The MPM85000 supports all MOST speed grades (MOST25, MOST50, and MOST150). In addition to system power management, other MOST-related features are supported, including: direct connection to power status inputs of MOST *Intelligent Network Interface Controllers* (INICs), MOST50 electrical network (ePHY) activity detection, and ECL support.

In Active Mode, the MPM85000 includes a fault-tolerant keep-alive hardware signal (or software bit) that can be used by an external device to keep power enabled until the application is ready to power-down. The MPM85000 also provides continuous monitoring of the application battery voltage and ECU temperature, and can alert the EHC when user-programmed thresholds are crossed.

For robust fault tolerance, stuck wakeup events can be ignored, allowing the MPM85000 to revert to *Sleep Mode*. The MPM85000 detects recovery from stuck conditions and re-enables a signal's ability to wakeup the device.

# **Ordering Information**

| Order Number | Package                                               |

|--------------|-------------------------------------------------------|

| MPM85000AMT  | 24-pin QFN (Lead-Free, RoHS Compliant), Tray          |

| MPM85000AMR  | 24-pin QFN (Lead-Free, RoHS Compliant), Tape and Reel |

This table represents valid part numbers at the time of printing and may not represent parts that are currently available. For the latest list of valid ordering numbers for this product, please contact the nearest sales office.

### **Further Information**

For more information on SMSC automotive products, including integrated circuits, software, and MOST development tools and modules, visit our web site: <a href="http://www.smsc-ais.com">http://www.smsc-ais.com</a>. Direct contact information is available at: <a href="http://www.smsc-ais.com/offices">http://www.smsc-ais.com/offices</a>.

#### **SMSC Europe GmbH**

Bannwaldallee 48 D-76185 Karlsruhe Germany

#### **SMSC**

80 Arkay Drive Hauppauge, New York 11788 USA

# **Technical Support**

Contact information for technical support is available at: <a href="http://www.smsc-ais.com/contact">http://www.smsc-ais.com/contact</a>.

# Legend

Copyright © 2012 SMSC. All rights reserved.

Ensure that all information within a document marked as 'Confidential' or 'Confidential Controlled Access' is handled solely in accordance with the agreement pursuant to which it is provided, and is not reproduced or disclosed to others without the prior written consent of SMSC. The confidential ranking of a document can be found in the footer of every page. This document supersedes and replaces all information previously supplied. The technical information in this document loses its validity with the next edition. Although the information is believed to be accurate, no responsibility is assumed for inaccuracies. Specifications and other documents mentioned in this document are subject to change without notice. SMSC reserves the right to make changes to this document and to the products at any time without notice. Neither the provision of this information nor the sale of the described products conveys any licenses under any patent rights or other intellectual property rights of SMSC or others. There are a number of patents and patents pending on the MOST technology and other technologies. No rights under these patents are conveyed without any specific agreement between the users and the patent owners. The products may contain design defects or errors known as anomalies, including but not necessarily limited to any which may be identified in this document, which may cause the product to deviate from published descriptions. Anomalies are described in errata sheets available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an officer of SMSC will be fully at your own risk. TrueAuto is a trademark and Medial B, SMSC and MOST are registered trademarks of Standard Microsystems Corporation ("SMSC"). Other names mentioned may be trademarks of their respective holders.

The Microchip name and logo, and the Microchip logo are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

### Conventions

Within this manual, the following abbreviations and symbols are used to improve readability.

| Example                 | Description                                                                                                                                                    |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT                     | Name of a single bit within a field                                                                                                                            |

| FIELD.BIT               | Name of a single bit (BIT) in FIELD                                                                                                                            |

| xy                      | Range from x to y, inclusive                                                                                                                                   |

| BITS[m:n]               | Groups of bits from m to n, inclusive                                                                                                                          |

| PIN                     | Pin Name                                                                                                                                                       |

| msb, Isb                | Most significant bit, least significant bit                                                                                                                    |

| MSB, LSB                | Most significant byte, least significant byte                                                                                                                  |

| zzzzb                   | Binary number (value zzzz)                                                                                                                                     |

| 0xzzz                   | Hexadecimal number (value zzz)                                                                                                                                 |

| zzh                     | Hexadecimal number (value zz)                                                                                                                                  |

| rsvd                    | Reserved memory location. Must write 0, read value indeterminate                                                                                               |

| code                    | Instruction code, or API function or parameter                                                                                                                 |

| Multi Word Name         | Used for multiple words that are considered a single unit, such as:<br>Resource Allocate message, or Connection Label, or Decrement Stack Pointer instruction. |

| Section Name            | Section or Document name.                                                                                                                                      |

| VAL                     | Over-bar indicates active low pin or register bit                                                                                                              |

| Х                       | Don't care                                                                                                                                                     |

| <parameter></parameter> | <> indicate a Parameter is optional or is only used under some conditions                                                                                      |

| {,Parameter}            | Braces indicate Parameter(s) that repeat one or more times.                                                                                                    |

| [Parameter]             | Brackets indicate a nested Parameter. This Parameter is not real and actually decodes into one or more real parameters.                                        |

## **TrueAuto**™

TrueAuto is SMSC's automotive quality process. It has proven its ability to deliver leading-edge quality and services for IC device products to fulfill the needs of the most demanding automotive customers. TrueAuto is a proven total automotive-grade quality approach. TrueAuto IC device robustness begins with SMSC's design for reliability techniques within the silicon IC itself: automotive-grade robustness and testability are designed into the IC. Once available in silicon, the IC is fully-characterized and qualified over a multitude of operating parameters to prove quality under the harshest conditions. In this, SMSC's TrueAuto approach significantly exceeds the usual automotive reliability standards and customer- specific requirements and goes far beyond the stress tests prescribed by the AEC-Q100 specifications. During the fabrication of TrueAuto products, extensive technologies and processes, such as enhanced monitors are used in order to continuously drive improvements in accordance with SMSC's zero Defects per Million (DPM) goals.

# **TABLE OF CONTENTS**

| 1  | OVE  | RVIEW              |                                                     | 6   |

|----|------|--------------------|-----------------------------------------------------|-----|

|    | 1.1  | Function           | nal Blocks                                          | 7   |

|    | 1.2  |                    | onnection Examples                                  |     |

| 2  | PINC | DUT                |                                                     | 11  |

| _  | 2.1  |                    | ist                                                 |     |

|    | 2.2  |                    |                                                     |     |

|    | 2.3  |                    | ent Schematics for Pins                             |     |

| 3  |      | •                  | NAL MODES                                           |     |

|    |      | _                  | MONITORS                                            | _   |

| 4  |      |                    |                                                     |     |

|    | 4.1  | _                  | Pin                                                 |     |

| _  | 4.2  |                    | d VBATT_F Pin                                       |     |

| 5  | ACT  | IVITY D            | ETECTORS                                            | 26  |

|    | 5.1  |                    | Activity Detection                                  |     |

|    | 5.2  | STATUS             | S Pin Activity Detection                            | 28  |

|    | 5.3  |                    | ctivity Detection                                   |     |

|    | 5.4  | ON_SW              | Pin Activity Detection                              | 30  |

| 6  | LIN  | TRANS              | CEIVER                                              | 32  |

|    | 6.1  | Short-To           | o-Power Detector                                    | 34  |

|    | 6.2  | Optional           | I Timeout Condition                                 | 36  |

|    | 6.3  | Thermal            | Shutdown Condition                                  | 36  |

| 7  | RES  | ET GEN             | IERATOR AND VDDP                                    | 37  |

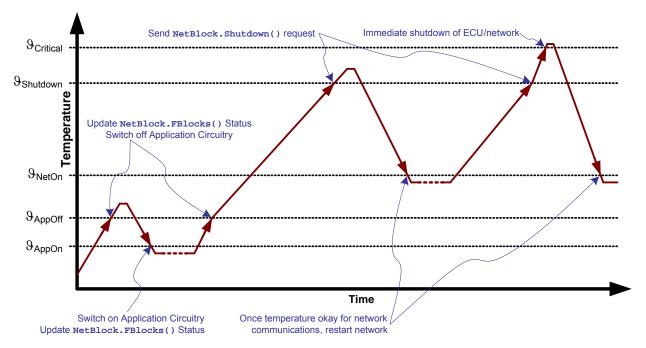

| 8  | TEM  | PERAT              | URE SENSOR                                          | 38  |

| _  | 8.1  |                    | mplementation                                       |     |

| 9  | POV  |                    | NAGEMENT PORT                                       |     |

|    |      |                    |                                                     |     |

| 10 |      |                    | PORT                                                |     |

|    | 10.1 | •                  | t Events                                            |     |

|    | 10.2 | •                  | rs                                                  |     |

|    |      | 10.2.1             | Interrupt Register (IR)                             |     |

|    |      | 10.2.2<br>10.2.3   | Status Register (SR)Line Status Register (LSR)      |     |

|    |      | 10.2.3             | Reset Delay Register (RD)                           |     |

|    |      | 10.2.5             | VPRO Comparator Threshold Register (VCT)            |     |

|    |      | 10.2.6             | LIN Control Register (LC)                           |     |

|    |      | 10.2.7             | Override Register (OR)                              |     |

|    |      | 10.2.8             | Configuration Register (CR)                         |     |

|    |      | 10.2.9             | Mask Register (MR)                                  | 55  |

|    |      | 10.2.10            | Temperature Sensor Registers                        |     |

|    |      | 10.2.11            | Temperature Limit Registers                         |     |

|    |      | 10.2.12            | Initial Wakeup Event Register (IWE)                 |     |

|    |      | 10.2.13            | Data Registers                                      |     |

|    |      | 10.2.14<br>10.2.15 | OTP Control Registers Product Information Registers |     |

|    |      | 10.2.13            | i roduct illioittation registers                    | 0 1 |

### MPM85000

| 11 | ELE(  | CTRICAL CHARACTERISTICS                    | 62 |

|----|-------|--------------------------------------------|----|

|    | 11.1  | Absolute Maximum Ratings                   | 62 |

|    | 11.2  | Guaranteed Operating Conditions            |    |

|    | 11.3  | DC Characteristics                         |    |

|    | 11.4  | AC Characteristics                         | 64 |

|    | 11.5  | Activity Detectors                         | 64 |

|    | 11.6  | Temperature Sensor                         | 65 |

|    | 11.7  | Voltage Monitors                           | 65 |

|    | 11.8  | Reset Generator                            |    |

|    | 11.9  | MicroPower Regulator                       |    |

|    |       | Control Port                               |    |

|    | 11.11 | LIN Transceiver                            |    |

|    |       | 11.11.1 General                            |    |

|    |       | 11.11.2 DC Characteristics                 |    |

|    |       | 11.11.3 AC Characteristics                 | /1 |

| 12 | PAC   | KAGE OUTLINE (QFN24)                       | 72 |

| 13 | APPI  | LICATION INFORMATION                       | 73 |

|    | 13.1  | Communication Interface                    | 74 |

|    | 13.2  | EHC POR From MPM85000                      | 75 |

|    | 13.3  | Power Supply Arrangements                  | 76 |

|    |       | 13.3.1 MOST150 Network/Power Configuration |    |

|    |       | 13.3.2 MOST50 Network/Power Configuration  |    |

|    | 40.4  | 13.3.3 MOST25 Network/Power Configuration  |    |

|    | 13.4  | ECL/LIN Support                            |    |

|    | 13.5  | STP Event Detection                        |    |

|    | 13.6  | Layout Guidelines                          |    |

|    |       | 13.6.2 LIN/ECL Input Protection            |    |

|    |       | 13.6.3 Thermal Considerations              |    |

| ΔΕ | PENI  | DIX A: REGISTER SUMMARY                    |    |

|    |       |                                            |    |

|    |       | DIX B: REFERENCES                          |    |

| AF | PENI  | DIX C: REVISION HISTORY                    | 86 |

| AF | PENI  | DIX D: LIST OF TABLES                      | 89 |

| ΑF | PENI  | DIX E: LIST OF FIGURES                     | 90 |

# 1 Overview

The MPM85000 is a low-cost, feature-rich *Automotive Power Management Device* (APMD) intended for integration into an *Electrical Control Unit* (ECU). A number of different power architectures exist for automotive ECU systems. In modern automotive infotainment systems, the key-switch position rarely directly controls ECU power, as doing so prohibits advanced network startup and shutdown features (e.g. recalling/saving critical system parameters). Therefore, modern automotive infotainment systems require some type of power management implementation. Although the MPM85000 works well in key-switch managed systems, its feature set is suitable for more advanced power management implementations.

In a networked system with multiple ECUs, continuous battery power is generally supplied to all ECUs, each of which supports a low-power mode of operation in which a majority of the ECU is powered off. In this low-power mode, only the circuitry needed to enable power to the rest of the ECU is active. This power architecture allows the network to power down cleanly, and permits more than one ECU to restore the network to a full-power mode of operation. Power management system architectures are more fully described in the MOST INIC Hardware Concepts Technical Bulletin [1].

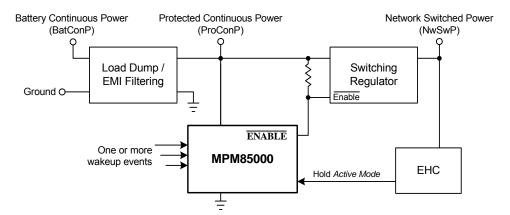

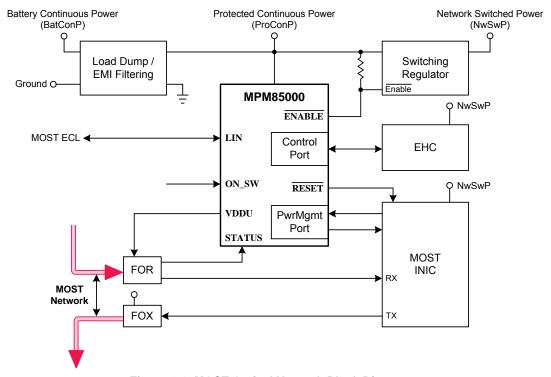

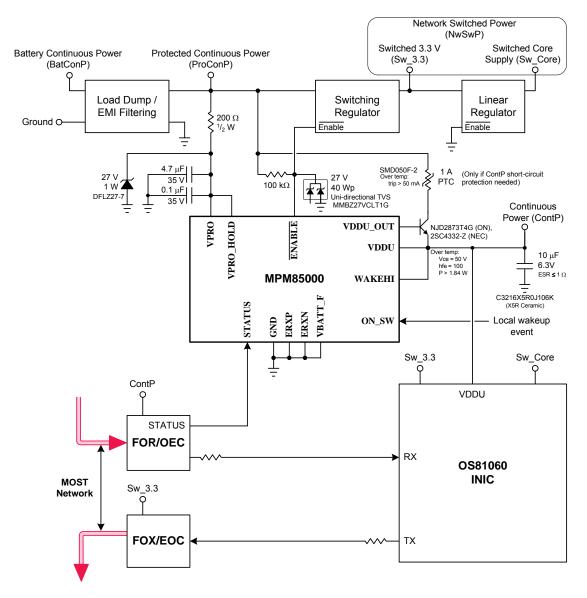

To support modern power architectures, the MPM85000 supports two modes of operation: a very low-power *Sleep Mode* and an *Active Mode*. When in *Sleep Mode*, the MPM85000 uses multiple activity detectors to monitor different signals that may indicate the ECU should wakeup from *Sleep Mode*. For robustness, all activity detectors have glitch filters to minimize false wakeup events and the MPM85000 does not exit *Sleep Mode* unless the power supply voltage is within the proper range. Once an activity signal is qualified (and the power supply is valid), the MPM85000 enters *Active Mode* and drives the ENABLE pin low. The ENABLE pin is typically connected to switching-mode power regulators that power the rest of the ECU, as illustrated in Figure 1-1. The MPM85000 also includes a precision reset generator that can be used as an ECU-wide power-on reset (POR) signal.

Figure 1-1: Typical ECU Power Arrangement

Once the MPM85000 transitions to *Active Mode*, the ECU is fully powered and the *External Host Controller* (EHC) can keep the MPM85000 in *Active Mode* until the device is ready to be powered down. This MPM85000 "hold" *Active Mode* feature is fault-tolerant and supports either a hardware signal or a register bit. If the MPM85000 transitions to *Active Mode* and the EHC never responds, the MPM85000 returns to *Sleep Mode* on its own to keep from draining the battery. If the EHC is reset due to a fault condition, the MPM85000 delays entering *Sleep Mode* to allow the EHC time to recover from the reset condition.

The MPM85000 can operate without EHC configuration or interaction (defined as stand-alone operation). However, additional features are available when an EHC is connected to the MPM85000 Control Port, including power supply monitoring and status information, system temperature monitoring and status information, the ability to change the voltage monitoring thresholds, and also the ability to adjust the reset active time period.

The MPM85000 meets the power management requirements of the MOST Network [2] and includes a number of features specifically designed to support MOST Networks. With respect to wakeup event options, the MPM85000 is designed to wakeup due to MOST optical network activity (from the fiber-optic receiver/optical-electrical converter, FOR/OEC), and also can wakeup due to MOST50 electrical network activity. The integrated LIN transceiver can also wakeup the MPM85000 from *Sleep Mode* as a result of standard LIN communications [3], or activity on a MOST Network Electrical Control Line (ECL) [4]. The MPM85000 also supports local wakeup events through the ON\_SW pin, and can support diagnostic *Switch-To-Power* (STP) event detection, when enabled.

An on-chip 3.3 V MicroPower regulator supplies constant power to ECU circuitry that requires power during *Sleep Mode* (e.g. FOR/OEC, Rx PHY). When used with MOST ROM INIC devices, the MicroPower regulator provides *Sleep Mode* power for their persistent memory requirements.

Utilizing the MPM85000 for ECU power management simplifies design requirements and saves PCB real estate usage, supporting faster development time and lower overall cost. In addition, many fault-tolerant features are available in ECU designs that include the MPM85000 which do not exist in discrete solutions.

### 1.1 Functional Blocks

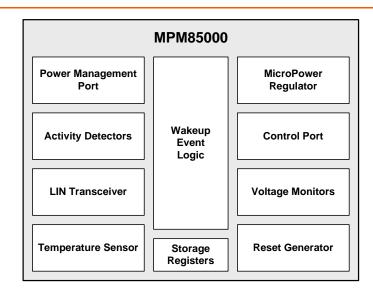

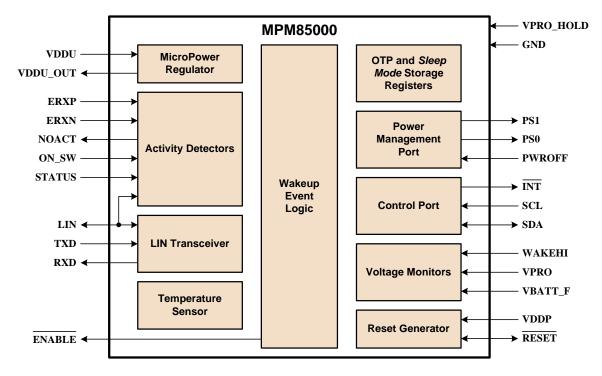

The MPM85000 features can be divided into the following functional blocks, as shown in Figure 1-2:

- Wakeup Event Logic Provides an output for controlling application regulators (wakeup from Sleep Mode) based on configurable parameters and actual conditions detected by other MPM85000 functional blocks. Supports the two MPM85000 operational modes: Sleep Mode and Active Mode.

- Power Management Port Intended for direct connection to a MOST INIC or an EHC.

- Status outputs report STP events and voltage information from the internal voltage monitor

- Keep-alive input for a controlled node shutdown (forces the wakeup event logic to hold the power control output active until the application is ready to power down)

- **Activity Detectors** Used to detect and qualify activity on various inputs.

- LIN Transceiver activity detection / MOST ECL activity detection

- MOST50 electrical network (ePHY) activity detection

- MOST25/MOST150 optical network (FOR/EOC, Rx PHY) activity detection

- Local application wakeup event, such as an external push-button switch (with debouncing)

- **LIN Transceiver** Provides a bi-directional pin for connection to a standard LIN bus [3], with independent transmit and receive signals level-shifted to 3.3 V logic for connection to the EHC. Designed for MOST ECL compliance with many fail-safe features.

- **Temperature Sensor** Detects when programmed temperature thresholds are crossed and can alert the EHC. Simplifies the implementation of MOST Network over-temperature condition management.

- MicroPower Regulator Provides a constant 3.3 V output to supply external devices/circuitry that must be continuously powered. Typically used for external circuitry that must remain powered through Sleep Mode, such as MOST optical receivers (FOR/OEC) and MOST ROM INIC persistent memory supplies.

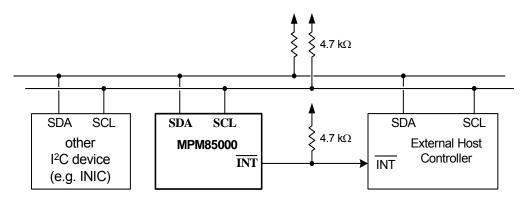

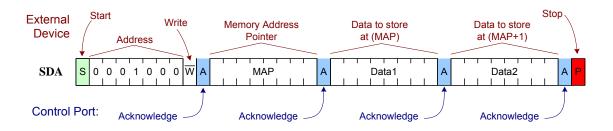

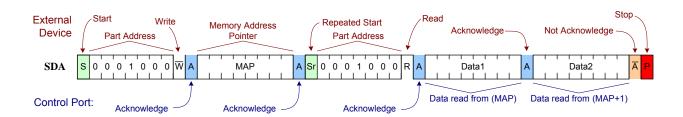

- Control Port Supports optional I<sup>2</sup>C bus [5] slave device implementation for communication with the EHC. Provides access to internal control and status registers, with an interrupt output signal to notify the EHC of various application events.

#### MPM85000

- Voltage Monitors Used for power supply (battery) voltage monitoring.

- Supports configurable wakeup from Sleep Mode voltage regions to ensure the battery voltage is high enough for ECU operation

- Monitors the supply for over- and under-voltage events during Active Mode

- Includes an optional Switch-To-Power (STP) pulse detector for legacy MOST Network systems [6] that support this feature

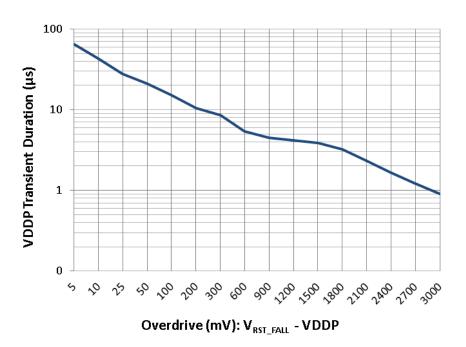

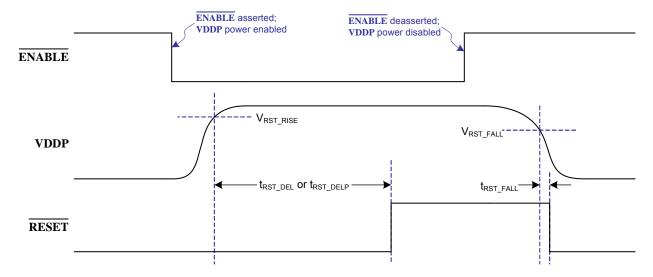

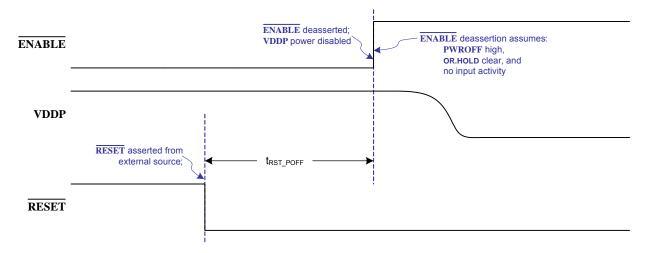

- Reset Generator Provides a programmable system reset output based on a 3.3 V input voltage that can be used as a system-wide power-on reset (POR) after regulators stabilize. Also monitors for external reset events.

- Storage Registers Provides two types of storage registers for general purpose customer use. Each register is 8 bits wide (1 byte of storage).

- 16 RAM-based registers which maintain their values through Sleep Mode (see Section 10.2.13)

- 56 One-Time-Programmable (OTP) registers which maintain their data through *Sleep Mode* and also through disruptions to continuous battery power (see Section 10.2.14 for more information).

Figure 1-2: Functional Blocks

# 1.2 ECU Connection Examples

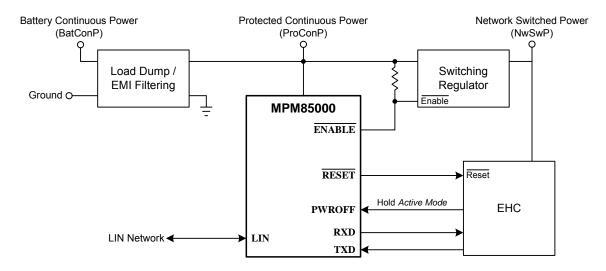

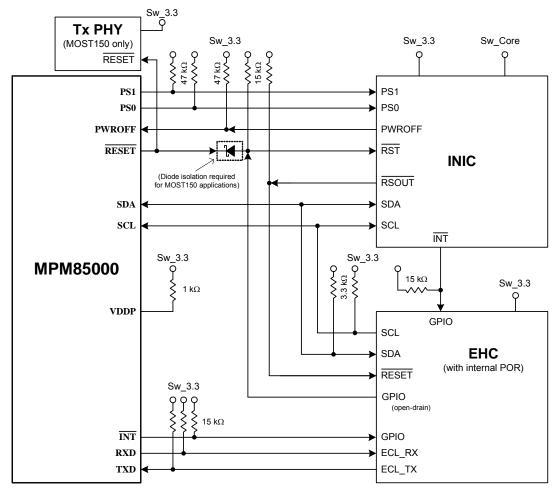

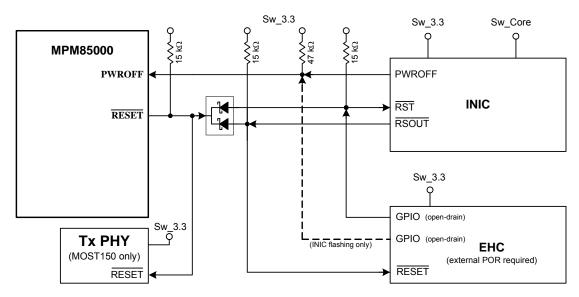

The MPM85000 includes many optional features, not all of which are intended for use in any one design. Figure 1-3 illustrates an ECU block diagram that utilizes the MPM85000 in a stand-alone capacity, without EHC configuration through the Control Port. This block diagram supports wakeup from *Sleep Mode* via the LIN bus. The MPM85000 reset generator provides the power-on reset (POR) for the entire module. Although not shown, the Power Management Port can provide the EHC with power supply monitoring information (using the PS1/PS0 pins), as needed. For ECUs that need to support local wakeup event capabilities during *Sleep Mode*, the MPM85000 MicroPower regulator provides continuous power and either the STATUS or ON\_SW pins signal the local wakeup event. Refer to the *MOST INIC Hardware Concepts Technical Bulletin* [1] for more information regarding local wakeup events.

Figure 1-3: LIN Network Stand-Alone Block Diagram

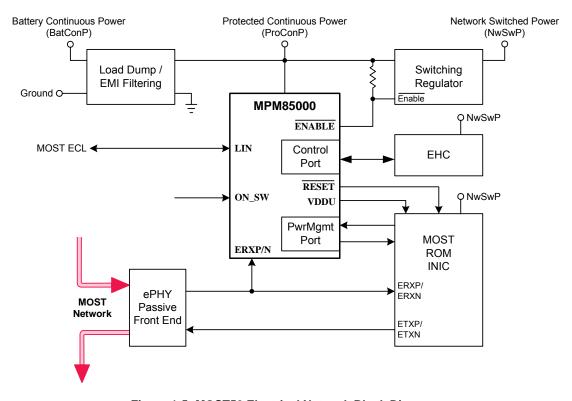

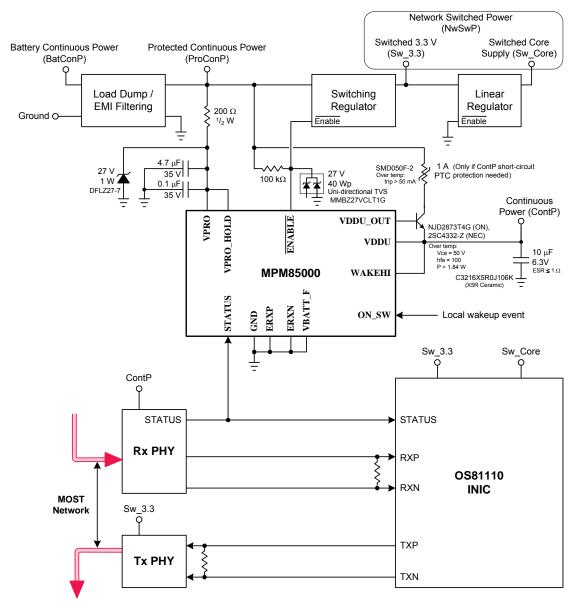

Figure 1-4 on page 10 illustrates a typical MOST optical network ECU block diagram. In this example, the MPM85000 reset generator provides the reset signal to the MOST INIC device while the Power Management Port conveys power states to the INIC. The example also shows two non-local wakeup events: MOST Network activity (FOR activity signal tied to the STATUS pin) and the MOST ECL signal (connected to the LIN pin). Although the EHC could use the RXD and TXD pins for MOST ECL, this example assumes the EHC is using register bits (through the Control Port) to manage the LIN pin, thereby saving hardware pins. The continuous power required by the FOR is provided by the MPM85000 MicroPower regulator (VDDU pin). The ON\_SW pin remains available for local wakeup events. Since the EHC is connected to the Control Port, it can use the MPM85000 OTP storage registers for end-of-line configuration options and use the RAM-based storage registers for volatile settings which must be restored when returning to Active Mode.

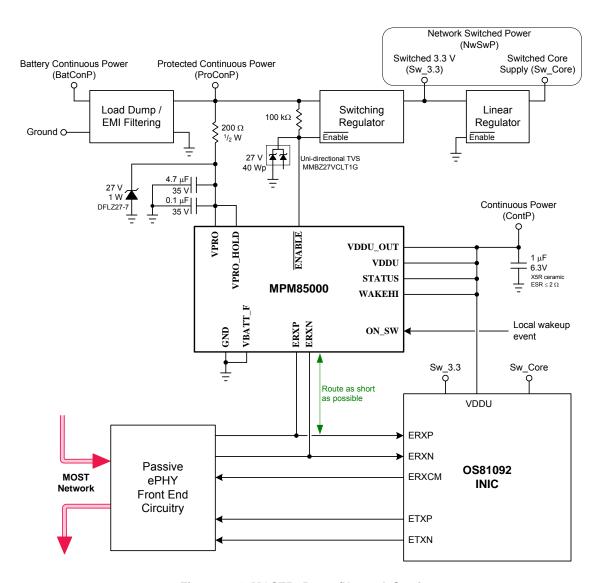

Figure 1-5 on page 10 illustrates a typical MOST50 electrical network ECU block diagram supporting ePHY network activity detection and qualification. The MPM85000 MicroPower regulator output is not connected to a network receiver, as the electrical network front-end is passive; however, the **VDDU** pin does supply power to the persistent memory voltage pin of the ROM INIC.

These figures provide general information and are just a few examples of how the MPM85000 can be utilized in both MOST and non-MOST applications to save cost and increase robustness for automotive ECUs. For more detailed MPM85000 usage information, see Chapter 13, *Application Information*.

Figure 1-4: MOST Optical Network Block Diagram

Figure 1-5: MOST50 Electrical Network Block Diagram

# 2 Pinout

Input pins must not be left floating; therefore, they must be driven, have pull-ups or pull-downs, or be tied directly to one of the appropriate power or ground pins.

Digital pins that can be configured as outputs (e.g.  $D_{I/OD}$ ) are high impedance during initial power-up, except NOACT. The "Type" column indicates the pin type, defined in Section 2.3.

## 2.1 Pinout List

| Pin | Name                 | Туре              | Logic Block          | Description                                                                                                                                                                                                                                                                                    |

|-----|----------------------|-------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | STATUS               | D <sub>IN</sub>   | Activity Detector    | Local wakeup event input (active low). In optical systems, this pin is typically connected to the Fiber Optic Receiver (FOR) status output, which signals optical network activity. Tie to 3.3 V continuous power (VDDU) if unused.                                                            |

| 2   | VDDU_OUT             | A <sub>OUT</sub>  | MicroPower Regulator | Power supply output. This pin provides a 3.3 V continuous power supply, which can be used to power external application circuitry, such as the FOR/OEC and/or INIC persistent memory.                                                                                                          |

| 3   | VDDU                 | A <sub>IN</sub>   | MicroPower Regulator | Feedback input. This pin must either be connected directly to <b>VDDU_OUT</b> or to the emitter of an external NPN pass transistor when additional current is required by the application.                                                                                                     |

| 4   | ERXP                 | A <sub>IN</sub>   | Activity Detector    | Positive differential input of ePHY receive circuit. Tie to ground if unused.                                                                                                                                                                                                                  |

| 5   | ERXN                 | A <sub>IN</sub>   | Activity Detector    | Negative differential input of ePHY receive circuit. Tie to ground if unused.                                                                                                                                                                                                                  |

| 6   | NOACT <sup>1</sup>   | D <sub>OUTD</sub> | Activity Detector    | ePHY network activity indicator (active low). The MPM85000 drives this pin active when valid ePHY activity exists on <b>ERXP/ERXN</b> . Pull-up resistor to the 3.3 V switched supply is required. Tie to ground if unused.                                                                    |

| 7   | GND                  |                   |                      | Ground                                                                                                                                                                                                                                                                                         |

| 8   | VBATT_F <sup>2</sup> | A <sub>IN</sub>   | Voltage Monitor      | Switch-To-Power (STP) event monitor input. This pin should be connected to the battery voltage (prior to load dump filtering) through a 27 k $\Omega$ (1/4 W) series resistor. If STP event detection is not required, tie this pin to ground.                                                 |

| 9   | VPRO <sup>2</sup>    | A <sub>IN</sub>   | Voltage Monitor      | Monitored input from the battery supply. This pin also powers the LIN transceiver. This pin should be connected to the protected battery voltage (after the load dump filter) with a 200 $\Omega$ (1/2 W) series resistor.                                                                     |

| 10  | VPRO_HOLD            |                   |                      | Main power supply input for the MPM85000 12 V core. This pin is typically tied directly to <b>VPRO</b> .                                                                                                                                                                                       |

| 11  | LIN                  | D <sub>I/OD</sub> | LIN Transceiver      | LIN bus input/output signal, internally pulled high to <b>VPRO</b> . This pin may be used as a wakeup event input supporting either LIN bus or MOST ECL. Leave floating if unused.                                                                                                             |

| 12  | ENABLE <sup>1</sup>  | D <sub>OUTD</sub> | Wakeup Event Logic   | Enable control signal (active low) for external voltage regulators. This pin is High-Z in <i>Sleep Mode</i> and driven low in <i>Active Mode</i> . A pull-up resistor is required; however, the voltage level and circuit configuration depends on the requirements of the external regulator. |

- 1. Pull-up resistor required.

- 2. Series resistor required.

Table 2-1: Pinout List

### MPM85000

| Pin | Name               | Туре              | Logic Block              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|--------------------|-------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13  | VDDP <sup>2</sup>  | A <sub>IN</sub>   | Reset Generator          | Monitored input from external application voltage regulator. Requires 1 k $\Omega$ series resistor to the 3.3 V switched supply. If the reset generator is not used, this pin must remain connected to 3.3 V switched power through the 1 k $\Omega$ resistor.                                                                                                                                                                               |

| 14  | RXD <sup>1</sup>   | D <sub>OUTD</sub> | LIN Transceiver          | LIN bus output (from LIN bus to EHC). Pull-up resistor to the 3.3 V switched supply is required. Tie to ground if unused.                                                                                                                                                                                                                                                                                                                    |

| 15  | TXD                | D <sub>IN</sub>   | LIN Transceiver          | LIN bus input (from EHC to LIN bus). A pull-up resistor is recommended to set the initial state during EHC power-up/reset. Tie to the 3.3 V switched supply if unused.                                                                                                                                                                                                                                                                       |

| 16  | WAKEHI             | D <sub>IN</sub>   | Voltage Monitor          | Power-up configuration input. At initial power-up, the sampled value of this pin sets the default state of the <b>CR.WAKECV</b> bit. This pin is used to control the lower boundary of the <i>Allowed Wakeup Range</i> (see Section 4.1) for initial power-up. Tie to either 3.3 V continuous power ( <b>VDDU</b> ) or ground.                                                                                                               |

| 17  | RESET <sup>1</sup> | D <sub>I/OD</sub> | Reset Generator          | External device reset output signal (active low). This pin is asserted based on the input voltage at the <b>VDDP</b> pin and is also monitored to detect external reset conditions. A pull-up resistor to the 3.3 V switched supply is required. If the reset generator is not used, this pin must still be connected to 3.3 V switched power through a resistor (15-100 $k\Omega$ range) while remaining disconnected from the application. |

| 18  | PWROFF             | D <sub>IN</sub>   | Power<br>Management Port | Power-down control input signal. External devices (EHC or INIC) drive this signal low to keep the MPM85000 in <i>Active Mode</i> until they are ready to be powered down. A pull-up resistor to the 3.3 V switched supply is recommended so that external devices release this signal high when reset. Tie to the 3.3 V switched supply if unused.                                                                                           |

| 19  | PS0 <sup>1</sup>   | D <sub>OUTD</sub> | Power<br>Management Port | Power status output signal. Together with <b>PS1</b> , this pin indicates coded power status to the INIC or the EHC. Pull-up resistor to the 3.3 V switched supply is required. Tie to ground if unused.                                                                                                                                                                                                                                     |

| 20  | PS1 <sup>1</sup>   | D <sub>OUTD</sub> | Power<br>Management Port | Power status output signal. Together with <b>PS0</b> , this pin indicates coded power status to the INIC or the EHC. Pull-up resistor to the 3.3 V switched supply is required. Tie to ground if unused.                                                                                                                                                                                                                                     |

| 21  | ĪNT <sup>1</sup>   | D <sub>OUTD</sub> | Control Port             | Interrupt output (active low). The MPM85000 drives this line active to signal various power management interrupt events (defined in Section 10.1) to an external controller. Pull-up resistor to the 3.3 V switched supply is required. Tie to ground if unused.                                                                                                                                                                             |

| 22  | SDA <sup>1</sup>   | D <sub>I/OD</sub> | Control Port             | Data input/output signal for I <sup>2</sup> C communication with an external controller. Pull-up resistor to the 3.3 V switched supply is required. Tie to the 3.3 V switched supply if unused.                                                                                                                                                                                                                                              |

| 23  | SCL <sup>1</sup>   | D <sub>IN</sub>   | Control Port             | Clock input signal for I <sup>2</sup> C communication with an external controller. Pull-up resistor to the 3.3 V switched supply is required. Tie to the 3.3 V switched supply if unused.                                                                                                                                                                                                                                                    |

| 24  | ON_SW              | D <sub>IN</sub>   | Activity Detector        | Application wakeup event input signal (active low), internally pulled high to <b>VDDU</b> . This pin is provided for use as a general-purpose, local application event - either real or simulated. If unused, tie to 3.3 V continuous power ( <b>VDDU</b> ) or leave floating.                                                                                                                                                               |

- 1. Pull-up resistor required.

- 2. Series resistor required.

**Table 2-1: Pinout List (Continued)**

| Pin | Name | Type | Logic Block | Description                                                                                          |  |

|-----|------|------|-------------|------------------------------------------------------------------------------------------------------|--|

| TAB | GND  |      |             | The paddle of the QFN package should be soldered to the ground plane for efficient heat dissipation. |  |

- 1. Pull-up resistor required.

- 2. Series resistor required.

**Table 2-1: Pinout List (Continued)**

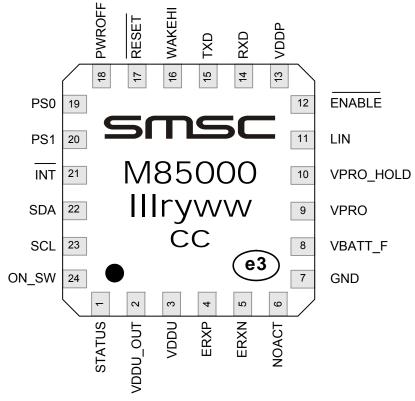

### 2.2 Pinout

Figure 2-1: Pinout (Topside)

The package designators are:

- III Lot Sequence Code

- r Chip Revision Letter

- y last digit of Assembly Year

- ww Assembly Work Week

- cc Country of Origin Abbreviation (up to 2 characters)

- e3 Pb Free Symbol

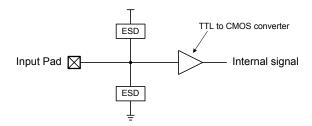

# 2.3 Equivalent Schematics for Pins

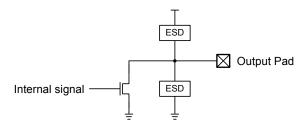

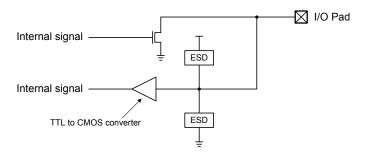

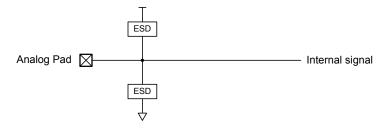

Figure 2-2: Pin-equivalent for Digital Input pin - D<sub>IN</sub>

Figure 2-3: Pin-equivalent for Open-Drain Digital Output pin - D<sub>OUTD</sub>

Figure 2-4: Pin-equivalent for Digital Input/Open-Drain Output pin - D<sub>I/OD</sub>

Figure 2-5: Pin-equivalent for Analog Input/Output pin -  ${\sf A_{I/O}}$

# 3 Operational Modes

The MPM85000 supports two basic modes of operation:

- Sleep Mode minimal circuitry active; waiting for wakeup events (ECU powered down).

- Active Mode all circuits are active (normal ECU operation).

When power is initially applied to the ECU and the <u>VPRO</u> supply is above the <u>WAKEHI</u> threshold, the MPM85000 begins operating in *Active Mode* and the <u>ENABLE</u> pin is driven low to enable the external voltage regulator(s). If no qualified activity is detected after the EHC powers up (and the EHC has not made any changes the MPM85000's configuration registers that would prevent power-down), the MPM85000 reverts to *Sleep Mode* and releases the <u>ENABLE</u> pin by placing it in a high-impedance state.

In *Sleep Mode*, all non-critical circuitry is disabled to minimize power. Only the internal logic required to detect and qualify wakeup events is enabled. The following five events (in addition to initial power being applied) can trigger a transition from *Sleep Mode* to *Active Mode*:

- Valid activity detected on the LIN pin (active low). Used for LIN bus [3] or MOST ECL [4] wakeup and communication.

- Valid activity detected on the STATUS pin (active low). Connected to the FOR/OEC in MOST optical systems to permit wakeup from optical network activity. Can be used as a local wakeup event input in other applications.

- Valid network activity detected on the ERXP/ERXN pins (for MOST50 electrical networks),

- Valid activity detected on the ON\_SW pin (active low). This pin is intended for general purpose local wakeup events, such as a power-on switch.

- Diagnostic Switch-To-Power (STP) event detected and qualified. When this feature is enabled, the MPM85000 detects STP pulses on the battery supply.

In any particular system, not all these wakeup events are used. For example, the ERXP/ERXN pins are only used in MOST50 electrical network systems to detect and wakeup as the result of electrical network activity. These pins would not be used (tied to ground) in non-MOST or MOST optical systems.

All input activity is qualified with glitch suppression to prevent erroneous wakeup events. Additionally, these wakeup events only trigger a transition to *Active Mode* if the power supply voltage monitor (VPRO) is within the *Allowed Wakeup Range* (V<sub>WakeupRange</sub>), which is a requirement of the *MOST Specification* [2]. The V<sub>WakeupRange</sub> levels are programmable and are only used to qualify a transition from *Sleep Mode* to *Active Mode*. Once in *Active Mode*, V<sub>WakeupRange</sub> is not considered when transitioning back to *Sleep Mode*.

#### MPM85000

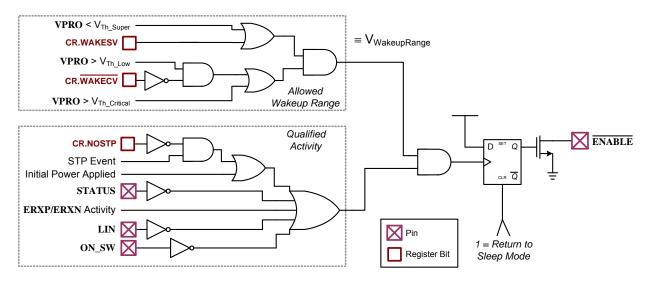

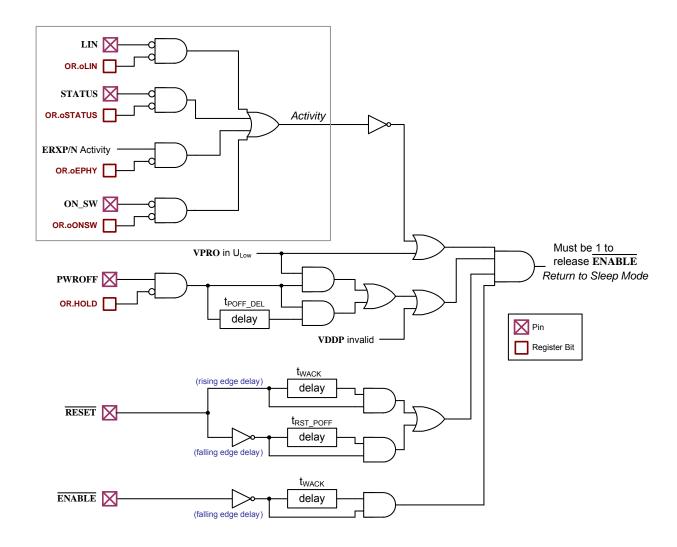

Figure 3-1 shows a conceptual diagram of the MPM85000 wakeup event logic. For simplicity, the timers for glitch suppression are omitted from each activity input signal.

The Allowed Wakeup Range ( $V_{WakeupRange}$ ) always includes the  $U_{Normal}$  region and may optionally include the  $U_{Super}$  and  $U_{Critical}$  regions; however,  $V_{WakeupRange}$  never includes the  $U_{Low}$  region. The cr.wakesv bit sets the upper bound of  $V_{WakeupRange}$  by determining if the MPM85000 is permitted to wakeup in the  $U_{Super}$  region while the cr.wakecv bit determines if the MPM85000 is permitted to wakeup in the  $U_{Critical}$  region. Furthermore, the initial power-up state of the cr.wakecv bit is determined by the wakeup configuration pin. The various power supply regions are defined by their respective programmable thresholds:  $V_{Th}$   $V_{Low}$ ,  $V_{Th}$   $V_{Critical}$ , and  $V_{Th}$   $V_{Super}$  (see Section 4.1 for more information).

Figure 3-1: Wakeup Event Logic (Conceptual Diagram)

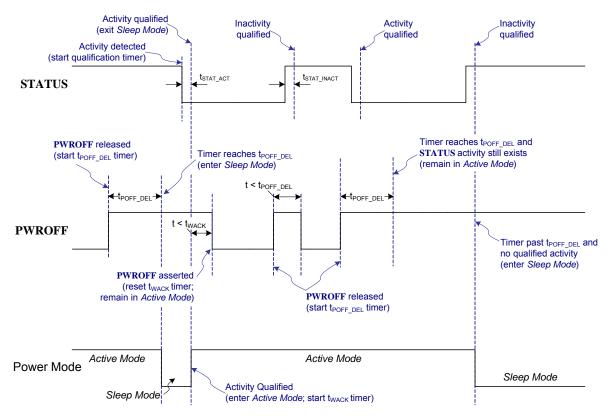

When a wakeup event is qualified and the power supply is in the *Allowed Wakeup Range*, the MPM85000 enters *Active Mode* and drives ENABLE low. After entering *Active Mode*, the MPM85000 gives the application time to initialize (t<sub>WACK</sub>) before considering a transition back to *Sleep Mode*. This timer allows the external device time to drive PWROFF low (or set the OR.HOLD bit) after powering up. If PWROFF is driven low or OR.HOLD is set prior to expiration of the t<sub>WACK</sub> timer, the timer is reset, and the MPM85000 remains in *Active Mode*. The t<sub>WACK</sub> application initialization timer is more robust than standard LIN transceivers or discrete circuits that latch the wakeup event. The MPM85000 reverts back to *Sleep Mode* if PWROFF or OR.HOLD are never asserted, and qualified activity is no longer detected. This behavior prevents a failure from keeping the ECU in *Active Mode* and draining the battery.

Figure 3-2 illustrates the MPM85000 logic for reverting to *Sleep Mode*. Four conditions must all be met for the MPM85000 to release the ENABLE pin and return to *Sleep Mode*:

- No qualified activity on any of the wakeup event input pins (unless VPRO is within the U<sub>I ow</sub> region)

- PWROFF input high and the or.Hold bit cleared for at least tpoff DEL.

- The t<sub>POFF DEL</sub> delay is disregarded if VPRO within U<sub>Low</sub>.

- Additionally, a VDDP invalid condition (defined in Chapter 7, Reset Generator and VDDP) overrides the PWROFF pin and OR.HOLD bit.

- Minimum time elapsed from a transition on RESET.

- t<sub>RST POFF</sub> from falling edge (to detect RESET stuck low)

- t<sub>WACK</sub> from rising edge (to allow external device, such as INIC/EHC, time to recover)

- Minimum time in *Active Mode* elapsed (t<sub>WACK</sub> time from ENABLE going low)

Figure 3-2: Sleep Mode Logic (Conceptual Diagram)

#### MPM85000

As shown in Figure 3-2 on page 17, LIN, STATUS, and ON\_SW pins are active low (logic low level corresponds to activity detected). For robustness, bits in the *Override Register* (OR) (see Section 10.2.7) allow any of these inputs or ePHY activity to be ignored; thereby allowing the MPM85000 to return to *Sleep Mode* in the case of a stuck input condition. If the stuck input is cleared, the corresponding OR bit is automatically cleared to allow the device to wakeup when activity returns on that input.

Table 3-1 lists different scenarios that cause the MPM85000 to enter *Sleep Mode* (power down). For simplicity, Table 3-1 only lists **PWROFF**, but the **OR.HOLD** register bit works similarly. Therefore, the following scenarios assume that **OR.HOLD** is cleared. The "Activity" column references the *Activity* signal shown in Figure 3-2 on page 17, which comes from at least one of the four input pins.

|   | Sleep Mode Transition Scenarios                         | Activity   | PWROFF                    | VPRO               | RESET                         |

|---|---------------------------------------------------------|------------|---------------------------|--------------------|-------------------------------|

| 1 | PWROFF released                                         | 0          | t > t <sub>POFF_DEL</sub> | > U <sub>Low</sub> | 1                             |

| 2 | PWROFF released; VPRO within U <sub>Low</sub>           | don't care | <u>_</u>                  | $U_Low$            | 1                             |

| 3 | All activity ceases (t <sub>WACK</sub> already expired) | 7          | 1                         | > U <sub>Low</sub> | 1                             |

| 4 | t <sub>WACK</sub> expires                               | 0          | 1                         | don't care         | t → t → t > t <sub>WACK</sub> |

| 5 | RESET stuck low; external reset                         | 0          | 1                         | don't care         | $t > t_{RST\_POFF}$           |

| 6 | Internal reset (VDDP invalid)                           | 0          | don't care                | don't care         | $t > t_{RST\_POFF}$           |

Cells containing a transition (edge marked with an arrow) indicate the reason for reverting to Sleep Mode.

**Table 3-1: Power Down Scenarios**

Scenario 1 is the typical case, where all qualified input activity ceases. When no activity has occurred for a period of time (t<sub>PwrSwitchOffDelay</sub> [2] for MOST Network designs), then the external device (INIC/EHC) releases **PWROFF**, and the MPM85000 reverts to *Sleep Mode* after t<sub>POFF DEL</sub> expires.

Scenario 2 is similar to Scenario 1, except the **VPRO** supply is in the U<sub>Low</sub> region. In this case, t<sub>POFF\_DEL</sub> is ignored to allow a faster transition to *Sleep Mode* when the ECU supply is collapsing. Since the ECU supply is collapsing, qualified activity is ignored (consistent with *MOST Specification* [2] requirements).

Scenario 3 would generally be caused by a faulty ECU module, where **PWROFF** was never pulled low and the initial POR t<sub>WACK</sub> timer expires, but input activity keeps the MPM85000 in *Active Mode*. Therefore, when all qualified activity ceases, the MPM85000 reverts to *Sleep Mode*.

Scenario 4 is similar to 3, except input activity ceases before the  $t_{WACK}$  timer expires. The  $t_{WACK}$  timer keeps the MPM85000 in *Active Mode*, to give the external device (INIC/EHC) time to initialize and pull **PWROFF** low. In this scenario, **PWROFF** is never pulled low, so the MPM85000 reverts to *Sleep Mode* once  $t_{WACK}$  expires (fail-safe feature to save battery power).

Scenario 5 is a robustness feature that allows the MPM85000 to enter *Sleep Mode* if an external device holds  $\overline{\text{RESET}}$  low for longer than  $t_{\text{RST POFF}}$  (faulty reset is assumed).

Scenario 6 is a result of the **VDDP** voltage dropping to the point where the reset generator asserts **RESET** (**VDDP** invalid condition). In a typical system **PWROFF** is pulled-up to **VDDP**; therefore, if **VDDP** is invalid, then **PWROFF** becomes invalid and cannot be relied upon. In this scenario, **PWROFF** is ignored and cannot hold the MPM85000 in *Active Mode*.

The following three figures illustrate the power down scenarios defined in Table 3-1 (two scenarios shown per figure). In each figure, qualified activity is represented by just one of the four activity inputs; however, activity on any of the other three inputs would result in the same behavior.

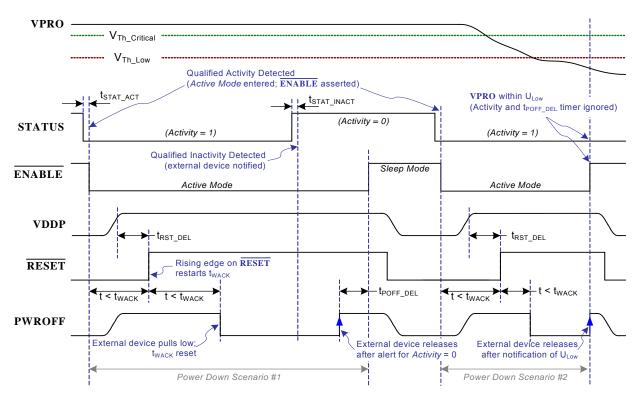

Figure 3-3 illustrates two power cycles that utilize the STATUS pin as the wakeup event while the PWROFF pin is used by an external device (e.g. INIC/EHC) to keep the MPM85000 in *Active Mode*. When qualified activity ceases (STATUS goes high), the external device is notified and should release the PWROFF pin when appropriate, which causes the MPM85000 to revert to *Sleep Mode*.

The first power cycle in Figure 3-3 depicts scenario 1 (listed in Table 3-1). After input activity ceases, **PWROFF** is released to revert to *Sleep Mode*. The second power cycle depicts scenario 2, when **VPRO** dips into the U<sub>Low</sub> region. When the external device is notified about the power dropping, it prepares for power down, then releases **PWROFF**. This causes **ENABLE** to be released regardless of input activity.

Figure 3-3: Typical Power Cycle (Scenarios 1 and 2)

#### MPM85000

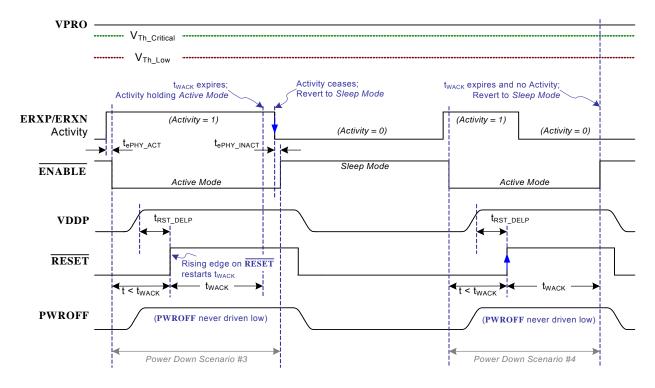

The first power cycle in Figure 3-4 depicts scenario 3 (listed in Table 3-1). After entering *Active Mode*, **PWROFF** is never driven low and the  $t_{WACK}$  timer expires; however, the ePHY input is still active. Once ePHY activity ceases, the MPM85000 reverts to *Sleep Mode*. The second power cycle depicts scenario 4, where the ePHY activity ceases soon after entering *Active Mode*, but the  $t_{WACK}$  timer keeps the MPM85000 in *Active Mode*. Since **PWROFF** is never driven low by the external device (fault condition), the MPM85000 reverts to *Sleep Mode* once  $t_{WACK}$  expires.

Figure 3-4: Power Down Scenarios 3 and 4

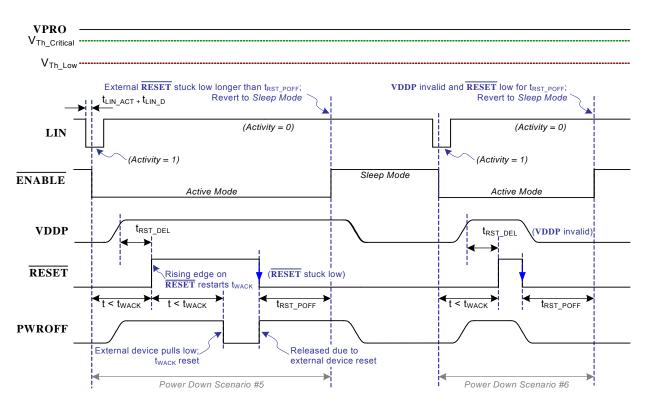

The first power cycle in Figure 3-5 depicts scenario 5 (listed in Table 3-1). After entering *Active Mode*, LIN activity ceases (LIN goes high), and the PWROFF signal is pulled low by the external device (INIC/EHC). At some point later, the RESET pin is externally pulled low, which causes the external device to release the PWROFF signal. The t<sub>RST\_POFF</sub> timer keeps the MPM85000 in *Active Mode* to allow the INIC/EHC time to recover after the reset. However, in this scenario, RESET is faulty (stuck low); therefore, when the t<sub>RST\_POFF</sub> timer expires, the MPM85000 reverts to *Sleep Mode*. The second power cycle depicts scenario 6, where the VDDP supply is faulty. In this scenario, VDDP collapsing causes the MPM85000 reset generator to drive RESET low. Since VDDP is invalid, PWROFF is ignored, and the MPM85000 reverts to *Sleep Mode* after t<sub>RST\_POFF</sub>.

Figure 3-5: Power Down Scenarios 5 and 6

# 4 Voltage Monitors

The MPM85000 voltage monitors provide high-impedance internal attenuators that are connected to the VPRO and VBATT\_F pins. A large internal impedance is required to minimize current in *Sleep Mode*. Since the attenuator ladders are internal, conformal coating (which is required to maintain accuracy when using a discrete solution) is not needed. Voltages on VPRO and VBATT\_F are divided down to a level that can be compared to programmed voltage thresholds.

### 4.1 VPRO Pin

The **VPRO** pin should be connected to the protected power supply, after the load dump protection circuitry (see Chapter 13 for typical application connection diagrams). This pin voltage is divided down to obtain the various voltage levels defined in the *MOST Specification* [2]. When in *Sleep Mode*, these regions are used to define the *Allowed Wakeup Range* (V<sub>WakeupRange</sub>), which prevents the MPM85000 from transitioning to *Active Mode* when the power supply voltage is irregular. The V<sub>WakeupRange</sub> voltage range is programmable through the **WAKEHI** configuration pin as well as the **CR.WAKESV** and **CR.WAKECV** register bits.

The following four distinct VPRO Power Regions are defined:

- Normal Power Region (U<sub>Normal</sub>)

- Low Power Region (U<sub>Low</sub>)

- Critical Power Region (U<sub>Critical</sub>)

- Super Power Region (U<sub>Super</sub>)

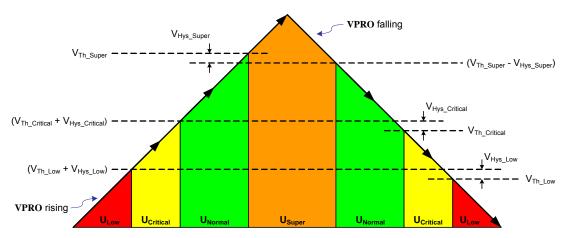

Programmed thresholds set the boundaries of the *VPRO Power Regions*, which are shown in Figure 4-1. When in *Active Mode*, these regions are used to alert the INIC/EHC to abnormal power conditions.

Figure 4-1: VPRO Power Regions

Table 4-1 defines the *Allowed Wakeup Range*, V<sub>WakeupRange</sub>, of the MPM85000.

| CR.WAKECV* | CR.WAKESV | VP                                     | Allowed Wakeup Range                |                                                                  |

|------------|-----------|----------------------------------------|-------------------------------------|------------------------------------------------------------------|

| CR.WARECV  | CR.WARESV | Lower Bound                            | Upper Bound                         | (V <sub>WakeupRange</sub> )                                      |

| 0          | 0         | <b>VPRO</b> ≥ V <sub>Th_Low</sub>      | <b>VPRO</b> < V <sub>Th_Super</sub> | U <sub>Critical</sub> , U <sub>Normal</sub>                      |

| 0          | 1         | <b>VPRO</b> ≥ V <sub>Th_Low</sub>      | none                                | U <sub>Critical</sub> , U <sub>Normal</sub> , U <sub>Super</sub> |

| 1          | 0         | <b>VPRO</b> ≥ V <sub>Th_Critical</sub> | <b>VPRO</b> < V <sub>Th_Super</sub> | U <sub>Normal</sub>                                              |

| 1          | 1         | <b>VPRO</b> ≥ V <sub>Th_Critical</sub> | none                                | U <sub>Normal</sub> , U <sub>Super</sub>                         |

<sup>\*</sup> The state of the WAKEHI pin at initial power-up sets the default value of the CR.WAKECV bit.

Table 4-1: Allowed Wakeup Range

Voltage thresholds for VPRO ( $V_{Th\_Low}$ ,  $V_{Th\_Critical}$ ,  $V_{Th\_Super}$ ) are set in the VPRO Comparator Threshold Register (VCT), which is accessible via the Control Port. Refer to Section 10.2.5 for details on VCT. A fixed hysteresis ( $V_{Hys\_Low}$ ,  $V_{HyS\_Critical}$ , and  $V_{Hys\_Super}$ ) exists for each threshold.

When the MPM85000 is in Active Mode, transitions between VPRO Power Regions result in:

- the appropriate bit in the Status Register (SR) is changed to indicate the current power region,

- the PS1 and PS0 pins are driven to reflect the current power region (to alert INIC/EHC), and

- the IR.IVOLT bit is set and, assuming MR.mVOLT is not set, the INT pin is asserted to alert the EHC.

The U<sub>Super</sub> region notification is generally used to secure ECU application hardware that is sensitive to high voltage, such as power amplifiers or disk drives.

The U<sub>Critical</sub> region notification is generally used to secure hardware that cannot operate with at low voltage levels and to secure audio connections in a MOST Network application. Additionally, persistent parameters can be saved at this point before the supply drops further.

The  $U_{Low}$  region notification generally indicates the power supply is collapsing and the local device should take the necessary action in anticipation of full loss of power. Bulk capacitance in the load dump circuitry usually prevents small transients into  $U_{Low}$  from disrupting the ECU. For MOST Network devices, the MOST Specification [2] indicates that the ECU should stop network communications and transition to Sleep Mode when the supply drops into the  $U_{Low}$  region. The MPM85000 facilitates this feature when VPRO drops below  $V_{Th\_Low}$  by ignoring qualified activity on input signals and overriding the PWROFF pin delay timer to allow quick transition into Sleep Mode once the external device releases PWROFF.

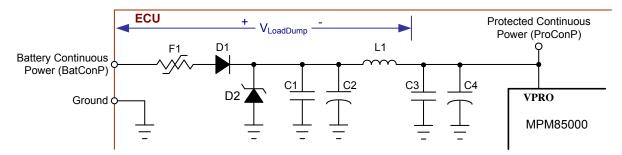

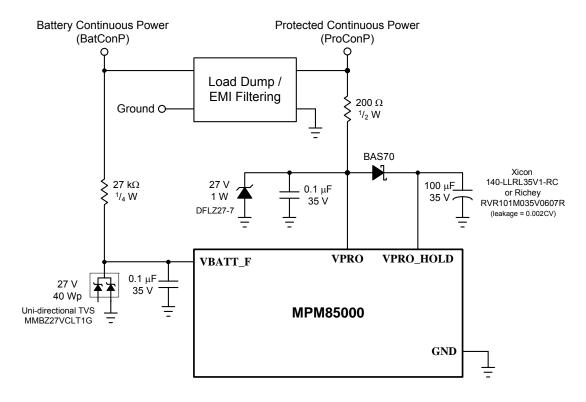

Automotive ECU power supply inputs typically include load dump and filtering circuits which protect the ECU from voltage transients and provide reserve power for short periods of voltage dropout. These components also provide EMI immunity and reduce EMI emissions. The hardware configuration needed is application specific; however, Figure 4-2 illustrates a basic circuit for discussion purposes. The polarized capacitors (C2 and C4) and transient diode (D2) should be specified for low leakage since they contribute to *Sleep Mode* current. The load dump circuitry also causes a voltage drop, V<sub>LoadDump</sub>, between the ECU box edge and the internal protected power (ProConP) net, where the MPM85000 **VPRO** pin monitors the supply voltage.

Figure 4-2: Load Dump Voltage Drop

This voltage drop must be taken into account when selecting the **VPRO** comparator thresholds, since the MPM85000 measures the voltage levels at the protected power (ProConP) net, but OEMs specify ECU voltage levels from the outside of the ECU (BatConP).

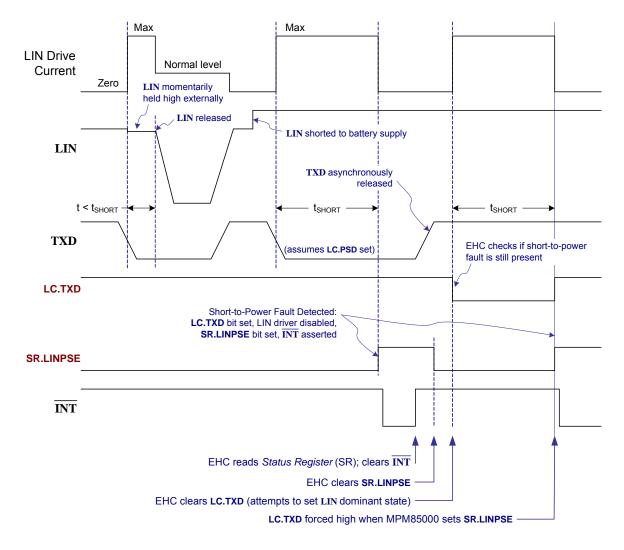

## 4.2 STP and VBATT F Pin

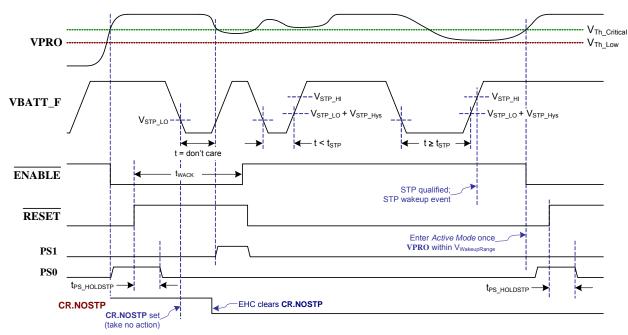

In legacy MOST Network systems (see the MOST Specification Version 2.5 [6] for more information) a Switch-To-Power Detector is available as a method for initiating ring-break diagnosis (RBD), which can identify and localize a break in a MOST Network for easy repair. A Switch-To-Power (STP) event does not occur during normal ECU operation, but rather in a vehicle repair shop or assembly line. The vast majority of newer systems use the Electrical Control Line Specification [4] since it provides additional diagnostic capabilities. STP is disabled by default on the MPM85000; the CR.NOSTP bit must be cleared to support STP. In addition, the power supply pins must be configured as shown in Section 13.5.

When STP event detection is not required, the **VBATT\_F** pin should be tied directly to ground to reduce power consumption in *Sleep Mode*.

The disruption of battery power for at least the t<sub>STP</sub> time is referred to as a Switch-To-Power (STP) event.

The MPM85000 detects an STP wakeup event when  $valebox{VBATT}_F$  drops below the  $valebox{V}_{STP\_LO}$  threshold for at least  $talebox{V}_{STP}$  then rises above the  $valebox{V}_{STP\_HI}$  threshold. Once an STP event occurs, protected power ( $valebox{VPRO}$ ) must also be within the  $valebox{V}_{WakeupRange}$  voltage range to wakeup from  $salebox{SIP}$  must also be within the  $valebox{V}_{WakeupRange}$  voltage range to wakeup from  $salebox{SIP}$  must also be within the  $valebox{V}_{WakeupRange}$  voltage range to wakeup from  $salebox{SIP}$  must also be within the  $valebox{V}_{WakeupRange}$  voltage range to wakeup from  $salebox{V}_{WakeupRange}$  voltage range to wakeup from  $salebox{V}_{WakeupRange}$

When an STP event is detected, PS1 and PS0 are set appropriately (as described in Chapter 9, Power Management Port), the IR.iPOR bit is set, and INT is driven low. When set, the IR.iPOR register bit indicates either initial power applied to the MPM85000 or that an STP event occurred. In either case, the response (initiating RBD) is the same for MOST INIC devices that are configured to support STP. Table 4-2 illustrates various conditions on VBATT\_F and how the STP detection logic handles the condition, assuming the CR.NOSTP register bit is clear.

| Case | VBATT_F                                              | Condition                                                                                                                                                                                                                                                                                                                                                                                | STP Event |

|------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1    | VBATT_F/<br>VPRO                                     | Initial power-up condition:  When STP is enabled, this condition is also considered an STP event. In this case, the VPRO voltage is compared against V <sub>WakeupRange</sub> .                                                                                                                                                                                                          | Yes       |

| 2    | VBATT_F  VSTP_LO  VSTP_LO + VSTP_Hys  t < tSTP       | Engine start condition:  In this case, $VBATT\_F$ drops below $V_{STP\_LO}$ for less than $t_{STP}$ before rising above ( $V_{STP\_LO} + V_{STP\_Hys}$ ).  If the device is in <i>Sleep Mode</i> , it does not wake up.                                                                                                                                                                  | No        |

| 3    | $VBATT_F$ $V_{STP\_LO}$ $V_{STP\_LO} + V_{STP\_Hys}$ | Valid STP pulse detection:  In this case, VBATT_F drops below V <sub>STP_LO</sub> for at least t <sub>STP</sub> before rising above (V <sub>STP_LO</sub> + V <sub>STP_Hys</sub> ). The actual STP event does not occur until VBATT_F exceeds the V <sub>STP_HI</sub> threshold. Then the VPRO voltage must be within the V <sub>WakeupRange</sub> voltage range to cause a wakeup event. | Yes       |

| 4    | VBATT_F                                              | Normal operating condition:  In this case, VBATT_F remains above V <sub>STP_LO</sub> so the t <sub>STP</sub> timer is never started. If the device is in <i>Sleep Mode</i> , it does not wake up.                                                                                                                                                                                        | No        |

**Table 4-2: STP Event Detection**

Figure 4-3 illustrates STP activity and interaction with the application. Note that  $\mathbf{WAKEHI} = \mathbf{VDDU}$ , thereby prohibiting the MPM85000 from waking up when  $\mathbf{VPRO}$  is in the  $\mathbf{U}_{Critical}$  region.

Figure 4-3: STP Activity and Interaction

# **5 Activity Detectors**

The MPM85000 contains four inputs with activity detection and qualification circuits that are capable of waking the MPM85000 from *Sleep Mode*, as well as keeping the MPM85000 in *Active Mode*. The four inputs that support activity detection are:

- LIN Supports standard LIN bus [3] connections and is also MOST ECL [4] compliant. When used, activity on this pin wakes up the MPM85000 from Sleep Mode whenever a qualified LIN or ECL wakeup pulse is detected.

- STATUS In MOST optical systems, the STATUS pin is connected to the OEC/FOR activity indicator output, which is driven active (low) whenever optical activity is present. This functionality allows MPM85000 wakeup events based on optical MOST Network activity. In non-MOST or non-optical MOST systems, STATUS can be used as a general purpose local wakeup event.

- ERXP/ERXN In MOST50 electrical systems, these pins are connected to the electrical network receive circuitry to provide network activity wakeup event signalling. This is equivalent to the functionality that the STATUS pin provides for optical MOST systems. For other applications (e.g. non-MOST or optical MOST systems) these pins are typically unused and should be tied directly to ground.

- ON\_SW Provides local wakeup event support, such as a momentary push-button switch. Other uses are as an on-board wakeup signal for a telematics system which needs to wakeup the MPM85000 from Sleep Mode when a call comes in, or a door open switch which needs to wakeup the ECU to respond to the event.

In addition to monitoring activity on these pins, all the activity detection circuits implement qualification procedures to validate both activity and inactivity over a set period of time. This provides robust fault tolerance and glitch protection by effectively ignoring spurious events on these input pins.

# 5.1 LIN Pin Activity Detection

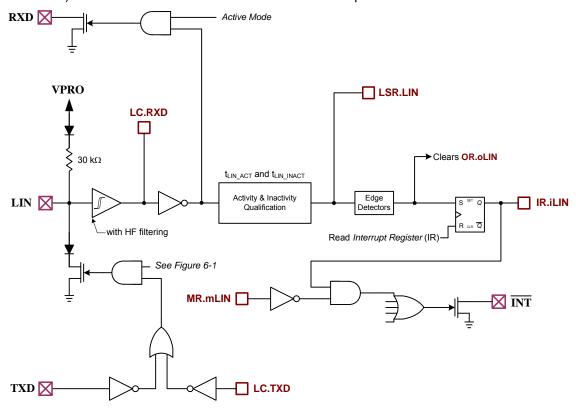

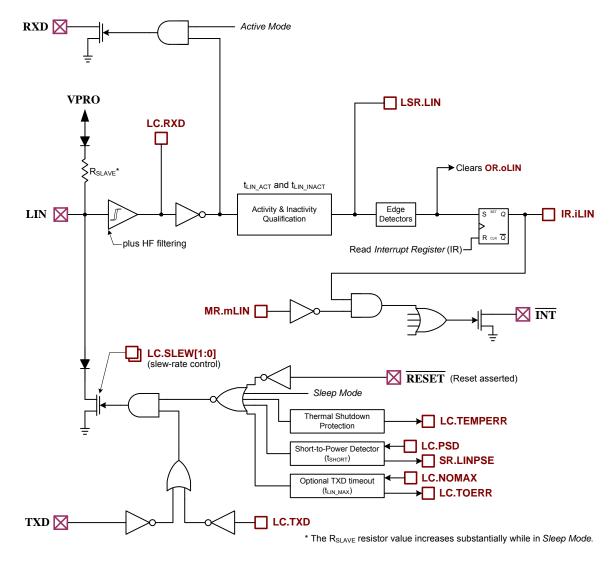

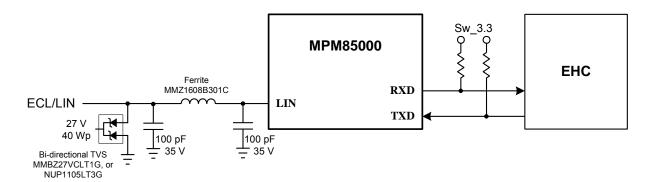

In addition to operating as a standard *Local Interconnect Network (LIN) Transceiver* [3] (refer to Chapter 6, *LIN Transceiver*), the MPM85000 LIN pin is also compliant to the *MOST Electrical Control Line (ECL) Specification* [4]. In simple, low-cost implementations, the LIN pin can serve as the only source of non-local wakeup events. In advanced systems, LIN or ECL communication can be specified as a redundant wakeup event mechanism to MOST Network activity, as it provides simultaneous wakeup to all ECUs and can also provide a communications bus for diagnostics. When used for MOST ECL signalling, software register bits can replace the hardware TXD/RXD pins, while the LIN pin activity detector is used to generate interrupts to the EHC whenever the LIN pin changes state (eliminates the need for software polling). If the LIN pin is not needed for a particular design, it can be left floating since it contains an internal pull-up resistor to VPRO.

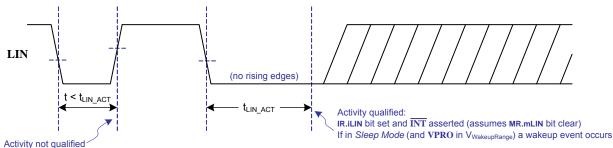

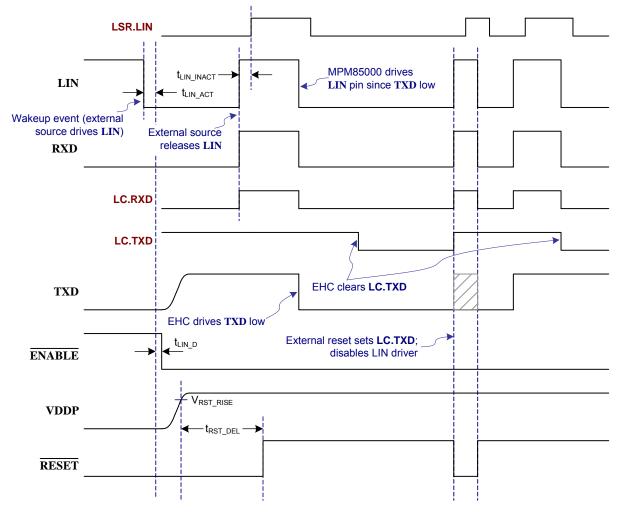

When a falling edge is detected on LIN, the MPM85000 turns on an internal timer to qualify the activity. If LIN remains low for  $t_{LIN\_ACT}$ , then the activity is considered valid, the IR.iLIN bit in the Interrupt Register (IR) is set, and the  $\overline{INT}$  pin is driven low (assumes the MR.mLIN mask bit is clear). If the MPM85000 is in Sleep Mode when the LIN activity is qualified as valid, and if the VPRO power supply is valid (within the  $V_{WakeupRange}$  voltage range), then the MPM85000 transitions to Active Mode. If the LIN pin causes the MPM85000 to exit Sleep Mode, then the INE.wLIN bit in the Initial Wakeup Event Register (IWE) is set. This register indicates the reason the MPM85000 entered Active Mode; refer to Section 10.2.12 for more information.

Once in *Active Mode*, both edges on LIN are qualified for noise rejection. Therefore, once LIN activity is qualified (logic low level, also defined as dominant) with  $t_{LIN\_ACT}$ , then LIN inactivity (logic high level, also defined as recessive) is qualified with the  $t_{LIN\_INACT}$  timer. The LSR.LIN bit in the *Line Status Register* (LSR) indicates the current qualified state of the LIN pin. The LSR.LIN bit is set when LIN is qualified low or active, and cleared when LIN is qualified high or inactive. Each transition of the LSR.LIN bit (each qualified edge of the LIN pin) causes the IR.ILIN bit in the *Interrupt Register* (IR) to be set, which in turn causes the  $\overline{INT}$  pin to

be driven low (assumes MR.mLIN clear). The IR bits are cleared (interrupt cleared) when the register is read. If the LIN pin is used for standard high-speed LIN communication (EHC using the RXD/TXD pins), then the MR.mLIN mask bit should be set so LIN communication does not cause excessive EHC interrupts.

Figure 5-1 depicts the *Active Mode* LIN pin detection logic, without the fail-safe features (see Figure 6-1 on page 33 for the complete LIN pin logic diagram). The LC.RXD bit is a software version of the RXD pin that differs from LSR.LIN in polarity. Also, the LC.RXD register bit represents the actual pin value (i.e. it is not qualified with timers). The LC.TXD bit is a software version of the TXD pin.

Figure 5-1: LIN Pin Detector Logic

If the LIN pin override bit (OR.oLIN in the Override Register (OR)) was previously set to ignore a stuck LIN pin, then any transition from qualified activity to qualified inactivity, or vice versa (i.e. any change of LSR.LIN), clears the OR.oLIN bit. In a normal operating environment, qualified LIN activity (LIN pin low, or dominant) keeps the MPM85000 in Active Mode. If the EHC determines that the LIN pin is stuck low for any reason (e.g. short to ground), then the EHC can set OR.oLIN which allows the MPM85000 to revert to Sleep Mode when the EHC chooses. If, while in Sleep Mode, the LIN pin gets unstuck, then any transitions automatically clear OR.oLIN thereby allowing the MPM85000 to wakeup again from LIN activity. Figure 5-2 below illustrates the LIN activity qualification process.

Figure 5-2: LIN Activity Qualification

# 5.2 STATUS Pin Activity Detection

In MOST optical systems, the MPM85000 STATUS pin is connected to the OEC/FOR network activity indicator output, which is driven active (low) when optical activity is present. The OEC/FOR is powered from the MPM85000 MicroPower regulator (VDDU pin) continuous power supply and typically implements its own low-power (sleep mode) mode of operation to meet OEM power requirements. The OEC/FOR wakes up from its sleep mode when optical activity exists and drives its activity indicator output pin active (logic low level). This, in turn, wakes up the MPM85000 from Sleep Mode (provided VPRO is within the VWakeupRange voltage range). In non-MOST or non-optical MOST systems, the STATUS input can be used to detect a general purpose local wakeup event (see the MOST INIC Hardware Concepts Technical Bulletin [1] for examples of local wakeup events). If the STATUS input pin is not needed in a particular design, it should be tied to VDDU.

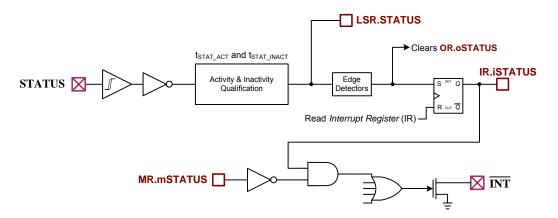

When a falling edge is detected on STATUS, the MPM85000 turns on an internal timer to qualify the activity. If STATUS remains low for t<sub>STAT</sub> ACT, then the activity is considered valid, the IR.ISTATUS bit in the Interrupt Register (IR) is set, and the INT pin is driven low (assumes the MR.mSTATUS mask bit is clear). If the MPM85000 is in Sleep Mode when the STATUS activity is qualified as valid, and if the VPRO power supply is valid (within V<sub>WakeupRange</sub>), then the MPM85000 transitions to Active Mode. If the STATUS pin causes the MPM85000 to exit Sleep Mode, then the IWE.wSTATUS bit in the Initial Wakeup Event Register (IWE) is set.

Once in *Active Mode*, both edges on STATUS are qualified for noise rejection. Therefore, once STATUS activity is qualified (logic low level) with t<sub>STAT\_ACT</sub>, then STATUS inactivity (logic high level) is qualified with the t<sub>STAT\_INACT</sub> timer. The LSR.STATUS bit in the *Line Status Register* (LSR) indicates the current qualified state of the STATUS pin. The LSR.STATUS bit is set when STATUS is qualified low or active, and cleared when STATUS is qualified high or inactive. Each transition of the LSR.STATUS bit (each qualified edge on the STATUS pin) causes the IR.ISTATUS bit to be set, which in turn causes the INT pin to be driven low (assumes MR.mSTATUS clear). The IR bits are cleared (interrupt cleared) when the register is read. Figure 5-3 depicts the STATUS pin logic.

Figure 5-3: STATUS Pin Detector Logic

If the STATUS pin override bit (OR.oSTATUS bit in the Override Register (OR)) was previously set to ignore a stuck STATUS pin, then any transition from qualified activity to qualified inactivity, or vice versa (i.e. any change of LSR.STATUS), clears the OR.oSTATUS bit. In a normal operating environment, qualified STATUS activity (STATUS pin low) keeps the MPM85000 in Active Mode. If the EHC determines that the STATUS pin is stuck low for any reason, then the EHC can set OR.oSTATUS which allows the MPM85000 to revert to Sleep Mode when the EHC chooses. If, while in Sleep Mode, the STATUS pin gets unstuck, then any transitions automatically clear OR.oSTATUS thereby allowing the MPM85000 to wakeup again from STATUS activity.

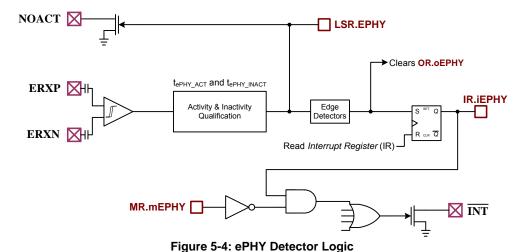

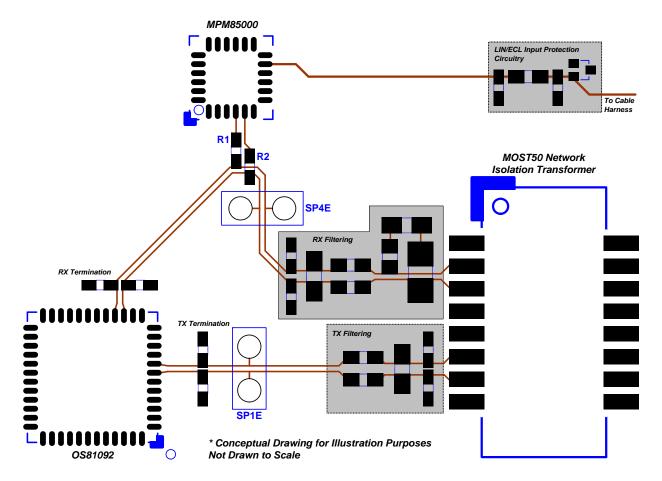

# 5.3 ePHY Activity Detection

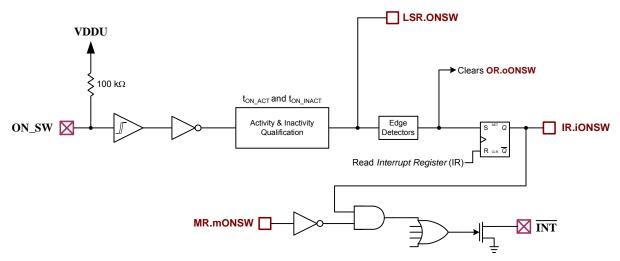

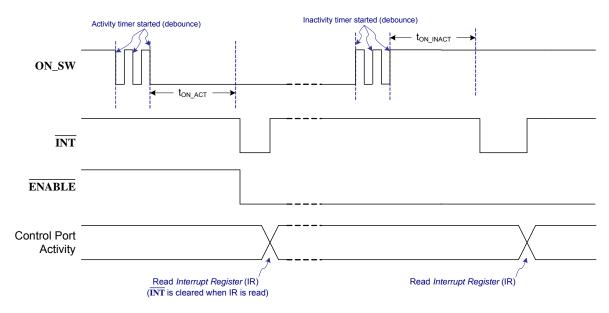

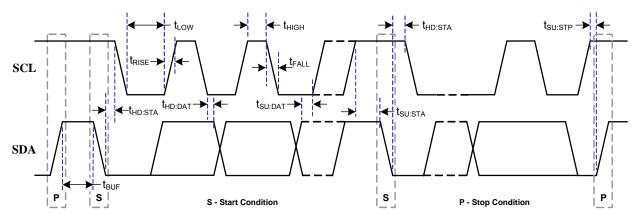

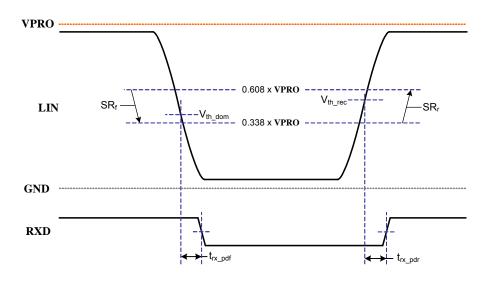

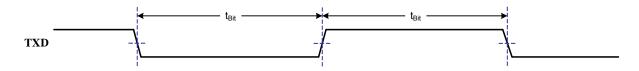

In MOST50 electrical systems, the physical layer front-end circuitry is passive and does not include activity detection logic (unlike MOST optical systems, in which the FOR/OEC checks for network activity). For these electrical network systems, the MPM85000 contains an internal ePHY network activity detector. The MPM85000 ERXP/ERXN pins should connect to the network at MOST50 specification point four (also known as SP4E; see the MOST Specification of Electrical Physical Layer [7] for more information) to allow wakeup events based on ePHY network activity. For systems that do not require electrical network activity detection, the ERXP/ERXN pins should both be tied directly to ground. Additionally, the ePHY activity detector should be powered down (by setting the CR.PDEPHY bit in the Configuration Register (CR)) to minimize Sleep Mode current.