# 1.0A Constant-Current Buck Regulator for Driving High Power LEDs

The NCL30160 is an NFET hysteretic step-down, constant-current driver for high power LEDs. Ideal for industrial and general lighting applications utilizing minimal external components. The NCL30160 operates with an input voltage range from 6.3 V to 40 V. The hysteretic control gives good power supply rejection and fast response during load transients and PWM dimming to LED arrays of varying number and type. A dedicated PWM input (DIM/EN) enables wide range of pulsed dimming and a high switching frequency up to 1.4 MHz allows the use of smaller external components minimizing space and cost. Protection features include resistor-programmed constant LED current, shorted LED protection, under-voltage and thermal shutdown. The NCL30160 is available in a SOIC-8 package.

#### **Features**

- Integrated 1.0A MOSFET

- VIN Range 6.3 V to 40 V

- Short LED Shutdown Protection

- Up to 1.4 MHz Switching Frequency

- No Control Loop Compensation Required

- Adjustable LED Current

- Single Pin Brightness and Enable/Disable Control Using PWM

- Supports All-Ceramic Output Capacitors and Capacitor-less Outputs

- Thermal Shutdown Protection

- Capable of 100% Duty Cycle Operation

- This is a Pb-Free Device

### **Typical Application**

- LED Driver

- Constant Current Source

- General Illumination

- Industrial Lighting

# ON Semiconductor®

www.onsemi.com

SOIC-8 NB CASE 751

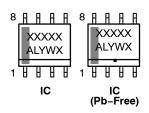

#### **MARKING DIAGRAM**

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

■ = Pb-Free Package

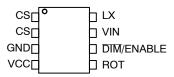

#### PIN CONNECTIONS

#### **ORDERING INFORMATION**

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| NCL30160DR2G | SOIC-8<br>(Pb-Free) | 2500 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

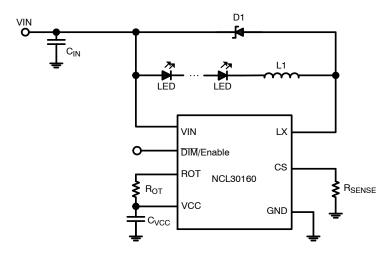

Figure 1. Typical Application Circuit

# PIN FUNCTION DESCRIPTION

| Pin  | Pin Name | Description                             | Application Information                                                                                                                                                                                                                                                                        |

|------|----------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2 | CS       | Current Sense feedback pin              | Set the current through the LED array by connecting a resistor from this pin to ground.                                                                                                                                                                                                        |

| 3    | GND      | Ground Pin                              | Ground. Reference point for all voltages                                                                                                                                                                                                                                                       |

| 4    | VCC      | Output of Internal 5 V linear regulator | The VCC pin supplies the power to the internal circuitry. The VCC is the output of a linear regulator which is powered from VIN. A 2 uF ceramic capacitor is recommended for bypassing and should be placed as close as possible to the VCC and AGND pins. Do not connect to an external load. |

| 5    | Rot      | Off-Time Setting Resistor               | Resistor ROT from this pin to VCC sets the Off–Time range for the hysteretic controller.                                                                                                                                                                                                       |

| 6    | DIM/EN   | PWM Dimming Control & ENABLE            | Connect a logic-level PWM signal to this pin to enable/disable the power MOSFET and LED array                                                                                                                                                                                                  |

| 7    | VIN      | Input Voltage Pin                       | Nominal operating input range is 6.3 V to 40 V. Input supply pin to the internal circuitry and the positive input to the current sense comparators. Due high frequency noise, a 10 $\mu F$ ceramic capacitor is recommended to be placed as close as possible to VIN and power ground.         |

| 8    | LX       | Drain of Internal Power<br>MOSFET       | The LX pin connects to the inductor and provides the switching current necessary to operate in hysteretic mode.                                                                                                                                                                                |

### **MAXIMUM RATINGS**

| Rating                                                                                                                                                | Symbol                 | Min         | Max        | Unit      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|------------|-----------|

| VIN to GND                                                                                                                                            | VIN                    | -0.3        | 40         | V         |

| MOSFET Drain Voltage to GND                                                                                                                           | LX                     | -           | 40         | V         |

| VCC to GND                                                                                                                                            | VCC                    | -           | 6          | V         |

| DIM/EN to GND                                                                                                                                         | DIM                    | -0.3        | 6          | V         |

| CS to GND                                                                                                                                             | CS                     | -0.3        | 6          | V         |

| ROT to GND                                                                                                                                            | ROT                    | -0.3        | 6          | V         |

| Absolute Maximum Junction Temperature                                                                                                                 | $T_{J(MAX)}$           | 150         |            | °C        |

| Operating Junction Temperature Range                                                                                                                  | TJ                     | -40         | 125        | °C        |

| Maximum LED Drive Current                                                                                                                             | ILIM                   | 1           | .5         | Α         |

| Storage Temperature Range                                                                                                                             | T <sub>stg</sub>       | -55 to +125 |            | °C        |

| Thermal Characteristics SOIC-8 Plastic Package Maximum Power Dissipation @ T <sub>A</sub> = 25°C (Note 1) Thermal Resistance Junction-to-Air (Note 2) | PD<br>R <sub>θJA</sub> |             | .11<br>1.7 | W<br>°C/W |

| Lead Temperature Soldering (10 sec): Re-flow (SMD styles only)  Pb-Free (Note 3)                                                                      | TL                     | 260         | peak       | °C        |

| Moisture Sensitivity Level (Note 4)                                                                                                                   | MSL                    |             | 1          | -         |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. The maximum package power dissipation limit must not be exceeded.

$$P_D = \frac{T_{J(max)} - T_A}{R_{\theta JA}}$$

- When mounted on a multi-layer board with 35 mm<sup>2</sup> copper area, using 1 oz Cu.

60–180 seconds minimum above 237°C.

Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020A.

# **ELECTRICAL CHARACTERISTICS** (Unless otherwise noted: $V_{IN} = 12 \text{ V}$ , $T_A = 25 ^{\circ}\text{C}$ , unless otherwise specified.)

| Symbol               | Characteristics                                                                    |                     | Min | Тур  | Max | Unit |

|----------------------|------------------------------------------------------------------------------------|---------------------|-----|------|-----|------|

| YSTEM PARA           | AMETERS                                                                            |                     |     |      |     |      |

| V <sub>IN</sub>      | Input Supply Voltage Range                                                         | Normal Operation    | 8.0 |      | 40  | V    |

|                      |                                                                                    | Functional (Note 5) | 6.3 | 1    |     |      |

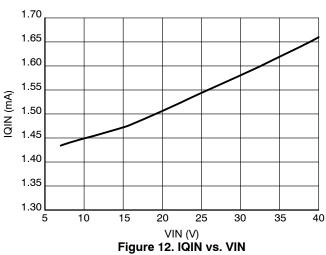

| I <sub>Q_IN</sub>    | Quiescent Current in                                                               | to V <sub>IN</sub>  |     | 1.5  |     | mA   |

| V <sub>CC</sub>      | Internal Regulator Outpu                                                           | t (Note 6)          |     | 5.0  |     | V    |

| V <sub>UV+</sub>     | Under-Voltage Lock-out<br>(V <sub>IN</sub> Rising)                                 | Threshold           | 5.5 | 6.0  | 6.5 | V    |

| V <sub>UV</sub> _    | Under-Voltage Lock-out Threshold<br>(V <sub>IN</sub> Falling)                      |                     | 5.2 | 5.6  | 6.3 | V    |

| URRENT LIM           | IT AND REGULATION                                                                  |                     |     |      |     |      |

| V <sub>CS_UL</sub>   | CS Regulation Upper Limit                                                          | 25°C                | 213 | 220  | 226 | mV   |

|                      | (CS Increasing, FET Turns-OFF)                                                     | -40 to 125°C        | 209 | 1    | 231 |      |

| V <sub>CS_LL</sub>   | CS Regulation Lower Limit                                                          | 25°C                | 174 | 180  | 186 | mV   |

|                      | (CS Decreasing, FET Turns-ON)                                                      | -40 to 125°C        | 171 | 1    | 189 |      |

| V <sub>OCP</sub>     | Over Current Protect<br>(Reference to CS F                                         |                     | 500 |      | mV  |      |

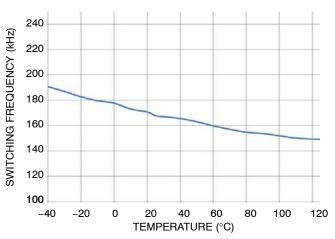

| F <sub>SW</sub>      | Switching Frequency Ranç                                                           |                     |     | 1400 | kHz |      |

| IM INPUT             |                                                                                    |                     |     |      | •   |      |

| V <sub>PWMH/L</sub>  | PWM (DIM/EN) high level in                                                         | 1.4                 |     |      | V   |      |

| V <sub>PWML</sub>    | PWM (DIM/EN) low level input voltage                                               |                     |     |      | 0.4 | V    |

| I <sub>DIM-PU</sub>  | DIM/EN Pull-up Current                                                             |                     |     | 50   |     | μΑ   |

| f <sub>pwm</sub>     | PWM (DIM/EN) dimming frequency range                                               |                     | 0.1 |      | 20  | kHz  |

| dmax                 | Maximum Duty Cycle (Note 7)                                                        |                     |     | 100  |     | %    |

| OWER MOSF            | ET                                                                                 |                     | •   |      | •   |      |

| V <sub>BRDSS</sub>   | Drain-to-Source Breakdo                                                            | wn Voltage          | 40  |      |     | V    |

| I <sub>DSS</sub>     | Drain-to-Source Leakage Current<br>(V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 40 V) |                     |     |      | 10  | μΑ   |

| R <sub>DS(on)</sub>  | On Resistance<br>(Id = 500 mA)                                                     |                     |     |      | 55  | mΩ   |

| V <sub>SD</sub>      | Source-Drain Body I<br>(Forward On-Volta                                           |                     | 0.8 | 1.1  | V   |      |

| t <sub>PD_Off</sub>  | Propagation Delay V <sub>CS_UL</sub> - LX_High                                     |                     |     | 35   |     | ns   |

| HERMAL SHU           | JTDOWN                                                                             |                     |     |      |     | _    |

| T <sub>SD</sub>      | Thermal Shutdown                                                                   |                     |     | 165  |     | °C   |

| T <sub>Hyst</sub>    | Thermal Hysteresis                                                                 |                     |     | 40   |     | °C   |

| FF TIMER             |                                                                                    |                     |     |      |     |      |

| t <sub>OFF-MIN</sub> | Minimum Off-tim                                                                    | ne                  |     | 137  |     | ns   |

<sup>5.</sup> The functional range of V<sub>IN</sub> is the voltage range over which the device will function. Output current and internal parameters may deviate from normal values for V<sub>IN</sub> and V<sub>CC</sub> voltages between 6.3 V and 8 V, depending on load conditions

6. V<sub>CC</sub> should not be driven from a voltage higher than V<sub>IN</sub> or in the absence of a voltage at V<sub>IN</sub>.

7. Guaranteed by design.

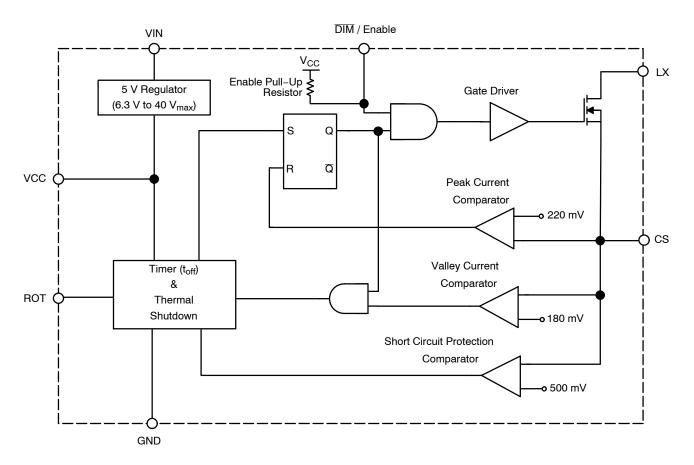

Figure 2. Simplified Block Diagram

# TYPICAL APPLICATION CIRCUITS AND WAVEFORMS

(T<sub>J</sub> = 25°C, Unless Otherwise Specified)

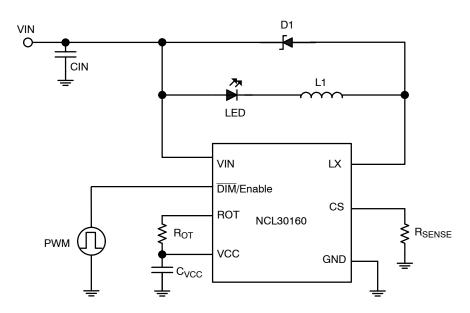

Figure 3. Typical Application Circuit To Drive One LED (Buck)

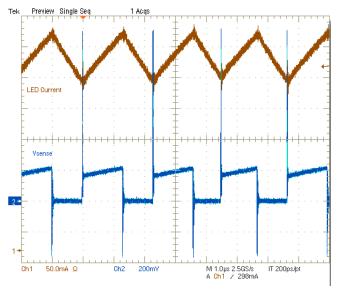

Figure 4. Typical Operation Waveforms (V<sub>CC</sub> = 12 V, V<sub>LED</sub> = 6.5 V, R<sub>SENSE</sub> = 0.68  $\Omega$ , L = 100  $\mu$ H)

# THEORY OF OPERATION

This switching power supply is comprised of an inverted buck regulator controlled by a current mode, hysteretic control circuit. The buck regulator operates exactly like a conventional buck regulator except the power device placement has been inverted to allow for a low side power FET. Referring to Figure 1, when the FET is conducting, current flows from the input,through the inductor, the LED and the FET to ground.

When the FET shuts off, current continues to flow through the inductor and LED, but is diverted through the diode (D1). This operation keeps the current in the LED continuous with a continuous current ramp.

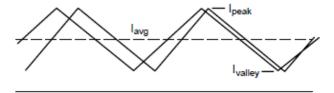

The control circuit controls the current hysteretically. Figure 2 illustrates the operation of this circuit. The CS comparator thresholds are set to provide a 10% current ripple. The peak current comparator threshold of 220 mV sets  $I_{peak}$  at 10% above the average current while the valley current comparator threshold of 180 mV sets  $I_{valley}$  at 10% below the average current.

When the FET is conducting, the current in the inductor ramps up. This current is sensed by an external sense resistor that is connected from CS to ground. When the CS pin reaches 220 mV, the peak current comparator turns off the power FET. A conventional hysteretic controller would monitor the load current and turn the switch back on when the CS pin reaches 180 mV. But in this topology, the current information is not available to the control circuit when the FET is off. To set the proper FET off time, the CS voltage is

sensed when the FET is turned back on and a correction signal is sent to the off time circuit to adjust the off time as necessary.

Figure 5. Typical Current Waveforms

The current waveshape is triangular, and the peak and valley currents are controlled. The average value for a triangular waveshape is halfway between the peak and valley, so even with changes in duty cycle due to input voltage variations or load changes, the average current will remain constant.

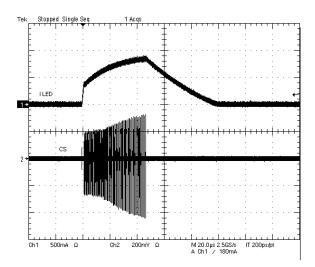

In the event there is a short-circuit across the LEDs, a large amount of current could potentially flow through the circuit during startup. To protect against this, the NCL30160 comes with a short circuit protection feature. If the voltage on the CS pin is detected to be greater than 500 mV (equating to 2.5 times the intended average output current), the NCL31060 will turn off the FET, and prevent the FET from turning on again until power is recycled to NCL30160.

**Figure 6. Short-Circuit Protection**

When  $V_{IN}$  rises above the UVLO threshold voltage, switching operation of the FET will begin. However, until the  $V_{IN}$  voltage reaches 8 V, the VCC regulator may not provide the expected gate drive voltage to the FET. This could result in the  $R_{DS(on)}$  of the FET being higher than expected or there not being enough gate drive capability to operate at the maximum rated switching frequency. For optimal performance, it is recommended to operate the part at a  $V_{IN}$  voltage of 8 V or greater.

#### **Setting The Output Current**

The average output current is determined as being the middle of the peak and valley of the output current, set by the CS comparator thresholds. The nominal average output current will be the current value equivalent to 200 mV at the CS pin. The proper  $R_{\rm SENSE}$  value for a desired average output current can be calculated by:

$$R_{SENSE} = \frac{200 \text{ mV}}{I_{LED}}$$

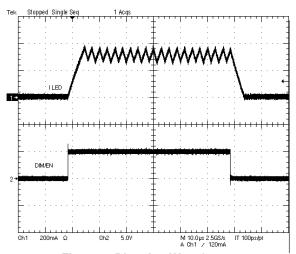

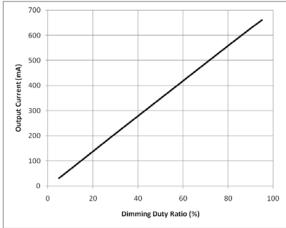

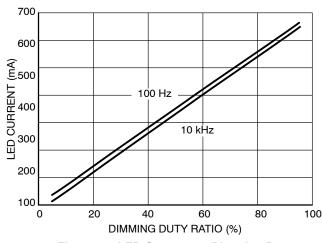

#### **PWM Dimming**

For a given R<sub>SENSE</sub> value, the average output current, and therefore the brightness of the LED, can be set to a lower value through the DIM/EN pin. When the DIM/EN pin is brought low, the internal FET will turn off and switching will remain off until the DIM/EN pin is brought back into its high state.

Figure 7. Dimming Waveforms

By applying a pulsed signal to DIM/EN, the average output current can be adjusted to the duty ratio of the pulsed signal. It is recommended to keep the frequency of the DIM/EN signal above 100 Hz to avoid any visible flickering of the LED.

Figure 8. Dimming Performance

#### **Inductor Selection**

The inductor that is used directly affects the switching frequency the driver operates at. The value of the inductor sets the slope at which the output current rises and falls during the switching operation. The slope of the current, in turn, determines how long it takes the current to go from the valley point of the current ripple to the peak when the FET is on and the current and rising, and how long it takes the current to go from the peak point of the current to the valley when the FET is off and the current is falling. These times can be approximated from the following equations:

$$= \frac{L \times \Delta I}{\text{VIN} - \text{V}_{\text{LED}} - \text{I}_{\text{OUT}} \times \left(\text{FET}_{\text{R}_{\text{DS}}}(\text{on}) + \text{DCR}_{\text{L}} + \text{R}_{\text{SENSE}}\right)}$$

$$t_{OFF} = \frac{L \times \Delta I}{V_{LED} + V_{diode} + I_{OUT} \times DCR_{L}}$$

Where DCR<sub>L</sub> is the dc resistance of the inductor,  $V_{LED}$  is the forward voltages of the LEDs,  $FET_{RDS(ON)}$  is the on-resistance of the power MOSFET, and  $V_{diode}$  is the forward voltage of the catch diode.

The switching frequency can then be approximated from the following:

$$f_{SW} = \frac{1}{t_{ON} + t_{OFF}}$$

Higher values of inductance lead to slower rates of rise and fall of the output current. This allows for smaller discrepancies between the expected and actual output current ripple due to propagation delays between sensing at the CS pin and the turning on and off of the power MOSFET. However, the inductor value should be chosen such that the peak output current value does not exceed the rated saturation current of the inductor.

#### **Catch Diode Selection**

The catch diode needs to be selected such that average current through the diode does not exceed the rated average forward current of the diode. The average current through the diode can be calculated as:

$$I_{avg\_diode} = I_{OUT} \times \frac{t_{OFF}}{t_{ON} + t_{OFF}}$$

It is also important to select a diode that is capable of withstanding the peak reverse voltage it will see in the application. It is recommended to select a diode with a rated reverse voltage greater than VIN. It is also recommended to use a low-capacitance Schottky diode for better efficiency performance.

#### **Selecting The Off-Time Setting Resistor**

The off-time setting resistor ( $R_{OT}$ ) programs the NCL30160 with the initial time duration that the MOSFET is turned off when the switching operation begins. During subsequent switching cycles, the voltage at the CS pin is sensed every time the MOSFET is turned on, and the off-time will be adjusted depending on how much of a discrepancy exists between the sensed value and the CS lower limit threshold value. The  $R_{OT}$  value can be calculated using the following equation:

$$R_{OT} = t_{OFF} \times 10^{11} \Omega$$

Where  $t_{\mbox{OFF}}$  is the expected off time during normal switching operation, calculated in the Inductor Selection section above.

#### **Input Capacitor**

A decoupling capacitor from VIN to ground should be used to provide the current needed when the power MOSFET turns on. A 4.7  $\mu F$  ceramic capacitor is recommended.

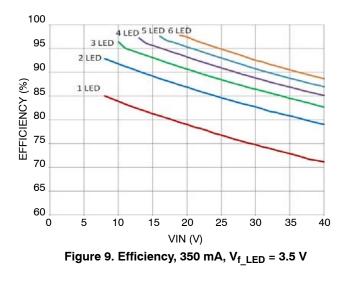

Figure 10. Efficiency, 700 mA,  $V_{f\_LED}$  = 3.5 V

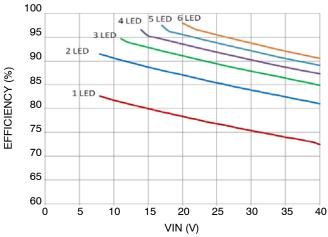

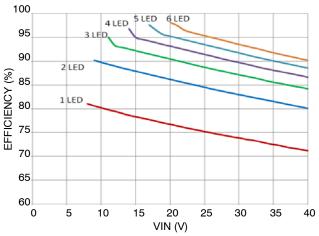

Figure 11. Efficiency, 1 A,  $V_{f\_LED}$  = 3.5 V

Figure 13. LED Current vs. Dimming Duty Ratio

Figure 14. Switching Frequency vs. Temperature (12 V  $V_{IN}$ , 3 LEDs, 0.7 Å, 0.47  $\mu H$ )

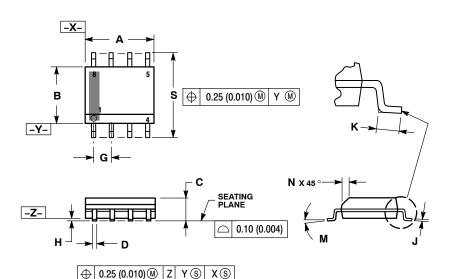

SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |           | INCHES |           |  |

|-----|-------------|-----------|--------|-----------|--|

| DIM | MIN         | MAX       | MIN    | MAX       |  |

| Α   | 4.80        | 5.00      | 0.189  | 0.197     |  |

| В   | 3.80        | 4.00      | 0.150  | 0.157     |  |

| С   | 1.35        | 1.75      | 0.053  | 0.069     |  |

| D   | 0.33        | 0.51      | 0.013  | 0.020     |  |

| G   | 1.27        | 1.27 BSC  |        | 0.050 BSC |  |

| Н   | 0.10        | 0.10 0.25 |        | 0.010     |  |

| J   | 0.19        | 0.25      | 0.007  | 0.010     |  |

| K   | 0.40        | 1.27      | 0.016  | 0.050     |  |

| М   | 0 °         | 8 °       | 0 °    | 8 °       |  |

| N   | 0.25        | 0.50      | 0.010  | 0.020     |  |

| S   | 5.80        | 6.20      | 0.228  | 0.244     |  |

#### **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

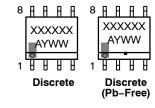

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location = Wafer Lot = Year = Work Week

= Pb-Free Package

XXXXXX = Specific Device Code = Assembly Location Α = Year ww = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

#### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repositor Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                | PAGE 1 OF 2 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. **onsemi** does not convey any license under its patent rights nor the rights of others.

### SOIC-8 NB CASE 751-07 ISSUE AK

### **DATE 16 FEB 2011**

|                                                                                                                                                                    |                                                                                                                                                           |                                                                                                                                                     | D, 112 101 2D 2                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE 8. EMITTER                                                                 | STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1 8. EMITTER, #1 STYLE 6:      | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1 STYLE 7:                   | STYLE 4: PIN 1. ANODE 2. ANODE 3. ANODE 4. ANODE 5. ANODE 6. ANODE 7. ANODE 8. COMMON CATHODE STYLE 8:                                                                   |

| PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                                        | PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                                                             | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER #2                                                                                                              |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND                                                              | STYLE 11:  PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                              | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                  |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                              | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                                     | 8. DRAIN 1  STYLE 15: PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON   | STYLE 16:  PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2 4. BASE, DIE #2 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 7. COLLECTOR, DIE #1 8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                                 | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                    |

| STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6                                        | STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3. COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | STYLE 24: PIN 1. BASE 2. EMITTER 3. COLLECTOR/ANODE 4. COLLECTOR/ANODE 5. CATHODE 6. CATHODE 7. COLLECTOR/ANODE 8. COLLECTOR/ANODE                                       |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                         | STYLE 26: PIN 1. GND 2. dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                                    | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                            | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V_MON 6. VBULK 7. VBULK 8. VIN                                                                         |

| STYLE 29: PIN 1. BASE, DIE #1 2. EMITTER, #1 3. BASE, #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                        | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1/DRAIN 2 6. SOURCE 1/DRAIN 2 7. SOURCE 1/DRAIN 2 8. GATE 1                           |                                                                                                                                                     |                                                                                                                                                                          |

| DOCUMENT NUMBER: | 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the Document Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| DESCRIPTION:     | SOIC-8 NB                                                                                                                                                                        |  | PAGE 2 OF 2 |

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

$\Diamond$