SLVSBJ2C - FEBRUARY 2013-REVISED JULY 2016

**TPS2546**

# TPS2546 USB Charging Port Controller and Power Switch With Load Detection

#### Features

- D+/D- CDP/DCP Modes per USB Battery Charging Specification 1.2

- D+/D- Shorted Mode per Chinese Telecommunication Industry Standard YD/T 1591-2009

- Supports Non-BC1.2 Charging Modes by Automatic Selection:

- D+/D- Divider Modes 2 V/2.7 V and 2.7 V/2 V

- D+/D- 1.2-V Mode

- Supports Sleep-Mode Charging and Mouse/Keyboard Wakeup

- Automatic SDP/CDP Switching for Devices That Do Not Connect to CDP Ports

- Load Detection for Power Supply Control in S4/S5 Charging and Port Power Management in All Charge Modes

- Compatible With USB 2.0 and 3.0 Power Switch Requirements

- Integrated 73-mΩ (Typical) High-Side MOSFET

- Adjustable Current-Limit up to 3 A (Typical)

- Operating Range: 4.5 V to 5.5 V

- Max Device Current:

- 2 µA When Device Disabled

- 270 µA When Device Enabled

- Drop-In and BOM Compatible With TPS2543

- Available in 16-Pin WQFN (3.00 mm x 3.00 mm) Package

- 8-kV ESD Rating on DM/DP Pins

- UL Listed File No. E169910 and CB certified

# 2 Applications

- USB Ports (Host and Hubs)

- Notebook and Desktop PCs

- Universal Wall-Charging Adapters

# 3 Description

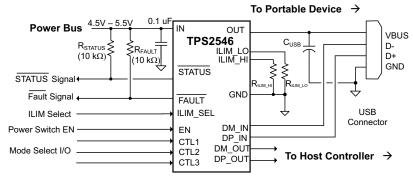

The TPS2546 is a USB charging port controller and power switch with an integrated USB 2.0 high-speed data line (D+/D-) switch. TPS2546 provides the electrical signatures on D+/D- to support charging schemes listed under Feature Description. TI tests charging of popular mobile phones, tablets, and media devices with the TPS2546 to ensure compatibility with both BC1.2 compliant, and non-BC1.2 compliant devices.

In addition to charging popular devices, the TPS2546 also supports two distinct power management features, namely, power wake and port power management (PPM) through the STATUS pin. Power wake allows for power supply control in S4/S5 charging and PPM the ability to manage port power in a multi-port application. Additionally, system wake up (from S3) with a mouse/keyboard (both low speed and full speed) is fully supported in the TPS2546.

The TPS2546 73-m $\Omega$  power-distribution switch is intended for applications where heavy capacitive loads and short-circuits are likely to be encountered. programmable current thresholds provide flexibility for setting current limits and load detect thresholds.

# Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TPS2546     | WQFN (16) | 3.00 mm × 3.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

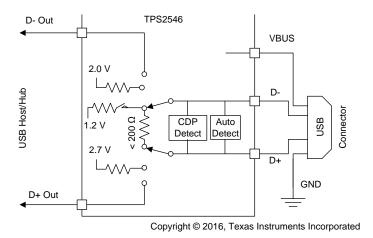

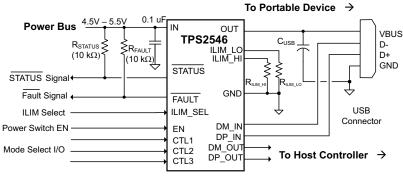

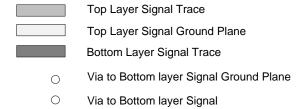

#### Simplified Schematic

Copyright © 2016, Texas Instruments Incorporated

# **Table of Contents**

| 1 | Features 1                                              | 8.3    | Feature Description                            | 15      |

|---|---------------------------------------------------------|--------|------------------------------------------------|---------|

| 2 | Applications 1                                          | 8.4    | Device Functional Modes                        | 26      |

| 3 | Description 1                                           | 9 App  | olication and Implementation                   | 29      |

| 4 | Revision History2                                       | 9.1    | Application Information                        | 29      |

| 5 | Pin Configuration and Functions                         | 9.2    | Typical Application                            | 30      |

| 6 | Specifications4                                         | 10 Po  | wer Supply Recommendations                     | 33      |

| ٠ | 6.1 Absolute Maximum Ratings                            | 11 Lay | out                                            | 33      |

|   | 6.2 ESD Ratings                                         | 11.    |                                                |         |

|   | 6.3 Recommended Operating Conditions                    | 11.3   | 2 Layout Example                               | 34      |

|   | 6.4 Thermal Information                                 | 12 De  | vice and Documentation Support                 | 35      |

|   | 6.5 Electrical Characteristics                          | 12.    | Documentation Support                          | 35      |

|   | 6.6 Electrical Characteristics: High-Bandwidth Switch 6 | 12.    | 2 Receiving Notification of Documentation Upda | ates 35 |

|   | 6.7 Electrical Characteristics: Charging Controller 7   | 12.    | 3 Community Resources                          | 35      |

|   | 6.8 Typical Characteristics9                            | 12.    | Trademarks                                     | 35      |

| 7 | Parameter Measurement Information                       | 12.    | 5 Electrostatic Discharge Caution              | 35      |

| 8 | Detailed Description                                    | 12.0   | Glossary                                       | 35      |

| • | 8.1 Overview                                            |        | chanical, Packaging, and Orderable             | 0.5     |

|   | 8.2 Functional Block Diagram 15                         | Info   | ormation                                       | 35      |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C        | hanges from Revision B (January 2016) to Revision C                                                                                                                                                                                                                                  | Page |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •        | Corrected references to images in the Feature Description section                                                                                                                                                                                                                    | 15   |

| <u>•</u> | Added text to the Layout Guidelines section                                                                                                                                                                                                                                          | 34   |

| C        | hanges from Revision A (Febuary 2013) to Revision B                                                                                                                                                                                                                                  | Page |

| •        | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section. | 1    |

| C        | hanges from Original (February 2013) to Revision A                                                                                                                                                                                                                                   | Page |

| •        | Changed the device From: Preview To: Production                                                                                                                                                                                                                                      | 1    |

Product Folder Links: TPS2546

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

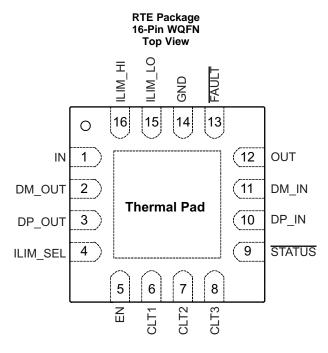

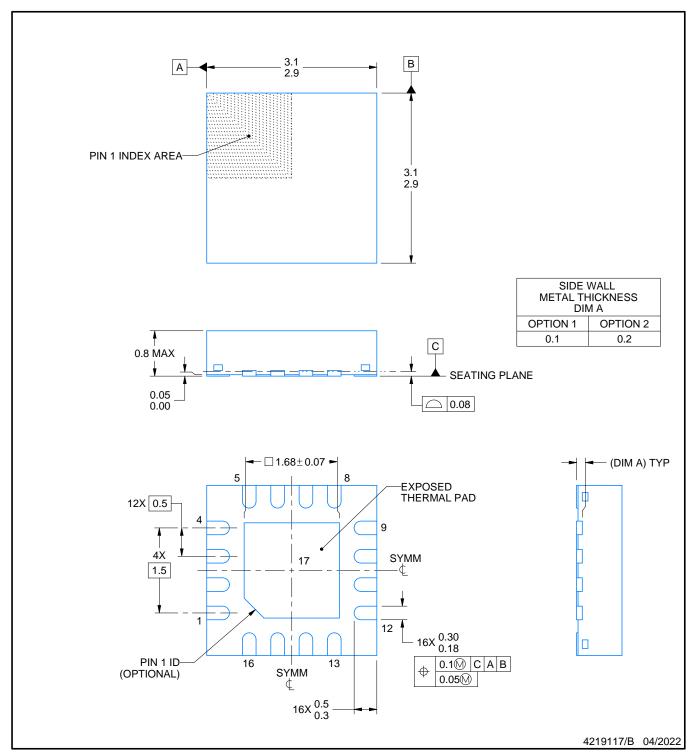

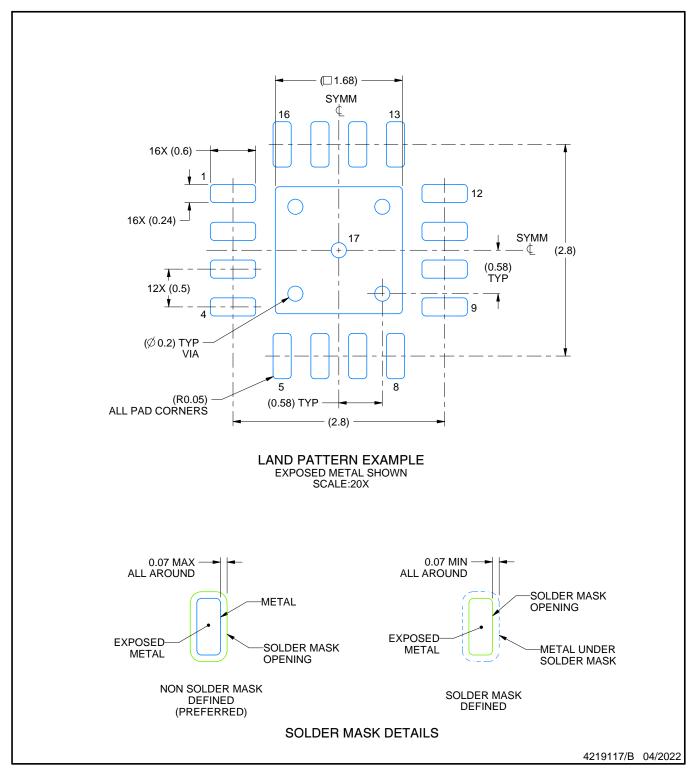

# 5 Pin Configuration and Functions

**Pin Functions**

|        | PIN            | TYPE(1) | DESCRIPTION                                                                                                                                                                                                                         |

|--------|----------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.    | NAME           | ITPE    | DESCRIPTION                                                                                                                                                                                                                         |

| 1      | IN             | Р       | Input voltage and supply voltage; connect 0.1 $\mu F$ or greater ceramic capacitor from IN to GND as close to the device as possible.                                                                                               |

| 2      | DM_OUT         | I/O     | D– data line to USB host controller.                                                                                                                                                                                                |

| 3      | DP_OUT         | I/O     | D+ data line to USB host controller.                                                                                                                                                                                                |

| 4      | ILIM_SEL       | 1       | Logic-level input signal used to control the charging mode, current limit threshold, and load detection; see Table 3. Can be tied directly to IN or GND without pullup or pulldown resistor.                                        |

| 5      | EN             | I       | Logic-level input for turning the power switch and the signal switches on/off; logic low turns off the signal and power switches and holds OUT in discharge. Can be tied directly to IN or GND without pullup or pulldown resistor. |

| 6      | CTL1 I         |         |                                                                                                                                                                                                                                     |

| 7 CTL2 |                | I       | Logic-level inputs used to control the charging mode and the signal switches; see Table 3. Can be tied directly to IN or GND without pullup or pulldown resistor.                                                                   |

| 8      | CTL3           | I       | directly to fix of Civib without pullup of pulluowit register.                                                                                                                                                                      |

| 9      | STATUS         | 0       | Active-low open-drain output, asserted in load detection conditions.                                                                                                                                                                |

| 10     | DP_IN          | I/O     | D+ data line to downstream connector.                                                                                                                                                                                               |

| 11     | DM_IN          | I/O     | D– data line to downstream connector.                                                                                                                                                                                               |

| 12     | OUT            | Р       | Power-switch output.                                                                                                                                                                                                                |

| 13     | FAULT          | 0       | Active-low open-drain output, asserted during overtemperature or current limit conditions.                                                                                                                                          |

| 14     | GND            | Р       | Ground connection.                                                                                                                                                                                                                  |

| 15     | ILIM_LO        | I       | External resistor connection used to set the low current-limit threshold and the load detection current threshold. A resistor to ILIM_LO is optional; see <i>Current-Limit Settings</i> in <i>Detailed Description</i> .            |

| 16     | ILIM_HI        | I       | External resistor connection used to set the high-current-limit threshold.                                                                                                                                                          |

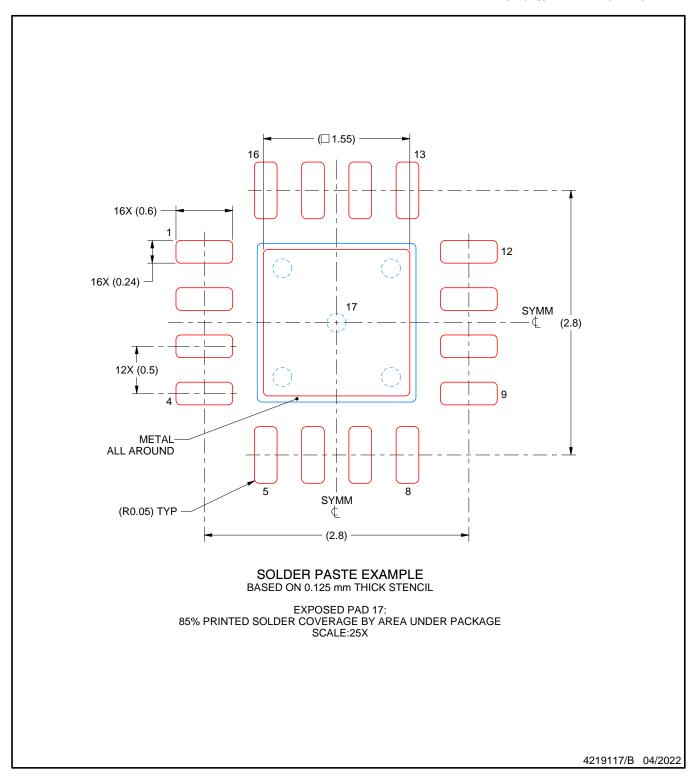

| _      | Thermal<br>Pad | _       | Internally connected to GND; used to heatsink the part to the circuit board traces. Connect to GND plane.                                                                                                                           |

(1) G = ground, I = input, O = output, P = power.

Submit Documentation Feedback

Product Folder Links: TPS2546

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                |                                                                          | MIN                | MAX                | UNIT |

|------------------------------------------------|--------------------------------------------------------------------------|--------------------|--------------------|------|

|                                                | IN, EN, ILIM_LO, ILIM_HI, FAULT, STATUS, ILIM_SEL, CTL1, CTL2, CTL3, OUT | -0.3               | 7                  |      |

| Voltage                                        | IN to OUT                                                                | <b>-</b> 7         | 7                  | V    |

|                                                | DP_IN, DM_IN, DP_OUT, DM_OUT                                             | -0.3               | (IN + 0.3) or 5.7  |      |

| Input clamp current                            | DP_IN, DM_IN, DP_OUT, DM_OUT                                             |                    | ±20                | mA   |

| Continuous current in SDP or CDP mode          | DP_IN to DP_OUT or DM_IN to DM_OUT                                       |                    | ±100               |      |

| Continuous current in BC1.2 DCP mode           | DP_IN to DM_IN                                                           |                    | ±50                |      |

| Continuous output current                      | OUT                                                                      | Inte               | ernally limited    |      |

| Continuous output sink current                 | FAULT, STATUS                                                            | 25                 |                    | mA   |

| Continuous output source current               | ILIM_LO, ILIM_HI                                                         | Internally limited |                    | mA   |

| Operating junction temperature, T <sub>J</sub> |                                                                          | -40                | Internally limited | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                                            |                    |                                                       |                           | VALUE | UNIT |

|--------------------------------------------|--------------------|-------------------------------------------------------|---------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge |                    |                                                       | HBM                       | ±2000 |      |

|                                            | 001 <sup>(1)</sup> | HBM wrt GND and each other, DP_IN, DM_IN, OUT         | ±8000                     | V     |      |

|                                            |                    | Charged-device model (CDM), per JEDEC specification J | ESD22-C101 <sup>(2)</sup> | ±500  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

voltages are referenced to GND (unless otherwise noted)

|                  |                                                                                         | MIN  | MAX      | UNIT      |

|------------------|-----------------------------------------------------------------------------------------|------|----------|-----------|

| $V_{IN}$         | Input voltage, IN                                                                       | 4.5  | 5.5      | V         |

|                  | Input voltage, logic-level inputs, EN, CTL1, CTL2, CTL3, ILIM_SEL                       | 0    | 5.5      | V         |

|                  | Input voltage, data line inputs, DP_IN, DM_IN, DP_OUT, DM_OUT                           | 0    | $V_{IN}$ | V         |

| $V_{IH}$         | High-level input voltage, EN, CTL1, CTL2, CTL3, ILIM_SEL                                | 1.8  |          | V         |

| $V_{IL}$         | Low-level input voltage, EN, CTL1, CTL2, CTL3, ILIM_SEL                                 |      | 8.0      | V         |

|                  | Continuous current, data line inputs, SDP or CDP mode, DP_IN to DP_OUT, DM_IN to DM_OUT |      | ±30      | mA        |

|                  | Continuous current, data line inputs, BC1.2 DCP mode, DP_IN to DM_IN                    |      | ±15      | mA        |

| I <sub>OUT</sub> | Continuous output current, OUT                                                          | 0    | 2.5      | Α         |

|                  | Continuous output sink current, FAULT, STATUS                                           | 0    | 10       | mA        |

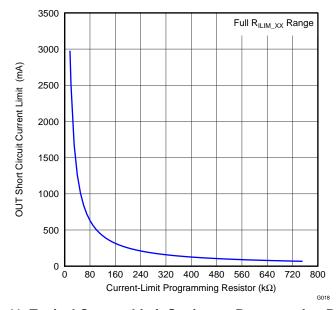

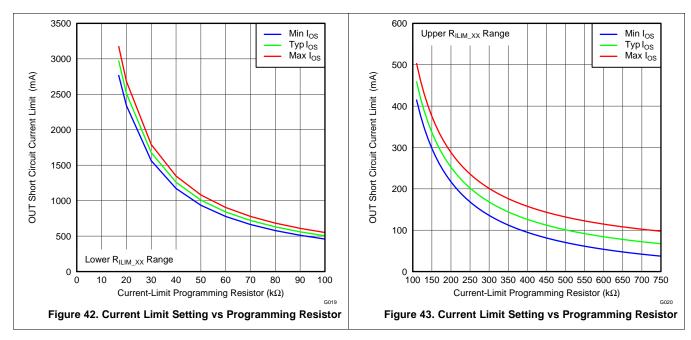

| $R_{ILIM\_XX}$   | Current-limit set resistors                                                             | 16.9 | 750      | $k\Omega$ |

| $T_J$            | Operating virtual junction temperature                                                  | -40  | 125      | °C        |

Product Folder Links: TPS2546

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.4 Thermal Information

|                      |                                              | TPS2546    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RTE (WQFN) | UNIT |

|                      |                                              | 16 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 53.4       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 51.4       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 17.2       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 3.7        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 20.7       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 3.9        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 6.5 Electrical Characteristics

Unless otherwise noted:  $-40 \le T_J \le 125^{\circ}C$ ,  $4.5 \ V \le V_{IN} \le 5.5 \ V$ ,  $V_{EN} = V_{IN}$ ,  $V_{ILIM\_SEL} = V_{IN}$ ,  $V_{CTL1} = V_{CTL2} = V_{CTL3} = V_{IN}$ .  $R_{\overline{FAULT}} = R_{\overline{STATUS}} = 10 \ k\Omega$ ,  $R_{ILIM\_HI} = 20 \ k\Omega$ ,  $R_{ILIM\_LO} = 80.6 \ k\Omega$ . Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                     | PARAMETER                                 | TEST CONDITIONS                                                                                                      | MIN  | TYP  | MAX  | UNIT      |

|---------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------|------|------|-----------|

| POWER               | SWITCH                                    |                                                                                                                      |      |      |      |           |

|                     |                                           | T <sub>J</sub> = 25°C, I <sub>OUT</sub> = 2 A                                                                        |      | 73   | 84   |           |

| R <sub>DS(on)</sub> | ON resistance <sup>(1)</sup>              | $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 85^{\circ}\text{C}, \text{ I}_{\text{OUT}} = 2 \text{ A}$           |      | 73   | 105  | $m\Omega$ |

|                     |                                           | $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}, \text{ I}_{\text{OUT}} = 2 \text{ A}$          |      | 73   | 120  |           |

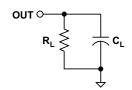

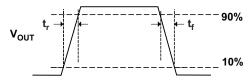

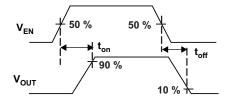

| t <sub>r</sub>      | OUT voltage rise time                     | $V_{IN}$ = 5 V, $C_L$ = 1 $\mu$ F, $R_L$ = 100 $\Omega$ (see Figure 23 and                                           | 0.7  | 1    | 1.6  |           |

| t <sub>f</sub>      | OUT voltage fall time                     | Figure 24)                                                                                                           |      | 0.35 | 0.5  | ms        |

| t <sub>on</sub>     | OUT voltage turnon time                   | $V_{IN}$ = 5 V, $C_L$ = 1 $\mu$ F, $R_L$ = 100 $\Omega$ (see Figure 23 and                                           |      | 2.7  | 4    |           |

| t <sub>off</sub>    | OUT voltage turnoff time                  | Figure 25)                                                                                                           |      | 1.7  | 3    | ms        |

| I <sub>REV</sub>    | Reverse leakage current                   | $V_{OUT} = 5.5 \text{ V}, V_{IN} = V_{EN} = 0 \text{ V}, -40 \le T_{J} \le 85^{\circ}\text{C},$<br>Measure $I_{OUT}$ |      |      | 2    | μΑ        |

| DISCHA              | RGE                                       |                                                                                                                      | 1    |      |      |           |

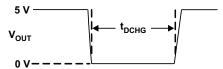

| R <sub>DCHG</sub>   | OUT discharge resistance                  |                                                                                                                      | 400  | 500  | 630  | Ω         |

| t <sub>DCHG_L</sub> | Long OUT discharge hold time              | Time V <sub>OUT</sub> < 0.7 V (see Figure 26)                                                                        | 1.3  | 2    | 2.9  | s         |

| t <sub>DCHG_S</sub> | Short OUT discharge hold time             | Time V <sub>OUT</sub> < 0.7 V (see Figure 26)                                                                        | 205  | 310  | 450  | ms        |

| EN, ILIM            | SEL, CTL1, CTL2, CTL3 INPUTS              |                                                                                                                      | •    |      | •    |           |

|                     | Input pin rising logic threshold voltage  |                                                                                                                      | 1    | 1.35 | 1.7  | V         |

|                     | Input pin falling logic threshold voltage |                                                                                                                      | 0.85 | 1.15 | 1.45 |           |

|                     | Hysteresis <sup>(2)</sup>                 |                                                                                                                      |      | 200  |      | mV        |

|                     | Input current                             | Pin voltage = 0 V or 5.5 V                                                                                           | -0.5 |      | 0.5  | μA        |

| ILIMSEL             | CURRENT LIMIT                             |                                                                                                                      |      |      | ,    |           |

|                     |                                           | $V_{ILIM\_SEL} = 0 \text{ V}, \text{ R}_{ILIM\_LO} = 210 \text{ k}\Omega$                                            | 205  | 240  | 275  |           |

|                     |                                           | $V_{ILIM\_SEL} = 0 \text{ V}, R_{ILIM\_LO} = 80.6 \text{ k}\Omega$                                                   | 575  | 625  | 680  |           |

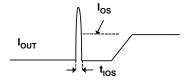

| Ios                 | OUT short-circuit current limit (1)       | $V_{ILIM\_SEL} = 0 \text{ V}, R_{ILIM\_LO} = 22.1 \text{ k}\Omega$                                                   | 2120 | 2275 | 2430 | mA        |

|                     |                                           | $V_{ILIM\_SEL} = V_{IN}, R_{ILIM\_HI} = 20 \text{ k}\Omega$                                                          | 2340 | 2510 | 2685 |           |

|                     |                                           | $V_{ILIM\_SEL} = V_{IN}, R_{ILIM\_HI} = 16.9 \text{ k}\Omega$                                                        | 2770 | 2970 | 3170 |           |

| t <sub>IOS</sub>    | Response time to OUT short-circuit (2)    | $V_{IN} = 5 \text{ V}, \text{ R} = 0.1\Omega, \text{ lead length} = 2 \text{ inches}$ (see Figure 27)                |      | 1.5  |      | μs        |

<sup>(1)</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; Thermal effects must be taken into account separately.

<sup>(2)</sup> These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

# **Electrical Characteristics (continued)**

Unless otherwise noted:  $-40 \le T_J \le 125^{\circ}C$ ,  $4.5 \ V \le V_{IN} \le 5.5 \ V$ ,  $V_{EN} = V_{IN}$ ,  $V_{ILIM\_SEL} = V_{IN}$ ,  $V_{CTL1} = V_{CTL2} = V_{CTL3} = V_{IN}$ .  $R_{\overline{FAULT}} = R_{\overline{STATUS}} = 10 \ k\Omega$ ,  $R_{ILIM\_LO} = 80.6 \ k\Omega$ . Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                     | PARAMETER                                     | TEST CONDITIONS                                                                                                | MIN | TYP | MAX | UNIT |

|---------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SUPPLY              | CURRENT                                       |                                                                                                                |     |     |     |      |

| I <sub>IN_OFF</sub> | Disabled IN supply current                    | $V_{EN} = 0 \text{ V}, V_{OUT} = 0 \text{ V}, -40 \le T_{J} \le 85^{\circ}\text{C}$                            |     | 0.1 | 2   | μΑ   |

|                     |                                               | V <sub>CTL1</sub> = V <sub>CTL2</sub> = V <sub>IN</sub> , V <sub>CTL3</sub> = 0 V, V <sub>ILIM_SEL</sub> = 0 V |     | 165 | 220 |      |

|                     |                                               | V <sub>CTL1</sub> = V <sub>CTL2</sub> = V <sub>CTL3</sub> = V <sub>IN</sub> , V <sub>ILIM_SEL</sub> = 0 V      |     | 175 | 230 |      |

| $I_{IN\_ON}$        | Enabled IN supply current                     | $V_{CTL1} = V_{CTL2} = V_{IN}, V_{CTL3} = 0 \text{ V}, V_{ILIM\_SEL} = V_{IN}$                                 |     | 185 | 240 | μΑ   |

|                     |                                               | $V_{CTL1} = V_{CTL2} = V_{IN}, V_{CTL3} = VIN, V_{ILIM\_SEL} = V_{IN}$                                         |     | 195 | 250 |      |

|                     |                                               | $V_{CTL1} = 0 \text{ V}, V_{CTL2} = V_{CTL3} = V_{IN}$                                                         |     | 215 | 270 |      |

| UNDERV              | OLTAGE LOCKOUT                                |                                                                                                                |     |     |     |      |

| $V_{UVLO}$          | IN rising UVLO threshold voltage              |                                                                                                                | 3.9 | 4.1 | 4.3 | V    |

|                     | Hysteresis (2)                                |                                                                                                                |     | 100 |     | mV   |

| FAULT               |                                               |                                                                                                                |     |     |     |      |

|                     | Output low voltage                            | I <sub>FAULT</sub> = 1 mA                                                                                      |     |     | 100 | mV   |

|                     | OFF-state leakage                             | V <sub>FAULT</sub> = 5.5 V                                                                                     |     |     | 1   | μΑ   |

|                     | Overcurrent FAULT rising and falling deglitch |                                                                                                                | 5   | 8.2 | 12  | ms   |

| STATUS              |                                               |                                                                                                                |     |     |     |      |

|                     | Output low voltage                            | I <sub>STATUS</sub> = 1 mA                                                                                     |     |     | 100 | mV   |

|                     | OFF-state leakage                             | V <sub>STATUS</sub> = 5.5 V                                                                                    |     |     | 1   | μΑ   |

| THERMA              | L SHUTDOWN                                    |                                                                                                                |     |     |     |      |

|                     | Thermal shutdown threshold                    |                                                                                                                | 155 |     |     |      |

|                     | Thermal shutdown threshold in current-limit   |                                                                                                                | 135 |     |     | °C   |

|                     | Hysteresis (2)                                |                                                                                                                |     | 20  |     |      |

#### 6.6 Electrical Characteristics: High-Bandwidth Switch

Unless otherwise noted:  $-40 \le T_J \le 125 ^{\circ}\text{C}$ ,  $4.5 \text{ V} \le V_{\text{IN}} \le 5.5 \text{ V}$ ,  $V_{\text{EN}} = V_{\text{IN}}$ ,  $V_{\text{ILIM\_SEL}} = V_{\text{IN}}$ ,  $V_{\text{CTL1}} = V_{\text{CTL2}} = V_{\text{CTL3}} = V_{\text{IN}}$ .  $R_{\overline{\text{FAULT}}} = R_{\overline{\text{STATUS}}} = 10 \text{ k}\Omega$ ,  $R_{\overline{\text{ILIM\_HI}}} = 20 \text{ k}\Omega$ ,  $R_{\overline{\text{ILIM\_LO}}} = 80.6 \text{ k}\Omega$ . Positive currents are into pins. Typical values are at 25 °C. All voltages are with respect to GND.

|                   | PARAMETER                                        | TEST CONDITIONS                                                                                                                        | MIN | TYP  | MAX  | UNIT |

|-------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| HIGH-BA           | NDWIDTH ANALOG SWITCH                            |                                                                                                                                        |     |      |      |      |

|                   | DP/DM switch ON resistance                       | $V_{DP/DM\_OUT} = 0 \text{ V}, I_{DP/DM\_IN} = 30 \text{ mA}$                                                                          |     | 2    | 4    | Ω    |

|                   | DI /Divi switch On resistance                    | $V_{DP/DM\_OUT} = 2.4 \text{ V}, I_{DP/DM\_IN} = -15 \text{ mA}$                                                                       |     | 3    | 6    | 12   |

|                   | Switch resistance mismatch between               | $V_{DP/DM\_OUT} = 0 V$ , $I_{DP/DM\_IN} = 30 mA$                                                                                       |     | 0.05 | 0.15 | Ω    |

|                   | DP / DM channels                                 | $V_{DP/DM\_OUT} = 2.4 \text{ V}, I_{DP/DM\_IN} = -15 \text{ mA}$                                                                       |     | 0.05 | 0.15 | 52   |

|                   | DP/DM switch OFF-state capacitance (1)           | $\begin{aligned} &V_{EN} = 0 \text{ V, } V_{DP/DM\_IN} = 0.3 \text{ V, } V_{ac} = 0.6  V_{pk-pk}, \\ &f = 1 \text{ MHz} \end{aligned}$ |     | 3    | 3.6  | pF   |

|                   | DP/DM switch ON-state capacitance <sup>(2)</sup> | $V_{DP/DM_IN} = 0.3 \text{ V}, V_{ac} = 0.6 V_{pk-pk}, f = 1 \text{ MHz}$                                                              |     | 5.4  | 6.2  | pF   |

| O <sub>IRR</sub>  | OFF-state isolation <sup>(3)</sup>               | V <sub>EN</sub> = 0 V, f = 250 MHz                                                                                                     |     | 33   |      | dB   |

| X <sub>TALK</sub> | ON-state cross channel isolation (3)             | f = 250 MHz                                                                                                                            |     | 52   |      | dB   |

|                   | OFF-state leakage current                        | $V_{EN}$ = 0 V, $V_{DP/DM\_IN}$ = 3.6 V, $V_{DP/DM\_OUT}$ = 0 V, measure $I_{DP/DM\_OUT}$                                              |     | 0.1  | 1.5  | μΑ   |

| BW                | Bandwidth (-3 dB) <sup>(3)</sup>                 | $R_L = 50 \Omega$                                                                                                                      |     | 2.6  |      | GHz  |

| t <sub>pd</sub>   | Propagation delay <sup>(3)</sup>                 |                                                                                                                                        |     | 0.25 |      | ns   |

- (1) The resistance in series with the parasitic capacitance to GND is typically 250  $\Omega$ .

- (2) The resistance in series with the parasitic capacitance to GND is typically 150  $\Omega$

Product Folder Links: TPS2546

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

<sup>3)</sup> These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's product warranty.

# **Electrical Characteristics: High-Bandwidth Switch (continued)**

Unless otherwise noted:  $-40 \le T_J \le 125^{\circ}C$ ,  $4.5 \ V \le V_{IN} \le 5.5 \ V$ ,  $V_{EN} = V_{IN}$ ,  $V_{ILIM\_SEL} = V_{IN}$ ,  $V_{CTL1} = V_{CTL2} = V_{CTL3} = V_{IN}$ .  $R_{\overline{FAULT}} = R_{\overline{STATUS}} = 10 \ k\Omega$ ,  $R_{ILIM\_HI} = 20 \ k\Omega$ ,  $R_{ILIM\_LO} = 80.6 \ k\Omega$ . Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|     | PARAMETER                                                                       | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----|---------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| Tor | between opposite transitions of the port (t <sub>PHL</sub> – t <sub>PLH</sub> ) |                 |     | 0.1 | 0.2 | ns   |

# 6.7 Electrical Characteristics: Charging Controller

Unless otherwise noted:  $-40 \le T_J \le 125^{\circ}C$ ,  $4.5 \ V \le V_{IN} \le 5.5 \ V$ ,  $V_{EN} = V_{IN}$ ,  $V_{ILIM\_SEL} = V_{IN}$ ,  $V_{CTL1} = 0 \ V$ ,  $V_{CTL2} = V_{CTL3} = V_{IN}$ .  $R_{\overline{FAULT}} = R_{\overline{STATUS}} = 10 \ k\Omega$ ,  $R_{ILIM\_HI} = 20 \ k\Omega$ ,  $R_{ILIM\_LO} = 80.6 \ k\Omega$ . Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                      | PARAMETER                                                                 | TEST CONDI                   | MIN                                                                                | TYP  | MAX  | UNIT      |           |

|----------------------|---------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------|------|------|-----------|-----------|

| SHORTED              | MODE (BC1.2 DCP)                                                          |                              |                                                                                    |      |      |           |           |

|                      | DP_IN / DM_IN shorting resistance                                         | VCTL1 = VIN, VCTL2 = VCTL3   |                                                                                    | 125  | 200  | Ω         |           |

| 1.2 V MOD            | E                                                                         |                              |                                                                                    | •    |      |           |           |

|                      | DP_IN /DM_IN output voltage                                               | VCTI4 VIN VCTI2 VCTI2        | 0.1/                                                                               | 1.19 | 1.25 | 1.31      | V         |

|                      | DP_IN /DM_IN output impedance                                             | VCTL1 = VIN, VCTL2 = VCTL3   | 60                                                                                 | 75   | 94   | $k\Omega$ |           |

| DIVIDER1             | MODE                                                                      |                              |                                                                                    |      |      |           |           |

|                      | DP_IN divider1 output voltage                                             |                              |                                                                                    | 1.9  | 2    | 2.1       | V         |

|                      | DM_IN divider1 output voltage                                             | VCTL1 = VIN, VCTL2 = VCTL3 : | 2.57                                                                               | 2.7  | 2.84 | V         |           |

|                      | DP_IN output impedance                                                    | VOILI = VIIN, VOILZ = VOILS  | = U V                                                                              | 8    | 10.5 | 12.5      | $k\Omega$ |

|                      | DM_IN output impedance                                                    |                              |                                                                                    | 8    | 10.5 | 12.5      | $k\Omega$ |

| DIVIDER2             | MODE                                                                      |                              |                                                                                    | •    |      |           |           |

|                      | DP_IN divider2 output voltage                                             |                              |                                                                                    | 2.57 | 2.7  | 2.84      | V         |

|                      | DM_IN divider2 output voltage                                             | IOUT = 1 A                   | 1.9                                                                                | 2    | 2.1  | V         |           |

|                      | DP_IN output impedance                                                    | 1001 = 1 A                   | 8                                                                                  | 10.5 | 12.5 | $k\Omega$ |           |

|                      | DM_IN output impedance                                                    |                              |                                                                                    | 8    | 10.5 | 12.5      | $k\Omega$ |

| CHARGIN              | G DOWNSTREAM PORT                                                         |                              |                                                                                    |      |      |           |           |

| V <sub>DM_SRC</sub>  | DM_IN CDP output voltage                                                  | VCTL1 = VCTL2 = VCTL3 = VIN  | $V_{DP\_IN} = 0.6 \text{ V}, \\ -250  \mu\text{A} < I_{DM\_IN} < 0 \\ \mu\text{A}$ | 0.5  | 0.6  | 0.7       | V         |

| V <sub>DAT_REF</sub> | DP_IN rising lower window threshold for V <sub>DM_SRC</sub> activation    |                              |                                                                                    | 0.25 |      | 0.4       | V         |

|                      | Hysteresis <sup>(1)</sup>                                                 | VCTL1 = VCTL2 = VCTL3 = VIN  | 1                                                                                  |      | 50   |           | mV        |

| V <sub>LGC_SRC</sub> | DP_IN rising upper window threshold for V <sub>DM_SRC</sub> de-activation | VCILI = VCIL2 = VCIL3 = VIN  | ı                                                                                  | 0.8  |      | 1         | V         |

|                      | Hysteresis <sup>(1)</sup>                                                 |                              |                                                                                    |      | 100  |           | mV        |

| I <sub>DP_SINK</sub> | DP_IN sink current                                                        | VCTL1 = VCTL2 = VCTL3 = VIN  | V <sub>DP_IN</sub> = 0.6 V                                                         | 40   | 70   | 100       | μΑ        |

| LOAD DET             | FECT – NON-POWER WAKE                                                     |                              |                                                                                    |      |      |           |           |

| I <sub>LD</sub>      | IOUT rising load detect current threshold                                 |                              |                                                                                    | 635  | 700  | 765       | mA        |

|                      | Hysteresis (1)                                                            | VCTL1 = VCTL2 = VCTL3 = VIN  |                                                                                    | 50   |      | mA        |           |

| t <sub>LD_SET</sub>  | Load detect set time                                                      |                              |                                                                                    | 140  | 200  | 275       | ms        |

|                      | Load detect reset time                                                    |                              |                                                                                    | 1.9  | 3    | 4.2       | S         |

<sup>(1)</sup> These parameters are provided for reference only and do not constitute part of Texas Instrument's published device specifications for purposes of Texas Instrument's product warranty.

# **Electrical Characteristics: Charging Controller (continued)**

Unless otherwise noted:  $-40 \le T_J \le 125^{\circ}\text{C}$ ,  $4.5 \text{ V} \le V_{\text{IN}} \le 5.5 \text{ V}$ ,  $V_{\text{EN}} = V_{\text{IN}}$ ,  $V_{\text{ILIM\_SEL}} = V_{\text{IN}}$ ,  $V_{\text{CTL1}} = 0 \text{ V}$ ,  $V_{\text{CTL2}} = V_{\text{CTL3}} = V_{\text{IN}}$ .  $R_{\overline{\text{FAULT}}} = R_{\overline{\text{STATUS}}} = 10 \text{ k}\Omega$ ,  $R_{\text{ILIM\_HI}} = 20 \text{ k}\Omega$ ,  $R_{\text{ILIM\_LO}} = 80.6 \text{ k}\Omega$ . Positive currents are into pins. Typical values are at 25°C. All voltages are with respect to GND.

|                    | PARAMETER                                                             | TEST CONDITIONS                  | MIN  | TYP | MAX  | UNIT |

|--------------------|-----------------------------------------------------------------------|----------------------------------|------|-----|------|------|

| LOAD DE            | TECT – POWER WAKE                                                     |                                  |      |     |      | •    |

| I <sub>OS_PW</sub> | Power wake short-circuit current limit                                |                                  | 32   | 55  | 78   | mA   |

|                    | I <sub>OUT</sub> falling power wake reset current detection threshold | VCTL1 = VCTL2 = 0 V, VCTL3 = VIN | 23   | 45  | 67   | mA   |

|                    | Reset current hysteresis (1)                                          |                                  |      | 5   |      | mA   |

|                    | Power wake reset time                                                 |                                  | 10.7 | 15  | 20.6 | s    |

Product Folder Links: TPS2546

8

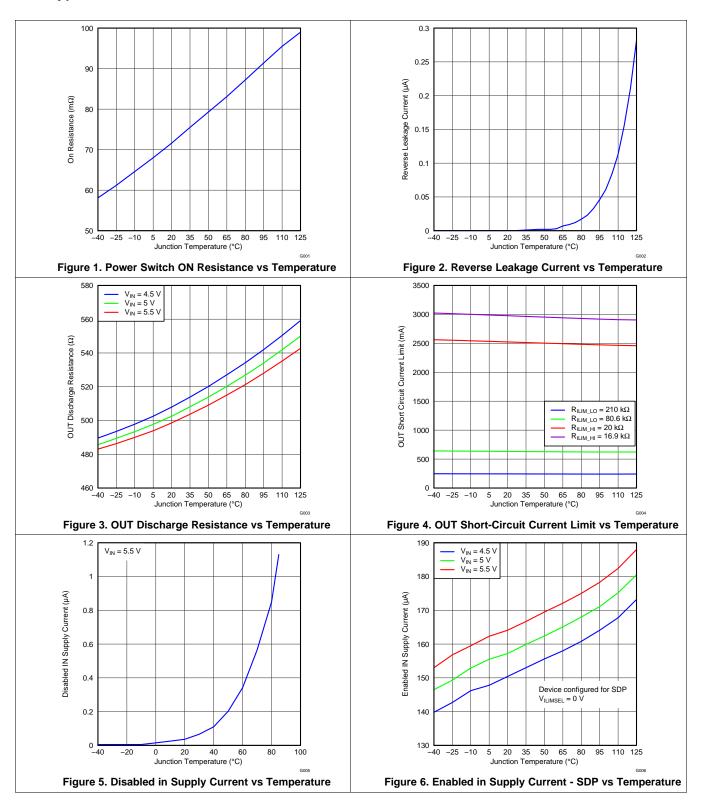

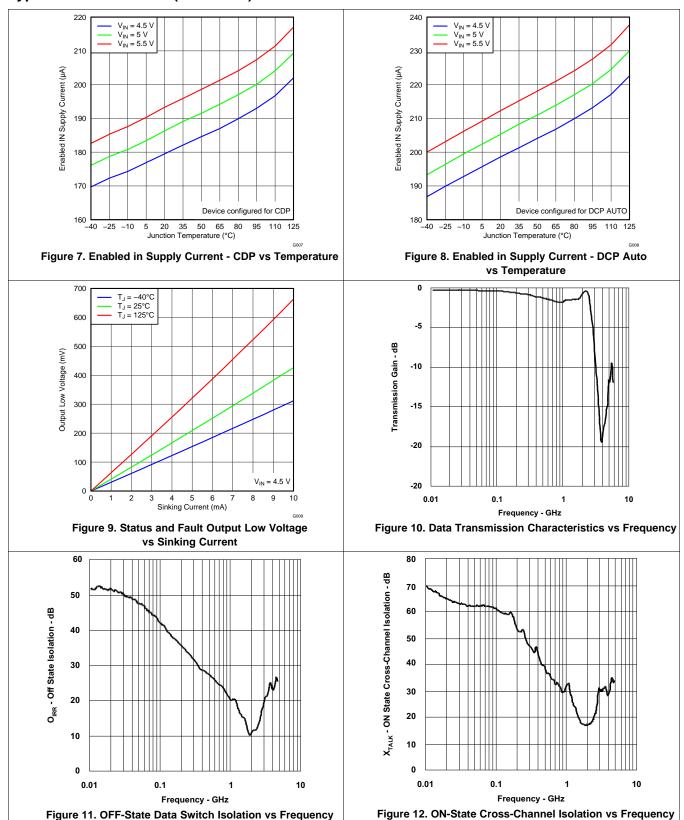

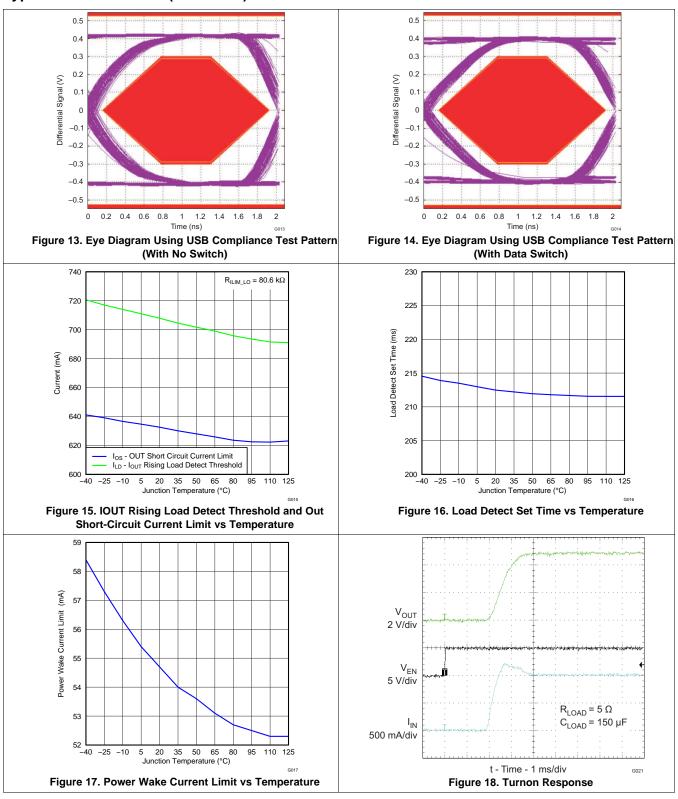

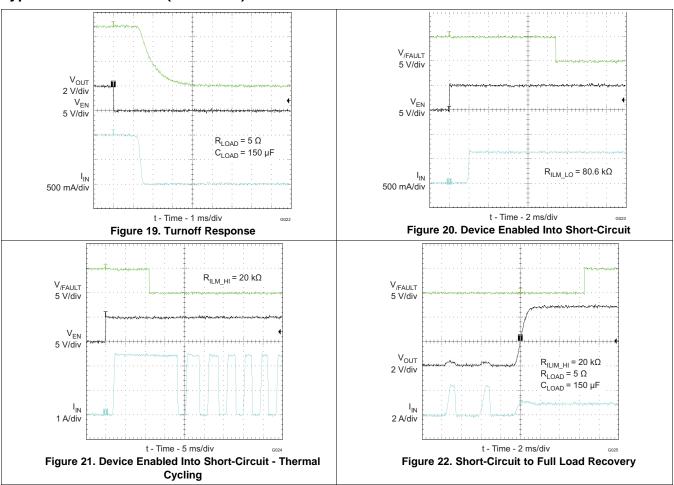

# 6.8 Typical Characteristics

Product Folder Links: TPS2546

Copyright © 2013–2016, Texas Instruments Incorporated

Submit Documentation Feedback

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Downloaded from Arrow.com.

# **Typical Characteristics (continued)**

Product Folder Links: TPS2546

Copyright © 2013–2016, Texas Instruments Incorporated

Submit Documentation Feedback

# **Typical Characteristics (continued)**

# 7 Parameter Measurement Information

Figure 23. Out Rise/Fall Test Load

Figure 24. Power-ON and OFF Timing

Figure 25. Enable Timing, Active High Enable

Figure 26. Out Discharge During Mode Change

Figure 27. Output Short-Circuit Parameters

Product Folder Links: TPS2546

Downloaded from Arrow.com.

# 8 Detailed Description

#### 8.1 Overview

The following overview references various industry standards. TI recommends consulting the most up-to-date standard to ensure the most recent and accurate information. Rechargeable portable equipment requires an external power source to charge its batteries. USB ports are a convenient location for charging, because of an available 5-V power source. Universally accepted standards are required to make sure host and client-side devices operate together in a system to ensure power management requirements are met. Traditionally, host ports following the USB 2.0 specification must provide at least 500 mA to downstream client-side devices. Because multiple USB devices can attach to a single USB port through a bus-powered hub, it is the responsibility of the client-side device to negotiate its power allotment from the host, ensuring the total current draw does not exceed 500 mA. In general, each USB device is granted 100 mA, and may request more current in 100-mA unit steps up to 500 mA. The host may grant or deny based on the available current. A USB 3.0 host port not only provides higher data rate than USB 2.0 port, but also raises the unit load from 100 mA to 150 mA. It is also required to provide a minimum current of 900 mA to downstream client-side devices.

Additionally, the success of USB makes the mini-USB connector a popular choice for wall adapter cables. This allows a portable device to charge from both a wall adapter, and USB port with only one connector. As USB charging has gained popularity, the 500-mA minimum defined by USB 2.0 or 900 mA for USB 3.0 has become insufficient for many handset and personal media players, which need a higher charging rate. Wall adapters can provide much more current than 500 mA/900 mA. Several new standards have been introduced, defining protocol handshaking methods that allow host and client devices to acknowledge and draw additional current beyond the 500 mA/900 mA minimum defined by USB 2.0 and 3.0, while still using a single micro-USB input connector.

The TPS2546 supports four of the most common USB charging schemes found in popular handheld media and cellular devices:

- USB Battery Charging Specification BC1.2

- Chinese Telecommunications Industry Standard YD/T 1591-2009

- Divider Mode

- 1.2-V Mode

YD/T 1591-2009 is a subset of BC1.2 specifications supported by vast majority of devices that implement USB changing. Divider and 1.2-V charging schemes are supported in devices from specific, yet popular device makers.

BC1.2 lists three different port types:

- Standard Downstream Port (SDP)

- Charging Downstream Port (CDP)

- Dedicated Charging Port (DCP)

BC1.2 defines a charging port as a downstream facing USB port that provides power for charging portable equipment. Under this definition, CDP and DCP are defined as charging ports.

Product Folder Links: TPS2546

Copyright © 2013-2016, Texas Instruments Incorporated

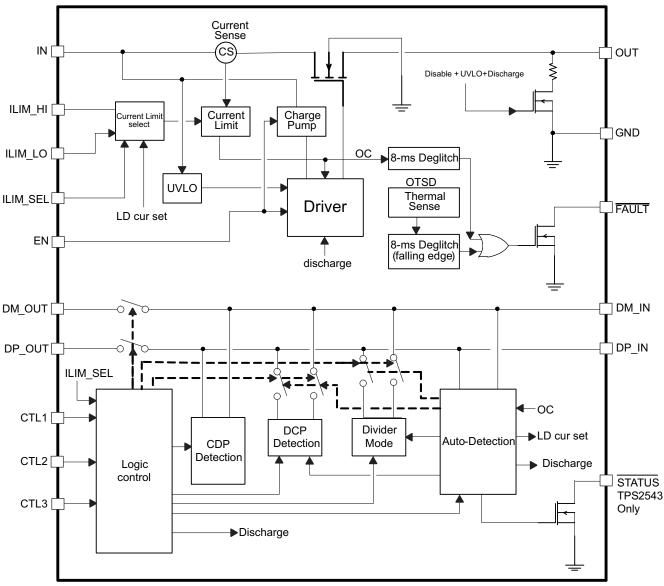

#### 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

# 8.3 Feature Description

#### 8.3.1 Standard Downstream Port (SDP) USB 2.0/USB 3.0

An SDP is a traditional USB port that follows USB 2.0 and 3.0 protocol, and supplies a minimum of 500 mA for USB 2.0 and 900 mA for USB 3.0 per port. USB 2.0 and 3.0 communications is supported, and the host controller must be active to allow charging. TPS2546 supports SDP mode in system power state S0, when system is completely powered ON, and fully operational. For more details on control pin (CTL1-CTL3) settings to program this state, see Table 3.

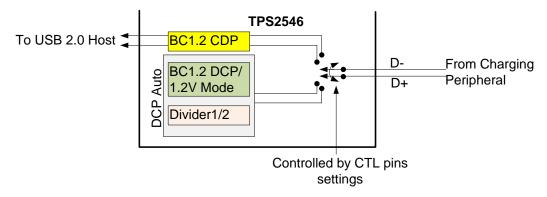

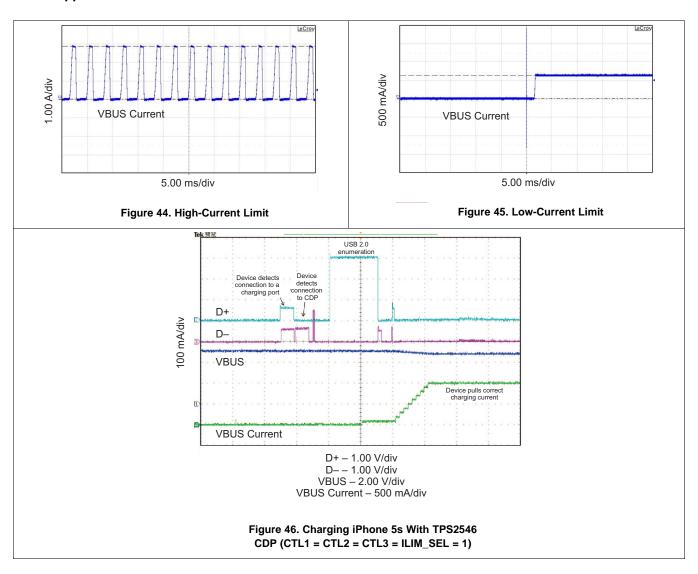

#### 8.3.2 Charging Downstream Port (CDP)

A CDP is a USB port that follows USB BC1.2 and supplies a minimum of 1.5 A per port. It provides power and meets USB 2.0 requirements for device enumeration. USB 2.0 communications is supported, and the host controller must be active to allow charging. What separates a CDP from an SDP is the host-charge handshaking logic that identifies this port as a CDP. A CDP is identifiable by a compliant BC1.2 client device, and allows for additional current draw by the client device.

The CDP process is done in two steps. During step one, the portable equipment outputs a nominal 0.6-V output on the D+ line, and reads the voltage input on the D- line. The portable device detects it is connected to an SDP if the voltage is less than the nominal data detect voltage of 0.3 V. The portable device detects that it is connected to a Charging Port if the D- voltage is greater than the nominal data detect voltage of 0.3 V, and optionally less than 0.8 V.

The second step is necessary for portable equipment to determine if it is connected to CDP or DCP. The portable device outputs a nominal 0.6 V output on its D– line, and reads the voltage input on its D+ line. The portable device detects it is connected to a CDP if the data line being read remains less than the nominal data detect voltage of 0.3 V. The portable device detects it is connected to a DCP if the data line being read is greater than the nominal data detect voltage of 0.3 V.

TPS2546 supports CDP mode in system power state S0 when system is completely powered ON, and fully operational. For more details on control pin (CTL1-CTL3) settings to program this state, see Table 3.

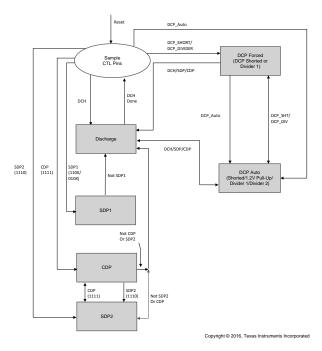

#### 8.3.3 Dedicated Charging Port (DCP)

A DCP only provides power but does not support data connection to an upstream port. As shown in following sections, a DCP is identified by the electrical characteristics of the data lines. The TPS2546 emulates DCP in two charging states, namely DCP Forced and DCP Auto as shown in Figure 37. In DCP Forced state the device supports one of the two DCP charging schemes, namely Divider1 or Shorted. In the DCP Auto state, the device charge detection state machine is activated to selectively implement charging schemes involved with the Shorted, Divider1, Divider2, and 1.2-V modes. Shorted DCP mode complies with BC1.2 and Chinese Telecommunications Industry Standard YD/T 1591-2009, while the Divider and 1.2-V modes are employed to charge devices that do not comply with BC1.2 DCP standard.

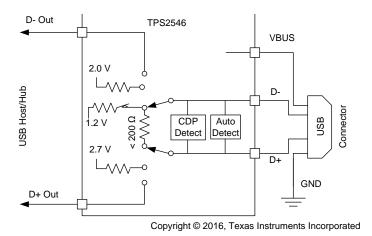

#### 8.3.3.1 DCP BC1.2 and YD/T 1591-2009

Both standards define that the D+ and D- data lines must be shorted together with a maximum series impedance of 200  $\Omega$ . This is shown in Figure 28.

Figure 28. DCP Supporting BC1.2/YD/T 1591-2009

Submit Documentation Feedback Copyright © 2013–2016

Product Folder Links: TPS2546

16

# 8.3.3.2 DCP Divider Charging Scheme

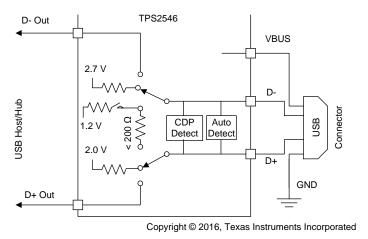

There are two Divider charging scheme supported by the device, Divider1 and Divider2 as shown in Figure 29 and Figure 30. In Divider1 charging scheme the device applies 2 V and 2.7 V to D+ and D- data line respectively. This is reversed in Divider2 mode.

Figure 29. DCP Divider1 Charging Scheme

Figure 30. Divider2 Charging Scheme

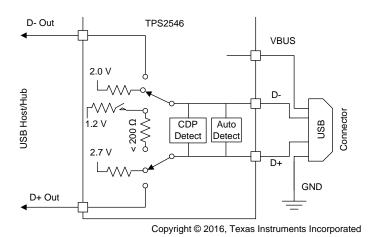

#### 8.3.3.3 DCP 1.2-V Charging Scheme

1.2-V charging scheme is used by some handheld devices to enable fast charging at 2 A. TPS2546 supports this scheme in the DCP-Auto mode before the device enters BC1.2 shorted mode. To simulate this charging scheme D+/D- lines are shorted and pulled-up to 1.2 V for fixed duration then device moves to DCP shorted mode as defined in BC1.2 specification. This is shown in Figure 31

Figure 31. DCP 1.2-V Charging Scheme

#### 8.3.4 Wake on USB Feature (Mouse/Keyboard Wake Feature)

#### 8.3.4.1 USB 2.0 Background Information

The TPS2546 data lines interface with USB 2.0 devices. USB 2.0 defines three types of devices according to data rate. These devices and their characteristics relevant to TPS2546 Wake on USB operation are shown below.

#### Low-speed USB devices:

- 1.5 Mbps

- Wired mice and keyboards are examples

- · No devices that need battery charging

- All signaling performed at 2 V and 0.8 V hi/lo logic levels

- D- high to signal connect and when placed into suspend

- D– high when not transmitting data packets

#### Full-speed USB devices:

- 12 Mbps

- Wireless mice and keyboards are examples

- Legacy phones and music players are examples

- Some legacy devices that need battery charging

- All signaling performed at 2 V and 0.8 V hi/lo logic levels

- D+ high to signal connect and when placed into suspend

- D+ high when not transmitting data packets

#### High-speed USB devices:

- 480 Mbps

- · Tablets, phones and music players are examples

- Many devices that need battery charging

- Connect and suspend signaling performed at 2 V and 0.8 V hi/lo logic levels

- Data packet signaling performed a logic levels below 0.8 V

- D+ high to signal connect and when placed into suspend (same as a full-speed device)

- D+ and D- low when not transmitting data packets

#### 8.3.4.2 Wake On USB

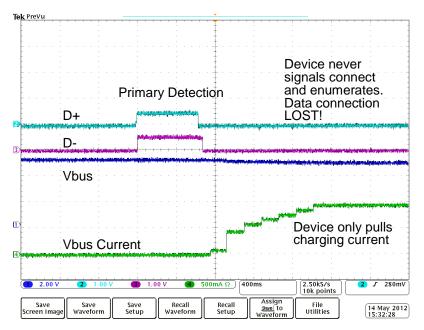

Wake on USB is the ability of a wake configured USB device to wake a computer system from its S3 sleep state back to its S0 working state. Wake on USB requires the data lines to be connected to the system USB host before the system is placed into its S3 sleep state, and remain continuously connected until they are used to wake the system.

The TPS2546 supports low-speed and high-speed HID (human interface device like mouse/key board) wake function. There are two scenarios under which wake on mouse are supported by the TPS2546. The specific CTL pin changes that the TPS2546 overrides are shown below. The information is presented as CTL1, CTL2, CTL3. The ILIM SEL pin plays no role

- 1. 111 (CDP/SDP2) to 011 (DCP-Auto)

- 2. 010 (SDP1) to 011 (DCP-Auto)

#### NOTE

The 110 (SDP1) to 011 (DCP-Auto) transition is not supported. This is done for practical reasons, because the transition involves changes to two CTL pins. Depending on which CTL pin changes first, the device sees either a temporary 111 or 010 command. The 010 command is safe but the 111 command causes an OUT discharge as the TPS2546 instead proceeds to the 111 state.

#### 8.3.4.3 USB Slow-Speed and Full-Speed Device Recognition

TPS2546 is capable of detecting LS or FS device attachment when TPS2546 is in SDP or CDP mode. Per USB specification, when no device is attached, the D+ and D- lines are near ground level. When a low-speed compliant device is attached to the TPS2546 charging port, D- line is pulled high in its idle state (mouse/keyboard not activated). However, when a FS device is attached then the opposite is true in its idle state, that is, D+ is pulled high and D- remains at ground level.

TPS2546 monitors both D+ and D- lines while CTL pin settings are in CDP or SDP mode to detect LS or FS HID device attachment. To support HID sleep wake, TPS2546 must first determine that it is attached to a LS or FS device when system is in S0 power state. TPS2546 does this as described above. While supporting a LS HID wake is straight forward, supporting FS HID requires making a distinction between a FS and a HS device. This is because a high-speed device always presents itself initially as a full speed device (by a 1.5-K pullup resistor on D+). The negotiation for high speed then makes the distinction whereby the 1.5-K pullup resistor gets removed.

TPS2546 handles the distinction between a FS and HS device at connect by memorizing if the D+ line goes low after connect. A HS device after connect always undergoes negotiation for HS, which requires the 1.5-k $\Omega$  resistor pullup on D+ to be removed. To memorize a FS device, TPS2546 requires the device to remain connected for at least 60 seconds while the system is in S0 mode, before placing it in sleep or S3 mode.

#### NOTE

If system is placed in sleep mode earlier than the 60 second window, a FS device may not get recognized and hence could fail to wake system from S3. This requirement does not apply for LS device.

### 8.3.4.3.1 No CTL Pin Timing Requirement After Wake Event and Transition from S3 to S0

Unlike the TPS2543, there is no CTL pin timing requirement for the TPS2546 when the wake configured USB device wakes the system from S3 back to S0. The TPS2543 requires the CTL pins to transition from the DCP-Auto setting back to the SDP/CDP setting within 64 ms of the attached USB device signaling a wake event (for example, mouse clicked or keyboard key pressed). No such timing condition exists for the TPS2546.

#### 8.3.5 Load Detect

TPS2546 offers system designers unique power management strategy not available in the industry from similar devices. There are two power management schemes supported by the TPS2546 through the STATUS pin, they are:

- Power Wake (PW)

- Port Power Management (PPM)

Either feature may be implemented in a system depending on power savings goals for the system. In general, Power Wake feature is used mainly in mobile systems, like a notebook, where it is imperative to save battery power when system is in deep sleep (S4/S5) state. Oppositely, Port Power Management feature would be implemented where multiple charging ports are supported in the same system, and system power rating is not capable of supporting high-current charging on multiple ports simultaneously.

#### 8.3.6 Power Wake

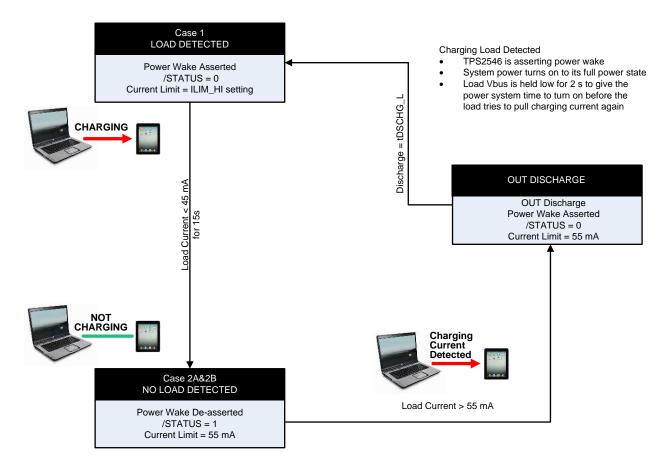

The goal of the power wake feature is to save system power when the system is in S4/S5 state. In the S4/S5 state, the system is in deep sleep and typically running off the battery; so every mW in system power savings translates to extending battery life. In this state, the TPS2546 monitors charging current at the OUT pin and provide a mechanism through the STATUS pin to switch out the high-power DC-DC controller and switch in a low power LDO when charging current requirement is < 45 mA (typical). This would be the case when no peripheral device is connected at the charging port or if a device has attained its full battery charge and draws <45 mA. A power wake flow chart and description is shown in Figure 32.

#### Load being Charged

- TPS2546 is asserting power wake

- System power is at its full capability

- Load can charge at high current

- TPS2546 monitors port to detect when charging load is done charging or removed

#### Charging Load Not Detected.

- TPS2546 is not asserting power wake. System power is in a low power state to save energy.

- TPS2546 monitors port to detect when charging load is attached and tries to charge

Copyright © 2016, Texas Instruments Incorporated

Figure 32. Power Wake Flow Chart

#### 8.3.6.1 Implementing Power Wake in Notebook System

An implementation of power wake in notebook platforms with the TPS2546 is shown in Figure 33 to Figure 35. Power wake function is used to select between a high-power DC-DC converter, and low-power LDO (100 mA) based on charging requirements. System power saving is achieved when under no charging conditions (the connected device is fully charged or no device is connected) the DC-DC converter is turned off (to save power because it is less efficient in low-power operating region) and the low-power LDO supplies standby power to the charging port.

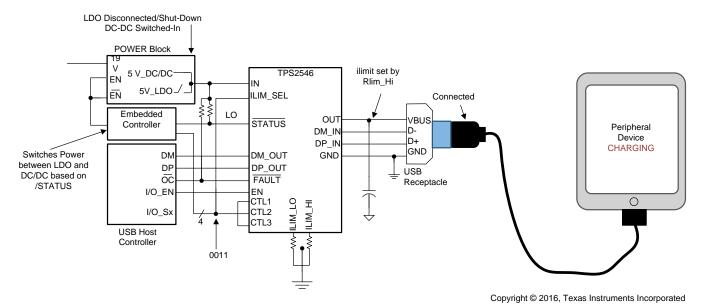

Power wake is activated in S4/S5 mode (0011 setting, see Table 3), TPS2546 is charging connected device as shown in Figure 33, STATUS is pulled LO (Case 1) which switches-out the LDO and switches-in the DC-DC converter to handle high-current charging.

Figure 33. Case 1: System in S4/S5, Device Charging

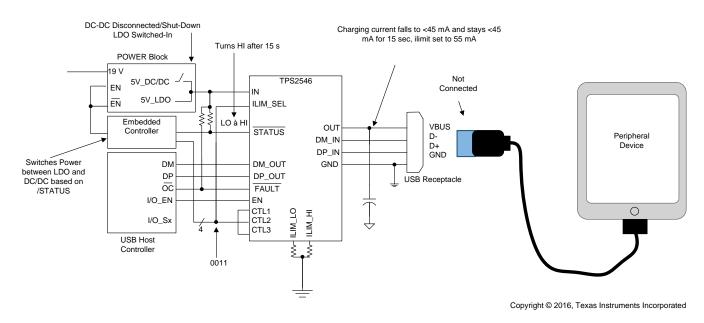

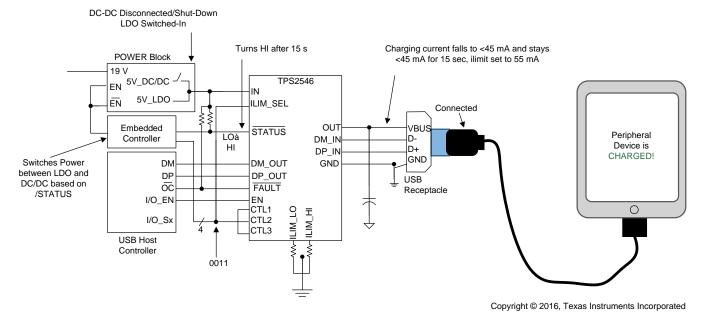

As shown in Figure 34 and Figure 35, when connected device is fully charged or gets disconnected from the charging port, the charging current falls. If charging current falls to < 45 mA and stays below this threshold for over 15 s, TPS2546 automatically sets a 55-mA internal current limit and STATUS is de-asserted (pulled HI). As shown in Figure 34 and Figure 35. This results in DC-DC converter turning off, and the LDO turning on. Current limit of 55 mA is set to prevent the low-power LDO output voltage from collapsing in case there is a spike in current draw due to device attachment or other activity such as display panel LED turning ON in connected device.

Following Power Wake flow chart (Figure 32) when a device is attached and draws > 55 mA of charging current the TPS2546 hits its internal current limit. This triggers the device to assert STATUS (LO), and turn on the DC-DC converter and turn off the LDO. TPS2546 discharges OUT for > 2 s (typical), allowing the main power supply to turn on. After the discharge, the device turns back on with current limit set by ILIM\_HI (Case 1)

Figure 34. Case 2A: System in S4/S5, No Device Attached

Figure 35. Case 2B: System in S4/S5, Attached Device Fully Charged

#### 8.3.7 Port Power Management (PPM)

PPM is the intelligent and dynamic allocation of power for systems that have multiple charging ports but cannot power them all simultaneously. The goals of this feature are:

- Enhance user experience because user does not have to search for charging port

- Ensure the power supply only has to be designed for a reasonable charging load

Initially all ports are allowed to <u>broadcast</u> high-current charging, charging current limit is based on ILIM\_HI resistor setting. System monitors STATUS to see when high-current loads are present. Once allowed number of ports assert STATUS, remaining ports are toggled to a non-charging port. Non-charging ports are SDP ports with current limit based on ILIM\_LO. TPS2546 allows for a system to toggle between charging and non-charging ports either with an OUT discharge or without an OUT discharge.

#### 8.3.7.1 Benefits of PPM

- Delivers better user experience

- · Prevents overloading of system's power supply

- · Allows for dynamic power limits based on system state

- · Allows every port to potentially be a high-power charging port

- · Allows for smaller power supply capacity because the loading is controlled

#### 8.3.7.2 PPM Details

All ports are allowed to broadcast high-current charging – CDP or DCP. Current limit is based on ILIM\_HI and <a href="mailto:system\_monitors">system\_monitors</a> STATUS pin to see when high-current loads are present. Once allowed number of ports assert STATUS, remaining ports are toggled to a SDP non-charging port. SDP current limit is based on ILIM\_LO <a href="mailto:setting.">setting.</a> SDP ports are automatically toggled back to CDP or DCP mode when a charging port de-asserts STATUS.

Based on CTL settings there is a provision for a port to toggle between charging and non-charging ports either with a Vbus discharge or without a Vbus discharge. For example when a port is in SDP2 mode (1110) and its ILIM\_SEL pin is toggled to 1 due to another port releasing its high-current requirements. The SDP2 port automatically reverts to CDP mode (1111) without a discharge event. This is desirable if this port was connected to a media device where it was syncing data from the SDP2 port; a discharge event would disrupt the syncing activity on the port and cause user confusion.

STATUS trip point is based on the programmable ILIM\_LO current limit set point. This does not mean STATUS is a current limit – the port itself is using the ILIM\_HI current limit. Since ILIM\_LO defines the current limit for a SDP port, it works well to use the ILIM\_LO value to define a high-current load. STATUS asserts in CDP and DCP when load current is above ILIM\_LO+60 mA for 200 ms. STATUS also asserts in CDP when an attached device does a BC1.2 primary detection. STATUS de-asserts in CDP and DCP when the load current is below ILIM\_LO+10 mA for 3 s.

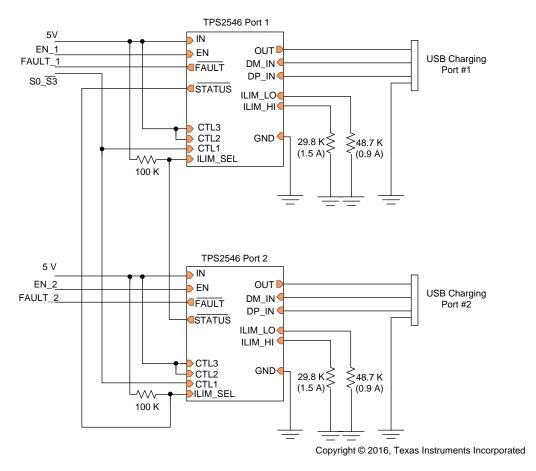

#### 8.3.7.3 Implementing PPM in a System with Two Charging Ports

Figure 36 shows implementation of two charging ports, each with its own TPS2546. In this example 5-V power supply for the two charging ports is rated at < 3 A or < 15 W maximum. Both devices have  $R_{LIM}$  chosen to correspond to the low (0.9 A) and high (1.5 A) current limit setting for the port. In this implementation the system can support only one of the two ports at 1.5-A charging current while the other port is set to SDP mode and  $I_{LIMIT}$  corresponding to 0.9 A.

Figure 36. Implementing Port Power Management in a System Supporting Two Charging Ports

#### 8.3.8 Overcurrent Protection

When an overcurrent condition is detected, the device maintains a constant output current and reduces the output voltage accordingly. Two possible overload conditions can occur. In the first condition, the output has been shorted before the device is enabled or before VIN has been applied. The TPS2546 senses the short and immediately switches into a constant-current output. In the second condition, a short or an overload occurs while the device is enabled. At the instant the overload occurs, high currents may flow for nominally one to two microseconds before the current-limit circuit can react. The device operates in constant-current mode after the current-limit circuit has responded. Complete shutdown occurs only if the fault is present long enough to activate thermal limiting. The device remains off until the junction temperature cools approximately 20°C and then restarts. The device continues to cycle on/off until the overcurrent condition is removed.

#### 8.3.9 FAULT Response

The FAULT open-drain output is asserted (active low) during an overtemperature or current limit condition. The output remains asserted until the fault condition is removed. The TPS2546 is designed to eliminate false FAULT reporting by using an internal de-glitch circuit for current limit conditions without the need for external circuitry. This ensures that FAULT is not accidentally asserted due to normal operation such as starting into a heavy capacitive load. overtemperature conditions are not de-glitched and assert the FAULT signal immediately.

#### 8.3.10 Undervoltage Lockout (UVLO)

The undervoltage lockout (UVLO) circuit disables the power switch until the input voltage reaches the UVLO turnon threshold. Built-in hysteresis prevents unwanted oscillations on the output due to input voltage drop from large current surges.

#### 8.3.11 Thermal Sense

The TPS2546 protects itself with two independent thermal sensing circuits that monitor the operating temperature of the power distribution switch and disables operation if the temperature exceeds recommended operating conditions. The device operates in constant-current mode during an overcurrent condition, which increases the voltage drop across power switch. The power dissipation in the package is proportional to the voltage drop across the power switch, so the junction temperature rises during an overcurrent condition. The first thermal sensor turns off the power switch when the die temperature exceeds 135°C and the part is in current limit. The second thermal sensor turns off the power switch when the die temperature exceeds 155°C regardless of whether the power switch is in current limit. Hysteresis is built into both thermal sensors, and the switch turns on after the device has cooled by approximately 20°C. The switch continues to cycle off and on until the fault is removed. The open-drain false reporting output FAULT is asserted (active low) during an overtemperature shutdown condition.

#### 8.4 Device Functional Modes

Table 1 shows the differences between these ports.

SUPPORT USB **MAXIMUM ALLOWABLE CURRENT PORT TYPE** 2.0 COMMUNICATION DRAW BY PORTABLE DEVICE (A) **SDP (USB 2.0)** Yes 0.5 SDP (USB 3.0) 0.9 Yes CDP Yes 1.5 DCP No 1.5

**Table 1. Operating Modes**

#### 8.4.1 DCP Auto Mode

As mentioned above the TPS2546 integrates an auto-detect state machine that supports all the above DCP charging schemes. It starts in Divider1 scheme, however if a BC1.2 or YD/T 1591-2009 compliant device is attached, the TPS2546 responds by discharging OUT, turning back on the power switch and operating in 1.2 V mode briefly and then moving to BC1.2 DCP mode. It then stays in that mode until the device releases the data line, in which case it goes back to Divider1 scheme. When a Divider1 compliant device is attached the TPS2546 stays in Divider1 state.

Also, the TPS2546 automatically switches between the Divider1 and Divider2 schemes based on charging current drawn by the connected device. Initially the device sets the data lines to Divider1 scheme. If charging current of > 750 mA is measured by the TPS2546 it switches to Divider2 scheme and test to see if the peripheral device still charges at a high current. If it does then it stays in Divider2 scheme otherwise it reverts to Divider1 scheme.

Figure 37. DCP Auto Mode

#### 8.4.2 DCP Forced Shorted / DCP Forced Divider1

In this mode the device is permanently set to one of the DCP schemes (BC1.2/ YD/T 1591-2009 or Divider1) as commanded by its control pin setting per Table 3.

# 8.4.3 High-Bandwidth Data Line Switch

The TPS2546 passes the D+ and D- data lines through the device to enable monitoring and handshaking while supporting charging operation. A wide bandwidth signal switch is used, allowing data to pass through the device without corrupting signal integrity. The data line switches are turned on in any of CDP or SDP operating modes. The EN input also needs to be at logic High for the data line switches to be enabled.

#### NOTE

- While in CDP mode, the data switches are ON even while CDP handshaking is occurring

- The data line switches are OFF if EN or all CTL pins are held low, or if in DCP mode. They are not automatically turned off if the power switch (IN to OUT) is in current limit

- The data switches are for USB 2.0 differential pair only. In the case of a USB 3.0 host, the super speed differential pairs must be routed directly to the USB connector without passing through the TPS2546

- Data switches are OFF during OUT (VBUS) discharge

Table 2 can be used as an aid to program the TPS2546 per system states however not restricted to below settings only.

Table 2. Control Pin Settings Matched to System Power States

| SYSTEM<br>GLOBAL<br>POWER<br>STATE | TPS2546 CHARGING MODE                                                                      | CTL1 | CTL2 | CTL3 | ILIM_SEL | CURRENT LIMIT<br>SETTING |

|------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|----------|--------------------------|

| S0                                 | SDP1                                                                                       | 1    | 1    | 0    | 1 or 0   | ILIM_HI / ILIM_LO        |

| S0                                 | SDP2, no discharge to / from CDP                                                           | 1    | 1    | 1    | 0        | ILIM_LO                  |

| S0                                 | CDP, load detection with ILIM_LO + 60-mA thresholds or if a BC1.2 primary detection occurs | 1    | 1    | 1    | 1        | ILIM_HI                  |

| S4/S5                              | Auto mode, load detection with power wake thresholds                                       | 0    | 0    | 1    | 1        | ILIM_HI                  |

| S3/S4/S5                           | Auto mode, no load detection                                                               | 0    | 0    | 1    | 0        | ILIM_HI                  |

| \$3                                | Auto mode, keyboard/mouse wake up, load detection with ILIM_LO + 60 mA thresholds          | 0    | 1    | 1    | 1        | ILIM_HI                  |

| S3                                 | Auto mode, keyboard/mouse wake-up, no load detection                                       | 0    | 1    | 1    | 0        | ILIM_HI                  |

| <b>S</b> 3                         | SDP1, keyboard/mouse wake-up                                                               | 0    | 1    | 0    | 1 or 0   | ILIM_HI / ILIM_LO        |

#### 8.4.4 Device Truth Table (TT)

Device TT lists all valid bias combinations for the three control pins CTL1-3 and ILIM\_SEL pin and their corresponding charging mode. It is important to note that the TT purposely omits matching charging modes of the TPS2546 with global power states (S0-S5) as device is agnostic to system power states. The TPS2546 monitors CTL inputs and transitions to the charging state it is commanded to go to (except when LS/FS HID device is detected). For example, if sleep charging is desired when system is in standby or hibernate state then the user must set TPS2546 CTL pins to correspond to DCP\_Auto charging mode as shown in the below table. When the system resumes operation mode set the control pins to correspond to SDP or CDP mode, as seen in Table 3.

**Table 3. Truth Table**

| CTL1 | CTL2 | CTL3 | ILIM_SEL | MODE                | CURRENT<br>LIMIT<br>SETTING                 | STATUS OUTPUT<br>(ACTIVE LOW)   | COMMENT                                                  |

|------|------|------|----------|---------------------|---------------------------------------------|---------------------------------|----------------------------------------------------------|

| 0    | 0    | 0    | 0        | Discharge           | NA                                          | OFF                             | OUT held low.                                            |

| 0    | 0    | 0    | 1        | Discharge           | NA                                          | OFF                             | OOT field low.                                           |