### **AGB2NOCS-GEVK**

## AGB2N0CS-GEVK Evaluation Board User's Manual

#### **Adapter Board Overview**

The AGB2N0CS Adapter Board helps connect Demo 2× headboards to the Demo 3 Baseboard, the AGB1N0CS-GEVK. The Demo 3 uses a high-bandwidth USB 3.0 interface and HDM1® connector to send sensor image data to the host computer. It supports single/double/quad MIPI interface, dual/quad lanes of HiSPi interface, CCP, and parallel interface. Since the Demo 2× Headboards do not use the same connector as the Demo 3, the AGB2N0CS provides communication between the headboard parallel and serial connectors to communicate with the Demo 3 Baseboard interface connection.

#### **Features**

- Demo 2× Headboard Connectors

- Parallel Data Buffer Option

- MIPI/HiSPi Connectors

- Demo 3 Baseboard Connector

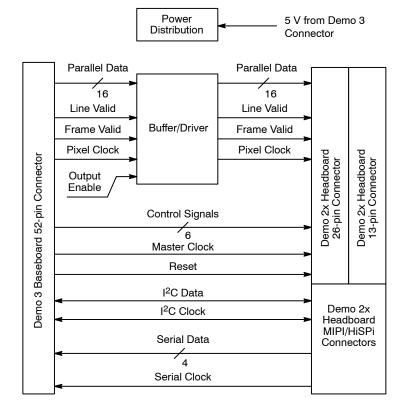

#### **Block Diagram**

Figure 2. Block Diagram of AGB2N0CS-GEVK

ON Semiconductor®

www.onsemi.com

#### **EVAL BOARD USER'S MANUAL**

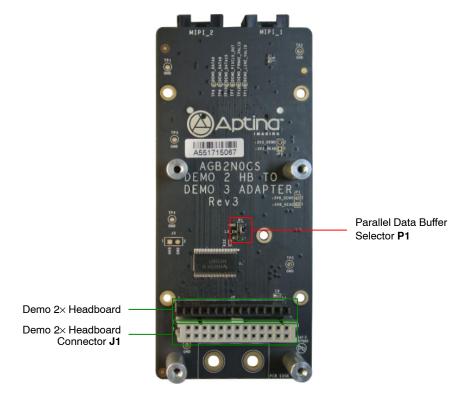

Top View

**Bottom View**

Figure 1. AGB2N0CS Evaluation Board

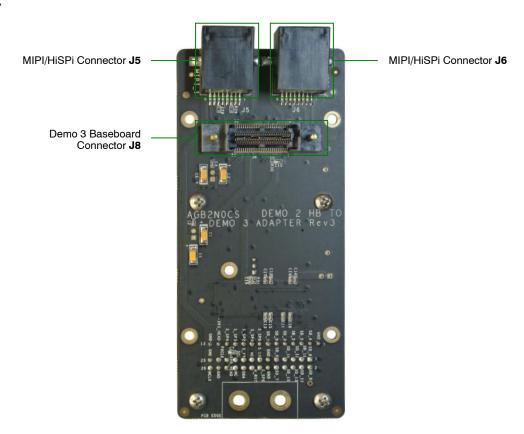

Top View

Figure 3. Top View of Adapter Board with Default Jumpers, Test Pins and Connectors

**Bottom View**

Figure 4. Bottom View of Adapter Board with Connectors

#### AGB2N0CS-GEVK

#### Jumper Pin Location

The jumpers on headboards start with Pin 1 on the leftmost side of the pin. Grouped jumpers increase in pin size with each jumper added.

Figure 5. Pin Locations for a Single Jumper. Pin 1 is Located at the Leftmost Side

#### Jumper/Header Functions & Default Positions

The P1 jumper/header configuration allows configuration of parallel data. Its default position shorts pins 2–3, which enables the parallel data buffer to pass parallel data signals. When pins 1–2 are shorted, the parallel data buffer is disabled.

#### AGB2N0CS-GEVK Connectors

The evaluation board supports has various different connectors on-board, including a Demo 3 connector, two MIPI/HiSPi connectors for the Demo 2× headboard, the 14-pin Demo 2× headboard connector, and 26-pin Demo 2× headboard connector.

#### Headboard Connectors

The Demo 2× headboard connectors are described in the pinouts in Tables 1 and 2. The headboard connector has a 14-pin and 26-pin connector, as well as two MIPI/HiSPi connectors.

#### **Baseboard Connector**

The Demo 3 Baseboard connector is shown in the pinout in Table 3. The Demo 3 connector has a serial sensor data input, I<sup>2</sup>C control interface, headboard power, and parallel image data interface.

Table 1. 26-PIN DEMO 2X HEADBOARD CONNECTOR FUNCTION DESCRIPTION (J1)

| Pin | Name          | Description                      | DIR | Comment                       |

|-----|---------------|----------------------------------|-----|-------------------------------|

| 1   | S_DATA8       | Parallel Data8                   | I/O | Parallel Data Bit             |

| 2   | S_DATA9       | Parallel Data9                   | I/O | Parallel Data Bit             |

| 3   | S_DATA10      | Parallel Data10                  | I/O | Parallel Data Bit             |

| 4   | S_DATA11      | Parallel Data11                  | I/O | Parallel Data Bit             |

| 5   | S_DATA12      | Parallel Data12                  | I/O | Parallel Data Bit             |

| 6   | S_DATA13      | Parallel Data13                  | I/O | Parallel Data Bit             |

| 7   | S_DATA14      | Parallel Data14                  | I/O | Parallel Data Bit             |

| 8   | S_DATA15      | Parallel Data15                  | I/O | Parallel Data Bit             |

| 9   | S_DATA6       | Parallel Data6                   | I/O | Parallel Data Bit             |

| 10  | S_DATA7       | Parallel Data7                   | I/O | Parallel Data Bit             |

| 11  | GND           | Ground                           | PWR |                               |

| 12  | GND           | Ground                           | PWR |                               |

| 13  | S_LINE_VALID  | Parallel Line Valid              | Out | Check Line Valid Signal       |

| 14  | S_SP5         | General Control Signal 5         | Out | Signal @ +3.3 V Level         |

| 15  | NOT USED      | Not Used                         | NA  |                               |

| 16  | HEAD_RESET_L  | Reset Signal to Sensor           | In  | Reset to Headboard Sensor     |

| 17  | S_FRAME_VALID | Parallel Frame Valid             | Out | Check Frame Valid Signal      |

| 18  | HEAD_SDA      | I <sup>2</sup> C Data to Sensor  | I/O | Signal @ +3.3 V Level         |

| 19  | HEAD_SCL      | I <sup>2</sup> C Clock to Sensor | I/O | Signal @ +3.3 V Level         |

| 20  | NOT USED      | Not Used                         | NA  |                               |

| 21  | +5V0_HEAD     | +5V0 Power Input                 | PWR | For Powering Up the Headboard |

| 22  | +5V0_HEAD     | +5V0 Power Input                 | PWR | For Powering Up the Headboard |

| 23  | S_PIXCLK      | Parallel Pixel Clock             | In  | Parallel Data Pixel Clock     |

| 24  | GND           | Ground                           | PWR |                               |

#### AGB2N0CS-GEVK

Table 1. 26-PIN DEMO 2X HEADBOARD CONNECTOR FUNCTION DESCRIPTION (J1) (continued)

| Pin | Name | Description  | DIR | Comment                        |

|-----|------|--------------|-----|--------------------------------|

| 25  | GND  | Ground       | PWR |                                |

| 26  | MCLK | Master Clock | In  | Master Clock from Demo 3 Board |

Table 2. 14-PIN DEMO 2X HEADBOARD CONNECTOR FUNCTION DESCRIPTION (J2)

| Pin | Name      | Description              | DIR | Comment                       |

|-----|-----------|--------------------------|-----|-------------------------------|

| 1   | GND       | Ground                   | PWR |                               |

| 2   | S_DATA4   | Parallel Data4           | I/O | Parallel Data Bit             |

| 3   | S_DATA5   | Parallel Data5           | I/O | Parallel Data Bit             |

| 4   | S_DATA2   | Parallel Data2           | I/O | Parallel Data Bit             |

| 5   | S_DATA3   | Parallel Data3           | I/O | Parallel Data Bit             |

| 6   | S_DATA0   | Parallel Data0           | I/O | Parallel Data Bit             |

| 7   | S_DATA1   | Parallel Data1           | I/O | Parallel Data Bit             |

| 8   | S_SP0     | General Control Signal 0 | Out | Signal @ +3.3 V Level         |

| 9   | S_SP1     | General Control Signal 1 | Out | Signal @ +3.3 V Level         |

| 10  | S_SP2     | General Control Signal 2 | Out | Signal @ +3.3 V Level         |

| 11  | S_SP3     | General Control Signal 3 | Out | Signal @ +3.3 V Level         |

| 12  | S_SP4     | General Control Signal 4 | Out | Signal @ +3.3 V Level         |

| 13  | +3V3_HEAD | +3.3 V to Headboard      | PWR | For Powering Up the Headboard |

| 14  | GND       | Ground                   | PWR |                               |

#### Shorted Jumper for Power Measurement

Different supplies to the headboard are provided by trace shorted jumper, for any voltage and power measurements. To conduct current for current measurement on a given power rail, cut the trace between the two pins of their respective JP, and insert an ammeter prior to powering up the system. The figure below shows where the trace to cut is located.

# Table 3. SHORTED JUMPERS FOR POWER MEASUREMENT

| Jumper          | Voltage (V) |  |  |

|-----------------|-------------|--|--|

| JP1 (+5V0 HEAD) | 5.0         |  |  |

| JP2 (+3V3 HEAD) | 3.3         |  |  |

Figure 6. Top and Bottom View of Shorted Jumper. The Bottom View Shows the Trace Location to Cut for Current Measurement

HDMI is a registered trademark of HDMI Licensing, LLC.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

The evaluation board/kit (research and development board/kit) (hereinafter the "board") is not a finished product and is not available for sale to consumers. The board is only intended for research, development, demonstration and evaluation purposes and will only be used in laboratory/development areas by persons with an engineering/technical training and familiar with the risks associated with handling electrical/mechanical components, systems and subsystems. This person assumes full responsibility/liability for proper and safe handling. Any other use, resale or redistribution for any other purpose is strictly prohibited.

THE BOARD IS PROVIDED BY ONSEMI TO YOU "AS IS" AND WITHOUT ANY REPRESENTATIONS OR WARRANTIES WHATSOEVER. WITHOUT LIMITING THE FOREGOING, ONSEMI (AND ITS LICENSORS/SUPPLIERS) HEREBY DISCLAIMS ANY AND ALL REPRESENTATIONS AND WARRANTIES IN RELATION TO THE BOARD, ANY MODIFICATIONS, OR THIS AGREEMENT, WHETHER EXPRESS, IMPLIED, STATUTORY OR OTHERWISE, INCLUDING WITHOUT LIMITATION ANY AND ALL REPRESENTATIONS AND WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, NON-INFRINGEMENT, AND THOSE ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE CUSTOM OR TRADE PRACTICE.

onsemi reserves the right to make changes without further notice to any board.

You are responsible for determining whether the board will be suitable for your intended use or application or will achieve your intended results. Prior to using or distributing any systems that have been evaluated, designed or tested using the board, you agree to test and validate your design to confirm the functionality for your application. Any technical, applications or design information or advice, quality characterization, reliability data or other services provided by **onsemi** shall not constitute any representation or warranty by **onsemi**, and no additional obligations or liabilities shall arise from **onsemi** having provided such information or services.

onsemi products including the boards are not designed, intended, or authorized for use in life support systems, or any FDA Class 3 medical devices or medical devices with a similar or equivalent classification in a foreign jurisdiction, or any devices intended for implantation in the human body. You agree to indemnify, defend and hold harmless onsemi, its directors, officers, employees, representatives, agents, subsidiaries, affiliates, distributors, and assigns, against any and all liabilities, losses, costs, damages, judgments, and expenses, arising out of any claim, demand, investigation, lawsuit, regulatory action or cause of action arising out of or associated with any unauthorized use, even if such claim alleges that onsemi was negligent regarding the design or manufacture of any products and/or the board.

This evaluation board/kit does not fall within the scope of the European Union directives regarding electromagnetic compatibility, restricted substances (RoHS), recycling (WEEE), FCC, CE or UL, and may not meet the technical requirements of these or other related directives.

FCC WARNING — This evaluation board/kit is intended for use for engineering development, demonstration, or evaluation purposes only and is not considered by **onsemi** to be a finished end product fit for general consumer use. It may generate, use, or radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment may cause interference with radio communications, in which case the user shall be responsible, at its expense, to take whatever measures may be required to correct this interference.

onsemi does not convey any license under its patent rights nor the rights of others.

LIMITATIONS OF LIABILITY: **onsemi** shall not be liable for any special, consequential, incidental, indirect or punitive damages, including, but not limited to the costs of requalification, delay, loss of profits or goodwill, arising out of or in connection with the board, even if **onsemi** is advised of the possibility of such damages. In no event shall **onsemi**'s aggregate liability from any obligation arising out of or in connection with the board, under any theory of liability, exceed the purchase price paid for the board, if any.

The board is provided to you subject to the license and other terms per **onsemi**'s standard terms and conditions of sale. For more information and documentation, please visit www.onsemi.com.

#### **ADDITIONAL INFORMATION**

TECHNICAL PUBLICATIONS:

Technical Library: <a href="https://www.onsemi.com/design/resources/technical-documentation">www.onsemi.com/design/resources/technical-documentation</a> onsemi Website: <a href="https://www.onsemi.com/design/resources/technical-documentation">www.onsemi.com/design/resources/technical-documentation</a> on the first of the state of the state

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales