## DESCRIPTION

Demonstration circuit 1249 is a PoE to 3.3V@3.0A Isolated Converter featuring the LTC4267CDHC-3. The board provides a complete IEEE 802.3af power device (PD) interface and isolated 3.3V power supply solution for use in Power-over-Ethernet (PoE) applications in a very small printed circuit board footprint.

The LTC4267-3 integrates the  $25\text{k}\Omega$  signature resistor, classification current source, thermal overload protection, signature disable and power good signal along with an undervoltage lockout optimized for use with the IEEE required diode bridge. The precision dual level input current limit allows

the LTC4267-3 to charge load capacitors and interface with legacy PoE systems.

The LTC4267-3 combines the above features with a current mode switching controller designed for driving a N-channel MOSFET. It features programmable slope compensation, soft-start, and constant frequency operation, minimizing electrical noise even with light loads.

**Design files for this circuit board are available. Call the LTC factory.**

**Table 1. Performance Summary ( $T_A = 25^\circ\text{C}$ )**

| PARAMETER                             | CONDITION                                                               | VALUE          |

|---------------------------------------|-------------------------------------------------------------------------|----------------|

| Turn-on Voltage                       | Input from PSE                                                          | -37V           |

| Maximum Turn-off Voltage              | Input from PSE, PD switch turns off                                     | -31V           |

| Minimum operating voltage             | $I_{\text{OUT}} = 3\text{A}$                                            | -33V           |

| Power Converter Input operating range | $V_{\text{OUT}} = 3.3\text{V}$ , $I_{\text{OUT}} = 0$ to $3.0\text{A}$  | -37V to -57V   |

| Maximum Input Current                 | Input from PSE, PD high level current limit                             | 375mA, typical |

| Maximum Output Current                | $V_{\text{OUT}} = 3.3\text{V}$                                          | 3.0A           |

| Output Voltage                        | $V_{\text{IN}} = 48\text{VDC}$ from PSE, $I_{\text{OUT}} = 3.0\text{A}$ | 3.3V, typical  |

| Output Regulation                     | Line (0% to 100% full load)                                             | 2%             |

|                                       | Load (0% to 100% of rated full load)                                    | 2%             |

## QUICK START PROCEDURE

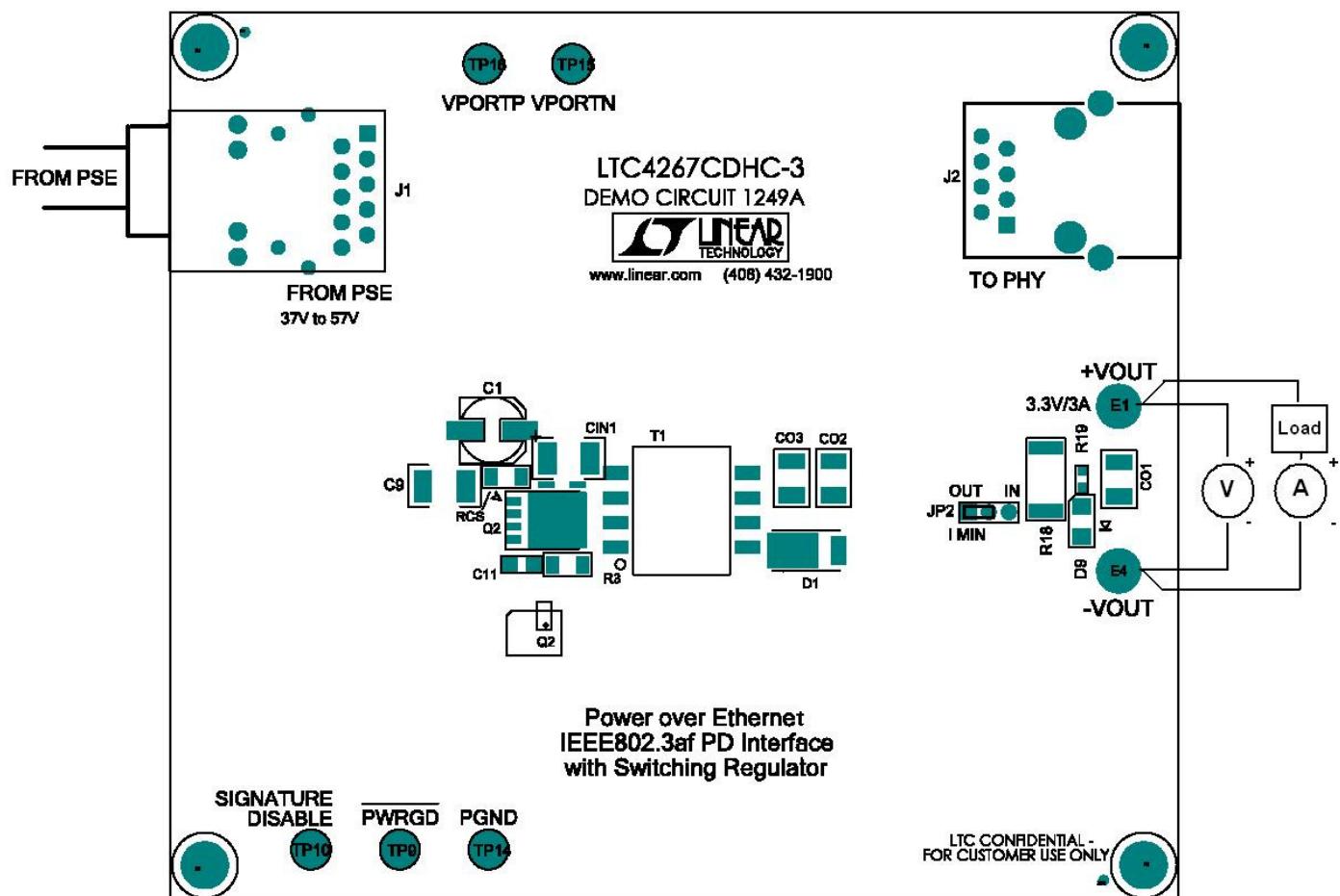

Demonstration circuit 1249 is easy to set up to evaluate the performance of the LTC4267-3. For proper equipment setup, refer to figure 1 and follow the procedure below:

1. With the power source to the PSE turned off, connect the input power supply to the board through the J1 filtered Ethernet connector.

2. In addition to a PSE, the DC1249 board can be powered by an alternate input power supply

through the VPORTP (TP16) and VPORTN (TP15) terminals. Do not connect more than one power source.

3. Connect the SIGNATURE DISABLE signal to VPORTN.

4. Turn on the PSE or alternate input power supply and increase the voltage until the power converter turns on. Be careful not to exceed 57VDC. NOTE: Make sure that the input voltage does not exceed 57VDC. If a higher voltage is required, power components with higher voltage ratings should be used.

## OPERATION

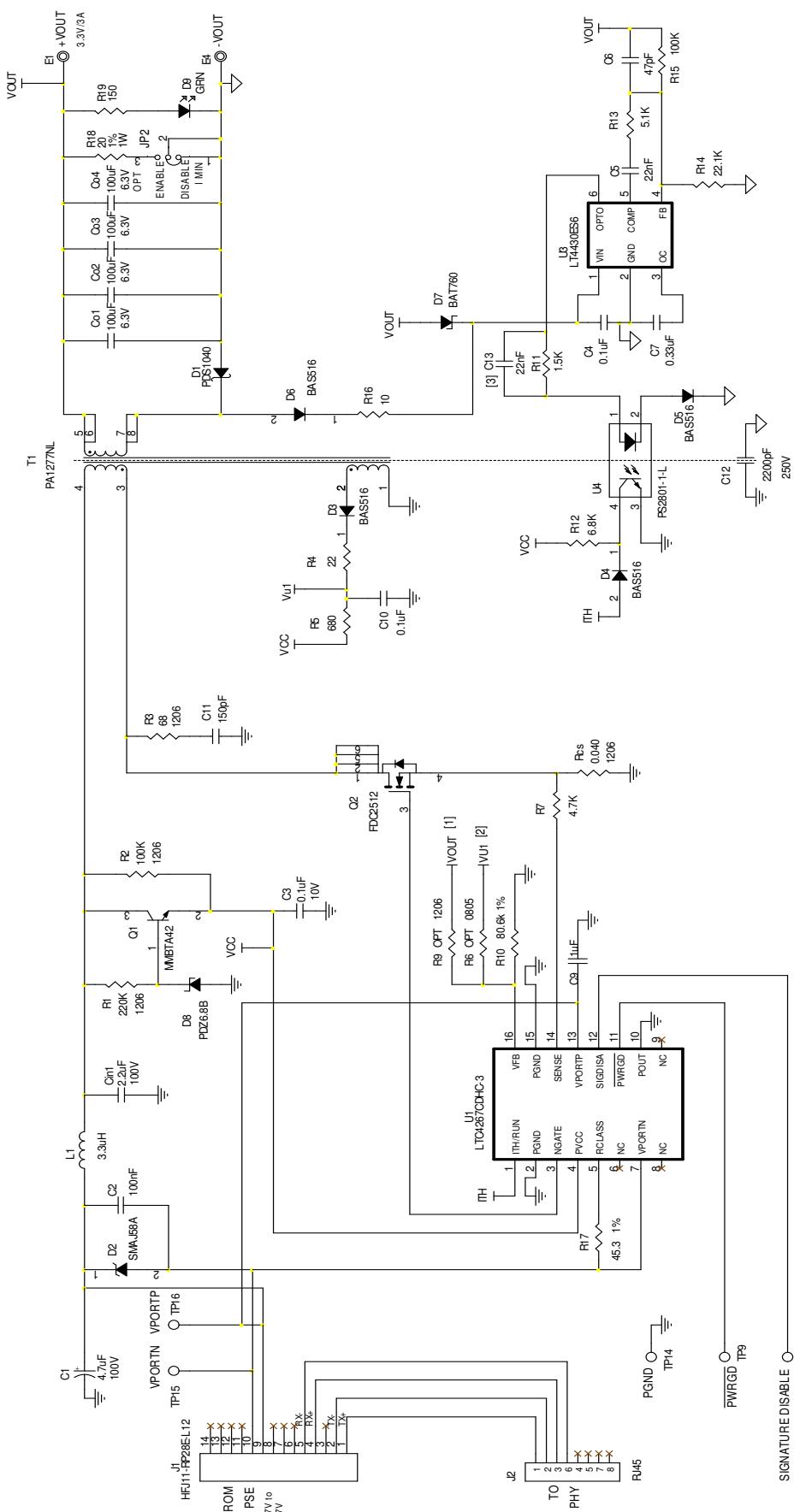

Demonstration circuit 1249 interfaces with a customer's Power-over-Ethernet test setup per Figure 1. The front end of the demo circuit implements the required Ethernet input interface transformer coupling and common-mode termination through the integrated connector J1. The demonstration circuit is set up to allow data to pass in and back out of the demo circuit while the DC1249 performs IEEE 802.3af interface functions. The Power Sourcing Equipment (PSE) is connected to J1 and the PHY is optionally connected to J2.

The PD is required to have 0.1uF of capacitance during detection; this is provided by C2. It is also required to have at least 5uF of capacitance after the in-rush circuit, provided by capacitors C1 and C9.

This demo circuit allows detection and power classification of the PD per the IEEE 802.3af specification. During the detection process of a PD, the LTC4267-3 displays the proper 25k $\Omega$  signature resistor. Signature detection may be disabled, if so desired, by pulling the SIGNATURE DISABLE line (TP10) up to VPORTP. If signature classification is disabled, all interface functions of

5. Verify proper classification and signature detection.

6. Check the output voltage. It should be 3.3V, typical. If there is no output, temporarily disconnect the load to make sure that the load is not too high.

7. Once the proper output voltage is established, adjust the load current within the appropriate range and observe the output regulation, ripple voltage, efficiency and other parameters.

the LTC4267-3 are disabled. Signature detection, classification and the internal power MOSFET switch are all disabled.

Note that the SIGNATURE DISABLE signal at TP10 is an open circuit. While it is true that this signal is internally pulled down within the LTC4267-3, the data sheet explicitly states that this signal must be tied to VPORTN or VPORTP. This signal is left open only for the convenience of the user when operating the demonstration circuit. The SIGNATURE DISABLE signal must be properly terminated in a production application.

Classification is programmed by the selection of a single external resistor, R17, connected to the RCLASS pin.

After detection and classification, the PD is powered up when the input voltage exceeds the LTC4267-3 turn-on under-voltage lock out (UVLO) through a dual-level current-limited power switch. While the voltage between POUT and VPORTN is above the Power Good trip point, the amperage through the power switch is held below the low-

# QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 1249

## POE TO 3.3V@3.0A ISOLATED

---

level current limit. When the voltage between POUT and VPORTN falls below the Power Good trip point, the Power Good signal goes active low and the amperage through the power switch is held below the high-level current limit.

For the PD to remain powered on, it must present to the PSE both AC and DC components of the Maintain Power Signature (MPS). The PD must hold the DC MPS by drawing at least 10mA or the PSE may disconnect power. The DC1249 demo board does implement a minimum load option with the JP2 jumper. By enabling this jumper the the circuit will draw approximately 16.5mA to satisfy the DC disconnect requirements.

The synchronous Flyback converter operates at a typical switching frequency of 300kHz, controlled by the current mode controller portion of the LTC4267-3. Galvanic isolation is achieved through transformer T1 and opto-isolator U4.

The primary side power path is comprised of C1, L1, Cin1,  $\frac{1}{2}$  of T1, Q2, and RCS. These components should be as close to each other as possible when laying out the printed circuit board. The secondary side power path is made up of the other  $\frac{1}{2}$  of T1, D1, and Cox. These parts should also be laid out as close to each other as possible, without overlapping any of the circuitry or traces of the primary side.

IN ORDER TO ENSURE PROPER OPERATION, THE DESIGNER MUST ENSURE THAT THE PD INPUT CURRENT REQUIREMENT DOES NOT EXCEED THE LTC4267-3 CURRENT LIMIT OVER THE UNIT'S OPERATING VOLTAGE RANGE.

# QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 1249

## POE TO 3.3V@3.0A ISOLATED

Figure 1. Proper Measurement Equipment Setup

# QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 1249

## POE TO 3.3V@3.0A ISOLATED

NOTES: UNLESS OTHERWISE SPECIFIED,

[1] FOR NON-ISOLATED DESIGN

[2] FOR NO-OPTO DESIGNS.

[3] ADD C13 ON TOP OF R11.

PWRGD O

TP10

SIGNATURE DISABLE O