# MLX75027 VGA Time-of-Flight Sensor

DATASHEET v1.0

## Features & Benefits

- 1/2" optical Time-of-Flight image sensor

- VGA (640 x 480) pixel array

- 10 x 10  $\mu\text{m}$  DepthSense® pixels

- Integrated microlenses

- Backside illumination (BSI technology)

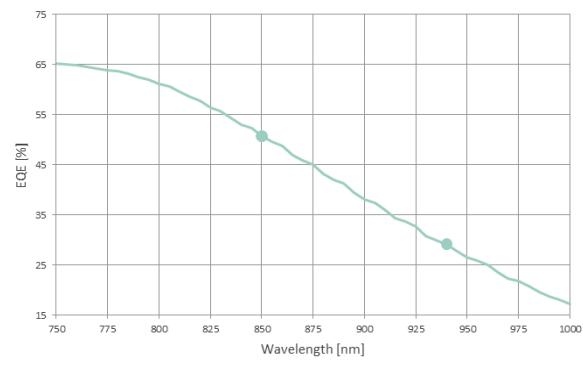

- External quantum efficiency 51% (850nm)

- External quantum efficiency 28% (940nm)

- High distance accuracy due to programmable modulating frequencies up to 100 MHz

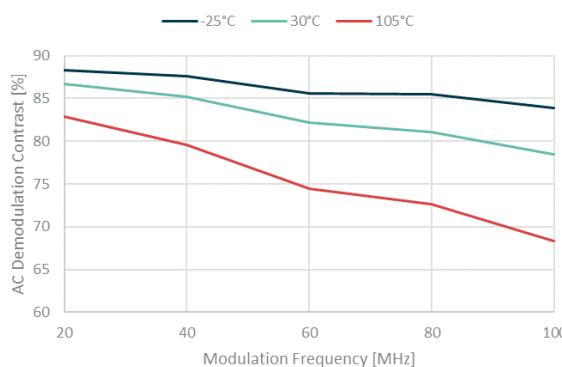

- AC Demodulation contrast 85 % (40 MHz)

- AC Demodulation contrast 78 % (100 MHz)

- Differential light source control with phase delay feedback loop

- Full resolution distance framerate of max. 120 FPS (4 phases, Tint 300 $\mu\text{s}$ , 4lane data @960Mbps MIPI configuration)

- Up to 8 raw phases (or quads) per frame

- Per-phase statistics & diagnostics

- Continuous or triggered operation mode(s)

- Configurable over I<sup>2</sup>C (up to 400kHz)

- CSI-2 serial data output, MIPI D-PHY, 1 clock lane, 2 or 4 data lanes (< 960 Mbps/lane)

- Build-in temperature sensor

- Region of interest (ROI) selection

- Integrated support for binning (2x2, 4x4, 8x8)

- Horizontal mirror & vertical flip image modes

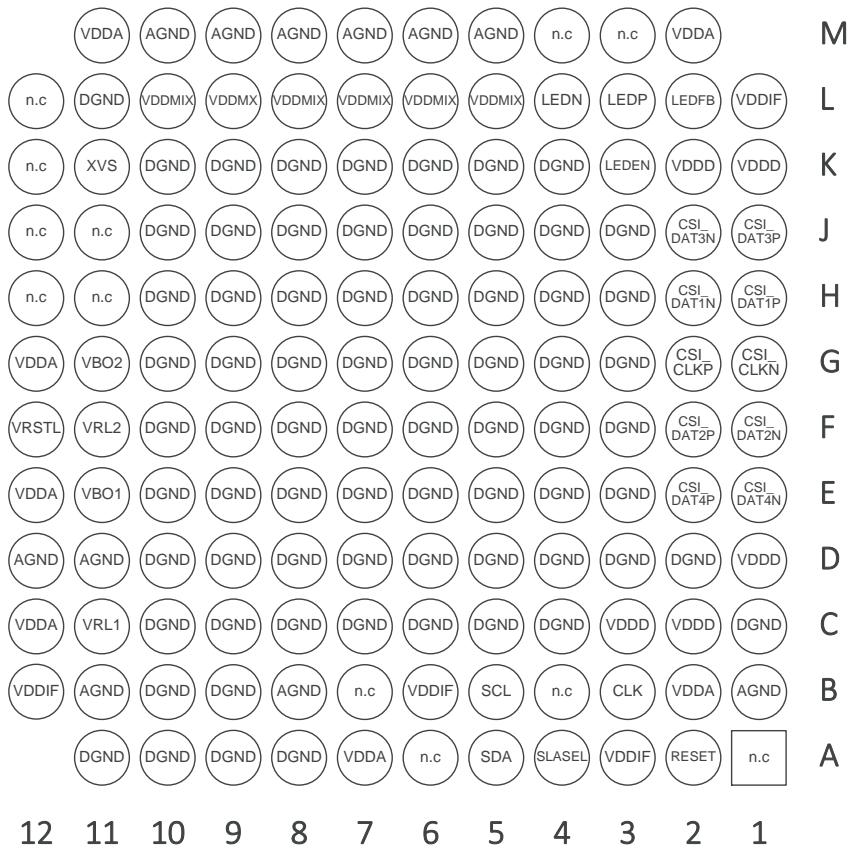

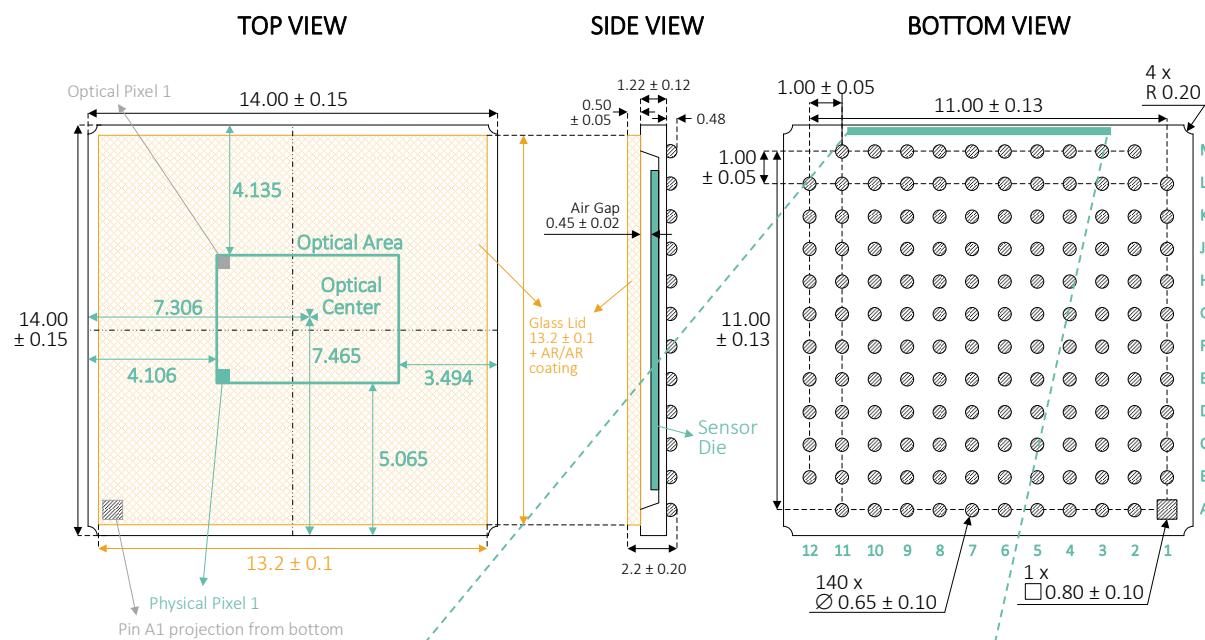

- 14 x 14 x 2.2 mm ceramic BGA package

- Number of pins = 141

- Ambient operating temperature range of -40 - 105°C

- MSL level 3 rated

- AEC-Q100 qualified (grade 2)

## Description

MLX75027 is a fully integrated optical Time-of-Flight image sensor. It's perfectly suited for automotive applications, including, but not limited to, gesture recognition, driver monitoring, skeleton tracking, people or obstacle detection and traffic monitoring. The sensor features a VGA (640x480) pixel array based on the DepthSense® pixel technology. Combined with a modulated light source this sensor is capable of measuring object distance and reflectivity under extreme background light conditions, 120KLUX robust when using lens with filter. This distance information can be used to calculate a complete 3D point cloud representation of a scene. Full resolution image acquisition up to 120 distance frames per second while supplied to a microcontroller via a standardized MIPI CSI-2 serial camera interface. The device is available in a ceramic BGA package and offers a variety of integration possibilities.

# Table of Contents

|                                                        |    |

|--------------------------------------------------------|----|

| Features & Benefits.....                               | 1  |

| Description.....                                       | 1  |

| Table of Contents.....                                 | 2  |

| Document Revision History.....                         | 5  |

| Ordering Information.....                              | 6  |

| 1. System Architecture.....                            | 7  |

| 2. Sensor Block Diagram.....                           | 8  |

| 3. Electrical Specifications.....                      | 9  |

| 3.1. Absolute Maximum Ratings.....                     | 9  |

| 3.2. Typical Operating Conditions.....                 | 9  |

| 3.3. Video Interface .....                             | 10 |

| 3.4. Power Consumption .....                           | 11 |

| 3.5. Maximum Distance Frame Rate .....                 | 13 |

| 3.6. Decoupling Recommendations.....                   | 13 |

| 3.7. Power-up Sequence.....                            | 14 |

| 3.8. Input Clock Requirements .....                    | 14 |

| 3.9. I <sup>2</sup> C Specifications.....              | 15 |

| 4. Optical Characteristics .....                       | 16 |

| 4.1. VGA Pixel Array Configuration.....                | 16 |

| 4.2. Pixel & Image Array Characteristics.....          | 17 |

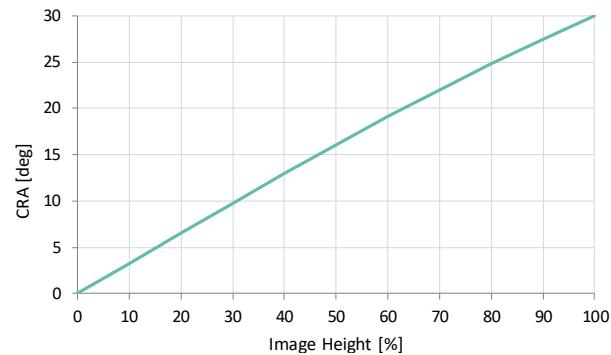

| 4.3. CRA (Chief Ray Angle) .....                       | 18 |

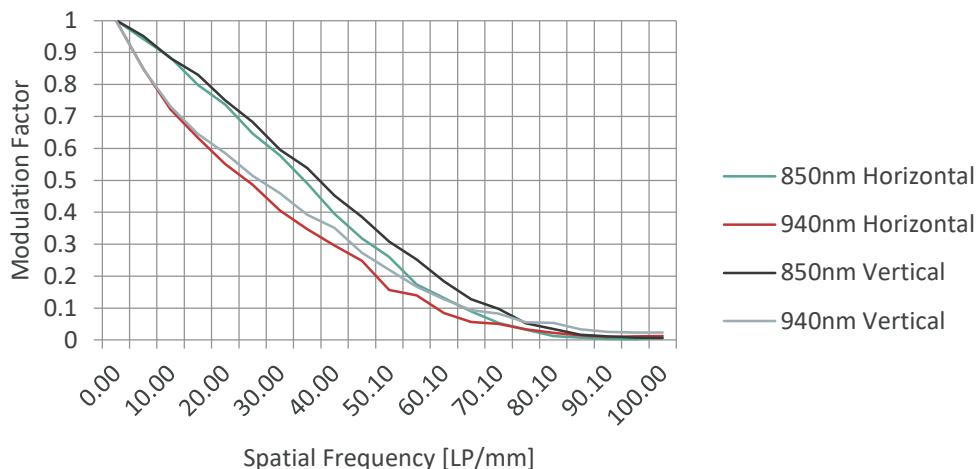

| 4.4. MTF (Modulation Transfer Function) .....          | 19 |

| 4.5. Application Lens Design Recommendations.....      | 19 |

| 5. Communication Interface(s).....                     | 20 |

| 5.1. I <sup>2</sup> C (Inter-Integrated Circuit) ..... | 20 |

| 5.2. MIPI Alliance CSI-2 Description.....              | 24 |

| 6. Start-up Sequence.....                              | 26 |

| 6.1. Initialization Process .....                      | 27 |

| 6.2. Initialization Register Map.....                  | 28 |

| 7. Register Settings .....                             | 30 |

| 7.1. Video Output Configuration .....                  | 30 |

| 7.2. Modes of Operation .....                          | 31 |

| 7.3. Data Output Modes .....                           | 32 |

|                                                              |           |

|--------------------------------------------------------------|-----------|

| 7.4. HMAX & Frame Read-Out Time .....                        | 33        |

| 7.5. PARAM_HOLD .....                                        | 35        |

| 7.6. USER_ID Register .....                                  | 35        |

| 7.7. Modulation Frequency .....                              | 36        |

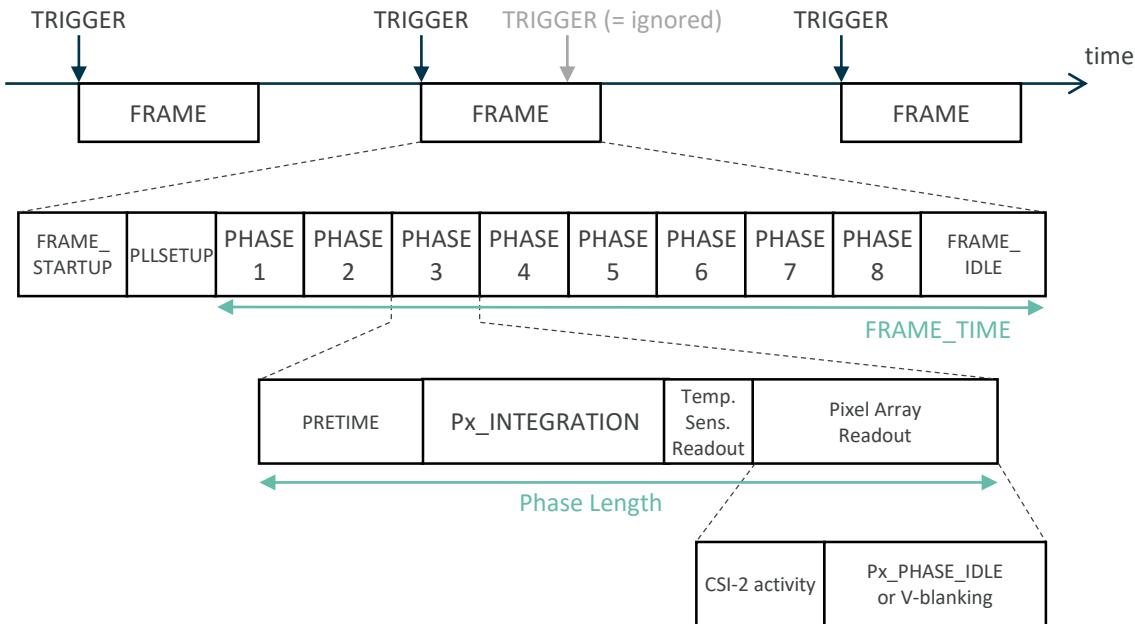

| 7.8. Frame Structure & Frame Rate .....                      | 37        |

| 7.9. FRAME_STARTUP .....                                     | 38        |

| 7.10. FRAME_TIME .....                                       | 38        |

| 7.11. PHASE_COUNT .....                                      | 38        |

| 7.12. Px_PREHEAT, Px_PREMIX .....                            | 39        |

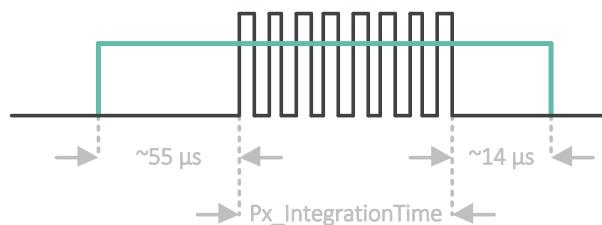

| 7.13. Px_INTEGRATION .....                                   | 41        |

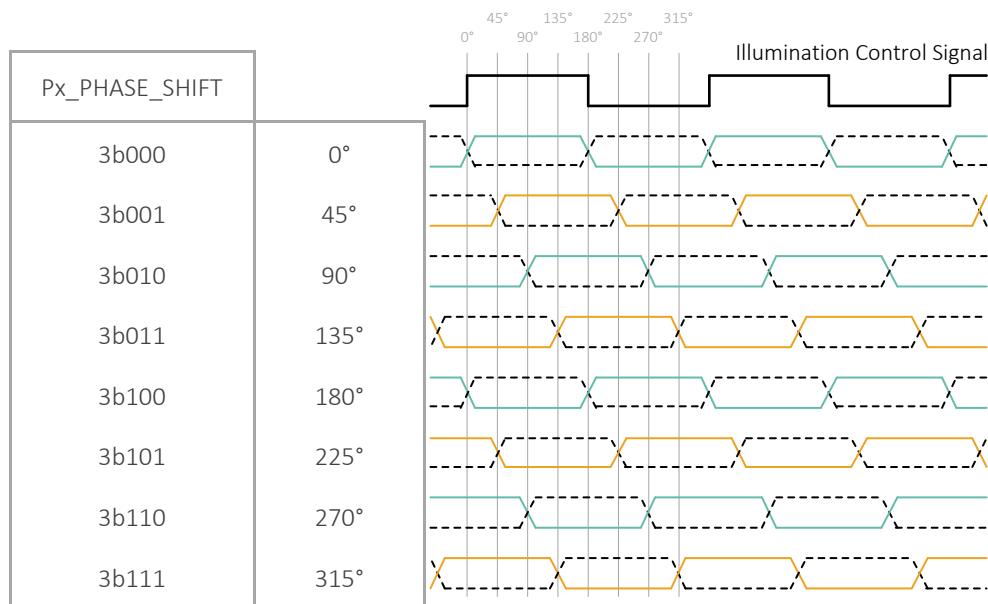

| 7.14. Px_PHASE_SHIFT .....                                   | 42        |

| 7.15. Px_PHASE_IDLE (or V-blanking) .....                    | 43        |

| 7.16. Px_LEDEN .....                                         | 43        |

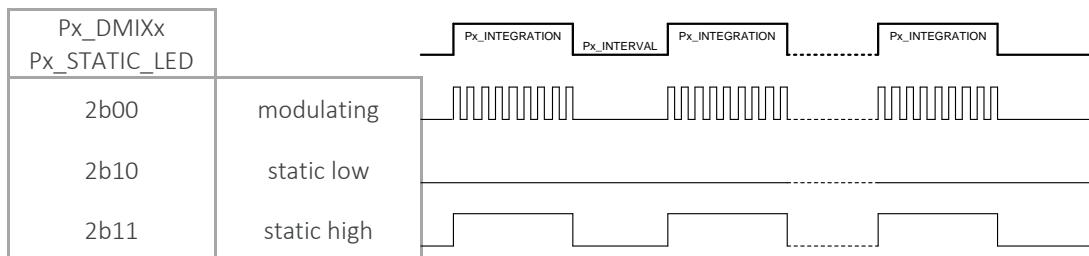

| 7.17. Px_DMIX0, Px_DMIX1 & Px_STATIC_LED .....               | 44        |

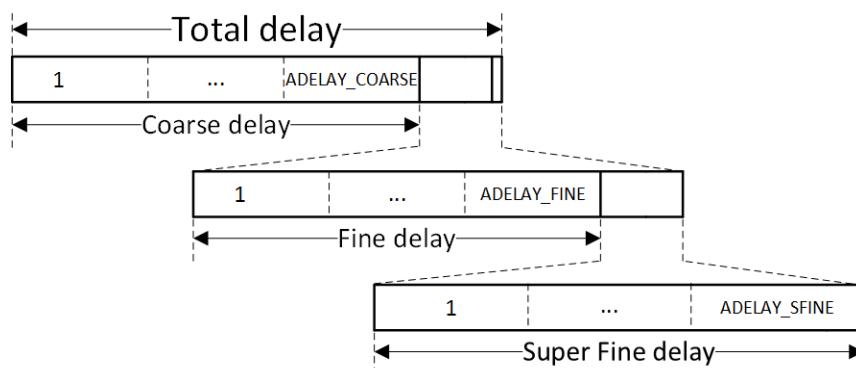

| 7.18. Analog Delay Setting .....                             | 45        |

| 7.19. Pixel Binning .....                                    | 47        |

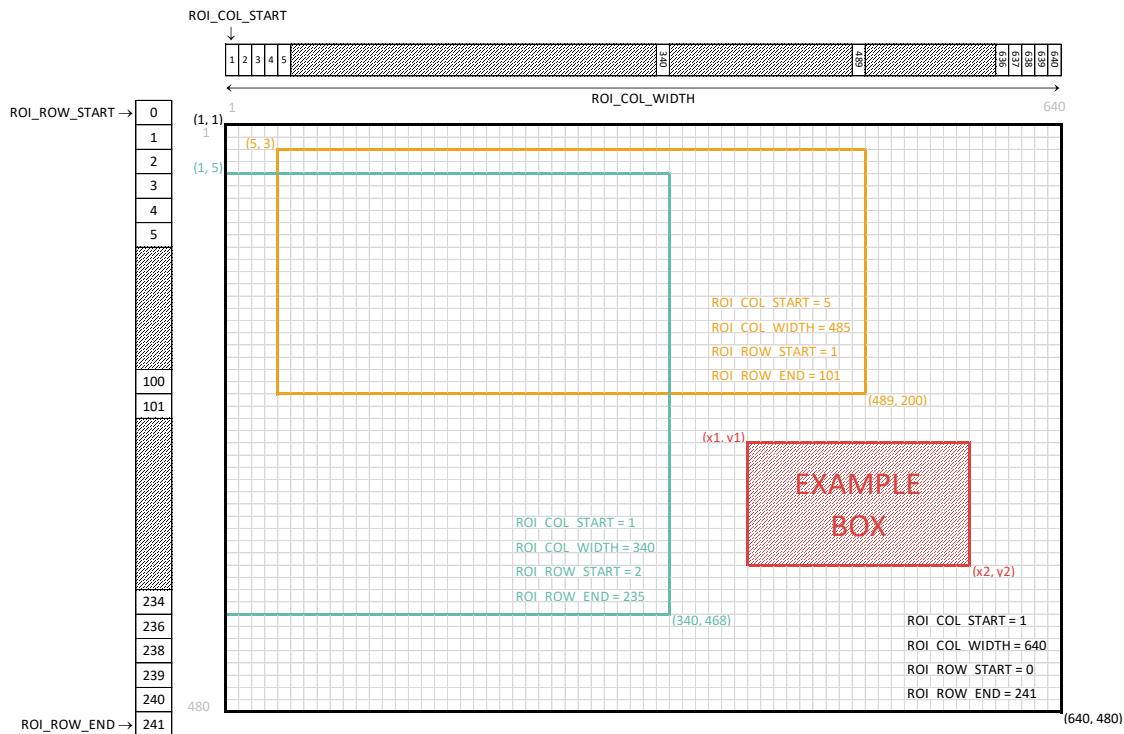

| 7.20. Region of Interest (ROI) .....                         | 48        |

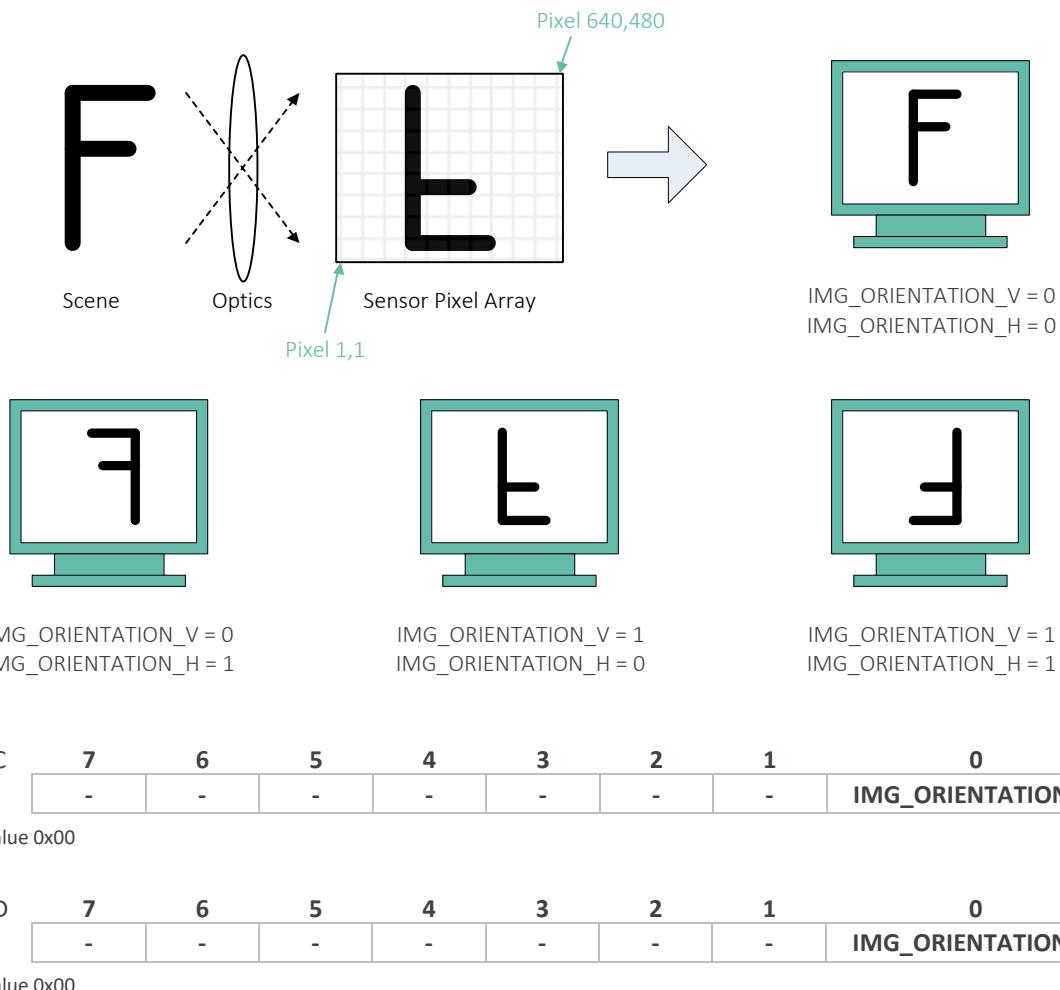

| 7.21. Flip & Mirror .....                                    | 49        |

| 7.22. Temperature Sensor .....                               | 49        |

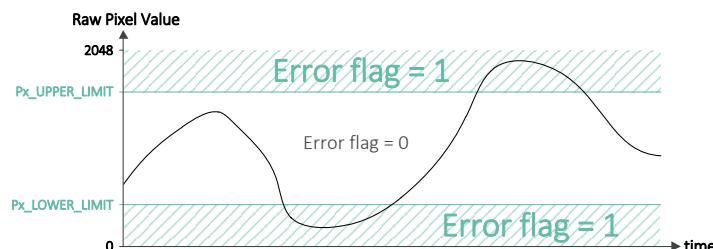

| 7.23. Pixel & Phase Statistics .....                         | 50        |

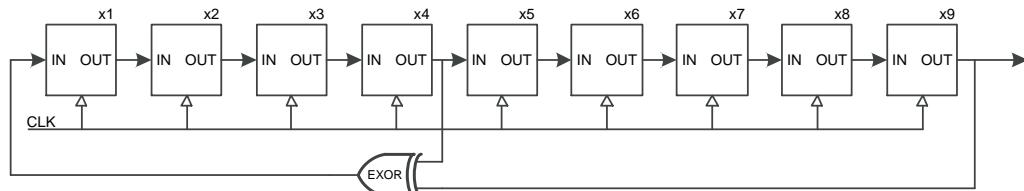

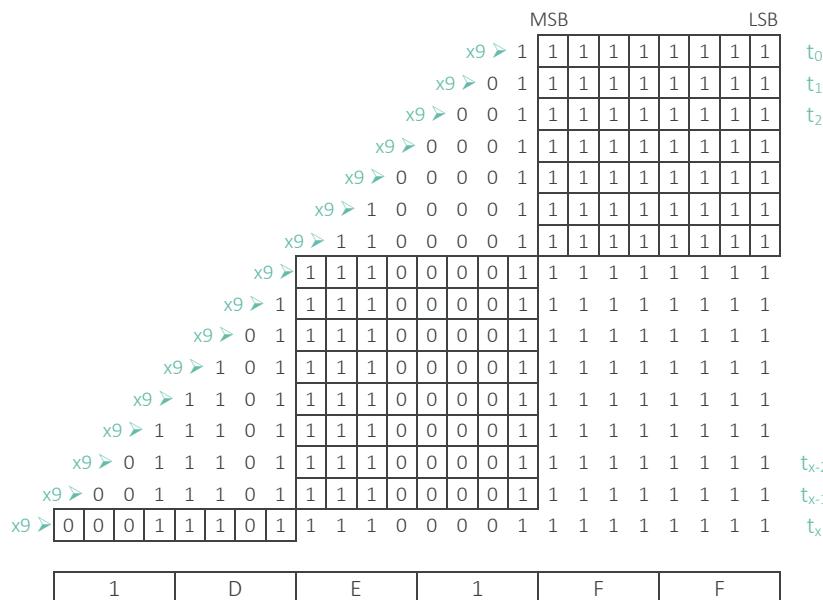

| 7.24. PN9 Test Pattern .....                                 | 53        |

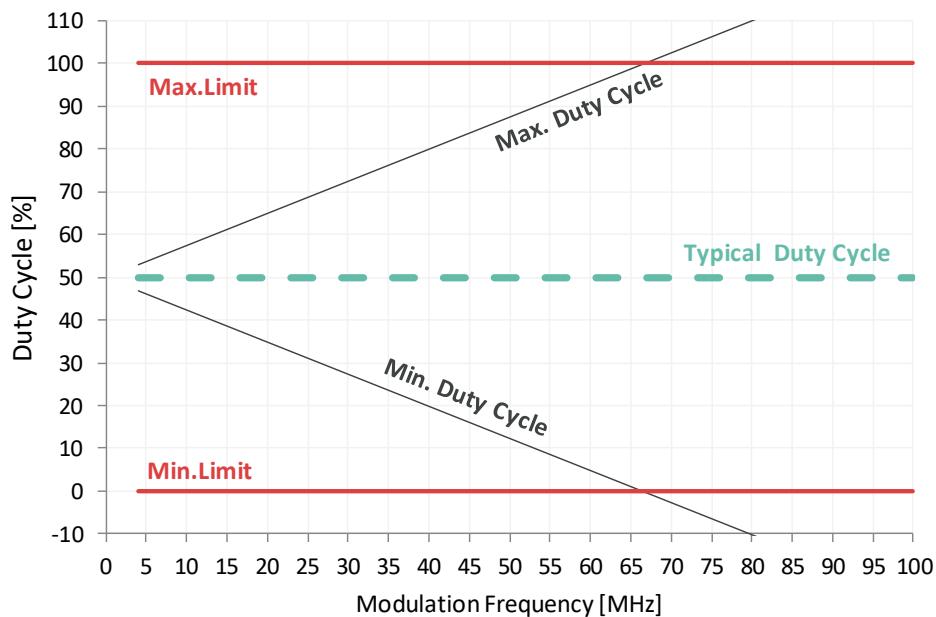

| 7.25. Duty Cycle Adjustment .....                            | 54        |

| 7.26. Illumination Signal (subLVDS or CMOS) .....            | 55        |

| 7.27. Device Identifiers .....                               | 55        |

| <b>8. MetaData Description .....</b>                         | <b>56</b> |

| 8.1. Embedded Data Format in 4 Lane MIPI Configuration ..... | 57        |

| 8.2. Embedded Data Format in 2 Lane MIPI Configuration ..... | 57        |

| <b>9. Distance &amp; Amplitude Calculation .....</b>         | <b>58</b> |

| <b>10. Package Information .....</b>                         | <b>59</b> |

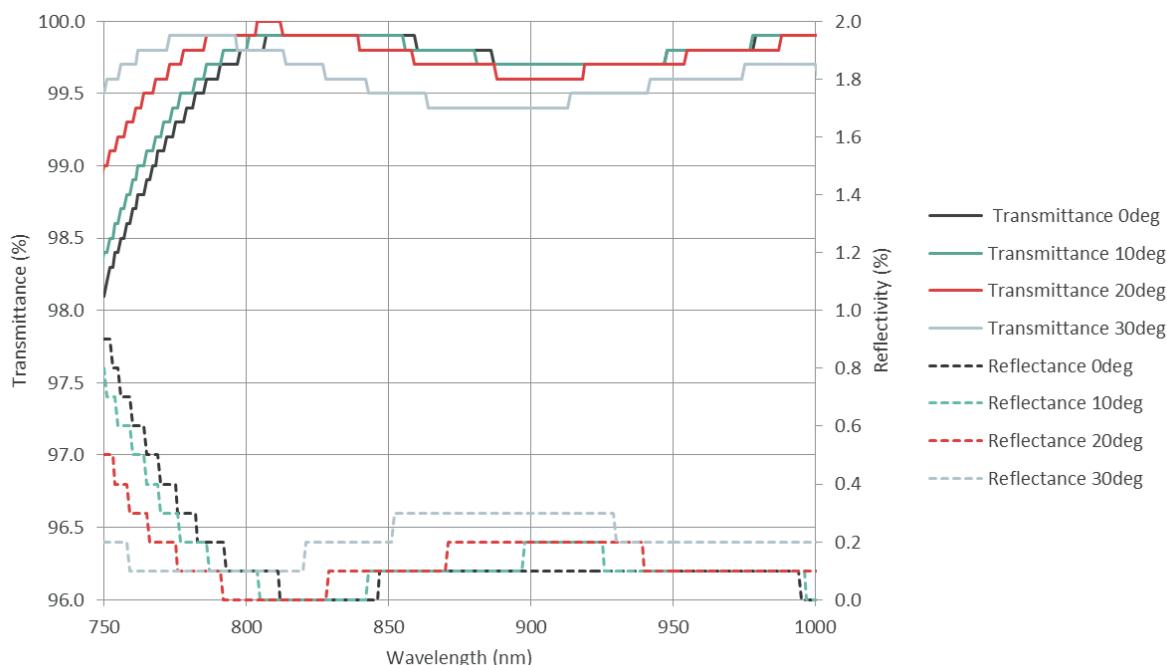

| 10.1. Transmittance and Reflectance .....                    | 59        |

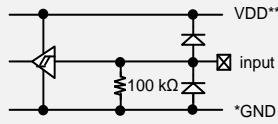

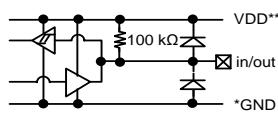

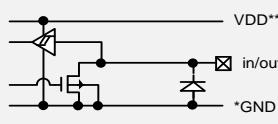

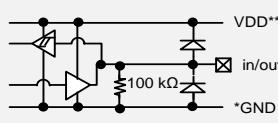

| 10.2. Pinout & Equivalent I/O Circuitry .....                | 60        |

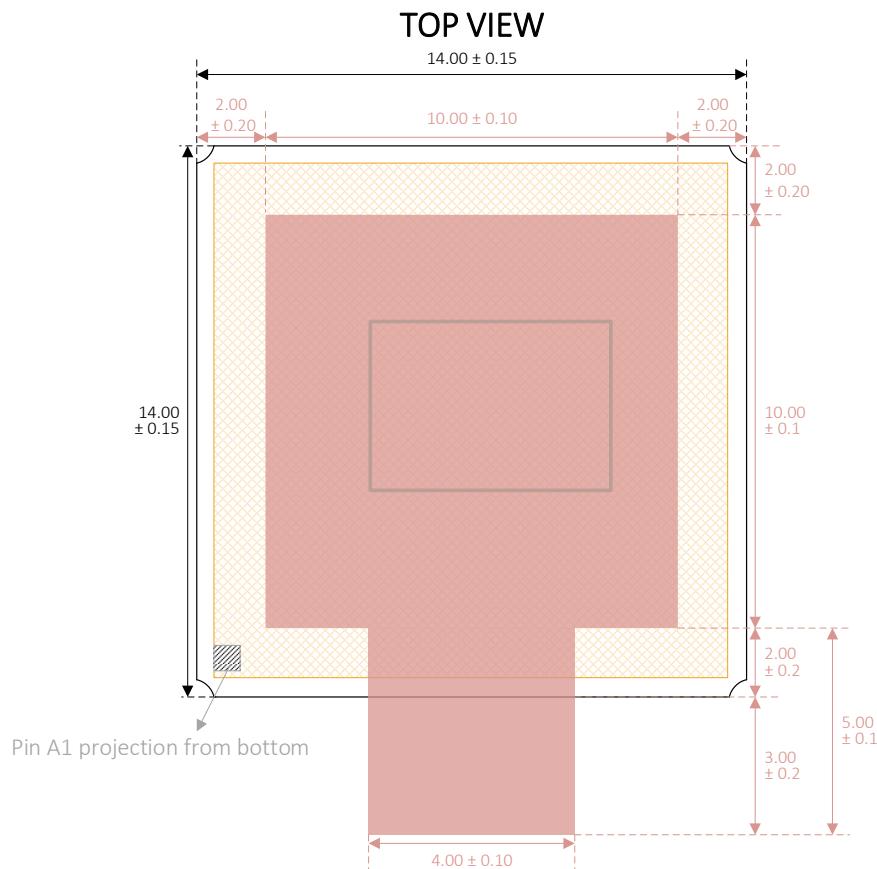

| 10.3. Mechanical Dimensions .....                            | 64        |

| 10.4. Package Marking .....                                  | 64        |

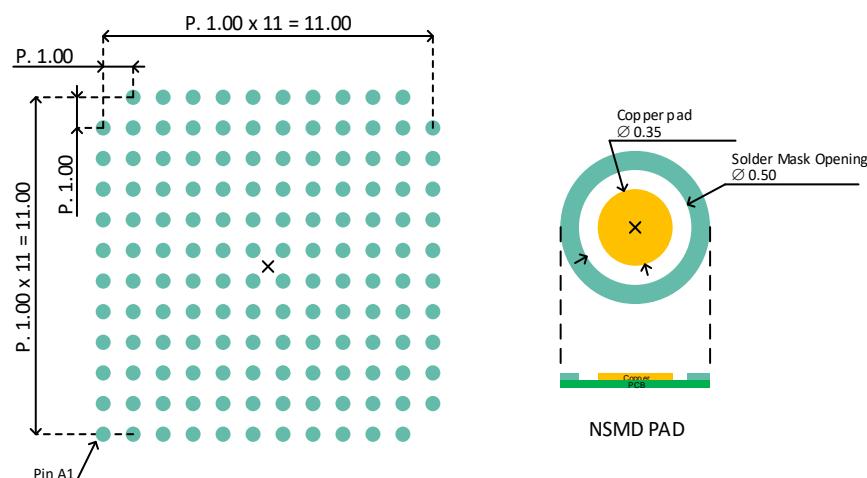

| 10.5. PCB Landing Pattern .....                              | 64        |

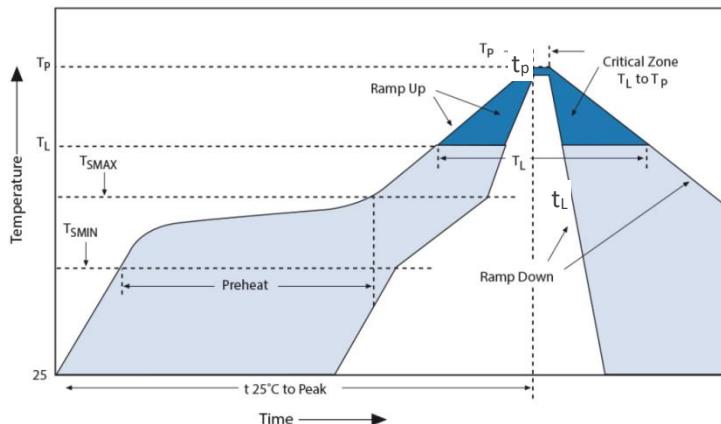

| 10.6. Reflow Solder Profile .....                            | 65        |

| 10.7. Reflow Cleaning Instructions .....                     | 65        |

|                        |    |

|------------------------|----|

| 10.8. Cover Tape ..... | 66 |

| Disclaimer .....       | 67 |

## Document Revision History

| Version   | Date       | Changes                                                         |

|-----------|------------|-----------------------------------------------------------------|

| 0.1 - 0.9 | /          | Draft version(s)                                                |

| 1.0       | 15/12/2020 | Section Ordering Information: Correction sample pack order code |

|           |            | Section 6: Updated Start-Up diagram and timings                 |

|           |            | Section 7.8: Correction phase length calculation                |

|           |            | Section 7.18: Correction analog delay calculations              |

|           |            | Section 7.27: Added DeviceType and LotNr. registers             |

|           |            | Section 10.3: Updated graphical representation optical area     |

|           |            | Section 10.5: Correction solder pad size                        |

|           |            | Section 10.8.1: Added covertape dimensions                      |

|           |            | Overall: Renaming of TRIGGER pin to TRIGGERB                    |

|           |            |                                                                 |

Table 1: Changelog

## Ordering Information

| Product  | Temperature Rating | Package Identifier | Option Code | Packing Style |

|----------|--------------------|--------------------|-------------|---------------|

| MLX75027 | R                  | TC                 | ABA-210     | TR            |

| MLX75027 | R                  | TC                 | ABA-200     | TR            |

| MLX75027 | R                  | TC                 | ABA-210     | SP            |

Table 2: Device ordering information

|                    |                                                                                                                                           |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Temperature Rating | R : -40°C to 105°C                                                                                                                        |

| Package Identifier | TC : Ceramic ball grid array                                                                                                              |

| Option Code        | ABA-210 : incl. double sided ARC coating, no optical filter, with cover tape <sup>1</sup><br>ABA-200 : version ABA-210 without cover tape |

| Packing Style      | TR : Tray<br>SP: Sample Pack                                                                                                              |

| Ordering Example   | MLX75027RTC-ABA-210-TR                                                                                                                    |

Table 3: Ordering options

Note <sup>1</sup>: The properties of the covertape are guaranteed for one year after shipping date if the devices are stored in appropriate conditions according the device MSL rating.

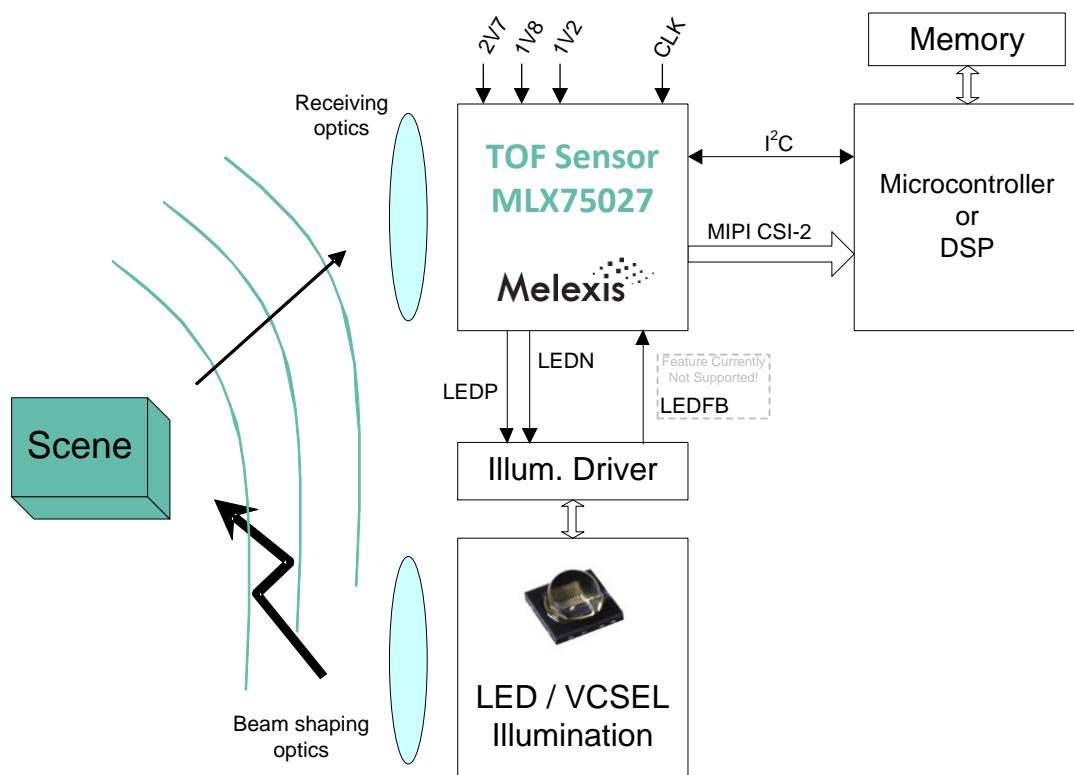

# 1. System Architecture

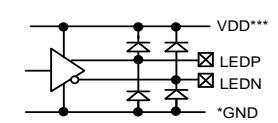

A complete TOF system or camera module includes at least these components:

- MLX75027 VGA (640x480 pixels) TOF pixel array

- A synchronized high bandwidth near infrared (NIR) active illumination source

- Beam shaping optics for the light distribution

- A receiving sensor lens (optimized for maximum NIR wavelength transmittance)

- A microprocessor, DSP, FPGA or SOC (system on chip) to calculate and process the data, compatible with MIPI camera serial interface CSI-2

Figure 1: System block diagram

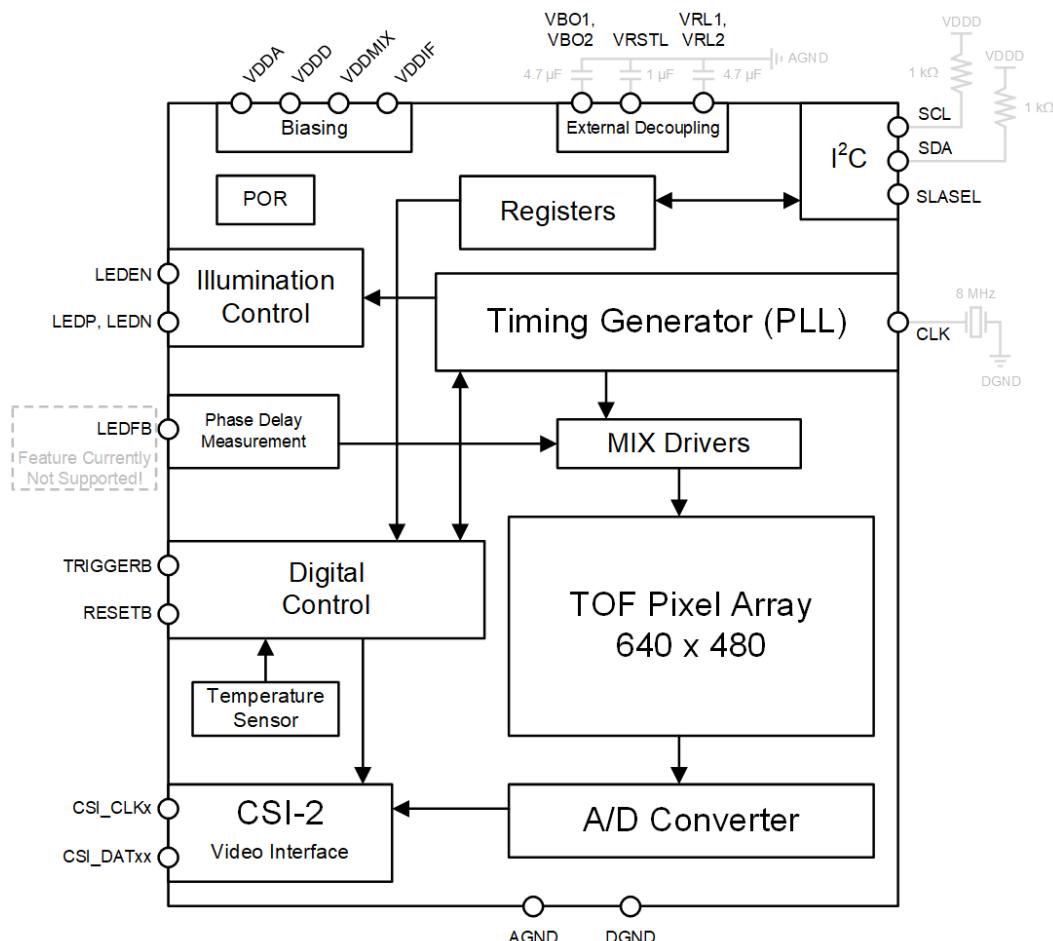

## 2. Sensor Block Diagram

MLX75027 is a Time-of-Flight (TOF) camera sensor with two tap Current Assisted Photo Demodulator (CAPD) pixels offering high responsivity. These backside illuminated pixels are connected to low noise analog amplifiers and converted by column ADCs which enable high speed & accurate image acquisition. Furthermore, it consists of a PLL timing generator, a high speed CSI2 serial interface, controllable registers via I<sup>2</sup>C and a digital control unit in charge of the different internal blocks.

Figure 2: Sensor block diagram

## 3. Electrical Specifications

### 3.1. Absolute Maximum Ratings

| Parameter                    | Symbol | Min. | Max. | Unit |

|------------------------------|--------|------|------|------|

| Supply voltage (analog)      | VDDA   | -0.3 | 3.3  | V    |

| Supply voltage (MIX drivers) | VDDMIX | -0.3 | 1.8  | V    |

| Supply voltage (digital)     | VDDD   | -0.3 | 1.8  | V    |

| Supply voltage (interfaces)  | VDDIF  | -0.3 | 3.3  | V    |

| Input voltage (digital IOs)  | VI     | -0.3 | 3.3  | V    |

| Output voltage (digital IOs) | VO     | -0.3 | 3.3  | V    |

| Storage temperature          |        | -40  | 125  | °C   |

Table 4: Absolute Maximum Ratings

Note : Absolute maximum ratings should not be exceeded at any time to avoid permanent hardware damage.

### 3.2. Typical Operating Conditions

| Parameter                                                             | Min.                                                                      | Typ.          | Max.               | Unit |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------|---------------|--------------------|------|

| VDDA Supply Voltage <sup>1</sup>                                      | 2.6                                                                       | 2.7           | 2.8                | V    |

| VDDMIX Supply Voltage <sup>1</sup>                                    | 1.1                                                                       | 1.2           | 1.3                | V    |

| VDDD Supply Voltage <sup>1</sup>                                      | 1.1                                                                       | 1.2           | 1.3                | V    |

| VDDIF Supply Voltage <sup>1</sup>                                     | 1.7                                                                       | 1.8           | 1.9                | V    |

| LEDP, LEDN single ended high level <sup>2</sup><br>LEDEN <sup>2</sup> | VDDIF -<br>0.2                                                            |               |                    | V    |

| LEDP, LEDN single ended low level <sup>3</sup><br>LEDEN <sup>3</sup>  |                                                                           |               | 0.2                | V    |

| LEDP/LEDN differential common mode<br>(LVDS_EN = 1)                   | VDDIF / 2<br>- 0.1                                                        | VDDIF / 2     | VDDIF / 2<br>+ 0.1 | mV   |

| LEDP/LEDN differential swing<br>(with R = 100Ω, LVDS_EN = 1)          | 100                                                                       | 150           | 220                | mV   |

| LEDP, LEDN termination resistor                                       |                                                                           | 100           |                    | Ohm  |

| Minimum TRIGGERB pulse length                                         |                                                                           | 1             |                    | μs   |

| Minimum RESETB pulse length                                           |                                                                           | 1             |                    | μs   |

| TRIGGERB<br>RESETB<br>SLASEL<br>LEDFB                                 | Maximum<br>input low                                                      |               | 0.2*<br>VDDIF      | V    |

| TRIGGERB<br>RESETB<br>SLASEL<br>LEDFB                                 | Minimum<br>input high                                                     | 0.8*<br>VDDIF |                    | V    |

| Junction to Ambient Thermal Resistance                                |                                                                           | 12            |                    | K/W  |

| Operating ambient temperature                                         | -40                                                                       |               | 105                | °C   |

| Temperature sensor accuracy                                           | @ -40°C T <sub>j</sub><br>@ 60°C T <sub>j</sub><br>@ 125°C T <sub>j</sub> |               | ±7<br>±5<br>±6     | °C   |

Table 5: Typical Operating Conditions

Note<sup>1</sup>: It is recommended to use the typical supply voltages

Note<sup>2</sup>: current of -2mA, LVDS\_EN = 0, typical load 15pF

Note<sup>3</sup>: current of 2mA, LVDS\_EN = 0, typical load 15pF

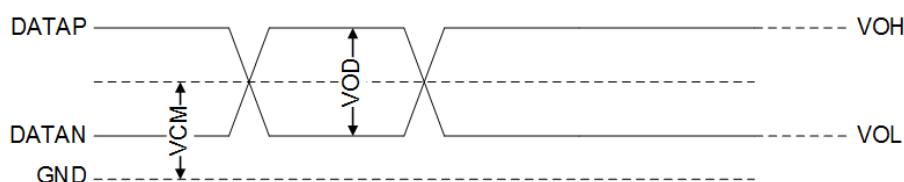

### 3.3. Video Interface

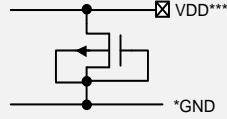

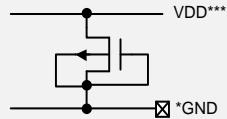

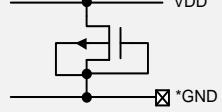

MLX75027 is fully compliant with the hardware description as described in the MIPI Alliance Specification for D-PHY version 1.20.00, released in September 2014. For a more detailed description about the parameters please consult the D-PHY MIPI documentation.

#### 3.3.1. MIPI DC specification

|      | Parameter | Min. | Typ. | Max. | Unit     |

|------|-----------|------|------|------|----------|

| HSDC | VOHHS     |      |      | 360  | mV       |

|      | VOD       | 140  |      | 270  | mV       |

|      | dVOD      |      |      | 14   | mV       |

|      | VCMTX     | 150  |      | 250  | mV       |

|      | dVCMTX    |      |      | 5    | mV       |

|      | ZOS       | 40   |      | 62.5 | $\Omega$ |

| LPDC | VOH       | 1.1  |      | 1.3  | V        |

|      | VOL       | -50  |      | 50   | mV       |

|      | ZOLP      | 110  |      |      | $\Omega$ |

Table 6: MIPI DC specification

Note: For a detailed explanation of the different parameters, please consult the MIPI D-PHY specifications v1.20.00.

Figure 3: MIPI DC layout

#### 3.3.2. MIPI AC specification

|      | Parameter                 | Min. | Typ. | Max.  | Unit    |

|------|---------------------------|------|------|-------|---------|

| HSAC | Trise, Tfall              | 50   |      | 312.5 | psec    |

|      | dVCMTX(>400MHz)           |      |      | 15    | mVrms   |

|      | dVCMTX(50-400MHz)         |      |      | 25    | mVpeak  |

| LPAC | Trise, Tfall              |      |      | 25    | ns      |

|      | Slew rate with Cload=0pF  |      |      | 500   | mV/nsec |

|      | Slew rate with Cload=5pF  |      |      | 300   | mV/nsec |

|      | Slew rate with Cload=20pF |      |      | 250   | mV/nsec |

|      | Slew rate with Cload=70pF |      |      | 150   | mV/nsec |

Table 7: MIPI AC specification

Note: For a detailed explanation of the different parameters, please consult the MIPI D-PHY specifications v1.20.00.

### 3.4. Power Consumption

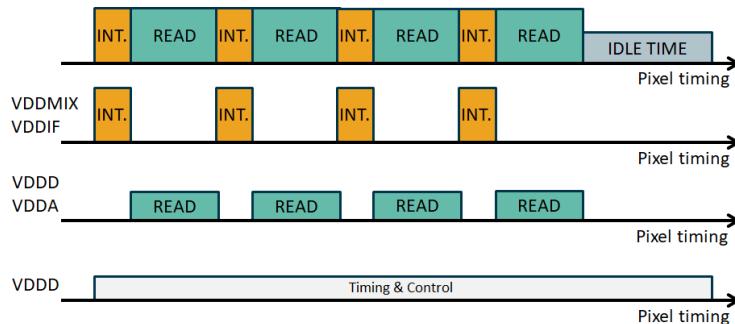

The total power consumption is split over four domains, none of the four domains are consuming at the same time. VDDMIX and VDDIF are dominantly active during the integration time, VDDD and VDDA during the readout time and a small amount of VDDD is active constantly. As shown below in Figure 4.

Figure 4: Power domains

The following table lists the absolute peak current per domain, however the typical duty cycle of each active period is only around 10%.

| Parameter                  | Symbol | Typ.   | Max. <sup>1</sup>   | Unit |

|----------------------------|--------|--------|---------------------|------|

| Analog Supply Current      | IDDA   | 39.8   | 42.2                | mA   |

| MIX Drivers Supply Current | IDDMIX | 1455.1 | 2980.3 <sup>2</sup> | mA   |

| Digital Supply Current     | IDDD   | 98.2   | 130.8               | mA   |

| I/O Supply Current         | IDDIF  | 2.1    | 2.6                 | mA   |

Table 8: Peak current

Note<sup>1</sup> : Max. is the worst case peak current over the full ambient operating temperature range, over the full process variation and at worst case settings.

Note<sup>2</sup> : This value is the worst case peak current at -40°C ambient temperature but realistically the system will not operate at this temperature so for PSU dimensioning we suggest to take into account the typical value. See Figure 6 for more information.

Taking the according duty cycles into account will lead to the following average power consumption per domain.

| Parameter          | Symbol | Application A     |                   | Application B     |                   |      |

|--------------------|--------|-------------------|-------------------|-------------------|-------------------|------|

|                    |        | Typ. <sup>1</sup> | Max. <sup>2</sup> | Typ. <sup>1</sup> | Max. <sup>2</sup> | Unit |

| Analog Supply      | PDDA   | 28.1              | 28.9              | 42.7              | 43.9              | mW   |

| MIX Drivers Supply | PDDMIX | 65.2              | 122.9             | 296.5             | 559.2             | mW   |

| Digital Supply     | PDDD   | 65.4              | 86.0              | 82.4              | 108.3             | mW   |

| I/O Supply         | PDDIF  | 1.7               | 1.9               | 2.4               | 2.6               | mW   |

| Total Supply       | P      | 160.3             | 239.7             | 423.8             | 714.0             | mW   |

Table 9: Power consumption

Note<sup>1</sup> : Typical values are the average power consumption with nominal voltage levels (at room temperature) for two defined application conditions:

**Application A : Typical**

- Full resolution (640x480 pixels)

- 4 raw phases per distance frame

- 30 distance frames per second

- 250  $\mu$ s integration time

- 60 MHz modulation frequency

- 800 mbps ( 4 lane MIPI data rate )

**Application B : Performance**

- Full resolution (640x480 pixels)

- 4 raw phases per distance frame

- 60 distance frames per second

- 600  $\mu$ s integration time

- 100 MHz modulation frequency

- 960 mbps ( 4 lane MIPI data rate )

Note<sup>2</sup> : Max. is the worst case power consumption over the full ambient operating temperature range and over the full process variation.

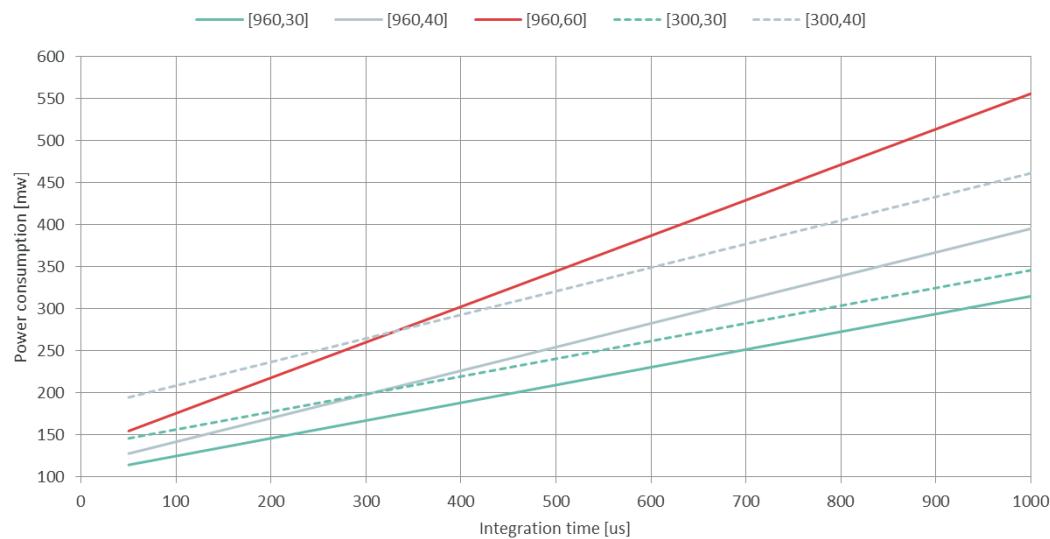

See Figure 5: Power consumption in function of integration time for typical power consumption at 40MHz modulation frequency in function of integration time for [MIPI speed, FPS]:

Figure 5: Power consumption in function of integration time

Note that there is a minor effect on power consumption at different MIPI speeds.

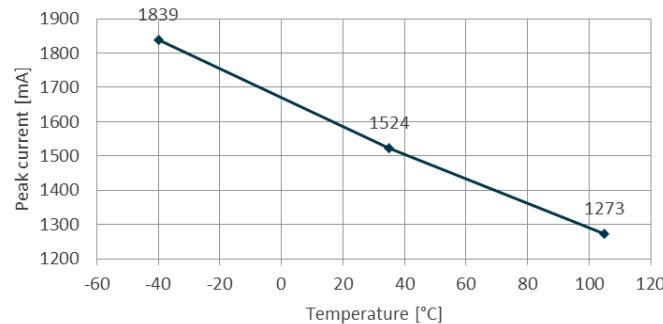

The previous plot does not take into account temperature variation. Over the full temperature range VDDMIX has the largest variation in power dissipation. Figure 6: MIX current over temperature indicates how MIX peak current changes over the full automotive -40°C to 105°C temperature range.

Figure 6: MIX current over temperature

Note that due to device self-heating in reality the device will always operate at a higher than ambient temperature resulting in a better overall power consumption.

### 3.5. Maximum Distance Frame Rate

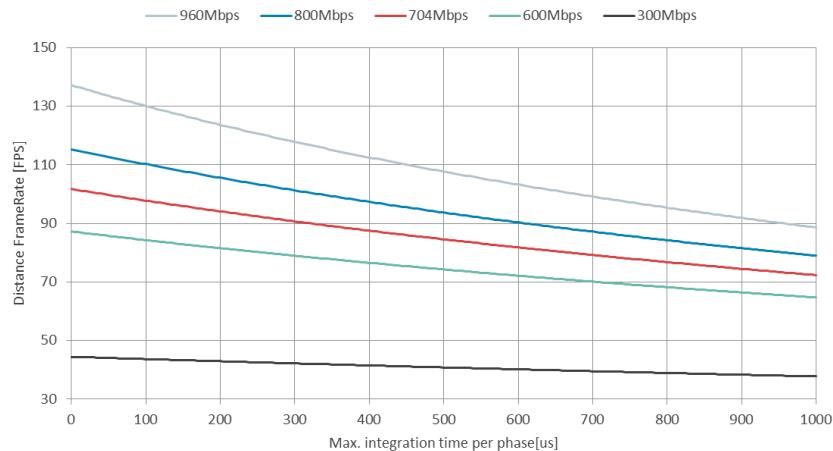

The maximum distance frame rate that can be achieved depends on the integration time, the minimum readout time per phase and the total amount of raw phases for each distance frame. Please consult the following section for more information how each parameter influences frame time: 7.8

The phase readout time is determined by the MIPI configuration settings as explained in section 7.4. In Figure 7: Theoretical Maximum Distance Frame Rate in function of Integration Time (per phase) is the Max. frame rate plotted for five typical MIPI settings.

Figure 7: Theoretical Maximum Distance Frame Rate in function of Integration Time (per phase)

Using higher integration time will increase the power consumption and self-heating. For safe operation within the automotive ambient temperature range of -40 to 105 °C this self-heating must be limited to 20 °C. A typical thermal resistance of 12K/W will result in max. allowable power of 1666mW which will not be reached by the device. However, a poor PCB design will result in worse thermal resistance and thus the framerate will not be readout but thermal / power limited, please make sure sufficient ground planes / heat dissipation is available.

### 3.6. Decoupling Recommendations

It is generally known that sensor performance can degrade with noisy input supplies. Specifications in this datasheet are only valid when stable voltage levels are available. Common decouple techniques use a two-step architecture consisting of a small capacitor (~10-100nF) as close as possible to the supply pin, combined with a bigger capacitor further away from the device, both connected to a low impedance ground plane to minimize inductance. Additionally, a small series ferrite bead can be used to keep high frequency noise outside of the IC, but also to keep internally generated noise from propagating to the rest of the system.

#### External Voltage Supplies

- VDDA : min. 1x 4.7µF

- VDDMIX : min. 1x 100nF & 4.7µF

- VDDD : min. 1x 100nF & 4.7µF

- VDDIF : min. 1x 100nF & 1µF

#### Internal Generated Voltage Supplies

- VBO1, VBO2 : min. 1x 4.7µF

- VRSTL : min. 1x 1µF

- VRL1, VRL2 : min. 1x 4.7µF

These recommendations are based on analysis of different available hardware platforms.

Each new hardware design requires an individual analysis to find & optimize the correct decoupling strategy.

### 3.7. Power-up Sequence

VDDD and VDDMIX use 1V2 as supply and it is possible to combine them on a single regulator source. However, VDDMIX exhibits high peak currents during the integration time that could compromise the stability of VDDD. Instantaneous voltage drops on VDDD need to be avoided and it is recommended to use two separate regulators instead.

With 2 regulators it is mandatory that VDDD is enabled simultaneously or not later than VDDMIX, and that VDDMIX is disabled before VDDD on power-down. More detailed power-up timings can be found in chapter 6. A slew rate of maximum 25 mV/μs has been specified for each power supply to avoid oscillations during power-up.

### 3.8. Input Clock Requirements

MLX75027 requires a fixed clock input signal of 8 MHz generated by an external crystal oscillator.

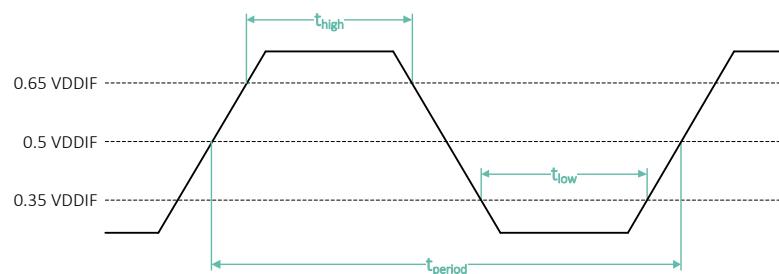

Figure 8: CLK square waveform input diagram

| Parameter            | Symbol              | Min. | Typ. | Max. | Unit |

|----------------------|---------------------|------|------|------|------|

| CLK high level       | CLK <sub>HIGH</sub> | 1.2  |      |      | V    |

| CLK low level        | CLK <sub>LOW</sub>  |      |      | 0.6  | V    |

| CLK frequency        |                     |      | 8    |      | MHz  |

| CLK low level width  | t <sub>low</sub>    | 50   | 62.5 | 75   | ns   |

| CLK high level width | t <sub>high</sub>   | 50   | 62.5 | 75   | ns   |

| CLK jitter           |                     |      |      | 600  | ps   |

Table 10: CLK input characteristics

### 3.9. I<sup>2</sup>C Specifications

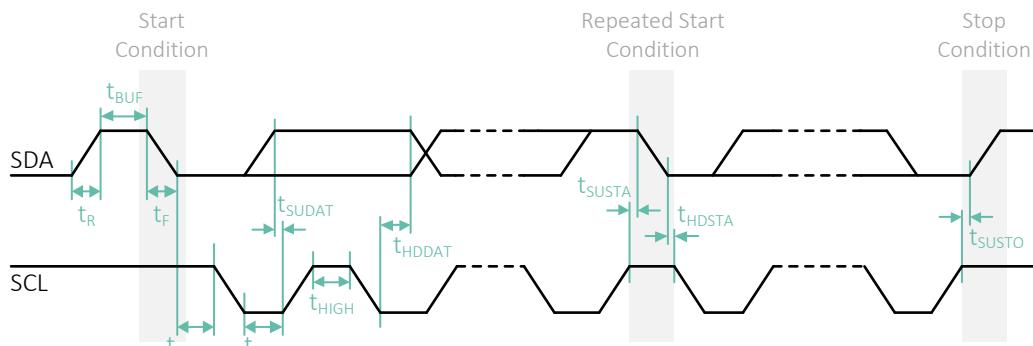

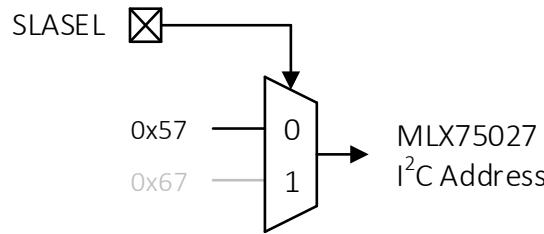

MLX75027 features a standard (up to 400 kHz) inter-integrated circuit communication interface, known as I<sup>2</sup>C. The sensor operates as I<sup>2</sup>C slave with default slave address of 0x57. This address can be changed via the external PIN SLASEL (more information can be found in section 5.1.6). The master I<sup>2</sup>C device is responsible to initiate all communication, it is in control of the clock line (SCL) & sends data via the SDA line. Each I<sup>2</sup>C slave on the bus monitors this communication and will respond to the master when requested.

Figure 9: I<sup>2</sup>C serial communication diagram

| Parameter                | Symbol           | Condition                                   | Min.      | Max.      | Unit |

|--------------------------|------------------|---------------------------------------------|-----------|-----------|------|

| Low level input voltage  | V <sub>IL</sub>  |                                             | -0.3      | 0.3*VDDIF | V    |

| High level input voltage | V <sub>IH</sub>  |                                             | 0.7*VDDIF | 1.9       | V    |

| Low level output voltage | V <sub>OL</sub>  | VDDIF > 2V, sink 3mA                        | 0         | 0.2*VDDIF | V    |

| Output fall time         | t <sub>of</sub>  | Load 10pF - 400 pF<br>0.7*VDDIF - 0.3*VDDIF |           | 250       | ns   |

| Input current            | I <sub>i</sub>   | 0.1*VDDIF - 0.9*VDDIF                       | -10       | 10        | µA   |

| SDA I/O capacitance      | C <sub>i/o</sub> |                                             |           | 10        | pF   |

| SCL input capacitance    | C <sub>i</sub>   |                                             |           | 10        | pF   |

Table 11: I<sup>2</sup>C Electrical Specifications

| Parameter                                      | Symbol             | Min. | Max. | Unit |

|------------------------------------------------|--------------------|------|------|------|

| SCL clock frequency                            | f <sub>SCL</sub>   | 0    | 400  | kHz  |

| Rise time (SCD & SCL)                          | t <sub>R</sub>     |      | 300  | ns   |

| Fall time (SDA & SCL)                          | t <sub>F</sub>     |      | 300  | ns   |

| Hold time (start condition)                    | t <sub>HDSTA</sub> | 0.6  |      | ns   |

| Setup time (rep.-start condition)              | t <sub>SUSTA</sub> | 0.6  |      | µs   |

| Setup time (stop condition)                    | t <sub>SUSTO</sub> | 0.6  |      | µs   |

| Data setup time                                | t <sub>SUDAT</sub> | 100  |      | µs   |

| Data hold time                                 | t <sub>HDDAT</sub> | 0    | 0.9  | µs   |

| Bus free time between stop and start condition | t <sub>BUF</sub>   | 1.3  |      | µs   |

| Low period of the SCL clock                    | t <sub>LOW</sub>   | 1.3  |      | µs   |

| High period of the SCL clock                   | t <sub>HIGH</sub>  | 0.6  |      | µs   |

Table 12: I<sup>2</sup>C Fast Mode Specifications

## 4. Optical Characteristics

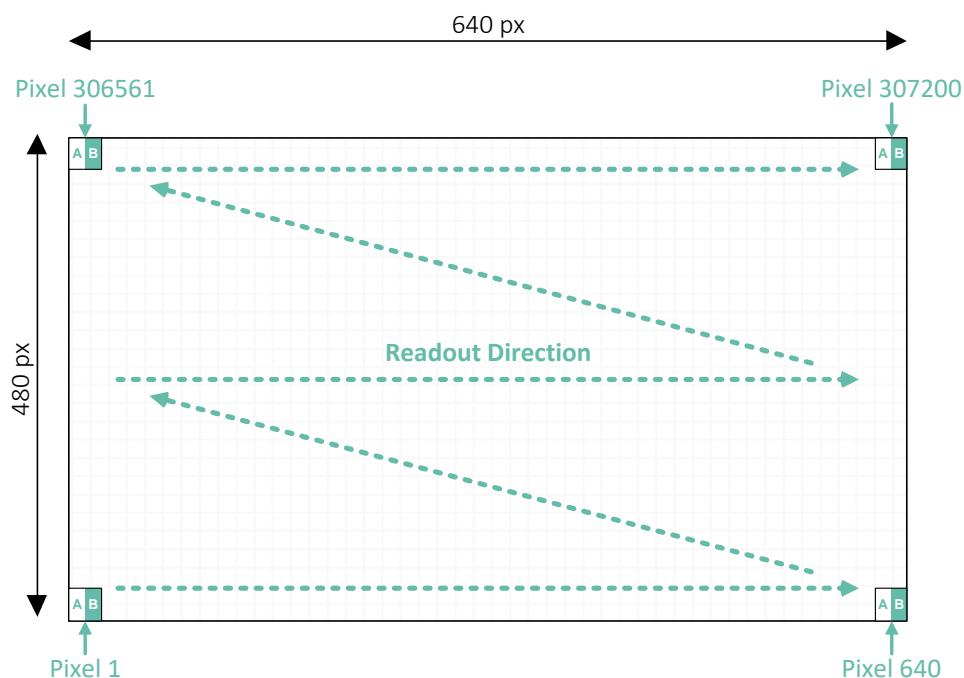

### 4.1. VGA Pixel Array Configuration

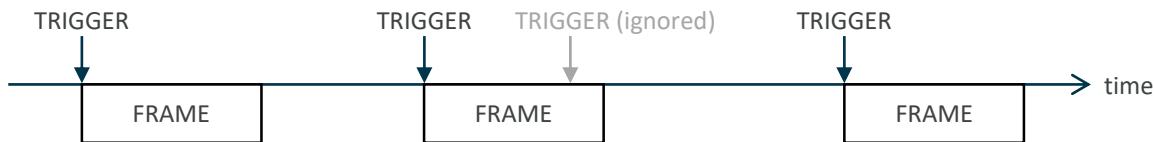

The pixel array has a total of 640 x 480 DepthSense® pixels. Each pixel consists of 2 individual taps called tap A and tap B. Information from both taps is needed for a reliable distance calculation. The data format (or output modes) available via the MIPI CSI2 video interface can be selected by the user and are described in more detail in section 7.3. The pixels are read out from bottom left, to top right, first horizontally, afterwards vertically, like indicated in this figure. This picture represents the physical pixel orientation, please note that output will have pixel 1 on top left to compensate for the lens by default as explained in section 7.21.

Figure 10: VGA readout

## 4.2. Pixel & Image Array Characteristics

| Parameter                                        | Min. | Typ.                                           | Max. | Unit   |

|--------------------------------------------------|------|------------------------------------------------|------|--------|

| Pixel pitch                                      |      | 10                                             |      | µm     |

| Pixel architecture                               |      | Dual Tap Current Assisted Photonic Demodulator |      |        |

| External Quantum Efficiency <sup>1</sup> @ 850nm |      | 51.0                                           |      | %      |

| External Quantum Efficiency <sup>1</sup> @ 940nm |      | 28.0                                           |      | %      |

| Pixel dark noise                                 |      | 83                                             |      | e-     |

| AC demodulation contrast <sup>2</sup> @ 40MHz    |      | 85                                             |      | %      |

| AC demodulation contrast <sup>2</sup> @ 100MHz   |      | 78                                             |      | %      |

| Single tap dark current                          | 20   | 51                                             | 508  | ke-/s  |

| Single tap full well capacity                    | 106  | 160                                            |      | ke-    |

| Single tap conversion gain                       |      | 0.0106                                         |      | DN/e-  |

| Phase drift over temperature <sup>3</sup>        |      | 0.046                                          |      | deg/°C |

| Local PDNU <sup>4</sup>                          |      |                                                | tbd  | deg    |

| Global PDNU <sup>5</sup>                         |      |                                                | tbd  | deg    |

| Microlens(s) <sup>6</sup>                        |      | yes                                            |      |        |

| Maximum CRA (chief ray angle)                    |      |                                                | 30   | °      |

Table 13: Pixel & Image Array Characteristics

Note<sup>1</sup> : External quantum efficiency (EQE) can be calculated as  $EQE_{\lambda} = \frac{RE_{\lambda}}{\lambda} \cdot \frac{h \cdot c}{e} \cdot FF = \frac{RE_{\lambda}}{\lambda} \cdot 1240 \cdot FF$

$RE_{\lambda}$  = responsivity at wavelength (in A/W)

$\lambda$  = the wavelength (in nm)

$h$  = Planck's constant

$c$  = speed of light in vacuum

$e$  = elemental charge

$FF$  = fill factor (in %)

Note<sup>2</sup> : Detailed AC demodulation contrast data can be found in Figure 11.

Note<sup>3</sup> : Stability of the calculated phase (= distance) over temperature

Note<sup>4</sup> : Local PDNU (phase depth non uniformity) is a metric for the phase offset between 3x3 pixel blocks for a homogeneous flat field measurement

Note<sup>5</sup> : Global PDNU is similar to local PDNU but data is based on 10x10 pixel blocks

Note<sup>6</sup> : The microlens array material is sensitive to excessive UV radiation. In product qualification it has been exposed with a constant UV equivalent of 10 years of sunlight without discernible degradation of the structure integrity. It is our recommendation to limit direct UV radiation during camera assembly/glue processes as much as possible

Figure 11: AC Demodulation Contrast in function of Modulation Frequency

Figure 12: External Quantum Efficiency in function of Wavelength

### 4.3. CRA (Chief Ray Angle)

| Image Height <sup>1</sup> (%) | Image Height <sup>1</sup> (mm) | CRA (°) |

|-------------------------------|--------------------------------|---------|

| 0                             | 0.0                            | 0       |

| 10                            | 0.4                            | 3.3     |

| 20                            | 0.8                            | 6.6     |

| 30                            | 1.2                            | 9.8     |

| 40                            | 1.6                            | 13      |

| 50                            | 2.0                            | 16.1    |

| 60                            | 2.4                            | 19.1    |

| 70                            | 2.8                            | 22.0    |

| 80                            | 3.2                            | 24.8    |

| 90                            | 3.6                            | 27.5    |

| 100                           | 4.0                            | 30      |

Table 14: Image Height vs CRA

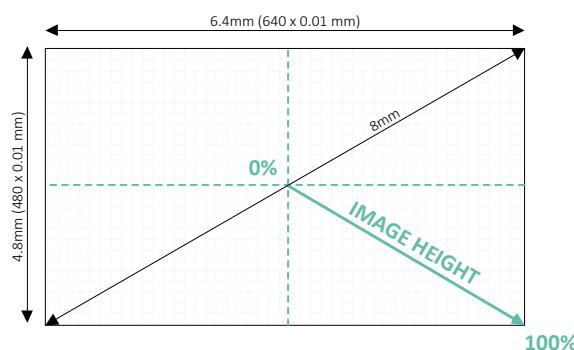

Note<sup>1</sup> : Image height is defined along the diagonal axis of the image array as shown in Figure 14: Image Height Definition.

Figure 13: Image height versus CRA

Figure 14: Image Height Definition

## 4.4. MTF (Modulation Transfer Function)

The modulation transfer function is a indication on the system response to different spatial frequencies. It tends to decrease with an increase in spatial frequency. A typical example is an out of focus lens, which has a low modulation factor for higher frequencies, resulting in an overall blur of the edges in the image.

Figure 15: Modulation Transfer Function

The total system MTF is impacted by the image sensor and its optics. The shown data is considered the sensor only MTF, as it has been compensated for lens influences.

## 4.5. Application Lens Design Recommendations

When designing or selecting external optics to focus the light on the optical sensitive pixel area there are a few recommendations to take into account:

- To avoid pixel saturation under strong sunlight an optical bandpass filter is highly recommended. The spectral width of this filter depends on the type of illumination, LED or VCSEL, and should be as small as possible, taken into account the spectral drift over temperature.

- To reduce the illumination radiant intensity and to maximize the system efficiency the lens aperture should be as high as possible (= low F-number)

## 5. Communication Interface(s)

MLX75027 uses one low speed bidirectional I<sup>2</sup>C interface for register control and one unidirectional high speed MIPI CSI2 serial video output interface.

### 5.1. I<sup>2</sup>C (Inter-Integrated Circuit)

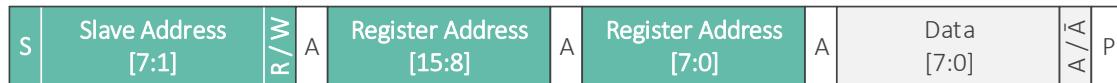

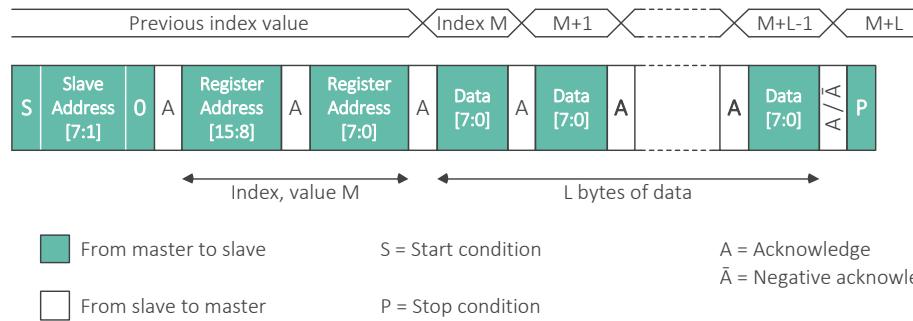

This 2-wire serial communication protocol supports 16 bit register addresses and 8 bit data messages.

#### 5.1.1. I<sup>2</sup>C Timing Sequence

- From master to slave

- S = Start condition

- Sr = Repeated start condition

- P = Stop condition

- R/W = read/write command

- 0 : Write (master > slave)

- 1 : Read (slave > master)

- Direction depends on operation

- A = Acknowledge

- Ā = Negative acknowledge

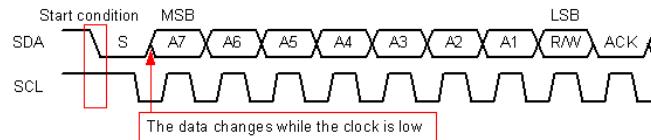

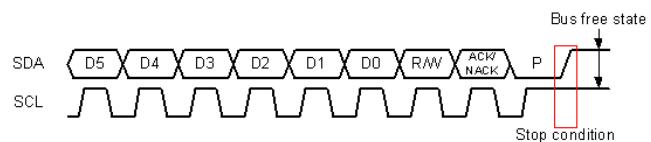

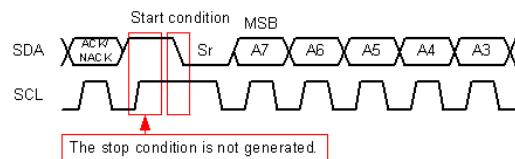

The data is transferred serially, MSB first in 8-bit units. After each data byte is transferred, A (Acknowledge) / Ā (Negative acknowledge) is transferred. Data (SDA) is transferred at the clock (SCL) cycle. SDA can change only while SCL is low, so the SDA value must be held while SCL is high. The Start condition is defined by SDA changing from high to low while SCL is high. When the Stop condition is not generated in the previous communication phase and Start condition for the next communication is generated, that Start condition is recognized as a Repeated Start condition.

Start condition

Stop condition

Repeated start condition

Figure 16: I<sup>2</sup>C conditions

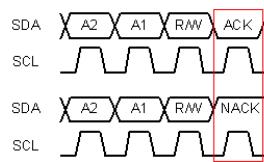

After transfer of each data byte, the Master or the sensor transmits an Acknowledge / Negative acknowledge and releases (does not drive) SDA. When a Negative acknowledge is generated, the Master must immediately generate the Stop Condition and end the communication.

Acknowledge, Negative Acknowledge

Figure 17: I2C negative acknowledge

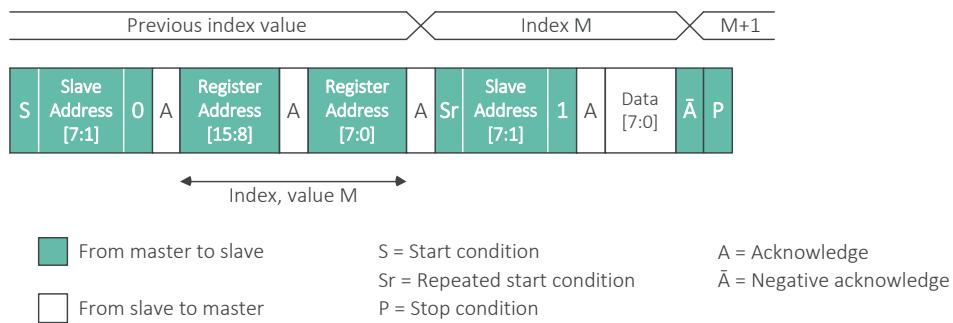

### 5.1.2. Single I<sup>2</sup>C Read

The sensor has an index function that indicates which address it is focusing on. When reading data, the Master must set the index value to the address to be read. For this purpose, it performs a dummy write operation up to the register address. The upper level of the figure shows the sensor internal index value, and the lower level of the figure shows the SDA I/O data flow. The Master sets the sensor index value to M by designating the sensor slave address with a write request, then designating the address (M). Then, the Master generates the start condition. The Start Condition is generated without generating the Stop Condition, so it becomes the Repeated Start Condition. Next, when the Master sends the slave address with a read request, the sensor outputs an Acknowledge immediately followed by the address data from index M on SDA. After the Master receives the data, it generates a Negative Acknowledge and the Stop Condition to end the communication

Note: It is possible to omit the Register Address [15:0] from the communication, in that case the sensor will simply read the value of register previously set to index M.

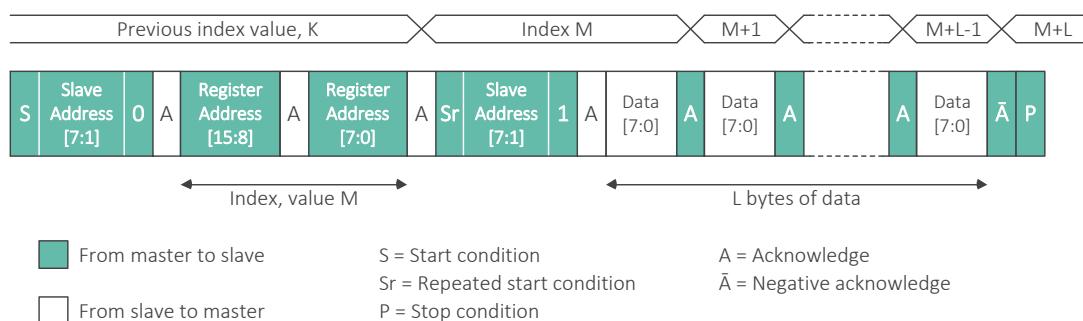

### 5.1.3. Sequential I<sup>2</sup>C Read

A sequential read of the data reads multiple registers sequentially without setting the register addresses individually. The Master must set the index value to the start of the addresses to be read. For this purpose, a dummy write operation includes the register address setting. The Master sets the sensor index value to M by designating the sensor slave address with a read request, then designating the address (M). Then, the Master generates the Repeated Start Condition. Next, when the Master sends the slave address with a read request, the sensor outputs an Acknowledge followed immediately by the data from index M on SDA. When the Master outputs an Acknowledge (instead of Negative acknowledge for a single I<sup>2</sup>C read) after it receives the data, the index value inside the sensor is incremented and the data at the next address is output on SDA. This allows the Master to read data sequentially. After reading the necessary data, the Master generates a Negative Acknowledge and the Stop Condition to end the communication.

Note: It is possible to omit the Register Address [15:0] from the communication, in that case the sensor will simply read the values of the registers starting at the previously set index M.

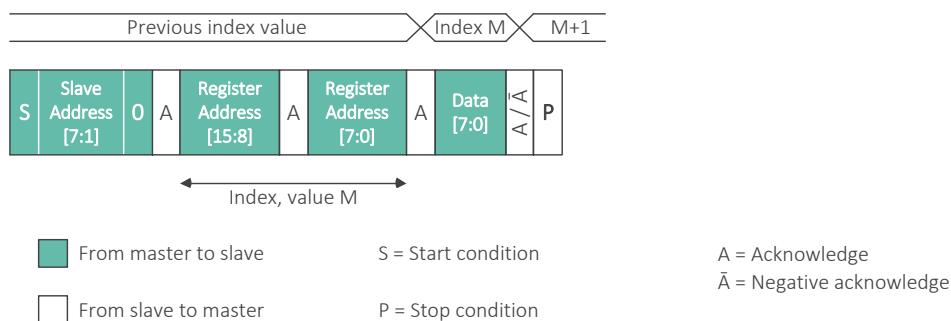

### 5.1.4. Single I<sup>2</sup>C Write

The Master sets the sensor index value to M by designating the sensor slave address with a write request, and designating the register address (M). After that the Master can write the value in the designated register by transmitting the data to be written. After writing the necessary data, the Master generates the Stop Condition to end the communication.

### 5.1.5. Sequential I<sup>2</sup>C Write

The Master can write a value to register address M by designating the sensor slave address with a write request, designating the address (M), and then transmitting the data to be written. After the sensor receives the write data, it outputs an Acknowledge and at the same time increments the register address, so the Master can write to the next address simply by continuing to transmit data. After the Master writes the necessary number of bytes, it generates the Stop Condition to end the communication.

### 5.1.6. I<sup>2</sup>C Slave Address

For communication with MLX75027 via I<sup>2</sup>C the user has to choose between two different 7bit slave addresses. Selection can be done by the external SLASEL pin, by connecting it either to VDDD (high) or DGND (low).

Note : I<sup>2</sup>C slave address 0x67 might not be programmed on engineering samples.

To avoid bring-up issues, please connect SLASEL to GND.

## 5.2. MIPI Alliance CSI-2 Description

This section describes a limited set of CSI-2 functionality needed to understand operation of MLX75027. For a full interface description, please refer to MIPI Alliance CSI-2 Specification version 1.20.

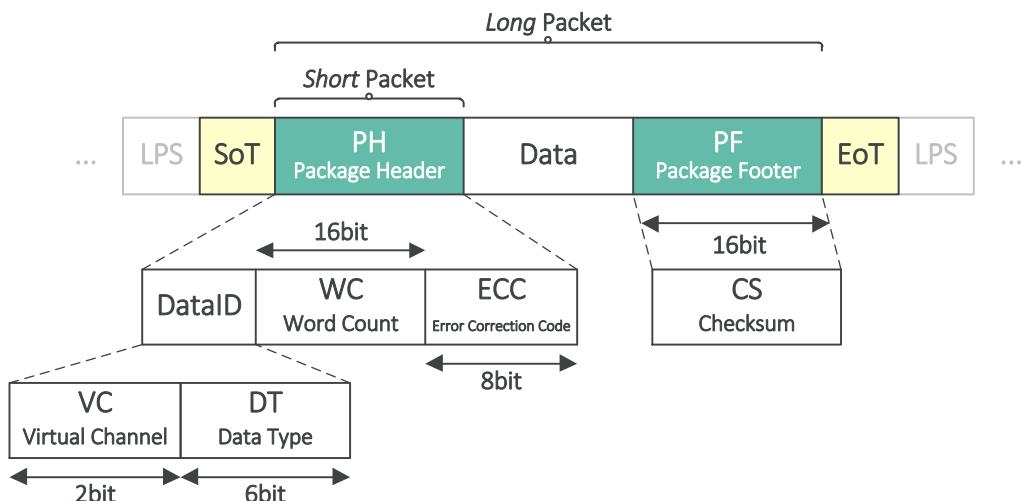

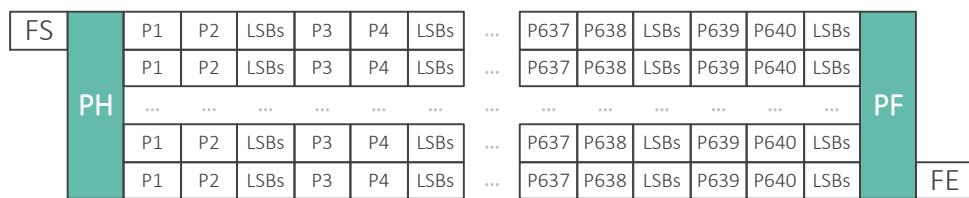

### 5.2.1. Packet Structure

CSI-2 uses a byte oriented, packet based protocol that supports the transport of arbitrary data using *Short Package* (SP) and *Long Package* (LP) formats. A 32bit *Short Package* does not have any data or a *Package Footer* (PF). Only FS (Frame Start) or FE (Frame End) indicators use *Short Packets*.

Figure 18: Package structure

Every packet starts with a SoT (start of transmission) sequence preceded by a LPS (low power state). An EoT (end of transmission) sequence followed by the low power state indicates the end of a packet.

Each byte is transmitted with the least significant bit first, in case of multi-byte data (such as WC or CS) the least significant byte will be transmitted first, unless otherwise specified by the data format.

- VC: The virtual channel identifier provides separate channels for different data flows that are interleaved in the data stream (lane indicator). The default value is 0.

- DT: The data type value specifies the format and content of the data payload.

|                         |                                    |

|-------------------------|------------------------------------|

| 0x00 = FS (Frame Start) | 0x12 = Embedded data (or MetaData) |

| 0x01 = FE (Frame End)   | 0x2C = RAW12 pixel data            |

- WC: For *short* packets the word count field is considered a 16bit data field, representing the Frame Count [7:0]. After each FS (Frame Start) transmission, the Frame Count will be increased by 1. For *long* packets word count specifies the total amount of bytes between the end of PH and start of PF.

- ECC: The error correction code used is a 7+1bits Hamming-modified code. This code allows single-bit errors to be corrected and 2-bit errors to be detected in the DataID and WC fields but is not capable of doing both simultaneously.

- CS: To detect possible errors in the data transmission, a checksum is calculated over each data packet. The checksum is a 16bit CRC generated by this polynomial:

$$CRC = x^{16} + x^{12} + x^5 + x^0$$

When WC is zero, CS will be 0xFFFF

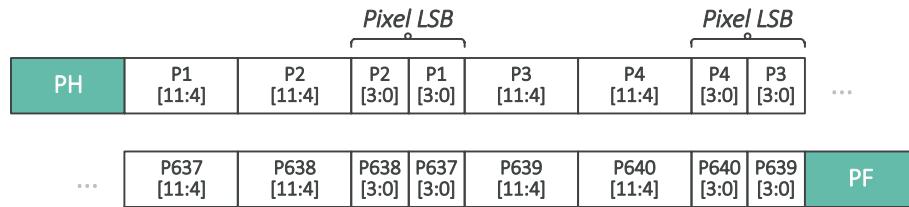

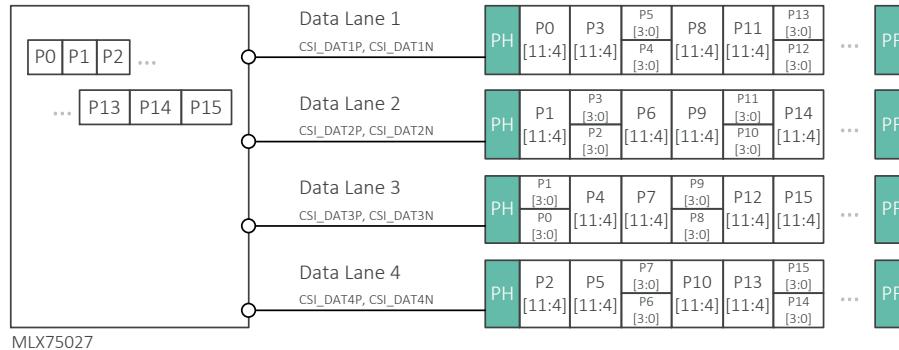

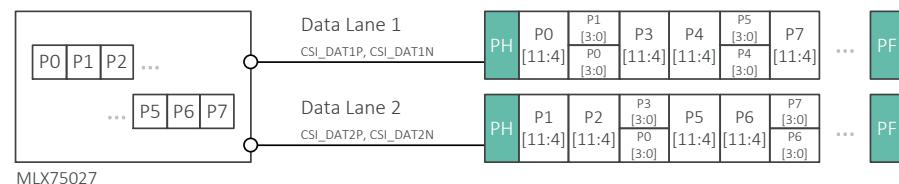

## 5.2.2. Data Format RAW12

Each DepthSense® pixel is represented by 12bit data packed like 8bit data.

Figure 19: Example of pixel ordering for one full line transmission

Figure 20: Example of pixel ordering for one full frame transmission

Table 15 specifies the minimum packet data size constraints.

The total length of each packet must be a multiple of the values in this table.

| # Pixels | # Bytes | # Bits |

|----------|---------|--------|

| 2        | 3       | 24     |

Table 15: RAW12 Packet size constraints

### 5.2.2.1. Data Format in 4 Lane MIPI Configuration

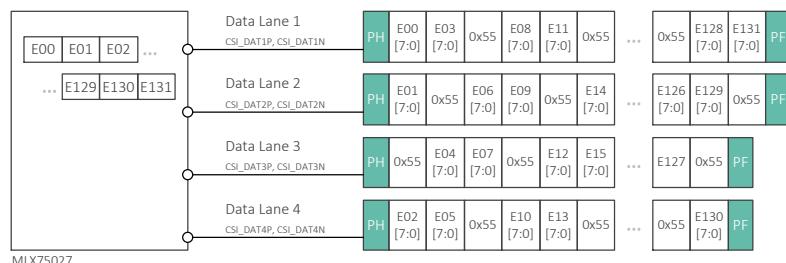

Figure 21: Pixel Data Format in 4 Lane Data Configuration

### 5.2.2.2. Data Format in 2 Lane MIPI Configuration

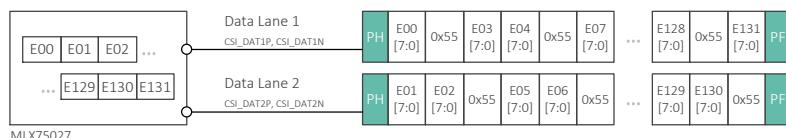

Figure 22: Pixel Data Format in 2 Lane Data Configuration

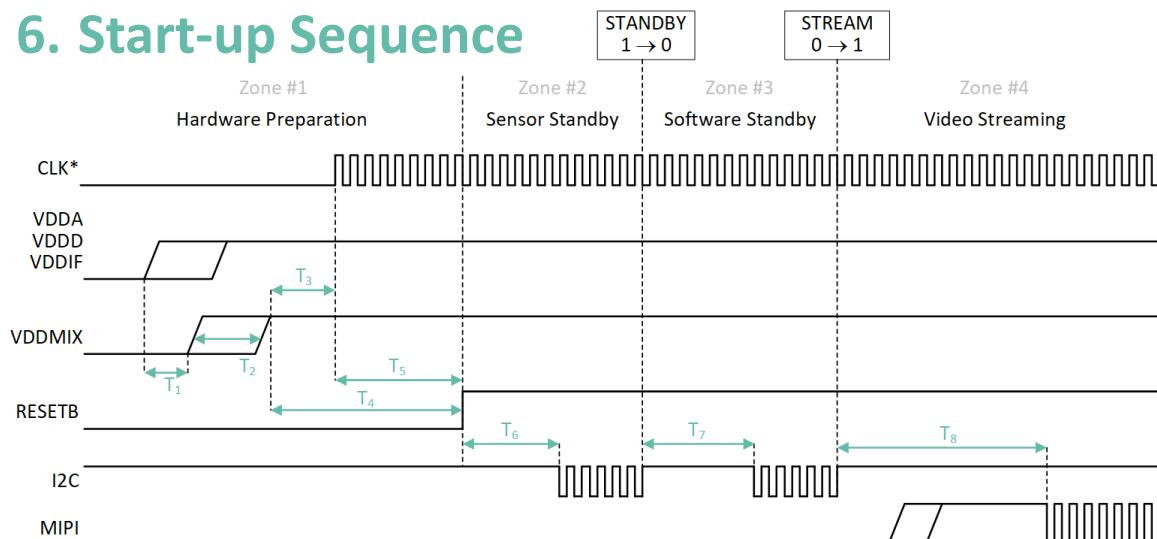

## 6. Start-up Sequence

Figure 23: Sensor start-up sequence

\* Availability of CLK signal before voltage domain bring up is also accepted

|        |   |   |   |   |   |   |   |   |         |

|--------|---|---|---|---|---|---|---|---|---------|

| 0x1000 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | STANDBY |

| R/W    | - | - | - | - | - | - | - | - |         |

Default Value 0x01

|        |   |   |   |   |   |   |   |   |        |

|--------|---|---|---|---|---|---|---|---|--------|

| 0x1001 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | STREAM |

| R/W    | - | - | - | - | - | - | - | - |        |

Default Value 0x00

**Zone #1 : Hardware Preparation :** Time to supply the clock, the required voltage domains and initialize the RESETB level. RESETB is a digital control signal, the µC keeps it low until all requirements of zone 2 have been fulfilled.

**Zone #2 : Sensor Standby :**

Time to define input clock settings, as shown in section 6

**Zone #3 : Software Standby :**

In this period it's advised to write all frame acquisition parameters (like integration time, modulation frequency & others) before video streaming.

**Zone #4 : Video Streaming :**

Frame capture is active and MIPI output data is available. Register changes during active frame acquisition will be applied on the next frame.

| Description                                                   | Symbol                                                                              | Min. | Max.                   | Unit               |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------|------|------------------------|--------------------|

| Slew rate for VDDA, VDDD, VDDIF, VDDMIX                       |  | S    |                        | $\frac{mV}{\mu s}$ |

| Time between VDDA, VDDD, VDDIF ON and VDDMIX ON               | T <sub>1</sub>                                                                      | 0    |                        | μs                 |

| Time between VDDMIX OFF and VDDMIX ON                         | T <sub>2</sub>                                                                      | 48   |                        | μs                 |

| Time between VDDMIX ON and CLK ON                             | T <sub>3</sub>                                                                      | 0    |                        | μs                 |

| Time between VDDA, VDDD, VDDIF, VDDMIX, CLK ON and RESETB OFF | T <sub>4</sub>                                                                      | 100  |                        | μs                 |

| Time between CLK ON and RESETB OFF                            | T <sub>5</sub>                                                                      | 0    |                        | μs                 |

| Time between RESETB and first I <sup>2</sup> C command        | T <sub>6</sub>                                                                      | 100  |                        | μs                 |

| Time between STANDBY OFF and STREAM ON                        | T <sub>7</sub>                                                                      | 12   |                        | ms                 |

| Time between STREAM ON and first video data                   | T <sub>8</sub>                                                                      |      | 2.8 + T <sub>int</sub> | ms                 |

Table 16: Startup timing

## 6.1. Initialization Process

MLX75027 requires a SW initialization on each start-up/reset and/or power cycle.

| Operating Mode              | Register Address                                                                                                   | Register Value | Comment                                                                                                                     |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------|

| <i>Hardware Preparation</i> |                                                                                                                    |                | End <i>Hardware Preparation</i> by pulling RESETB high                                                                      |

| <i>Sensor Standby</i>       | 0x1006                                                                                                             | 0x08           | Fixed Input Clock Settings                                                                                                  |

|                             | 0x1007                                                                                                             | 0x00           |                                                                                                                             |

|                             | 0x1040                                                                                                             | 0x00           |                                                                                                                             |

|                             | 0x1041                                                                                                             | 0x96           |                                                                                                                             |

|                             | 0x1042                                                                                                             | 0x01           |                                                                                                                             |

|                             | 0x1043                                                                                                             | 0x00           |                                                                                                                             |

|                             | 0x1044                                                                                                             | 0x00           |                                                                                                                             |

|                             | 0x1046                                                                                                             | 0x01           |                                                                                                                             |

|                             | 0x104A                                                                                                             | 0x01           |                                                                                                                             |

|                             | 0x1000                                                                                                             | 0x00           | Change from <i>Sensor Standby</i> to <i>Software Standby</i> by changing register 0x1000 (default value 0x01) to value 0x00 |

| <i>Software Standby</i>     | 313 initialization registers                                                                                       |                | Program the FULL initialization map from section 6.2                                                                        |

|                             | Add here relevant application registers that require an update of their reset value<br>▼ (examples listed below) ▼ |                |                                                                                                                             |

|                             | 0x100C<br>...<br>0x1071                                                                                            | custom         | Configure video output interface (see section 7.1)                                                                          |

|                             | 0x2020                                                                                                             | custom         | Configure TRIGGER or CONTINUOUS mode (see section 7.2)                                                                      |

|                             | 0x2100                                                                                                             | custom         |                                                                                                                             |

|                             | 0x2F05                                                                                                             | custom         |                                                                                                                             |

|                             | 0x2F06                                                                                                             | custom         |                                                                                                                             |

|                             | 0x2F07                                                                                                             | custom         |                                                                                                                             |

|                             | 0x3071                                                                                                             | custom         |                                                                                                                             |

|                             | 0x0828                                                                                                             | custom         | Configure Data Output Mode (see section 7.3)                                                                                |

|                             | 0x0800                                                                                                             | custom         | Configure HMAX related settings (see section 7.4)                                                                           |

|                             | 0x5267                                                                                                             | custom         |                                                                                                                             |

|                             | 0x21BE<br>...<br>0x104B                                                                                            | custom         | Configure Modulation Frequency (see section 7.7)                                                                            |

|                             | 0x21E8                                                                                                             | custom         | Configure number of phases (see section 7.11)                                                                               |

|                             | 0x2120<br>...<br>0x213F                                                                                            | custom         | Configure Integration Time per phase (see section 7.13)                                                                     |

|                             | 0x21B4<br>...<br>0x21B7                                                                                            | custom         | Configure PHASE_SHIFT per phase (see section 7.14)                                                                          |

|                             | ▲ End of relevant application registers ▲                                                                          |                |                                                                                                                             |

|                             | 0x1001                                                                                                             | 0x01           | Enter <i>Video Streaming</i> by changing register 0x1001 (value 0x00) to value 0x01                                         |

| <i>Video Streaming</i>      |                                                                                                                    |                | Application is now running                                                                                                  |

Table 17: Initialisation process

## 6.2. Initialization Register Map

This set of initialization registers are listed in order of priority (top > bottom, left > right, next page) :

| Register Address | Register Value |

|------------------|----------------|

| 0x10D2           | 0x00           |

| 0x10D3           | 0x10           |

| 0x1433           | 0x00           |

| 0x1448           | 0x06           |

| 0x1449           | 0x40           |

| 0x144A           | 0x06           |

| 0x144B           | 0x40           |

| 0x144C           | 0x06           |

| 0x144D           | 0x40           |

| 0x144E           | 0x06           |

| 0x144F           | 0x40           |

| 0x1450           | 0x06           |

| 0x1451           | 0x40           |

| 0x1452           | 0x06           |

| 0x1453           | 0x40           |

| 0x1454           | 0x06           |

| 0x1455           | 0x40           |

| 0x1456           | 0x06           |

| 0x1457           | 0x40           |

| 0x21C4           | 0x00           |

| 0x2202           | 0x00           |

| 0x2203           | 0x1E           |

| 0x2C08           | 0x01           |

| 0x3C2B           | 0x1B           |

| 0x400E           | 0x01           |

| 0x400F           | 0x81           |

| 0x40D1           | 0x00           |

| 0x40D2           | 0x00           |

| 0x40D3           | 0x00           |

| 0x40DB           | 0x3F           |

| 0x40DE           | 0x40           |

| 0x40DF           | 0x01           |

| 0x412C           | 0x00           |

| 0x4134           | 0x04           |

| 0x4135           | 0x04           |

| 0x4136           | 0x04           |

| 0x4137           | 0x04           |

| 0x4138           | 0x04           |

| 0x4139           | 0x04           |

| 0x413A           | 0x04           |

| 0x413B           | 0x04           |

| Register Address | Register Value |

|------------------|----------------|

| 0x413C           | 0x04           |

| 0x4146           | 0x01           |

| 0x4147           | 0x01           |

| 0x4148           | 0x01           |

| 0x4149           | 0x01           |

| 0x414A           | 0x01           |

| 0x414B           | 0x01           |

| 0x414C           | 0x01           |

| 0x414D           | 0x01           |

| 0x4158           | 0x01           |

| 0x4159           | 0x01           |

| 0x415A           | 0x01           |

| 0x415B           | 0x01           |

| 0x415C           | 0x01           |

| 0x415D           | 0x01           |

| 0x415E           | 0x01           |

| 0x415F           | 0x01           |

| 0x4590           | 0x00           |

| 0x4591           | 0x2E           |

| 0x4684           | 0x00           |

| 0x4685           | 0xA0           |

| 0x4686           | 0x00           |

| 0x4687           | 0xA1           |

| 0x471E           | 0x07           |

| 0x471F           | 0xC9           |

| 0x473A           | 0x07           |

| 0x473B           | 0xC9           |

| 0x4770           | 0x00           |

| 0x4771           | 0x00           |

| 0x4772           | 0x1F           |

| 0x4773           | 0xFF           |

| 0x4778           | 0x06           |

| 0x4779           | 0xA4           |

| 0x477A           | 0x07           |

| 0x477B           | 0xAE           |

| 0x477D           | 0xD6           |

| 0x4788           | 0x06           |

| 0x4789           | 0xA4           |

| 0x478C           | 0x1F           |

| 0x478D           | 0xFF           |

| 0x478E           | 0x00           |

| Register Address | Register Value |

|------------------|----------------|

| 0x478F           | 0x00           |

| 0x4792           | 0x00           |

| 0x4793           | 0x00           |

| 0x4796           | 0x00           |

| 0x4797           | 0x00           |

| 0x479A           | 0x00           |

| 0x479B           | 0x00           |

| 0x479C           | 0x1F           |

| 0x479D           | 0xFF           |

| 0x479E           | 0x00           |

| 0x479F           | 0x00           |

| 0x47A2           | 0x00           |

| 0x47A3           | 0x00           |

| 0x47A6           | 0x00           |

| 0x47A7           | 0x00           |

| 0x47AA           | 0x00           |

| 0x47AB           | 0x00           |

| 0x47AC           | 0x1F           |

| 0x47AD           | 0xFF           |

| 0x47AE           | 0x00           |

| 0x47AF           | 0x00           |

| 0x47B2           | 0x00           |

| 0x47B3           | 0x00           |

| 0x47B6           | 0x00           |

| 0x47B7           | 0x00           |

| 0x47BA           | 0x00           |

| 0x47BB           | 0x00           |

| 0x47BC           | 0x1F           |

| 0x47BD           | 0xFF           |

| 0x47BE           | 0x00           |

| 0x47BF           | 0x00           |

| 0x47C2           | 0x00           |

| 0x47C3           | 0x00           |

| 0x47C6           | 0x00           |

| 0x47C7           | 0x00           |

| 0x47CA           | 0x00           |

| 0x47CB           | 0x00           |

| 0x4834           | 0x00           |

| 0x4835           | 0xA0           |

| 0x4836           | 0x00           |

| 0x4837           | 0xA1           |

| Register Address | Register Value |

|------------------|----------------|

| 0x4878           | 0x00           |

| 0x4879           | 0xA0           |

| 0x487A           | 0x00           |

| 0x487B           | 0xA1           |

| 0x48BC           | 0x00           |

| 0x48BD           | 0xA0           |

| 0x48BE           | 0x00           |

| 0x48BF           | 0xA1           |

| 0x4954           | 0x00           |

| 0x4955           | 0xA0           |

| 0x4956           | 0x00           |

| 0x4957           | 0xA1           |

| 0x4984           | 0x00           |

| 0x4985           | 0xA0           |

| 0x4986           | 0x00           |

| 0x4987           | 0xA1           |

| 0x49B8           | 0x00           |

| 0x49B9           | 0x78           |

| 0x49C2           | 0x00           |

| 0x49C3           | 0x3C           |

| 0x49C8           | 0x00           |

| 0x49C9           | 0x76           |

| 0x49D2           | 0x00           |

| 0x49D3           | 0x3F           |

| 0x49DC           | 0x00           |

| 0x49DD           | 0xA0           |

| 0x49DE           | 0x00           |

| 0x49DF           | 0xA1           |

| 0x49EE           | 0x00           |

| 0x49EF           | 0x78           |

| 0x49F8           | 0x00           |

| 0x49F9           | 0x3C           |

| 0x49FE           | 0x00           |

| 0x49FF           | 0x78           |

| 0x4A04           | 0x00           |

| 0x4A05           | 0x3C           |

| 0x4A0A           | 0x00           |

| 0x4A0B           | 0x76           |

| 0x4A10           | 0x00           |

| 0x4A11           | 0x3F           |

| 0x4A1A           | 0x00           |

Table 18: Initialization Map Part I

| Register Address | Register Value |

|------------------|----------------|------------------|----------------|------------------|----------------|------------------|----------------|

| 0x4A1B           | 0xA0           | 0x4BC6           | 0x00           | 0x4D1B           | 0x49           | 0x4E39           | 0x07           |

| 0x4A1C           | 0x00           | 0x4BC7           | 0x1A           | 0x4D1E           | 0x07           | 0x4E7B           | 0x64           |

| 0x4A1D           | 0xA1           | 0x4BCE           | 0x00           | 0x4D1F           | 0xC9           | 0x4E8E           | 0x0E           |

| 0x4A1E           | 0x00           | 0x4BCF           | 0x1A           | 0x4D2A           | 0x07           | 0x4E9A           | 0x00           |

| 0x4A1F           | 0x78           | 0x4BEE           | 0x00           | 0x4D2B           | 0xC9           | 0x4E9C           | 0x01           |

| 0x4A28           | 0x00           | 0x4BEF           | 0xA0           | 0x4D4A           | 0x07           | 0x4EA0           | 0x01           |

| 0x4A29           | 0x3C           | 0x4BF0           | 0x00           | 0x4D4B           | 0xC9           | 0x4EA1           | 0x03           |

| 0x4A4A           | 0x00           | 0x4BF1           | 0xA1           | 0x4D50           | 0x06           | 0x4EA5           | 0x00           |

| 0x4A4B           | 0xA0           | 0x4BF6           | 0x00           | 0x4D51           | 0x9B           | 0x4EA7           | 0x00           |

| 0x4A4C           | 0x00           | 0x4BF7           | 0x1A           | 0x4D52           | 0x07           | 0x4F05           | 0x04           |

| 0x4A4D           | 0xA1           | 0x4C00           | 0x00           | 0x4D53           | 0xAE           | 0x4F0D           | 0x04           |

| 0x4A7A           | 0x00           | 0x4C01           | 0x1A           | 0x4D56           | 0x07           | 0x4F15           | 0x04           |

| 0x4A7B           | 0xA0           | 0x4C58           | 0x00           | 0x4D57           | 0xC9           | 0x4F19           | 0x01           |

| 0x4A7C           | 0x00           | 0x4C59           | 0xA0           | 0x4D5C           | 0x06           | 0x4F20           | 0x01           |

| 0x4A7D           | 0xA1           | 0x4C5A           | 0x00           | 0x4D5D           | 0x98           | 0x4F66           | 0x0F           |

| 0x4AEE           | 0x00           | 0x4C5B           | 0xA1           | 0x4D5E           | 0x07           | 0x500F           | 0x01           |

| 0x4AEF           | 0xA0           | 0x4C6E           | 0x00           | 0x4D5F           | 0xB1           | 0x5224           | 0x00           |

| 0x4AF0           | 0x00           | 0x4C6F           | 0xA0           | 0x4D70           | 0x06           | 0x5225           | 0x2F           |

| 0x4AF1           | 0xA1           | 0x4C70           | 0x00           | 0x4D71           | 0xA4           | 0x5226           | 0x00           |

| 0x4B2E           | 0x00           | 0x4C71           | 0xA1           | 0x4D72           | 0x07           | 0x5227           | 0x1E           |

| 0x4B2F           | 0xA0           | 0x4C7A           | 0x01           | 0x4D73           | 0x49           | 0x5230           | 0x00           |

| 0x4B30           | 0x00           | 0x4C7B           | 0x35           | 0x4D78           | 0x06           | 0x5231           | 0x19           |

| 0x4B31           | 0xA1           | 0x4CF2           | 0x07           | 0x4D79           | 0xA4           | 0x5244           | 0x00           |

| 0x4B5A           | 0x00           | 0x4CF3           | 0xC9           | 0x4D7A           | 0x07           | 0x5245           | 0x07           |

| 0x4B5B           | 0xA0           | 0x4CF8           | 0x06           | 0x4D7B           | 0xAE           | 0x5252           | 0x07           |

| 0x4B5C           | 0x00           | 0x4CF9           | 0x9B           | 0x4D7C           | 0x1F           | 0x5253           | 0x08           |

| 0x4B5D           | 0xA1           | 0x4CFA           | 0x07           | 0x4D7D           | 0xFF           | 0x5254           | 0x07           |

| 0x4B86           | 0x00           | 0x4CFB           | 0xAE           | 0x4D7E           | 0x1F           | 0x5255           | 0xB4           |

| 0x4B87           | 0xA0           | 0x4CFE           | 0x07           | 0x4D7F           | 0xFF           | 0x5271           | 0x00           |

| 0x4B88           | 0x00           | 0x4cff           | 0xC9           | 0x4D80           | 0x06           | 0x5272           | 0x04           |

| 0x4B89           | 0xA1           | 0x4D04           | 0x06           | 0x4D81           | 0xA4           | 0x5273           | 0x2E           |

| 0x4B9E           | 0x00           | 0x4D05           | 0x98           | 0x4D82           | 0x07           | 0x5281           | 0x00           |

| 0x4B9F           | 0x1A           | 0x4D06           | 0x07           | 0x4D83           | 0xAE           | 0x5282           | 0x04           |

| 0x4BAE           | 0x00           | 0x4D07           | 0xB1           | 0x4D84           | 0x1F           | 0x5283           | 0x2E           |

| 0x4BAF           | 0x1A           | 0x4D18           | 0x06           | 0x4D85           | 0xFF           | 0x5285           | 0x00           |

| 0x4BB6           | 0x00           | 0x4D19           | 0xA4           | 0x4D86           | 0x1F           | 0x5286           | 0x00           |

| 0x4BB7           | 0x1A           | 0x4D1A           | 0x07           | 0x4D87           | 0xFF           | 0x5287           | 0x5D           |

Table 19: Initialization Map Part II

## 7. Register Settings

### 7.1. Video Output Configuration

Correct data communication settings have to be programmed in *Software Standby* mode. This is part of the initialization map as described in section 6.

|        |   |   |   |   |   |   |                  |   |

|--------|---|---|---|---|---|---|------------------|---|

| 0x1010 | 7 | 6 | 5 | 4 | 3 | 2 | 1                | 0 |

| R/W    | - | - | - | - | - | - | DATA_LANE_CONFIG | 1 |

Reset Value 0x03

- 1b0: 2 data lane configuration

- 1b1: 4 data lane configuration (= default)

Registers listed in Table 20 and Table 21 need to be updated to support data transmission speeds of 300, 600, 704, 800 & 960 Mbps.

| # Data Lanes | Comm. Speed | 0x100C | 0x100D | 0x100E | 0x100F | 0x1016 | 0x1017 | 0x1045 | 0x1047 | 0x1060 | 0x1071 |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 2            | 300 Mbps    | 0x02   | 0x58   | 0x00   | 0x00   | 0x09   | 0x99   | 0x4B   | 0x02   | 0x01   | 0x0C   |

|              | 600 Mbps    | 0x04   | 0xB0   | 0x00   | 0x00   | 0x04   | 0xCC   | 0x4B   | 0x02   | 0x00   | 0x06   |

|              | 704 Mbps    | 0x05   | 0x80   | 0x00   | 0x00   | 0x04   | 0x17   | 0x58   | 0x02   | 0x00   | 0x06   |

|              | 800 Mbps    | 0x06   | 0x40   | 0x00   | 0x00   | 0x03   | 0x99   | 0x64   | 0x02   | 0x00   | 0x06   |

|              | 960 Mbps    | 0x07   | 0x80   | 0x00   | 0x00   | 0x03   | 0x00   | 0x78   | 0x02   | 0x00   | 0x06   |

| 4            | 300 Mbps    | 0x04   | 0xB0   | 0x00   | 0x00   | 0x09   | 0x99   | 0x4B   | 0x02   | 0x01   | 0x0C   |

|              | 600 Mbps    | 0x09   | 0x60   | 0x00   | 0x00   | 0x04   | 0xCC   | 0x4B   | 0x02   | 0x00   | 0x06   |

|              | 704 Mbps    | 0x0B   | 0x00   | 0x00   | 0x00   | 0x04   | 0x17   | 0x58   | 0x02   | 0x00   | 0x06   |

|              | 800 Mbps    | 0x0C   | 0x80   | 0x00   | 0x00   | 0x03   | 0x99   | 0x64   | 0x02   | 0x00   | 0x06   |

|              | 960 Mbps    | 0x0F   | 0x00   | 0x00   | 0x00   | 0x03   | 0x00   | 0x78   | 0x00   | 0x00   | 0x06   |

Table 20: Data Rate Configuration Settings 1

| # Data Lanes | Comm. Speed | 0x10C2 | 0x10C3 | 0x10C4 | 0x10C5 | 0x10D0 | 0x10D4 | 0x10D5 |

|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|

| 2 & 4        | 300 Mbps    | 0x00   | 0x1C   | 0x01   | 0x3A   | 0X0A   | 0X00   | 0XC5   |

|              | 600 Mbps    | 0X00   | 0X0F   | 0X00   | 0X9D   | 0X0A   | 0X00   | 0XC5   |

|              | 704 Mbps    | 0X00   | 0X0D   | 0X00   | 0X86   | 0X0A   | 0X00   | 0XC5   |

|              | 800 Mbps    | 0X00   | 0X0B   | 0X00   | 0X75   | 0X0A   | 0X00   | 0XC5   |

|              | 960 Mbps    | 0X00   | 0X0A   | 0X00   | 0X62   | 0X0A   | 0X00   | 0XC5   |

Table 21: Data Rate Configuration Settings 2

|        |   |   |   |   |   |   |   |         |

|--------|---|---|---|---|---|---|---|---------|

| 0x1C40 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

| R/W    | - | - | - | - | - | - | - | CLK_OFF |

Reset Value 0x01

The clock enters a low power state (LPS) between the different data frames (CLK\_OFF=1) by default. It is possible to enable to clock continuously (stay in HS mode during frame blanking) via parameter CLK\_OFF=0 for compatibility with some microcontrollers.

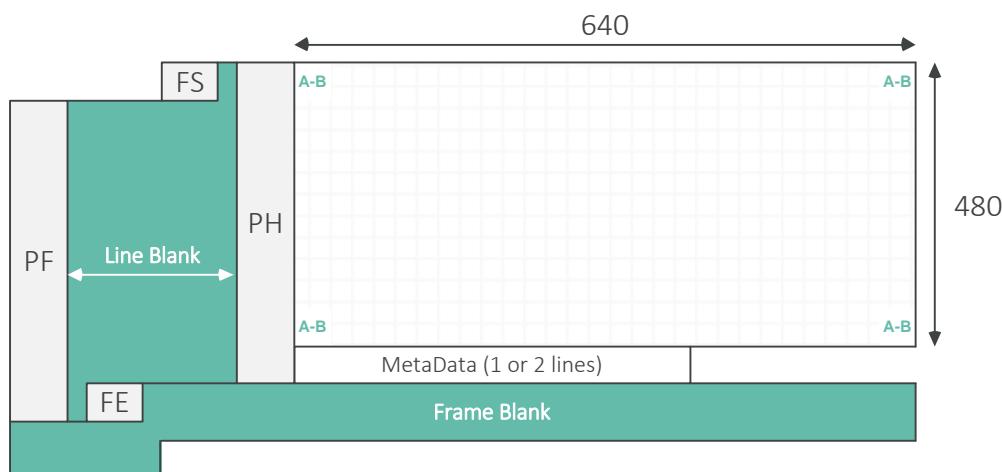

## 7.2. Modes of Operation

MLX75027 features three modes of operation: hardware triggered, software triggered or continuous mode. It's mandatory to change the operating mode during *Software Standby* as described in section 6.

| Register Address | Register Value                                   |                                                                                      |                                                                                                  |

|------------------|--------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

|                  | HARDWARE TRIGGERED MODE<br>(by external pin K11) | SOFTWARE TRIGGERED MODE                                                              | CONTINUOUS MODE<br>(trigger will occur internally at each FRAME_TIME interval, see section 7.10) |

| 0x2020           | 0x00                                             | 0x01                                                                                 | 0x01                                                                                             |

| 0x2100           | 0x00                                             | 0x01<br>(bit[0] is a self-clearing bit that acts as trigger when set to 0x1 via I2C) | 0x08                                                                                             |

| 0x2F05           | 0x07                                             | 0x01                                                                                 | 0x01                                                                                             |

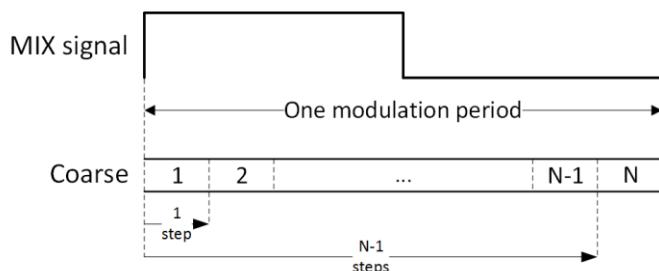

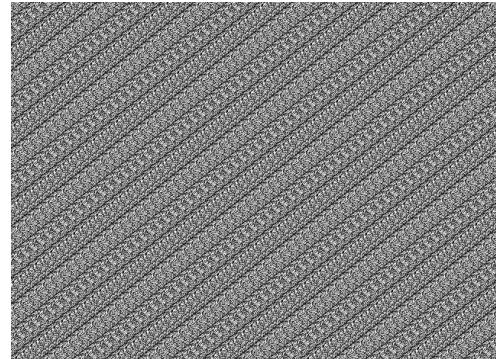

| 0x2F06           | 0x00                                             | 0x09                                                                                 | 0x09                                                                                             |